最新存储器习题及参考答案

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

习题四参考答案

1. 某机主存储器有16位地址,字长为8位。

(1)如果用1k X 4位的RAM芯片构成该存储器,需要多少片芯片?

(2)该存储器能存放多少字节的信息?

(3)片选逻辑需要多少位地址?

解:需要存储器总容量为:16K X 8位,故,

(1)需要1k X 4位的RAMI芯片位32片。

(2)该存储器存放16K字节的信息。

(3)片选逻辑需要4位地址。

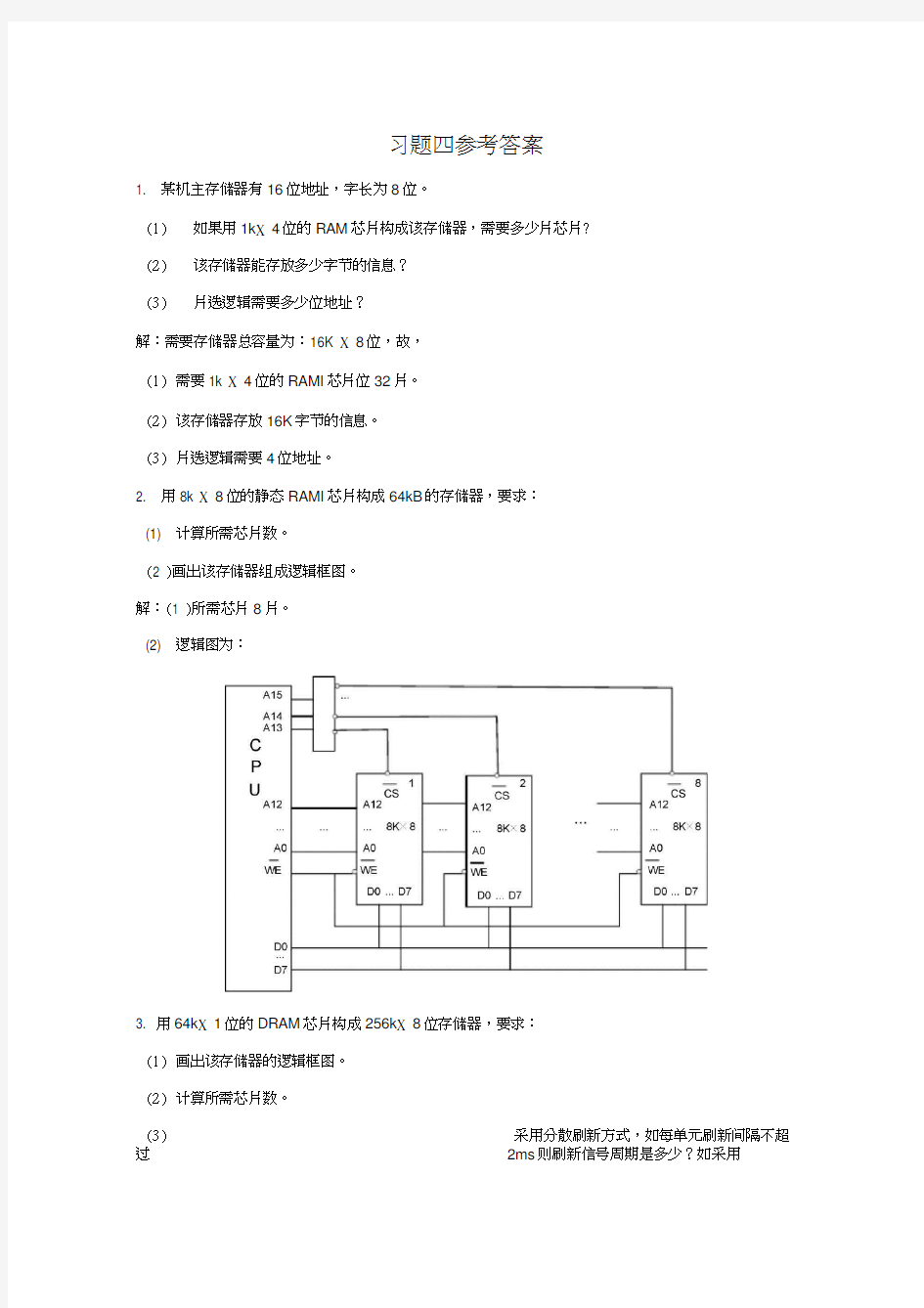

2. 用8k X 8位的静态RAMI芯片构成64kB的存储器,要求:

(1) 计算所需芯片数。

(2 )画出该存储器组成逻辑框图。

解:(1 )所需芯片8片。

(2) 逻辑图为:

3. 用64k X 1位的DRAM芯片构成256k X 8位存储器,要求:

(1)画出该存储器的逻辑框图。

(2)计算所需芯片数。

(3)采用分散刷新方式,如每单元刷新间隔不超过2ms则刷新信号周期是多少?如采用

集中刷新方式,存储器刷新一遍最少用多少读/写周期?解: (1)

DO D7

(2)所需芯片为32片。

(3) 设读写周期为0.5微妙,则采用分散式刷新方式的刷新信号周期为

X 1的存储矩阵是由四个 128X 128的矩阵构成,刷新时 4个存储矩阵同时对

128个元素操 作,一次刷新就可完成 512个元素,整个芯片只有128次刷新操作就可全部完成。 所以存储 器刷新一遍最少用128个读/写周期。

4. 用8k X 8位的EPROMS 片组成32k X 16位的只读存储器,试问: (1) 数据寄存器多少位? (2) 地址寄存器多少位? (3) 共需多少个 EPROMS 片? (4) 画出该只读存储器的逻辑框图?

解:因为只读存储器的容量为: 32k X 16,所以: (1) 数据寄存器16位。 (2) 地址寄存器15位。 (3) 共需8个EPROMS 片? (4) 逻辑框图为:

A17 A16

C U

A15

A7

CS

A7

CS

CS

CS WE

AO A7

A7

AO AO ©CAS 斗RAS

WE

CAS CAS T

RAS RAS

WE

64K X 1

WE

AO RAS

64K X 1

WE

1微妙。因为64K

AO

DRAMC

64K X 1

64K X 1

CAS

5. 某机器中,已经配有OOOOH- 3FFFH的ROM区域,现在再用8k X 8位的RAM芯片形成32k X 8位的存储区域,CPU地址总线为A0〜A15,数据总线为DO〜D7,控制信号为R/W(读/写)、

MRE Q访存),要求:

(1)画出地址译码方案。

(2)将ROM与RAM同CPU连接。

解:依题意假设存储器ROM和RAM的信息分布为:

ROM的地址为:0000H-3FFFH。RAM由8KB的四个RAM芯片组成,其

地址分别为:第一片:4000H-5FFFH,第二片:6000H-7FFFH

第三片:8000H-9FFFH第四片:A000H-BFFFH由以上分析可得其连接图

为:

6.对于单管动态存储电路, 如果其电容C=5pF,通过晶体管的漏电流为 2nA 。当电容C 被充 满电荷时, 两端电压为4.5V 。在此电压降到3V 之前,必须被刷新,请算出最小的刷新周期。 解:因为: . du "亠 1 = C ,其中,c=5pF,i=2 nA,du=4.5-3=1.5V

dt 所以,dt=3.75ms 。即最小的刷新周期为 3.75ms 。

7. 某计算机主存8MB 分成4096页,CACHED 64KB,和主存分成同样大小的页, 地址映映采用直接映像方式。

(1) CACHE!多少页?

(2) CACHE 勺页内地址为多少位?

(3) CACHE 勺页面地址为多少位?

(4) 设CACHED 主存标记如图3.1所示,当CPU 送出的地址为 6807FFH 时,能否

在CACHED 访问到该单元?若送出的地址为

2D07FFH 时,能否在CACHED 访问该

单元?若送出的地址为 751057H 时,能否在 CACHE 中访问到该单元?若送出的地址

为 000000H 时,能否在CACHED 访问到该单元?

解:(1 )主存每一页的大小为: 8M/4096=2KB 。 CACHE 勺页数为:64KB/2KB=32 (页)。 (3) CACHE 勺页内地址为 5位。

(4) 因为主存共有8MB 容量,所以主存地址共有 23位。格式为

:

当CPU 送出的地址为:6807FFH 时,转为二进制格式: 1101000, 00000 11111111111 以中间五位为页号查表, 得到标记为1101000,与地址中的标记进行比较,

相同,所以命中。

同样的道理,可知地址为 2D07FFH 7F1057时,也是命中。地址为 0000000H 没命中。 8. 一个组相联高速缓存由 64页(每页256字)组成,分为8组,主存有4096页。

(2)因为CACHE 勺一页大小为 2KB,所以CACHE 勺页内地址为 11位。

(1) 主存地址有多少位?

(2) 主存地址的标志段、组字段和字字段各有多少位?

解:(1)因为主存共有4096页,每页有256字,故主存共有4096*256字=220字,所以,主 存地址有20位。 (2)

9. 某计算机有64KB 的主存和4KB 的CACHE CACHED 组如下:每组4页,每页64字。存储 系统按组相联方式工作。

(1) 主存地址的标志段、组字段和字字段各有多少位?

(2) 若CACHED 来是空的,CPU 依次从0号地址单元顺序访问到 4344号单元,然后重复按 此序列访问存储器15次,页替换采用LRU 算法。若访问CACHE 勺时间为20ns ,访问主存的 时间为200ns ,试估计CPU

访存的平均时间。 解:主存的地址格式为:

因为某计算机有64KB 的主存,所以主存地址的总位数为

16位。 依题意得CACHE 勺组数为:4K/ (64*4 ) =16 (组),故CACHE 勺组字段位数为4位,也就是 主存的组字段位数。

主存的一页大小和 CACHE 勺一页大小一样,故主存的 字字段位数 位为6位。 由主存的地址格式可知,主存的标志字段位数为16-4-6=4位。 所以:主存的地址格式及各字段包含的位数为:

(2) CPU 平均访问时间的计算公式为:

t a = ht c +(1-h )t m

其中t c 表示命中时的CACHED 问时间,t m 表示未命中时的贮存访问时间,1-h 表示未命中率。 CACH 共有16组,每组4页,每页64字。主存分为16区,每区16块,每块64字。 主存地址 0-4344 转为二进制的地址(16 位)为:000000 0000 000000--000100 0011 111000