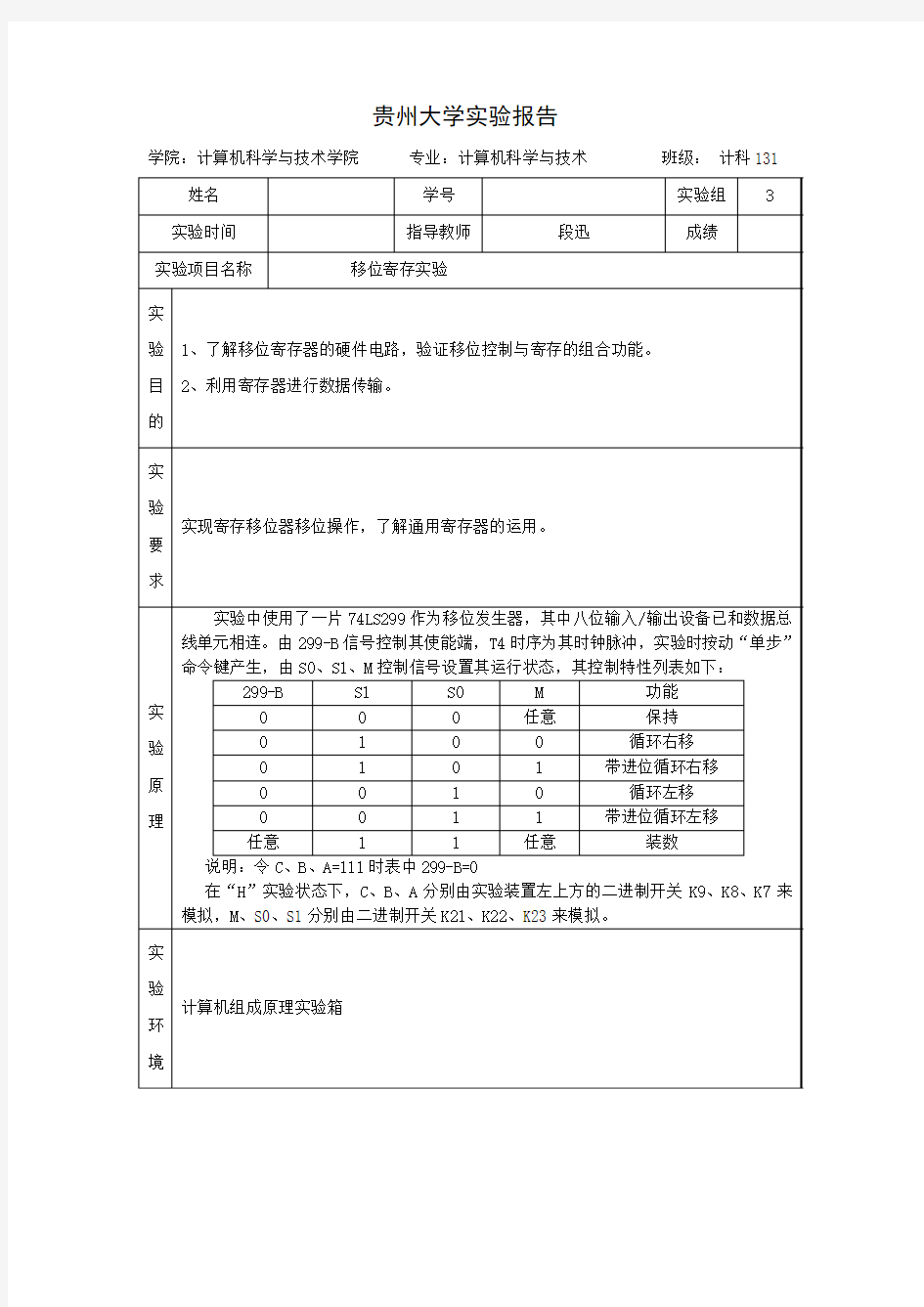

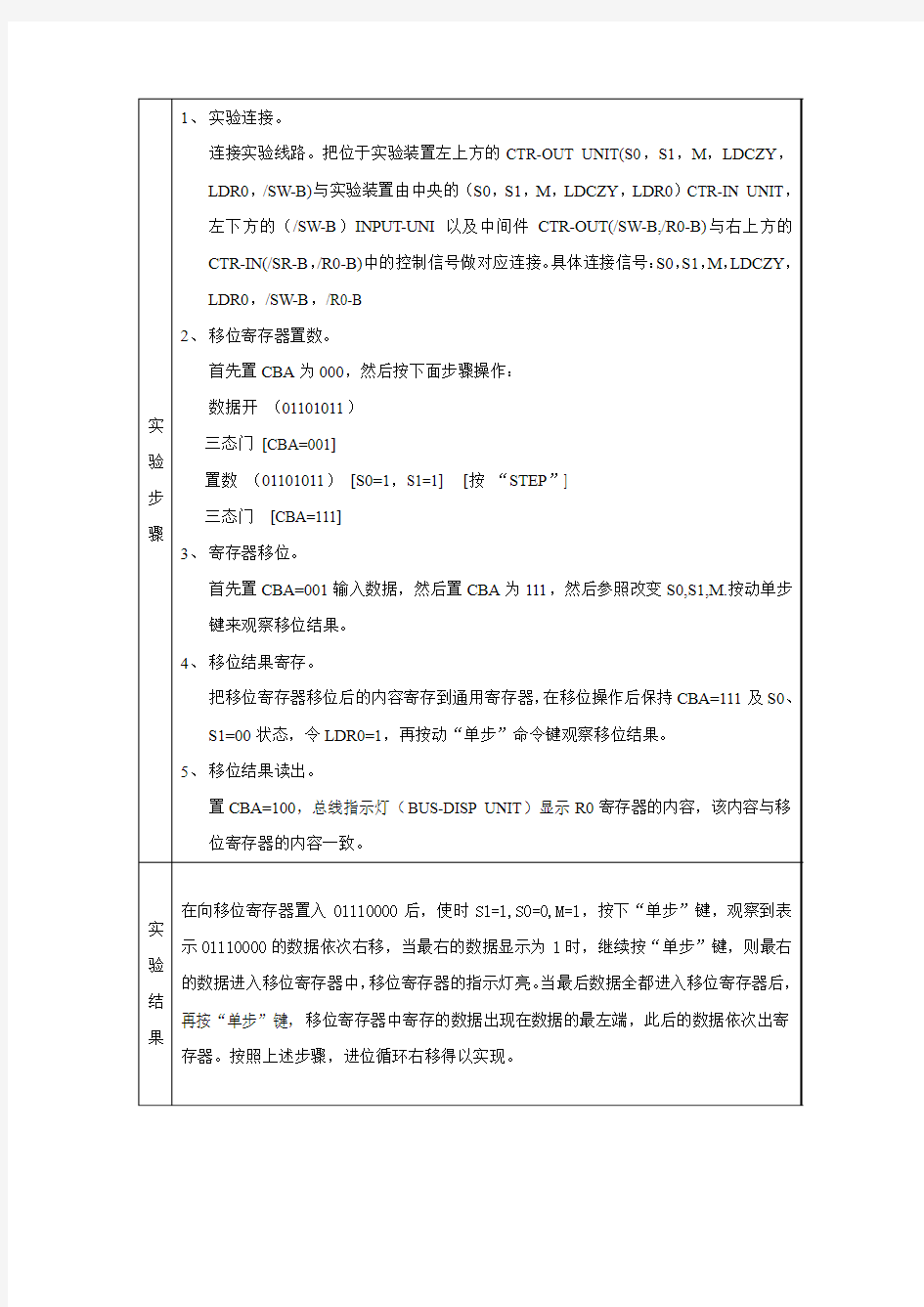

移位寄存实验

贵州大学实验报告

学院:计算机科学与技术学院专业:计算机科学与技术班级:计科131

寄存器实验报告

寄存器实验报告

一、实验目的 1. 了解寄存器的分类方法,掌握各种寄存器的工作原理; 2. 学习使用V erilog HDL 语言设计两种类型的寄存器。 二、实验设备 PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。 三、实验内容 寄存器中二进制数的位可以用两种方式移入或移出寄存器。第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。 本实验使用V erilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。 四、实验步骤 1.并行输入串行输出移位寄存器实验步骤 1). 运行Quartus II 软件,选择File New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。 2.) 选择File New 菜单,创建V erilog HDL 描述语言设计文件,打开文本编辑器界面。 3.) 在文本编辑器界面中编写V erilog HDL 程序,源程序如下: module SHFIT8R(din,r_st,clk,load,dout); input [7:0]din; input clk,r_st,load; output dout; reg dout; reg [7:0]tmp; always @(posedge clk) if(!r_st) begin dout<=0; end else begin if(load) begin tmp=din; end else

数字电路实验6移位寄存器的应用

实验报告 课程名称:数字电路实验第 6 次实验实验名称:移位寄存器的应用 实验时间:2012 年 5 月7 日 实验地点:组号 学号: 姓名: 指导教师:评定成绩:

《数字电路与系统设计》实验指导书 1 实验六移位寄存器应用 一、实验目的: 1.了解寄存器的基本结构。 2.掌握74LS194移位寄存器的逻辑功能。 3.学习中规模移位寄存器的应用。 二、实验仪器: 三、实验原理: 数据的存储和移动是数字信号的一种常见运作,能实现这种动作的是数据寄存器和移位寄存器,它们同计数器一样也是数字电路中不可缺少的基本逻辑器件。数据寄存器有两类结构,一类是由多个钟控D锁存器组成的,另一类是由多个钟控D触发器组成的。数据寄存器的数据的输入和输出都是并行的。移位寄存器的结构也是由多个触发器级联的,其数据不仅可以存储,还可以左移或右移。移位寄存器的数据的输入和输出都有串行和并行之分,数据的动作受公共时钟信号的控制,也就是同步工作的。 4位双向移位寄存器74LS194A为TTL双极型数字集成逻辑电路,外形为双列直插,它具有清除、左移、右移、并行送数和保持等多种功能,是一种功能比较全的中规模移位寄存器,图6-1是引脚排列图,逻辑符号如图6-2所示,74LS194A的功能表见表6-1。

《数字电路与系统设计》实验指导书 2 移位寄存器的最直接应用是数据的串/并转换,图6-3和图6-4就是简单的实例。在图6-3中M1M0=01,表示数据可以右移,首先清零端输入一个负脉冲,使Q1Q2Q3Q4=0,在单脉冲CP的作用下,右移输入端D R依次串入数据,4个CP后就可在4个输出端Q1Q2Q3Q4得到并行数据。在图6-4中首先M1M0=11,在单脉冲CP的作用下,4位数据并行输入到移存器,然后使M1M0=10,表示数据可以左移,左移输入端D L=1时,在单脉冲CP的作用下,数据依次从Q1端输出,空缺位被1(D L)填补。4个CP 后,原4位并入的数据全被移出,这时候Q1Q2Q3Q4=1111。

计数器和移位寄存器设计仿真实验报告.

实验四典型时序电路的功能测试与综合仿真报告 15291204张智博一.74LS290构成的24位计数器 方法:第一片74290的Q3与第二片的INB相连,R01,R02相连,INA,R91,R92悬空构成24位计数器。50Hz,5v方波电压源提供时钟信号,用白炽灯显示输出信号。 实验电路: 实验现象:

输出由000000变为000001,000010,000011,000100,001000,001001,001010,001011,001100,010001,010000,010010,010011,010100,011000,011001,011010,011011,011100,100000,100001,100010,100011,100100,最终又回到000000,实现一次进位。 二.74LS161构成的24位计数器 方法:运用多次置零法 用两片74LS161构成了24位计数器,两片计数器的时钟信号都由方波电压源提供,第一片芯片的Q3和第二片芯片的Q0通过与非门,构成两个74LS161的LOAD信号,第一片的CO接第二片的ENT,其他ENT和ENP接Vcc(5v)。输出接白炽灯。 电路图: 实验现象:以下为1—24的计数过程

三.74LS194构成的8位双向移位寄存器 方法:通过两片194级联,控制MA,MB的值,来控制左右移动 实验电路由两片74LS194芯片构成。两个Ma接在一起,两个Mb接在一起,第一片的Dr,第二片的Dl,分别通过开关接到Vcc(5v)上。第一片的Q3接到第二片的Dr,第二片的Q0接到第一片的Dl。8个输出端分别接白炽灯。 实验电路:

练习(算术运算及逻辑移位指令3题目)

练习 算术运算与逻辑移位指令 1、若AX=0ABCDH,BX=7F8FH,CF=1。分别执行0886 CPU指令 (1)ADD AX,BX (2)ADC AX,BX (3)SBB AX,BX (3)NEG AX (5)AND AX,BX (6)OR AX,BX (7)XOR AX,BX (8)IMUL BL 后,AX寄存器中的内容,并指出标志寄存器SF、ZF、AF、PF、CF及OF的状态。 2、若CX=6700H,DX=78FFH,CF=1,求分别执行指令 (1)ADD CX,DX (2)ADC CX,DX (3)SUB CX,DX (4)SBB CX,DX (5)AND CX,DX (6)OR CX,DX (7)XOR CX,DX 后,CX和DX中的内容。并指出标志寄存器SF、ZF、AF、PF、CF和OF的状态。 3、X,Y分别为下列各组数,当它们分别进行加、减、AND、OR、XOR运算后,其标志位,SF、OF、CF、PF、ZF的状态如何? (1)X=21H;Y=43H (2)X=9AH;Y=0BCH (3)X=48H;Y=8DH (2)X=54H;Y=54H 4、若AX=98ABH,BX=A8BCH,求执行指令ADD AX,BX后,AX与BX中的内容,并指出SF、ZF、AF、PF、CF和OF的状态。 5、针对下列各条指令执行后的结果,填入目的操作数的值及标志位的状态。 6、若AX=FFF8H,BX=FFFAH,求执行IMUL BX后,DX与AX中的内容,并指出标

志位OF与CF的状态。 7、若AX=FFFEH,BX=FFFDH,求执行指令IMUL BX后,DX与AX中的内容。指出标志位OF与CF的状态。 8、设AL=85H,BL=2AH,均为带符号数,求指令 IMUL BL的执行结果。 9、若AL=78H,BL=87H, (1)求执行指令 ADD AL,BL DAA 之后,AL=?标志位AF=?CF=?并说明BCD码调整情况。 (2)若执行指令SUB AL,BL与DAS后,情况又如何? 10、若AL=75H,BL=48, (1)求执行指令 ADD AL,BL DAA 之后,AL=?标志位AF=?CF=?并说明BCD码调整情况。 (2)若执行指令SUB AL,BL与DAS后,情况又如何? 11、若有一个4字节数,放在寄存器BX间址的内存中(低地址对应低字节),要求这个4字节整数整个左移一位如何实现?右移一位又如何实现? 12、若有一个四字节数,放在寄存器DX与AX中(DX放高16位),要求这个四字节数整个左移一位如何实现?右移一位又如何实现? 13、分别编写一程序使 (1)AX寄存器高3位清0; (2)BX寄存器高3位置1; (3)CX寄存器高4位取反; (4)DX寄存器高3位不变,其余位清0。

8位移位寄存器的电路设计与版图实现

8位移位寄存器的电路设计与版图实现 摘要 电子设计自动化,缩写为EDA,主要是以计算机为主要工具,而Tanner EDA则是一种在计算机windows平台上完成集成电路设计的一种软件,基本包括S-Edit,T-Spice,W-Edit,L-Edit与LVS等子软件,其S-Edit以及L-Edit为常用软件,前者主要实现电路设计,后者主要针对的是已知电路的版图绘制,而T-Spice主要可实现电路图及版图的仿真,可以用Tanner EDA实现电路的设计布局以及版图实现等一系列完整过程。本文用Tanner EDA工具主要设计的是8位移位寄存器,移位寄存器主要是用来实现数据的并行和串行之间的转换以及对数据进行运算或专业处理的工具,主要结构构成是触发器,触发器是具有储存功能的,可以用来储存多进制代码,一般N 位寄存器就是由N个触发器构成,移位寄存器工作原理主要是数据在其脉冲的作用下实现左移或者右移的效果,输入输出的方式表现为串行及并行自由组合,本设计就是在Tanner EDA的软件平台上进行对8位移位寄存器的电路设计仿真,再根据电路图在专门的L-Edit 平台上完成此电路的版图实现,直至完成的结果和预期结果保持一致。 关键词:Tanner EDA;L-Edit;移位寄存器,S-Edit

8 bits shift register circuit design and layout Abstract Electronic design automation,referred to as EDA,it is based on computers as the main tool,and Tanner EDA is a kind of software that complete the integrated circuit design on Windows platforms.Its Sub-Softwares include S-Edit,T-Spice,W-Edit,L-Edit and LVS and so on.S-Edit and L-Edit are commonly used software,S-Edit is primarily designed to achieve circuit,the latter is aimed primarily known circuit layout drawing,T-Spice can achieve schematic and layout simulation.We can achieve layout of the circuit design and a series of complete process layout used Tanner EDA tools.In this paper, Tanner EDA tools are mainly designed an 8-bit shift register.The shift register is mainly used for data conversion between parallel and serial, and the data processing tool operation or professional,its main structure is the trigger composition,flip-flop is a storage function,it can be used to store more hexadecimal code,In general N-bits register is composed of N trigger.Working principle of the shift register data under the action of the pulse, mainly the effect of the shift to the left or right,input and output of the way of serial and parallel free combination.This design is in Tanner on the EDA software platform to 8 bits shift register circuit design and simulation,then according to the circuit diagram on special L - Edit platform to complete the circuit layout implementation,until the finish is consistent with the results and expected results. Keywords:Tanner EDA;L-Edit;Shift register,S-Edit

移位寄存器及其应用

移位寄存器及其应用 一、实验目的 1、掌握移位寄存器CC40194的逻辑功能与使用方法, 2、了解移位寄存器的使用—实现数据的串行,并行转换和构成环形计数器; 3、进一步掌握用示波器观察多个波形时序关系的方法。 二、实验仪器及材料 1. 数电实验箱、 双踪示波器、 数字万用表。 2. 元件:CC40194两片、 74HC125两片, 74LS20一片。 三、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下 依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左右移的控制信号便可实现双向移位要求。根据寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图所示: 2、移位寄存器应用很广,可构成移位寄存器型计数器、顺序脉冲发生器和串行累加器;可用作数 据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如下图所示

(2)实现数据串、并转换 1、串行/并行转换器串行/并行转换是指串行输入的数据,经过转换电路之后变成并行输出。下面是用两片74LS194构成的七位串行/并行转换电路。 2、并行/串行转换是指并行输入的数据,经过转换电路之后变成串行输出。对于中规模的集成移位寄存器,其位数往往以4 位居多,当所需要的位数多于4位时,可以把几片集成移位寄存器用级连的方法来扩展位数。 四、实验内容 1、按照以下实验电路图测试移位寄存器CC40194的逻辑功能。Q0~Q3接LED 显示,CP 接手动单次脉冲或1Hz 正方波,M1、M0接数据开关 实验得到的逻辑功能表为 2、参照上图组装移位寄存器。Q0~Q3接LED 显示,选单次手动脉冲或1Hz 正方波作为CP 输入,观察数据的循环过程。将CP 改为1kHz 的正方波,用示波器观察并记录CP 、Q0~Q3的波形。 电路图如下 输入为1kHz 及输出端Q 0、Q 1 Q 2 Q 3波形的波形图: (3)设计下图所示的串行移位器,然后组装、测试电路的逻辑功能,三态门74HC125的输

EDA课程设计——移位寄存器的设计与实现

河南科技大学 课程设计说明书 课程名称 EDA技术与应用 题目移位寄存器的设计与实现 学院 班级 学生姓名 指导教师 日期

EDA技术课程设计任务书 班级:姓名:学号: 设计题目:移位寄存器的设计与实现 一、设计目的 进一步巩固理论知识,培养所学理论知识在实际中的应用能力;掌握EDA设计的一般方法;熟悉一种EDA软件,掌握一般EDA系统的调试方法;利用EDA软件设计一个电子技术综合问题,培养VHDL编程、书写技术报告的能力。为以后进行工程实际问题的研究打下设计基础。 二、设计任务 根据计算机组成原理中移位寄存器的相关知识,利用VHDL语言设计了三种不同的寄存器:双向移位寄存器、串入串出(SISO)移位寄存器、串入并出(SIPO)移位寄存器。 三、设计要求 (1)通过对相应文献的收集、分析以及总结,给出相应课题的背景、意义及现状研究分析。 (2)通过课题设计,掌握计算机组成原理的分析方法和设计方法。 (3)学习按要求编写课程设计报告书,能正确阐述设计和实验结果。 (4)学生应抱着严谨认真的态度积极投入到课程设计过程中,认真查阅相应文献以及实现,给出个人分析、设计以及实现。 四、设计时间安排 查找相关资料(1天)、设计并绘制系统原理图(2天)、编写VHDL程序(2天)、调试(2天)、编写设计报告(2天)和答辩(1天)。 五、主要参考文献 [1] 江国强编著. EDA技术与实用(第三版). 北京:电子工业出版社,2011. [2] 曹昕燕,周凤臣.EDA技术实验与课程设计.北京:清华大学出版社,2006.5 [3] 阎石主编.数字电子技术基础.北京:高等教育出版社,2003. [4] Mark Zwolinski. Digital System Design with VHDL.北京:电子工业出版社,2008 [5] Alan B. Marcovitz Introduction to logic Design.北京:电子工业出版社,2003 指导教师签字:年月日

实验六移位寄存器的设计

实验六移位寄存器的设计 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验预习要求 1、复习有关寄存器及串行、并行转换器有关内容。 2、查阅CC40194、CC4011及CC4068 逻辑线路。熟悉其逻辑功能及引脚排列。 3、在对CC40194进行送数后,若要使输出端改成另外的数码,是否一定要使寄存器清零? 4、使寄存器清零,除采用R C输入低电平外,可否采用右移或左移的方法?可否使用并行送数法?若可行,如何进行操作? 5、若进行循环左移,图6-4接线应如何改接? 6、画出用两片CC40194构成的七位左移串 /并行转换器线路。 7、画出用两片CC40194构成的七位左移并 /串行转换器线路。 三、实验设备及器件 1、+5V直流电源 2、单次脉冲源 3、逻辑电平开关 4、逻辑电平显示器 5、CC40194×2(74LS194)CC4011(74LS00) CC4068(74LS30) 四、设计方法与参考资料 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图6-1所示。 其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输 C为直接无条件清零端; 入端,S L为左移串行输入端;S1、S0为操作模式控制端;R

实验十七、移位寄存器74164的逻辑功能测 试

实验十七、移位寄存器74164的逻辑功能测 试 一、实验目的 1、掌握中规模8位移位寄存器逻辑功能。 2、认识74LS164及其引脚封装。 二、实验预习要求 1、复习有关寄存器的内容。 2、查阅74LS164及逻辑电路,熟悉其逻辑功能及引脚排 列。 三、实验设备 1、+5V直流电源 2、单次脉冲源 3、逻辑电平开关 4、DM74LS164 四、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中锁存的代码能够在移位脉冲的作用下一次左移和右移。既能左移又能右移称为双向移位寄存器,只需要改变左、右移的控制信号可实现双向移位要求。根据移位寄存器取存信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的8位移位寄存器,型号可为74LS164,其逻辑符号及引脚排列如图所示。 其中A、B为串行输入端;

CLR为异步清零端; QH—QA为输入端; CLK为移位脉冲输入端; 74164是一种串行输入、并行输出的器件,时钟高电平有效,没有时钟使能端,该器件用低电平复位 图1 74LS164的逻辑符号及引脚功能表其中QAO、QBO、QHO为在暂稳态输入条件建立之前QA、QB和QH相应的电平;QAN、QGN为在最近的时钟上升沿转换前QA或QG的电平,表示移一位。 移位寄存器应用很广,可构成移位寄存器型计数器;属虚脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换位并行数据,或把并行数据转换位串行数据等。 五、实验内容 1、测试74LS164的逻辑功能 按图所示接线,A、B、CLK分别接至逻辑电平显示输入端。QA—QH分别接至逻辑电平显示输出端。14脚接+5V电源、7脚接地。

移位寄存器工作方式

一,串行口控制寄存器SCON 它用于定义串行口的工作方式及实施接收和发送控制。字节地址为98H,其各位定义如下表: SM0、SM1:串行口工作方式选择位,其定义如下: 其中fosc为晶振频率 SM2:多机通讯控制位。在方式0时,SM2一定要等于0。在方式1中,当(SM2)=1则只有接收到有效停止位时,RI才置1。在方式2或方式3当(SM2)=1且接收到的第九位数据RB8=0时,RI才置1。 REN:接收允许控制位。由软件置位以允许接收,又由软件清0来禁止接收。 TB8: 是要发送数据的第9位。在方式2或方式3中,要发送的第9位数据,根据需要由软件置1或清0。例如,可约定作为奇偶校验位,或在多机通讯中作为区别地址帧或数据帧的标志位。 RB8:接收到的数据的第9位。在方式0中不使用RB8。在方式1中,若(SM2)=0,RB8为接收到的停止位。在方式2或方式3中,RB8为接收到的第9位数据。 TI:发送中断标志。在方式0中,第8位发送结束时,由硬件置位。在其它方式的发送停止位前,由硬件置位。TI置位既表示一帧信息发送结束,同时也是申请中断,可根据需要,用软件查询的方法获得数据已发送完毕的信息,或用中断的方式来发送下一个数据。TI必须用软件清0。 RI:接收中断标志位。在方式0,当接收完第8位数据后,由硬件置位。在其它方式中,在接收到停止位的中间时刻由硬件置位(例外情况见于SM2的说

明)。RI置位表示一帧数据接收完毕,可用查询的方法获知或者用中断的方法获知。RI也必须用软件清0。 二,串行口的工作方式 8051单片机的全双工串行口可编程为4种工作方式,现分述如下: 1,方式0为移位寄存器输入/输出方式。可外接移位寄存器以扩展I/O口,也可以外接同步输入/输出设备。8位串行数据者是从RXD输入或输出,TXD用来输出同步脉冲。 (1)输出串行数据从RXD引脚输出,TXD引脚输出移位脉冲。CPU将数据写入发送寄存器时,立即启动发送,将8位数据以fos/12的固定波特率从RXD输出,低位在前,高位在后。发送完一帧数据后,发送中断标志TI由硬件置位。 (2)输入当串行口以方式0接收时,先置位允许接收控制位REN。此时,RXD 为串行数据输入端,TXD仍为同步脉冲移位输出端。当(RI)=0和(REN)=1同时满足时,开始接收。当接收到第8位数据时,将数据移入接收寄存器,并由硬件置位RI。 2,方式1为波特率可变的10位异步通讯接口方式。发送或接收一帧信息,包括1个起始位0,8个数据位和1个停止位1。 (1)输出当CPU执行一条指令将数据写入发送缓冲SBUF时,就启动发送。串行数据从TXD引脚输出,发送完一帧数据后,就由硬件置位TI。 (2)输入在(REN)=1时,串行口采样RXD引脚,当采样到1至0的跳变时,确认是开始位0,就开始接收一帧数据。只有当(RI)=0且停止位为1或者(SM2)=0时,停止位才进入RB8,8位数据才能进入接收寄存器,并由硬件置位中断标志RI;否则信息丢失。所以在方式1接收时,应先用软件清零RI和SM2标志。

移位与循环移位指令--习题

课堂练习: 22.设AX=3762H,CL=5,执行“SHR AX,CL”后,AX=()。 A.0376H B.01BBH C.01BB D.0376 28.执行“DIV BX”指令后,()寄存器中存放商。 A.AL B.AH C.AX D.DX 24.若移位指令的移位位数大于1时,其移位位数必须放在中。 25.如果AL=85H,CL=4,执行“SAR AL,CL”时,AL= ,CF= 。 6.设BX=8234H,请说明下列两条指令的区别,执行下列各指令后BX中的内容是什么? SHR BX,1 SAR BX,1 6.现有程序段如下: MOV BL,AL MOV CL,4 SHR BL,CL MOV A,BL AND AL,0FH MOV B,AL 请回答:(1)该程序段完成的功能是什么? (2)如果AL的初值为56H,则A= ,B= 。 8.现有程序段如下: MOV AX,M MOV DX,N SHR DX,1 RCR AX,1 请回答:(1)该程序段完成的功能是什么? (2)若M=1234H,N=5678H,程序运行后DX= ,AX= 。

9.现有程序段如下: XOR AX,AX MOV AX,6342H MOV CX,0404H ROL AH,CL XCHG CH,CL ROR AL,CL 请回答:(1)该程序段执行后AX= 。 (2)CF= 。 11.现有程序段如下: MOV CX,16 MOV BX,0 MOV DX,1 L:MOV AX,9AB8H AND AX,DX JZ N INC BX N:SHL DX,1 LOOP L MOV M,BX 请回答:(1)该程序段完成的功能是什么? (2)该程序段执行完后(M)= 。 14.现有程序段如下: MOV AL,0 MOV BL,1 MOV CX,10 L:ADD AL,BL

(整理)实验-寄存器.

实验十一移位寄存器及其应用 一、实验目的: 1、熟悉中规模4位双向移位寄存器的逻辑功能并掌握其使用方法; 2、熟悉移位寄存器的应用典例一——构成串行累加器和环形计数器。 二、实验原理: 1、移位寄存器是一种具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的移位寄存器称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位。根据存取信息的方式不同移位寄存器可分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为74LS194或CC40194,两者功能相同, S L为左移串行输入端;S1、S0为操作模式控制端;CR为异步清零端;CP为时钟脉冲输入端。 74LS194有5种不同操作模式:并行送数寄存,右移(方向由Q3至Q0),左移(方向由Q0至Q3),保持及清零。S1、S0和CR 端的控制作用如表11-1所示。表11-1

2、移位寄存器的应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验主要研究移位寄存器用作环形计数器和串行累加器的线路连接及其原理。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图11-2所示,把输出端Q3和右移串行输入端S R相连接,设初始状态Q3Q2Q1Q0=1000,则在时钟脉冲的作用下Q3Q2Q1Q0将依次变为0100、0010、0001、1000-----,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图11-2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 (2)串行累加器 累加器是由移位寄存器和全加器组成的一种求和电路,它的功能是将本身寄存的数和另一个输入的数相加,并存放在累加器中。 图11-2 图11-3是由两个右向移位寄存器、一个全加器和一个进位触发器组成的串行累加器。 设开始时,被加数A=A N-1.....A O和加数B=B N-1......B O已分别存入N+1位累加数移位寄存器和加数移位寄存器。再设进位触发器D已被清零。 在第一个CP脉冲到来之前,全加器各输入、输出端的情况为:A N=A0,B N=B0,C N-1=0,S N=A0+B0+0=S0,C N=C0。 当第一个CP脉冲到来后,S0存入累加和移位寄存器的最高位,C0存入进位触发器D端,且两个移位寄存器中的内容都向右移动一位。全加器输出为S N=A1+B1+C0=S1,C N=C1。

实验七移位寄存器及其应用

实验七移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图7-1所示。 图7-1 CC40194的逻辑符号及引脚功能 其中D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串 C为直接无条件清零端;行输入端,S L为左移串行输入端;S1、S0为操作模式控制端;R CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0→Q3),左移(方向由Q3→Q0),保持及清零。 S1、S0和R C端的控制作用如表7-1。

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图7-2所示,把输出端Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表7-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图7-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。 图7-2 环形计数器 如果将输出Q O与左移串行输入端S L相连接,即可达左移循环移位。 (2)实现数据串、并行转换 ①串行/并行转换器 串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。 图7-3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。

最新实验6-移位寄存器功能测试及应用-(实验报告要求)

实验六 移位寄存器功能测试及应用 --实验报告要求 一. 实验目的(0.5分) 1. 熟悉寄存器、移位寄存器的电路结构和工作原理。 2. 掌握中规模4位双向移位寄存器逻辑功能及使用方法。 3. 熟悉移位寄存器的应用。 二. 实验电路 D0、D1 、D2 、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;SR 为右移串行输入端,SL 为左移串行输入端;S1、S0 为操作模式控制端;R C 为直接无条件清零端;CP 为时钟脉冲输入端。 三 图2 CC40194/74LS194 逻辑功能测试 图1 CC40194/74LS194的逻辑符号及引脚功能 图3 环形计数器

四. 实验原理(0.5分) 1.移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用。 74LS194有5种不同操作模式:即并行送数寄存,右移(方向由Q0-->Q3),左移(方向由Q3→Q0),保持及清零。 2.移位寄存器应用很广,可构成移位寄存器型计数器:顺序脉冲发生器;串行累加器;可用数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环行计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位。 (2)实现数据、并行转换器 a)串行∕并行转换器 串行∕并行转换器是指串行输入的数码,经转换电路之后变换成并行输出。 b)并行∕串行转换器 并行∕串行转换器是指并行输入的数码经转换电路之后,换成串行输出。 五. 实验内容与步骤(共1分) 1. 2.测试74LS194的逻辑功能(0.5分) (1)在实验箱上选取一个16P插座,按定位标记插好74LS194集成块。 (2)将实验挂箱上+5V直流电源接40194的16脚,地接8脚。S1、S0、SL、SR、D0、D1、D2、D3分别接至逻辑电平开关的输出插口;Q0、Q1、Q2、Q3接至发光二极管。CP端接单次脉冲源。 (3)改变不同的输入状态,逐个送入单次脉冲,观察寄存器输出状态,记录之。 a)清除:令=0,其它输入均为任意态,这时寄存器输出Q0、 Q1、 Q2 、Q3应均为0。清除后,至=1。 b)送数:令=S1=S0=1 ,送入任意4位二进制数,如D0、D1、D2、D3=1010,加CP脉冲,观察CP=0、CP由1→0、CP=1三种情况下寄存器输出状态的变化,观察寄存输出状态变化是否发生在CP脉冲的上升沿。 (c)右移:清零后,令=1, S1=0 S0=1,由右移输入端S R送入二进制数码如0100,由CP端连续加4个脉冲,观察输出情况,记录之。 (d)左移:先清零或予至,再令=1 S1=1,S0=0,由左移输入端S L送入二进制数码

s7-200 传送及移位指令(MOV SHL)

案例7相关背景知识 关于:数据处理指令 一、传送类指令 传送类指令用于在各个编程元件之间进行数据传送。根据每次传送数据的数量,可分为单个传送指令和块传送指令。 1.单个传送指令MOVB,BIR,BIW,MOVW,MOVD,MOVR 单个传送指令每次传送l个数据,传送数据的类型分为字节传送、字传送、双字传送和实数传送。 (1)字节传送指令MOVB,BIR,BlW 字节传送指令可分为周期性字节传送指令和立即字节传送指令。 ①周期性字节传送指令MOVB。 在梯形图中,周期性字节传送指令以功能框的形式编程,指令名称为MOV_B。当允 许输入EN有效时,将一个无符号的单字节数据IN传送到0UT中。 影响允许输出EN0正常工作的出错条件为:SM4.3(运行时问),0006(问接寻址)。 在语句表中,周期性字节传送指令MOVB的指令格式为:MOVB IN,OUT。IN和0UT的寻址范围。 操作数类型寻址范围 IN BYTE VB,IB,QB,MB,SB,SMB,LB,AC,*VD,*AC,*LD和常数 OUT BYTE VB,IB,QB,MB,SB,SMB,LB,AC,*VD,*AC,*LD ②立即字节传送指令BIR,BIW。 立即读字节传送指令BIR:当允许输入EN有效时,BIR指令立即读取(不考 虑扫描周期)当前输入继电器区中由IN指定的字节,并传送到OUT。在梯形图 中,立即读字节传送指令以功能框的形式编程,指令名称为:MOV_BIR。 当允许输入EN有效时,将1个无符号的单字节数据IN传送到0UT中。 在语句表中,立即读字节传送指令BIR的指令格式为: BIR IN,OUT。 IN和0UT的寻址范围如下表所示. 操作数类型寻址范围 IN BYTE IB OUT BYTE VB,IB,QB,MB,SB,SMB,LB,AC,。VD,8AC,。LD (2)字传送指令MOVW 字传送指令MOVW将1个字长的有符号整数数据IN传送到OUT。在梯形图中,字传送指令以功能框的形式编程,当允许输入EN有效时,将1个无符号的单字长数据IN传送到0UT中。 影响允许输出EN0正常工作的出错条件为:SM4.3(运行时间),0006(间接寻 址)。在语句表中,字传送指令MOVW的指令格式为MOVW IN,OUT。IN和0UT的 寻址范围. 操作数类型寻址范围 IN WORD VW,IW,QW,MW,SW,SMW,LW,T,C,AC,*VD,*AC,*LD和常数 OUT WORD VW,IW,QW,MW,SW,SMW,LW,T,C,AC,*VD,*AC,*LD (3)双字传送指令MOVD 双字传送指令MOVD将1个双字长的有符号整数数据IN传送到0UT。 在梯形图中,双字传送指令以功能框的形式编程,指令名称为:MOV_DW。 当允许输入EN有效时,将1个有符号的双字长数据IN传送到0UT中。 影响允许输出EN0正常工作的出错条件为SM4.3(运行时间),0006(问接 寻址)。在语句表中,双字传送指令MOVD的指令格式为:MOVD IN,OUT。 IN和0UT的寻址范围如下表所示。 操作数类型寻址范围 IN DWORD VD,ID,QD,MD,SMD,LD,AC,HC,*VD,*AC,*LD和常数 OUT DWORD VD,ID,QD,MD,SMD,LD,AC,*VD,*AC,*LD (4)实数传送指令MOVR

电子线路基础数字电路实验6 移位寄存器

实验六移位寄存器 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、实验原理 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图9—1所示。 图9—1 CC40194的逻辑符号及引脚功能 其中D0、D1、D2、D3为并行输入端; Q0、Q1、Q2、Q3为并行输出端;SR为右移串行输入端,SL为左移串行输入端;S1、S0为操作模式控制端;C R为直接 无条件清零端;CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0~Q3),左移(方向由Q3~Q0),保持及清零。 S1、S0和C R端的控制作用如表9—l。 表9—l

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。(1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图9—2所示,把输出端Q3和右移串行输入端S R相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表9—2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图9—2电路可以由各个输出端输出在时间上有先后顺序的脉冲。因此也可作为顺序脉冲发生器。 图9—2环形计数器表9—2 如果将输出作与左移串行输入临,相连接,即可达左移循环移位。 (2)实现数据串、并行转换 ①串行/并行转换器 串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。图9—3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位申/并行数据转换电路。 图9—3 七位串行/并行转换器 电路中S0端接高电平1,S1受Q7控制,二片寄存器连接成串行输入右移工作模式。Q7是转换结束标志。当Q7=1时,S1为0,使之成为S1S0=01的串入右移工作方式,当Q7=0时,S1=1, S1S0=10则串行送数结束,标志着串行输入的数据已转换成并行输出了。’ 串行/并行转换的具体过程如下: 转换前,C R端加低电平,使1、2两片寄存器的内容清0,此时S1 S0=11,

西门子plc移位寄存器指令

西门子plc移位寄存器指令 移位寄存器指令SHRB是将DATA数值移入移位寄存器。S_BIT指定移位寄存器的最低位。N指定移位寄存器的长度和移位方向(移位加= N,移位减= -N)。移位寄存器的最大长度是64位的,可以正也可以负。我们要注意的是SHRB指令移出的每个位是被放置在溢出内存位(SM1.1)中的。 下面便以以下的程序来讲解指令的使用,用I0.2的上升沿来执行移位寄存器指令,那么就是一个扫描周期移一位的,指令中V100.0是移位寄存器的最低位,I0.3里面存的是0或1的数值,指令指定是移位加的,移位寄存器的长度是4。我们结合下面的时序图和移位的图来看,若V100为0000 0101,因为移位寄存器的长度是4,那么只有0101,当I0.3为1时,执行第一次移位,把1移到移位寄存器的最低位,把移出的位的值0放置到SM1.1中,那么SM1.1为0,当I0.3为0时,执行第二次移位,把0移到移位寄存器的最低位,把移出的位的值1放置到SM1.1中,那么SM1.1为1。 在顺序控制或步进控制中,应用移位寄存器编程是很方便的,移位寄存器指令如图所示。 1)移位寄存器有3个数据输入端: DATA:移位寄存器的数据输入端,数据类型为BOOL(位)。 S_BIT:组成移位寄存器的最低位,数据类型为BOOL(位)。 N:移位寄存器的长度和移位方向,-64N64,当N 》0时为正向移位(从移位寄存器的最低位移入,由最高位移出),当N 《0时为反向移位(从移位寄存器的最高位移入,由最低位移出)。 2)移位寄存器的特点: 移位寄存器的数据类型无字节型、字型、双字型之分,移位寄存器的长度N由程序指定。移位寄存器的组成: 最低位为:S_BIT;