低功耗的可重构数据Cache设计

0引言

近年来,嵌入式系统在便携设备上得到广泛应用。对于大多数以电池作为电源的移动设备,随着嵌入式系统计算性能的不断提高,功耗也逐渐成为设计者考虑的重点。在嵌入式处理器中,存储器已经成为最大的组成部分,也成为最主要的功耗来源。例如StrongARM 中的Cache 和存储器系统占芯片面积的60%,功耗的43%。而且随着嵌入式处理器设计的发展,存储器所占的比重也有不断提高的趋势。因此,对Cache 的优化设计越来越受到研究者的关注。

除了在逻辑设计级有许多技术可以用来节省Cache 功耗外,在体系结构级,也有很多针对Cache 功耗的设计,主要可以分为一下两类:一类是利用不同的程序以及同一程序的不同运行阶段其空间与时间局部性不同的特点,动态的调整Ca-che 的容量和关联度,以适应不同程序、如流媒体应用的需要,降低Cache 的功耗;另一类则利用程序的高频值局部性,对经常出现的数值进行压缩存储,以减少Cache 访问的功耗。程序运行中对数据访问的空间局部性和时间局部性原理是Ca-che 技术产生和发展的前提。目前的低功耗多媒体/嵌入式处理器的研究中,大部分都基于数据的空间和时间局部性对Ca-che 进行改进,如过滤Cache ,标量访问优化等。Cache 分区就

是其中一类经常使用的技术。例如D.H.Albonesi 提出的根据Cache 资源能够配置相联度的Cache 结构,是一种垂直方向上的Cache 分区模式。K.Ghose 和M.B.Kamble 提出了水平方向上的Cache 分区模式:内存分区技术,将数据Cache 的数据分区垂直分为多个子分区subbank ,在相应的TAG 命中时只打开部分子分区读写数据,从而节省不必要的功耗开支。

R.Balasubaramonian 等人提出了一种可重构cache 体系结构[1]

。他们将Cache 分为4个子分区subarray ,每个子分区内部为4路组相联。通过选择激活不同的子分区个数以及子分区内不同的路数,可以重构出一系列不同容量和关联度的L1Ca-che ,未激活部分作为L2,在L1未命中时被激活以进行访问。根据程序运行的状态,可以动态的调整L1的容量和关联度,以取得性能与功耗之间的平衡。

除了数据的空间与时间局部性之外,J.Yang 和R.Gupta 等人对高频值局部性进行了研究[2]。他们发现在存储器访问中,少数高频率出现的数据值占据了分配给程序的很大一部分内存区域,高频率数据值在整个存储空间中的分布也比较均匀。对于同一个程序,在整个运行过程中其高频率数据值集保持着相当的稳定性。另一方面,不同的程序之间高频率数据值集的差异又较大。基于高频值局部性,J.Yang 和R.Gupta 提出一种低功耗的Cache 结构[3,4],在读写Cache 的过程中,对高

收稿日期:2006-03-26E-mail :binxiao@https://www.360docs.net/doc/0f2703023.html,

作者简介:肖斌(1982-),男,山东泰安人,硕士研究生,研究方向为嵌入式系统;方亮,男,硕士研究生;柴亦飞,男,硕士研究生;陈章龙,男,教授;涂时亮,男,教授。

低功耗的可重构数据Cache 设计

肖

斌,方亮,柴亦飞,陈章龙,涂时亮

(复旦大学计算机科学与工程系,上海200433)

摘

要:

在嵌入式处理器中,Cache 功耗所占的比重越来越大。提出了一种可重构的低功耗数据Cache ,能够利用程序运行过程中的空间和时间局部性以及高频数据值局部性来节省功耗。Mibench 和Mediabench 的仿真结果表明,对于多媒体应用为主的测试程序,采用基于高频值的可重构低功耗数据Cache 与普通Cache 相比,平均能量消耗降低34.45%,平均能量延迟乘积降低27.50%。

关键词:

可重构;高速缓存;高频数据值;低功耗设计;嵌入式系统中图法分类号:TP333文献标识码:A 文章编号:

1000-7024(2007)07-1508-03Low power reconfigurable data cache design

XIAO Bin,

FANG Liang,

CHAI Yi-fei,

CHEN Zhang-long,

TU Shi-liang

(Department of Computer Science and Technology,Fudan University,Shanghai 200433,China )

Abstract :Caches compose larger and larger proportion in the power consumption of embedded processors.A low-power reconfigurable data design based on locality and frequent value locality is investigated.Mibench and Mediabench simulation results indicate that,com-pared with the frequent-value reconfigurable data cache and the normal data cache,the average energy consumption decreases 34.45%,while the average energy delay production improves 27.50%.

Key words :reconfigurable;cache;frequent value;low power design;embedded system

2007年4月计算机工程与设计

Apr.2007

第28卷第7期Vol.28

No.7

Computer Engineering and Design

频率出现的数据值进行压缩存储,从而

减少Cache访问的功耗。本文提出了一

种基于高频数据值的可重构数据Cache,

将空间与时间局部性和高频数据值局部

性相结合。一方面,可以根据程序特性

动态调整Cache的容量和关联度;另一方

面,基于高频值局部性对数据压缩存储,

进一步降低功耗。

1基于高频数据值的可重构数据

Cache设计

数据的空间和时间局部性是当前内

存系统优化时经常要考虑的特性,但是

当前普遍存在的一个问题是传统内存结

构对数据局部性的优化无法最好的适应

每个应用程序,在执行多个程序时,由于

程序的内存要求和内存系统的实现之间

的不匹配,不可避免的会存在明显的性

能降低和功耗损失现象。如果采用可重构的Cache和相应的

重构算法,能够有效地提高内存系统的性能和功耗表现。而

另一方面,高频值局部性与数据的空间和时间局部性之间相

互独立,因而可以与可重构Cache设计相结合,在可重构Cache

利用高频值局部性对数据进行压缩存储,进一步降低功耗。在

实现中,我们将阶段性的监测Cache的活动(失效率和分支频

率),通过动态权衡命中延迟和失效延迟的容忍度来调整Cache

结构,在重构算法中我们加入功耗考虑,并且在Cache内部实

现中还考虑了对高频率数据局部性的优化,这些设计对上述

两种数据局部性都进行了处理,能够在对性能影响较小的情

况下取得很好的功耗节省。

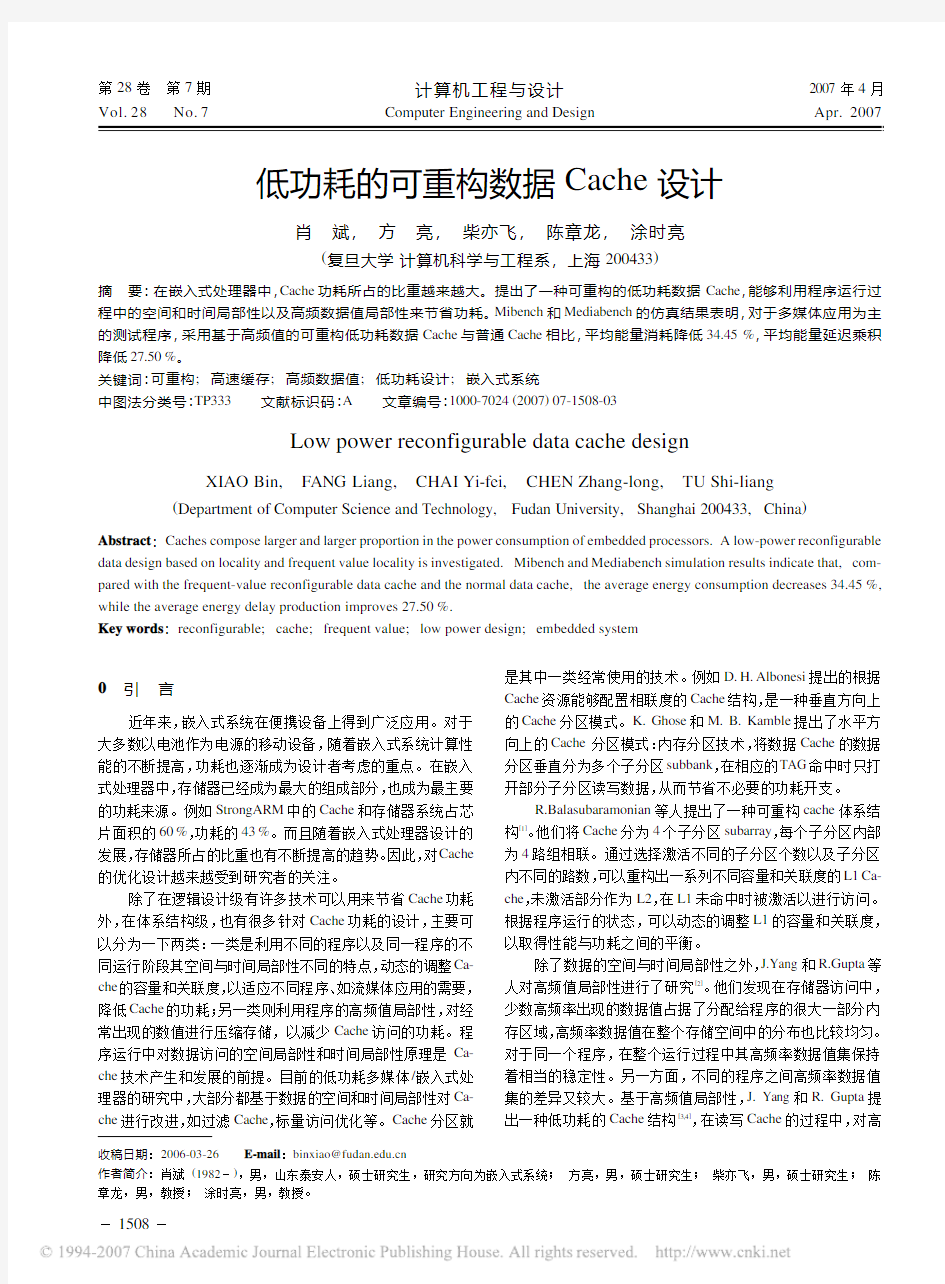

1.1系统设计

以32KB的数据Cache为例,Cache被分为4个8KB的

SRAM子分区。我们对基本的Cache结构做了一定的改动:增

加了Cache配置动态选择器(cache configuration dynamic selec-

tor,CCDS),使之支持动态配置;还增加了高频值查找器(fre-

quent value finder,FVF)和高频值解码器(frequent value decoder,

FVD),并将Cache内部的数据总线分为低位总线和高位总线

两部分。使之支持高频值的压缩存储。图1给出了整个Cache

的总体设计和功能模块,有两个地址位作为子分区选择位,在

每次访问中只有被选定子分区可以打开,其它子分区都将自

己的字选择线关闭,其预充电、读出放大器以及输出驱动线路

都将不再被激活,从而节省了其它分区的功耗。

每个子分区为4路组相联,每一路都由标示区(TAG ar-

rary)、低位数据区和高位数据区组成。假设采用n个数据的高

频值编码,n为2的幂,那么其中低位数据区存储log2n位高频

值编码或者非高频值数据的低log2n位,以及1位标示是否高

频值的有效位,共log2n+1位;高位数据区存储非高频值数据

的高32-log2n位。低位区和高位区的数据将被分别传送到低

位总线和高位总线上。图1的Subarray0详细给出了子分区

的结构和功能模块。一方面,可以有选择的打开某几路Cache

访问;另一方面,对高频值数据的读写只需访问标示区和低位

数据区,并将低位数据送到低位总线,而不需要访问高位数据

区和高位总线,因此可以节省功耗。

1.2运行机制

基于高频值的可重构Cache的运行过程可以分解为相对

独立的两类活动,一方面基于数据的时间和空间局部性,对

Cache的配置进行动态的重构;一方面基于高频值局部性,对

高频数据进行压缩存储。

1.2.1ache的动态重构

根据CCDS所选择的Cache配置,我们将整个Cache分成

了两级:La/Lb,这种分级方式同传统的L1/L2两级Cache结构

不同,La为由配置所选择的某几个ESubarray中的某几路Ca-

che,Lb是由La和其它数据区构成的(即La属于Lb的一部分)。

当进行读操作时,首先将访问La,当La命中时就直接返回。

只有在La访问失效时,才会将所有数据区打开。La Cache越

大,其命中率会越高,同时复杂度的增加也会带来访问时间的

提高,相应增加每次访问La的功耗,而命中率的提高却也可

能会节省整体的功耗损失;不同的应用程序,比如商业程序与

嵌入式多媒体程序,也会受到La配置变化产生不同影响。

为了获得在功耗和性能上最佳的La配置,我们设计了针

对多媒体应用的CCDS算法,通过历史信息来选择合适的La

配置变化。CCDS中包含了一定周期内Cache的访问信息,如

指令计数器、访存计数器、La失效计数器等。每次Cache访问,

都会更新CCDS的相应计数器。而CCDS会被周期性的激活,

进入重构阶段,判断Cache失效率是否超出预定范围,并据此

调整配置。其重构决策算法如下:

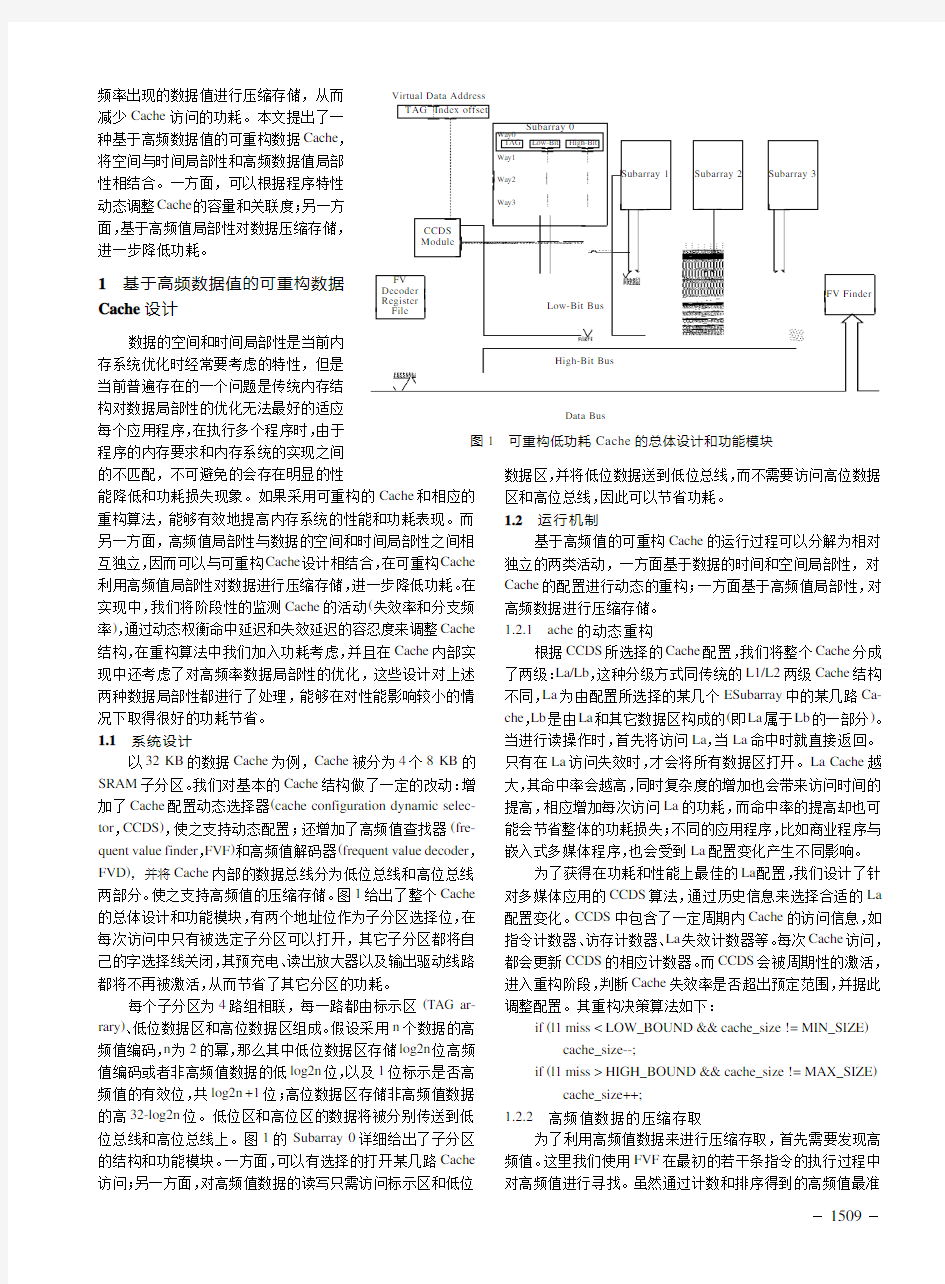

if(l1miss cache_size--; if(l1miss>HIGH_BOUND&&cache_size!=MAX_SIZE) cache_size++; 1.2.2高频值数据的压缩存取 为了利用高频值数据来进行压缩存取,首先需要发现高 频值。这里我们使用FVF在最初的若干条指令的执行过程中 对高频值进行寻找。虽然通过计数和排序得到的高频值最准 图1可重构低功耗Cache的总体设计和功能模块 High-Bit Bus Data Bus Way0 Virtual Data Address Subarray0 CCDS Module FV Decoder Register File Low-Bit Bus Subarray1Subarray2Subarray3 FV Finder TAG Low-Bit High-Bit Way1 Way2 Way3 TAG Index offset 确,但是开销大,实现复杂,因此采用数据交换机制来实现近似的排序算法,寻找使用频率最高的前32个高频值。数据被分为两个分区:高频率分区和次高频率分区,每个分区有32项数据,共有64项,每项都包含一个两位的计数器,初始为00。在监测阶段,如果访问数据同CAM 中的第i 项匹配,其计数器将增加1,当计数器饱和(即由11变为00)时,第i 项将同第i-1项交换Counter 和数据;如果没有找到匹配的项,则填入第64项,并将其Counter 置为00。当监测阶段结束时,高频率分区中的32项数据将依照CAM 编码成5位,并将这32项数据复制到FVD 的相应位置。 在找到32项高频值之后,对数据的存取也就依照是否为高频值分为两类:一类为高频值数据,存取时只需要访问低位区,占用5位的编码和1位有效位(置为1)共6位存储空间;另一类为非高频数据,访问时需要访问低位区,存放数据的前5位和1位有效位(置为0),以及高位区,存放数据的后32位。如图2所示。当进行写操作时,数据首先经过FVF 进行编码,如果为高频值,则将有效位至1,并将5位高频值编码和有效位送入低位总线,写入低位区;如果不是高频值,则将有效位至0,并将数据的低5位和有效位送入低位总线,写入低位区,然后将数据的高27位送入高位总线,写入高位区。当进行读操作时,首先读出低位区数据,送入低位总线,当有效位为1时,将低位区的5位编码送入FVD ,解码出32位高频值送入外部数据总线;当有效位为0时,再打开高位区,读出高位去数据送入高位总线,与低位总线上的低5位合并成32位数据,送入外部数据总线。 2 实验与数据分析 2.1 模拟方法 我们主要采用模拟的方法在性能和功耗上对可重构Ca-che 进行估算。我们使用Sim-Panalyzer 2.0[5] 和ARM 架构的 CPU 进行仿真模拟,并采用存储器模拟工具CACTI [6] 对Cache 子系统的功耗和延迟进行估算。Sim-Panalyzer 是目前常用的CPU 功耗模拟器,它建立在SimpleScalar [7] 的基础上,它对功耗的估算也是基于CACTI 。我们首先对Sim-Panalyzer 的Cache 部分的实现进行了修改,使之能够支持基于高频值的可重构数据Cache 。为了计算功耗,我们采用0.18um 工艺,200MHz 工作频率和1.8V 工作电压的配置进行模拟。我们修改了CAC-TI ,使之能够支持基于高频数据值的可重构数据Cache ,与传统Cache 向比较,对两者的功耗和延迟分别进行估算。我们设置了一个32KB 高频值的可重构数据Cache ,共有4个8KB 子分区,每个子分区为4路组相联,每路2KB ,并设置了8种 配置。对高频值采用5位高频值编码。另外,采用一个32KB 、4路组相联的普通数据Cache 进行对比。 2.2实验结果分析 我们针对嵌入式多媒体应用,选择了Mibench 和Media- bench 作为测试程序,进行比较测试。高频值命中率与程序特性及寻找的到高频数据值是否合适有关。当高频值命中率降低时,会使延迟增加,功耗增长。对于基于高频值的可重构Cache ,其高频值命中率如图3所示,平均命中率为42.4%。除adpcm encoder 的命中率低于10%之外,其它都在20%以上。 La 的命中率一方面与程序特性有关,另一方面与重构决策算法也有很大关系。当选择的La 大小正好可以容纳经常访问的数据集时,命中率上与传统Cache 相差无几,而功耗则大大降低。当La 不能容纳数据集时,数据就会频繁换出,极大的影响性能和功耗。此时就会引发重构操作。可重构Cache 与普通Cache 命中率比较如图4所示。第一列为可重构Cache 的La 命中率,第二列为整个可重构Cache 的命中率,第三列为普通Cache 的命中率。对于大部分测试程序而言,La 命中率与普通Cache 命中率相差很小,基本上都在1%以内。只有少数几个超过2%,如jpeg encoder 等。 我们采用正规化的延迟来衡量可重构Cache 在性能上的损失。延迟是由两方面的原因引起的,一方面是由于La Cache 失效引起的,另一方面是由于高频值失效引起的。各个程序的正规化延迟如图5所示,平均延迟为0.0995。其中最高的是dijkstra 程序,正规化延迟达到0.22,这主要与其高频值命中率较低,同时La 命中率与普通Cache 命中率相差较大有关。另外,我们采用正规化的能量消耗来衡量可重构Cache 在能耗上的节省。同样,能量消耗的减少也由两方面原因引起:一方面,当命中高频值时,只需要访问低位区,不需要访问高位区;另一方面La 通常只占整个Cache 的一部分,因而每次命中La 时只需要访问一部分Cache 。各个程序正规化的能量消耗 (下转第1707页) 图3高频值命中率 图4可重构Cache 与普通Cache 命中率比较 La Hit Rate New Hit Rate Original Hit Rate c r c d i j k s t r a f f t l a m e m a d q u i c k s o r t p a r t i c i a r i j i n d a e l r s y n t h s h a s u s a n t i f f 2b w t i f f 2r g b a t i f f m e d i a n a d p c m d e c o d e r a d p c m e n c o d e r e p i c d e c o d e r e p i c e n c o d e r g 721d e c o d e r g 721e n c o d e r j p e g d e c o d e r j p e g e n c o d e r m p e g 2d e c o d e r p e g w i t d e c r y p t i o n s t r i n g s e a r c h FV Hit Rate b i t c o u n t b l o w f i s h c r c d i j k s t r a f f t l a m e m a d q u i c k s o r t p a r t i c i a r i j i n d a e l r s y n t h s h a s u s a n t i f f 2b w t i f f 2r g b a t i f f m e d i a n a d p c m d e c o d e r a d p c m e n c o d e r e p i c d e c o d e r e p i c e n c o d e r g 721d e c o d e r g 721e n c o d e r j p e g d e c o d e r j p e g e n c o d e r m p e g 2d e c o d e r p e g w i t d e c r y p t i o n s t r i n g s e a r c h 70 %60%50%40%30%20%10%0% 图2对高频率数据进行优化的Cache 数据区 传统的Cache 数据区 高频率数据优化的Cache 数据区 通常需要一个周期的访问时间 通常需要一个周期的访问时间 通常需要多个周期的访问时间 (对于非高频率数据)高位区 低位区 32Log n 32-Log 与二维工程图相互转换实验(培养学生的投影能力);⑤部件的组装和运动仿真实验(培养学生的工程综合素质)。 4结束语 从现代工程设计模式出发,结合工程图学课程的发展趋 势,本文提出面向三维CAD 技术的工程图学教育的新模式,不仅可实现手工绘图向计算机绘图形式上的转变,而且将改变以画法几何为基本核心的传统教学观念,是更深层次的教学改革。这种改革更适应当前工程设计发展变化的需要,有利于培养学生的空间思维能力、图形表达能力和机械工程的素养,可以更好地适应科技、社会发展和知识经济时代人才培养的需要。 参考文献: [1] Ronald E Barr,Davor Juricic.The engineering design graphics (EDG )curriculum modernization project —A white paper sum-mary [C ].Austin Texas,USA:Proceedings of the NSF Sympo-sium on Modernization of the Engineering Design Graphics Cur- riculum,1999. [2]陈锦昌.工程制图课程由CG 主导式转向三维造型设计改革的思考[J ].工程图学学报,2002,23(5):76-80. [3]江洪,吉维峰.运用三维绘图软件SolidWorks 改革工程图学教学的实践[J ].工程图学学报,2004,25(1):109-113. [4]杨光,黄毓瑜,刘静华,等.突出设计和三维的观点改革工程制图图学教学[J ].工程图学学报,2002,23(2):150-156. [5]陈帜坤,尧燕.现代工程图学教育中的十大问题[C ].北京:机械工业出版社,2004.19-23. [6]王丹虹.机类本科生计算机造型和绘图技能培养[C ].北京:机械工业出版社,2004.163-165. [7]王飞.以三维设计为中心的图学课程改革[C ].北京:机械工业出版社,2004.266-270. [8]李世深.对工程图学教育若干热点问题的冷眼观察[C ].北京:机械工业出版社,2004.53-56. [9] 戴恒震.当代美国工程图学教育对我国图学教改的启示[C ].北京:机械工业出版社,2004.81-85. (上接第1510页) 如图5所示,平均为0.3445。我们可以看到,大部分程序的能量消耗减少了30%以上,最高的sha 将能耗减少了61%。但是,有少数几个程序能耗却增加了。这些程序的高频值命中率相对都不高,而且La 命中率与普通Cache 命中率相差较大。 为了评价Cache 的整体性能和功耗,我们采用正规化的能量延迟乘积。如图5所示,平均为0.2750。大部分程序的能量延迟乘积都在0.3以上,还有两个程序超过0.6。但是也有4个程序的能量延迟乘积小于0,意味着高频值的可重构Cache 对这些程序的优化并不成功,这主要是由于这些程序既不适合高频值优化,也不适合可重构优化造成的。 3结束语 本文提出了一种基于高频数据值的可重构数据Cache ,它 一方面对高频数据值进行压缩存取,另一方面动态的调整Ca-che 的大小,适应不同的程序,以降低功耗。这种Cache 能够适应大多数嵌入式多媒体应用,并且不需要修改处理器的整体架构和指令系统。使用Mibench 和Mediabench 测试程序进 行的仿真测试表明,对于多媒体应用为主的嵌入式应用程序,采用高频数据值的可重构数据Cache 与普通Cache 相比,平均能量消耗降低了34.45%,平均延迟增加仅9.95%,平均能量延迟乘积降低27.50%。 参考文献: [1] Rajeev Balasubramoniant,David Albonesit,Alper Buyuktosu-noglut,et al.Memory hierarchy reconfiguration for energy and performance in general-purpose processor architectures [C ].California,USA:33rd annual ACM/IEEE international sympo-sium on Microarchitecture,Monterey,2000.245-257.[2] Jun Yang,Rajiv Gupta.Frequent value locality and its applica-tions [J ].ACM Transactions on Embedded Computing Systems,2002,(1):79-105.[3] Jun Yang,Rajiv Gupta.Energy efficient frequent value data ca-che design [C ].Istanbul,Turkey:35th Annual IEEE/ACM Inter-national Symposium on Microarchitecture,2002.197-207.[4] Chuanjun Zhang,Jun Yang,Frank Vahid.Low static-power fre-quent-value data caches [C ].Paris,France:Design,Automation and Test in Europe Conference and Exhibition,2004.210-215.[5]Sim-Panalyzer [EB/OL ].https://www.360docs.net/doc/0f2703023.html,/~panaly-zer/. [6]CACTI [EB/OL ].https://www.360docs.net/doc/0f2703023.html,/wrl/people/jouppi/CACTI.html. [7]SimpleScalar [EB/OL ].https://www.360docs.net/doc/0f2703023.html,/. [8] Huang M,Renau J,Yoo SM,et al.L1Data cache decomposition for energy efficiency [C ].Huntington Beach,CA,USA:IEEE/ACM International Symposium on Low Power Electronics and Design,2001.10-15. 图5可重构Cache 与普通Cache 性能与功耗比较 Normalized Energy Redunction Normalized Delay Energy-Delay Product Reduction b e n c h m a r k b i t c o u n t b l o w f i s h c r c d i j k s t r a f f t l a m e m a d p a r t i c i a q u i c k s o r t r i j i n d a e l r s y n t h s h a s u s a n t i f f 2b w t i f f 2r g b a t i f f m e d i a n e p i c d e c o d e r e p i c e n c o d e r g 721d e c o d e r g 721e n c o d e r j p e g d e c o d e r j p e g e n c o d e r p e g w i t d e c r y p t i o n m p e g 2d e c o d e r a d p c m d e c o d e r a d p c m e n c o d e r 0.70.60.50.40.30.20.10-0.1-0.2-0.3 Caches实验 杨祯 15281139 实验目的 1.阅读分析附件模拟器代码 2.通过读懂代码加深了解cache的实现技术 3.结合书后习题1进行测试 4.通过实验设计了解参数(cache和block size等)和算法(LRU,FIFO 等)选择的优化配置与组合,需要定性和定量分析,可以用数字或图表等多种描述手段配合说明。 阅读分析模拟器代码 课后习题 stride=132下直接相连映射 1)实验分析 由题意得:cachesize=256B blockinbyte=4*4B Noofblock=256B/16B=16个组数位16 array[0]的块地址为0/4=0 映射到cache的块号为0%16=0 array[132]的块地址为132/4=33 映射到cache的块号为33%16=1 第一次访问cache中的0号块与1号块时,会发生强制性失效,之后因为调入了cache中,不会发生失效,所以 misscount=2 missrate=2/(2*10000)=1/10000 hitcount=19998 hitrate=9999/10000 实验验证 stride=131下直接相连映射 实验分析 由题意得:cachesize=256B blockinbyte=4*4B Noofblock=256B/16B=16个组数位16 array[0]的块地址为0/4=0 映射到cache的块号为0%16=0 array[131]的块地址为131/4=32 映射到cache的块号为32%16=0 第一次访问cache中的0号时,一定会发生强制性失效,次数为1;之后因为cache中块号为0的块不断地被替换写入,此时发生的是冲突失效,冲突失效次数为19999, 则发生的失效次数为19999+1=20000 所以 misscount=20000 missrate=20000/(2*10000)=1 超声波热量表 使 用 说 明 书 地址:唐山市路北区创业服务中心211号 电话: 传真: 网址: E-mail: 一、概述 超声波热量表是参考欧洲标准EN1434 和OIML-R75号国际规程开发设计的高性能、低功耗电子式测量仪表,用来测量和显示载热(冷)液体流经冷热交换系统释放(吸收)热量。 超声波热量表由流量传感器、微处理器和配对温度传感器组成。微处理器通过流量传感器得到流量信号,从测温电路得到出口和入口水温信号,根据标准热量计算公式计算出系统交换的能量。 用户可选用具有M-BUS通信接口或无线传输通信接口的RLB-C型超声波热量表,超声波热量表可和采集器、集中器以及配套软件组成远传抄表管理系统,管理部门可以随时抄取表中数据,方便对用户用热量的管控。 超声波热量表符合国家建设部颁布的CJ128-20XX《热量表》产品标准。M-BUS接口或无线接口通讯协议符合建设部CJ/T188-20XX《户用计量仪表数据传输技术条件》的要求;无线数传模块符合工信部无[20XX]423号《微功率(短距离)无线电设备的技术要求》。 二、性能特点 1、低电压报警。 2、自动数据纠错技术。 3、温度传感器断路和短路报警。 4、高清晰度宽温度型LCD显示。 5、流量分8段校准,准确度高。 6、超低功耗(静态功耗小于7uA)。 7、管段为直通一体结构采用锻压工艺制造而成。 8、测量机构无运动部件,永无磨损,计量精度不受使用周期影响。 9、具备光电接口,采用红外工具可以实现抄表。 10、安装极为方便,水平或垂直安装。 11、数据传输采用M-BUS或无线传输通信接口,通信距离远。 三、使用方法 1、超声波热量表一直循环显示: 累积热量:累积 XXX kW·h 累积流量:累积 XXX。XX m3 瞬时流量:瞬时 XXX。XXX m3/h 温度:入口 XX。X 出口 XX。X ℃ 温差:温差X。X K 累积工作时间:累积 XXX h 2、数据通讯(不带数据通讯的仪表无此功能) 用户可选用具有M-BUS通信接口或无线传输通信接口的RLB-C型超声波热量表,配合采集器、集中器、管理软件等可实现远程抄表。不同数据通讯接口的仪表选配相应采集器。使用前在上位机建立地址档案,表地址出厂时已设定(仪表ID号为12位数字编码),由热量表、集中器、采集器、上位机等组成的集中抄表系统组建完成后,管理部门就可以随时抄取表中数据。 计算机组成与体系结构课程设计报告题目:现代计算机cache技术的研究 学生姓名:谱 学号: 10204102 班级:10204102 指导教师:谌洪茂 2013 年1月6日 摘要 随着集成电路制造技术的持续发展,芯片的集成度和工作速度不断增加,功耗密度显著增大,功耗已经成为计算机系统设计中与性能同等重要的首要设计约束。在现代计算机系统中,处理器速度远远高于存储器速度,Cache作为处理器与主存之间的重要桥梁,在计算机系统的性能优化中发挥着重要作用,但Cache也占据着处理器的大部分能耗。处理器及其Cache存储器是整个计算机系统能耗的主要来源,降低其能耗对于优化计算机系统,特别是嵌入式系统,有着重要的意义。本文主要研究体系结构级的低能耗技术,利用优化Cache结构和动态电压缩放两种技术来实现处理器及其Cache的低能耗。本文首先详细地分析了低能耗Cache技术的研究现状,将该技术总结为基于模块分割的方法、基于路预测的方法、添加一级小Cache的方法、优化标识比较的方法和动态可重构Cache的方法等五大类,并在此基础上,提出了带有效位预判的部分标识比较Cache、带有效位判别的分离比较Cache、基于程序段的可重构Cache等三种Cache结构。然后从不同的实现层面分析比较了现有的电压缩放技术及其缩放算法,提出了一种基于程序段的动态电压缩放算法。最后结合可重构Cache和动态电压缩放技术,提出了一种基于程序段的可重构Cache及处理器电压自适应算法。本文通过仿真实验证明了上述几种方法的有效性。本文所取得的研究成果主要有: 1.一种带有效位预判的部分标识比较Cache(PTC-V Cache)。组相联Cache实现了高命中率,但同时也带来了更多的能耗。本文针对组相联Cache,提出了一种带有效位预判的部分标识比较Cache,它能够有效地节省Cache中信号放大器和位线的能耗。结果表明,PTC-V Cache平均能够节省指令Cache中约55%的能耗。 2.一种带有效位判别的分离比较Cache(SC-V Cache)。该Cache基于路暂停Cache结构,在此基础上,设计了有效位判断和分离标识比较器。它能缩短标识比较的时间,并且减少对无效数据块读取的能耗,以确保同时获得高性能和低能耗。该方案很大程度上节省了路暂停Cache的平均能耗,尤其对于大容量Cache。 3.一种基于程序段的可重构Cache自适应算法PBSTA。该算法使用建立在指令工作集签名基础上的程序段监测状态机来判断程序段是否发生变化,并做出容量调整决定;在程序段内,该算法使用容量调整状态机来指导Cache进行容量调整。与先前的算法相比,该算法不仅有效地降低了Cache存储系统的能耗,而且减少了不必要的重构所带来的性能损失。 4.一种基于程序段的动态电压缩放算法PBVSA。该算法使用程序段监测状态机来判断程序段是否发生变化,并做出CPU电压和频率调整决定,在程序段内,该算法通过计算该程序段的频率缩放因子β(片外工作时间与片上工作时间的比例关系)来设定CPU的电压和频率。结果表明,该算法在保证系统性能的前提下,有效地降低了处理器的能耗。 5.一种基于程序段的可重构Cache 与处理器电压自适应算法CVPBSTA。该算法结合PBSTA算法与PBVSA算法的特点,使用程序段监测状态机来判断程序段是否发生变化,并做出Cache容量及CPU电压和频率的调整决定。在程序段内,该算法采用了与PBSTA相似的Cache容量调整策略和与PBVSA相似的CPU电压和频率调整策略,先后对Cache容量及CPU电压和频率进行调整。结果表明,该算法在保证性能的前提下,更大程度上地节省了系统的能耗。 基于超低功耗无线模块RFM64的无线远传水表设计方案 概述 随着社会和经济的进步,住宅商品化发展迅速,住宅水、电、气、热表的抄表和收费问题日益突出。如何有效解决入户抄表收费的技术问题,提供一个合理、完整、系统的实施管理方案,需要企业、科研和公用事业管理部门共同努力。目前,住宅水、电、气、热表远程抄表系统形式多样,但市场比较混乱,技术上尚不成熟,没有一个被市场认可的完整系统实施管理方案。传统的有线抄表系统布线复杂、可靠性差、维护困难,难以实现管理升级,不能满足旧楼系统改造的市场要求;而新兴GPRS、短信GSM网络抄表方式使用成本昂贵,不适宜大面积推广。 RFM64是华普推出的一款超低功耗高性能的无线收发模块,最大发射功率10db以上,可工作在315/433MHz ISM的频点,故无需申请。RFM64经过优化具有非常低的接收功耗,典型接收电流为 2.6mA, 远小于同类收发器的接收电流。工作电压为 2.1-3.6V,最大发射功率+12.5dBm, RFM64集成度非常高,其包含了射频功能和逻辑控制功能的集成电路,内部集成压控振荡器、锁相环电路、功率放大电路、低噪声放大电路、调制解调电路、变频器、中放电路等。此外它整合了基带调制解调器的数据传输速率高达150Kbps数据处理功能包括一个64字节的FIFO,包处理,自动CRC生成和数据白化。它的高度集成的架构允许最少的外部元件数量,同时保持设计的灵活性。所有主要的射频通讯参数可编程,其中多数可动态设置。 基于超低功耗无线模块RFM64的设计,其具有传输距离相对远,接收的灵敏度较高,工作功耗低等诸多优点,所以它适用于无线远传水表、无线远传电表、无线远传燃气表、无线远传热量表无线遥控系统、无线传感器网络、无线温度压力数据采集、机器人控制等需要用电池长期工作的领域。 系统电路设计 系统主要由一个MCU和RFM64组成。MCU选用了ST公司的低功耗单片机 STM8L101F3, RFM64与单片机通讯采用SPI接口,与外部终端通信采用UART接口。由于高度集成化RFM64外围零件已经很少,所以设计的关键是RF前端的匹配电路的设计。另外高频部分的走线尽量的短粗,元器件参数要根据线路板的实际情况作出适当的调节,以抵消分布参数的影响。一般的RF芯片发射与接收端口的阻抗并不是标准的50?阻抗,要达到最佳的接收效果必须将输入阻抗通过外围器件的补偿使之与50?的天线匹配。 如何进行低功耗设计 现在电子产品,特别是最近两年很火爆的穿戴产品,智能手表等都是锂电池供电,如果采用同样容量大小的锂电池进行测试不难发现电子产品低功耗做的好的,工作时间越长。因此,低功耗设计排在电子产品设计的重要地位。 最近做穿戴产品设计,面临的第一个问题就是低功耗设计。经过这两天的认真分析总结,将低功耗设计的方法总结,以飨网友。 首先,要明白一点就是功耗分为工作时功耗和待机时功耗,工作时功耗分为全部功能开启的功耗和部分功能开启的功耗。这在很大程度上影响着产品的功耗设计。 对于一个电子产品,总功耗为该产品正常工作时的电压与电流的乘积,这就是低功耗设计的需要注意事项之一。 为了降低产品的功耗,在电子产品开发时尽量采用低电压低功耗的产品。比如一个产品,曾经用5v单片机正常工作,后来又了3.3v的单片机或者工作电压更低的,那么就是在第一层次中进行了低功耗设计,这也就是我们常说的研发前期低功耗器件选择。这一般需要有广阔的芯片涉猎范围或者与供应商有良好的沟通。 其次是模块工作的选择控制,一般选择具有休眠功能的芯片。比如在设计一个系统中,如果某些外部模块在工作中是不经常使用的,我们可以使其进入休眠模式或者在硬件电路设计中采用数字开关来控制器工作与否,当需要使用模块时将其唤醒,这样我们可以在整个系统进入低功耗模式时,关闭一些不必要的器件,以起到省电的作用,延长了待机时间。一般常用方法:①具有休眠模式的功能芯片②MOS管做电子开关③具有使能端的LDO芯片。 再次,选择具有省电模式的主控芯片。现在的主控芯片一般都具有省电模式,通过以往的经验可以知道,当主控芯片在省电模式条件下,其工作电流往往是正常工作电流的几分之一,这样可以大大增强消费类产品电池的使用时间。同时,现在一些控制芯片具有双时钟的模式,通过软件的配置使芯片在不同的使用场合使用不同的外部始终从而降低其功耗。这与始终分频器具有异曲同工之妙,不同之处想必就是BOM的价格问题。现在火爆的APPLE WATCH 就是低功耗的一个例子:全功能运行3-4小时,持续运行18小时。 主控芯片或者相关模块唤醒的方式选择。通常进过以上的步骤设计好了硬件结构,在系统需要省电,在什么时候进入省电模式,这一般在软件设计中实现,但是最主要还是需要根据产品的功能特性来决定了。当系统进入了省电模式,而系统的唤醒也需要控制。一般系统的唤醒分为自动唤醒和外部唤醒。 A、自动唤醒是使用芯片内部的定时器来计时睡眠时间,当睡眠时间达到预定时间时,自动进行唤醒。这与我们使用的看门狗或者中断有比较相近之处,不同就是其工作与否的时序。 B、外部唤醒就是芯片一直处于一种休眠状态,当有一个外部事件(主要是通过接口)来对芯片进行一个触发,则芯片会唤醒,在事件处理之后消除该触发事件而在此进入休眠状态。因此,根据系统的特性,就需要进行软件设计时,来决定如何使用睡眠及唤醒,以降低系统的功耗。 最后说说功耗的测试,功耗测试分为模块功耗和整机功耗,模块功耗需要测试休眠时功耗和工作时功耗。整机功耗分为最大负荷工作时功耗和基本功能时功耗和休眠时功耗。在前期的测试中我用直接用UI来进行测量,关于如何进行高精度低功耗产品的测量,在下篇中进一步说明。 计算机系统结构实验报告 名称: Cache性能分析学院:信息工程 姓名:陈明 学号:S121055 专业:计算机系统结构年级:研一 实验目的 1.加深对Cache的基本概念、基本组织结构以及基本工作原理的理解; 2.了解Cache的容量、相联度、块大小对Cache性能的影响; 3.掌握降低Cache失效率的各种方法,以及这些方法对Cache性能提高的好处; 4.理解Cache失效的产生原因以及Cache的三种失效; 5.理解LRU与随机法的基本思想,及它们对Cache性能的影响; 实验平台 Vmware 虚拟机,redhat 9.0 linux 操作系统,SimpleScalar模拟器 实验步骤 1.运行SimpleScalar模拟器; 2.在基本配置情况下运行程序(请指明所选的测试程序),统计Cache总失效 次数、三种不同种类的失效次数; 3.改变Cache容量(*2,*4,*8,*64),运行程序(指明所选的测试程序), 统计各种失效的次数,并分析Cache容量对Cache性能的影响; 4.改变Cache的相联度(1路,2路,4路,8路,64路),运行程序(指明所 选的测试程序),统计各种失效的次数,并分析相联度对Cache性能的影响; 5.改变Cache块大小(*2,*4,*8,*64),运行程序(指明所选的测试程 序),统计各种失效的次数,并分析Cache块大小对Cache性能的影响; 6.分别采用LRU与随机法,在不同的Cache容量、不同的相联度下,运行程序 (指明所选的测试程序)统计Cache总失效次数,计算失效率。分析不同的替换算法对Cache性能的影响。 预备知识 1. SimpleScalar模拟器的相关知识。详见相关的文档。 2. 复习和掌握教材中相应的内容 (1)可以从三个方面改进Cache的性能:降低失效率、减少失效开销、减少Cache命中时间。 (2)按照产生失效的原因不同,可以把Cache失效分为三类: ①强制性失效(Compulsory miss) https://www.360docs.net/doc/0f2703023.html,/inform ation/snug/2009/low-power-impleme ntation-flow-based-ieee1801-upf 基于IEEE1801(UPF)标准的低功耗设计实现流程 Low-power Implementation Flow Based IEEE1801 (UPF) 郭军, 廖水清, 张剑景 华为通信技术有限公司 jguo@https://www.360docs.net/doc/0f2703023.html, liaoshuiqing@https://www.360docs.net/doc/0f2703023.html, zhangjianjing@https://www.360docs.net/doc/0f2703023.html, Abstract Power consumption is becoming an increasingly important aspect of ASIC design. There are several different approaches that can be used to reduce power. However, it is important to use these low-power technology more effectively in IC design implementation and verification flow. In our latest low-power chip, we completed full implementation and verification flow from RTL to GDSII successfully and effectively by adopting IEEE1801 Unified Power Format (UPF). This paper will focus on UPF application in design implementation with Synopsys low power solution. It will highlight that how to describe our low-power intent using UPF and how to complete the design flow. This paper first illustrates current low-power methodology and UPF?s concept. Then, it discussed UPF application in detail. Finally, it gives our conclusion. Key words: IEEE1801, UPF, Low-Power, Shut-Down, Power Gating, Isolation, IC-Compiler 摘要 实验3 Cache 控制器设计 1、实验目的 (1)掌握Cache控制器的原理及其设计方法。 (2)熟悉FPGA应用设计及EDA 软件的使用。 (3) 熟悉Vivado软件的使用及FPGA应用设计。 2、实验原理 Cache是介于CPU与主存之间的小容量存储器,包括管理在内的全部功能由硬件实现,对程序员是透明的,在一定程度上解决了CPU与主存之间的速度差异、与主存容量相比,Cac he的容量特不小,它保存的内容只是内存内容的一个子集,且Cache与主存的数据交互以块为单位、把主存中的块放到Cache中时必须把主存地址映射到Cache中,即确定位置的对应关系,并采纳硬件实现,以便CPU给出的访存地址能够自动变换成Cache地址。由于程序访问的局部性,使得主存的平均读出时间接近Cache的读出时间,大大提高了CPU的访存效率、 地址映射方式有全相联方式、直截了当相联方式、组相联方式,本实验采纳的是直截了当方式,这种变换方式简单而直截了当,硬件实现特不简单,访问速度也比较快,然而块的冲突率比较高、其主要原则是:主存中一块只能映象到Cache的一个特定的块中、假设主存的块号为B,Cache的块号为b,则它们之间的映象关系能够表示为:b=B mod Cb其中,Cb是Cache的块容量、设主存的块容量为Mb,区容量为Me,则直截了当映象方法的关系如图3、19所示。把主存按Cache的大小分成区,一般主存容量为Cache容量的整数倍,主存每一个分区内的块数与Cache的总块数相等、直截了当映象方式只能把主存各个区中相对块号相同的那些块映象到Cache中同一块号的那个特定块中、例如,主存的块0只能映象到Cache的块0中,主存的块1只能映象到Cache的块1中,同样,主存区1中的块Cb(在区1中的相对块号是0)也只能映象到Cache 的块0中、依照上面给出的地址映象规则,整个Cache地址与主存地址的低位部分是完全相同的。 热量表设计方案 1 引言 把热表计量技术中的关键要素——温度和流量引入到热计量技术中;利用热介质的温差及供热系统中流量相对稳定的概念,将每个计算单元的温差及流量作为热能计量的依据,实现热量计量。 2 核心技术介绍 2.1热量计算原理 在供热用户中安装热量表,当热水流经供热用户时,根据流量传感器给出的流量和配对温度传感器给出的供回水温度,以及热水流经的时间,可计算并显示供热用户所吸收的热量。其基本公式为: 1 1 r r m v r r Q q hdt q hdt ρ= ?= ??? (1) 式中:Q —供热用户所吸收的热量,J 或W .h m q —流经热量表的水的质量流量,kg/h v q —流经热量表的水的体积流量,m 3 /h ρ—流经热量表的水的密度,kg/m 3 Δh —供热用户的入口和出口温度下的焓值差,J/kg τ—时间,h 2.2 红外无线通信技术 红外线是指波长在750nm~1mm 之间的电磁波,它的频率介于微波和可见光之间,是一种人眼看不到的光线。红外通信利用波长在850nm~900nm 之间的近红外线作为信息的载体来进行通信,将二进制数调制成脉冲序列并以此驱动红外线发射管向外发射红外光;而接收端则先将接收到的光脉冲信号转换为电信号,再进行放大、滤波、解调处理后还原为二进制信号。 2.3超声波流速测量原理 图1 超声波测量流量原理 超声波流量测量是应用一对超声波换能器相向交替(或同时)收发超声波,通过观测超声波在介质中的顺流和逆流传播时间差来间接测量流体的流速,再通过流速来计算流量的一种间接测量方法,如图1 所示。 3 总体设计方案及说明 本方案以MPS430为主控芯片、结合超声波测量技术利用高精度时间测量芯片TDC-GP2测量暖气管道进水流速、进回水温度,以此作为热量计算的依据。 3.1系统原理框图 通过一对超声波换能器测量供暖管道的水流速度,进而通过流速计算流量,实现流量的测量;通过温度传感器PT1000测量供暖管道进水温度和回水温度,计算其温度差,由流量和进回水温度差计算出用户所用的热量,作为计费的依据。其系统组成框图如图2所示。 图2 系统原理框图 3.2模块功能 超声波换能器 通过一对超声波换能器,相向交替收发超声波,通过测量超声波在顺流和逆流传播时间差来间接测量流体的流速。 进水温度、回水温度 采用PT系列温度传感器PT1000测量进回水温度,PT1000具有很好的线性性质,测量精度高,电路实现简单。 红外通信接口(预留) 通过此接口实现热能表参数设定、数据抄录等功能。 RS485通信接口(预留) 通过上位机读取指定热量表的热能数据、热能表系统参数信息、读取并设定数据参数。 液晶显示模块 通过按钮按下时间长短显示相应菜单,向用户提供相应热能数据信息,方便用户查询,并当系统发生故障时,显示报警信息。 按键接口 通过此按键按下时间长短显示相应菜单,实现与用户交互,方便用户查询。 注:预留功能接口其与外界通信数据格式与贵公司协商,由贵公司提供。 3.3 功能设计: ①显示功能:用户可以在显示屏查看累计用热、进出水温度值、进出水温差、流量以及其他提示性符号; ②记忆功能:热量表中信息自行记忆,保持时间大于10年; 汕头大学实验报告 学院: 工学院系: 计算机系专业: 计算机科学与技术年级: 13实验时间: 2015.6.16 姓名: 林子伦学号: 2013101030实验名称:基于SPIM-CACHE的Cache实验 一.实验目的: (1)熟悉SPIM-CACHE模拟器环境 (2)深入认识CACHE的工作原理及其作用。 二.实验内容: (1)阅读实验指导书资料(虚拟教室提供了英文论文的电子版本); (2)下载SPIM-CACHE软件,理解英文论文的基本内容之后,给出几种典型的cache配置,运行英文论文提供的代码,记录运行时CACHE命中率等重要数据;(3)运行Fig.4代码,了解mapping functions 即映射规则 (4)运行Fig.7代码,了解temporal and spatial locality 即时空局部性,进一步理解cache的工作原理; (5)运行Fig.8代码,运行学习replacement algorithms 即替代算法,理解其工作原理。 三.实验地点,环境 实验地点:软件工程实验室 实验环境: 操作系统:Microsoft Windows 8 中文版 处理器:Intel(R) Core(TM) i3-3120M CPU @ 2.50GHz 2.50GHz 内存: 4.00GB(3.82GB 可用) 四.实验记录及实验分析(80%): 4.1实验前配置: 1) 按下图配置好Spim设置 2)关于实验中cache设置如下(具体配置根据下面实验要求) ——》 ——》 Cache size ——cache大小 Block size ——块大小 Mapping ——组相连 4.2实验一:fig4.s 实验目的:Algorithm and corresponding code to study mapping functions Cache配置:256-B size, 16-B line size, four-way set associative 实验操作: 1) Ctrl+O 打开运行代码fig4.s 代码如下: .data 0x10000480 Array_A: .word 1,1,1,1,2,2,2,2 .data 0x10000CC0 Array_B: .word 3,3,3,3,4,4,4,4 .text .globl _start _start: la $2,Array_A li $6,0 li $4,8 loop: lw $5,0($2) add $6,$6,$5 addi $2,$2,4 基于32位Cortex-M3内核的超低功耗微控制器EFM32与ACAM公司的高集成度TDC-GP21芯片推出的超声波热量表方案,能够充分发挥EFM32的超低功耗与高运算能力的特点及GP21高精度的测量能力,它将成为超声波热量表方案中的最优之选。 主控及显示部分 超声波主控MCU采用EFM32TG840F32,它是基于ARM公司的32位Cortex-M3内核设计而来,对比于传统的8位、16位单片机,它具有更高的运算和数据处理能力,更高的代码密度,更低的功耗。实际数据显示,EFM32TG840在执行32位乘法运算仅需4个内核时钟周期,32 位除法运算仅需8个内核时钟周期,而相应热表上运用的16位单片机却分别需要50和465个时钟周期。而恰恰在时间数据转换芯片TDC-GP21上采集得到的数据均是32位长度,因此在运算和热量计算时均是32位的数据运算。可见,采用EFM32TG840可以让超声波热量表有更好的运算性能,从而使得整机可以缩短处在运行计算状态状态,达到降低运行功耗的效果。 EFM32TG840具有EM0-EM4共5种低功耗模式。在EM2的低功耗模式下,微控制器仍可实现RTC运行,LEUART、LETIMER 及LESENSE的通信或控制功能,而功耗仅需900你A。而且它具有灵活的唤醒方式和自主工作的PRS系统,可以由外部I/O、I2C通信接口、 LEUART 通信信号等等方式唤醒。 EFM32TG840集成了8×20段的LCD驱动器,满足直接驱动超声波热量表液晶屏的需求,而功耗仅为550nA。EFM32TG840的 LCD驱动器内部集成电压升压功能和对比度调节功能,可实现在芯片内部VCMP电压比较器监控VDD电压,分等级开启LCD升压及对比度调节,达到LCD 的现象效果良好,即使系统电池随着使用时间增加出现电压跌落现象。 Cache实验报告姓名:王宇航学号:09283020 安全0901 Cache实验报告 一、实验要求: 1.阅读分析附件模拟器代码 要求:1)读懂2)关键注释3)总结关键参数和算法的实现方法 2.通过读懂代码加深了解cache的实现技术 3.结合书后习题1进行测试 4.通过测试和进行实验设计了解参数和算法选择的特点和相互关系(比较,组合等),需要定性和量化结合说明,可以用数字或图表等多种描述手段配合说明。 二、实验代码: 1. LRU页面置换算法 程序一共有3中模式: Direct_mapped 2 Set_associate 3 Fully_associate 对于第一种,直接映射,显然用不到LRU算法,因为每一个地址在cache中只有一个地方可以去。 对于后两种,组相联映射和全相联映射,就需要用到LRU算法了。 其中,全相联映射等于是只有一个set的Set_associate,而LRU正是用在一个set中,所以,后面两种模式的LRU问题可以归结为一种:一个set中,来了一个没有的页面,需要置换出一个,应该置换出哪一个的问题。 那么,具体过程如下: 1 这个set中的每一个block都有一个lru值,初始为0。 2 每次访问这个set的时候,不管是否命中,这个set中的所有block的lru值都+1。 3 当需要置换出去一个页面的时候,选择一个lru值最大的那个置换出入,用来放入刚刚进来的。 4 不管是否命中,刚刚访问过的,或者加入的那个block的lru值置为0。 if(x 计算机组成原理 课程设计报告 5级流水无cache CPU实验 1.1 实验内容:无cache流水CPU的分析与改造 1.理解无cache流水CPU的工作原理,明确系统总体结构和数据通路图,分析解决各种相关用到的主 要信号,以及详细分析各流水段的功能和实现。 2.将16位的指令系统改为8位,设计新的指令系统,并修改相应的数据通路。 3.修改规则文件(cpu.txt),并编写测试程序验证系统改造的正确性。 1.2 总体基本信息 1.深刻理解无cache流水cpu的工作原理。在详细分析了各流水段的功能实现、3种相关的产生原因 和解决方法的基础上,完成了以下后续工作。 2.修改指令系统。具体包括: a)16位指令改为8位,重新编写了指令OP码。 b)新增了MOVI指令。由于原指令系统没有将立即数存进指定寄存器的指令,因此此处新增一 条MOVI指令。指令的汇编语句为 MOVI DR, IMM 其中DR为目的寄存器,IMM为立即数。因为指令长度为8位,OP和DR共占了6位,因此IMM 的大小不大于3(即二进制“00”至“11”)。 c)修改及删除了部分指令。此处详见5.1。 3.修改系统控制信号。在保持原有系统逻辑功能基本不变的情况下,修改各个模块里控制信号位数 以及模块接口信号位数以和新的指令系统兼容。 4.增加内存模块。使用vhdl编写了一个ram模块,根据读写信号来选择读写功能。reset时将事先写 好的二进制形式程序写进内存。 5.扩展了常量定义文件。在常量定义文件unitpack.vhd中,具体地: a)新增了ALU功能选择信号常量aluMOVI。 b)新增了寄存器编号常量R0、R1、R2和R3。 c)新增了ram类型。 6.使用Quartus II进行功能仿真并debug。 7.使用bdf构造顶层实体cpum。由于新增了内存模块,而原系统是使用vhdl编写的,为了方便对接, 我们使用bdf的形式将无cache流水线cpu和内存模块连接起来构造顶层实体cpum,“m”的含义是“memory”,即带内存模块的无cache流水线cpu。 8.重画数据通路图。我们使用了Microsoft Visio软件在原有的系统总结结构图的基础上修改并新增 了部分模块,详见2。 三、低功耗技术 1. 功耗分析 (1)由于电容的充放电引起的动态功耗 V DD C l i VDD v out 图(20)充放电转换图 如图(20)所示:PMOS 管向电容L C 充电时,电容的电压从0上升到DD V ,而这些能量来 自于电源。一部分能量消耗在PMOS 管上,而剩余的则保存在电容里。从高电压向低转换的过程中,电容放电,电容中储存的能量消耗在NMOS 管上。 我们来推导一下:考虑从低电压转换到高电压的情况,NMOS 和PMOS 不同时导通。在转换过程中电源提供的能量为C E ,而是转换后储存在电容里的能量。 ???====∞∞VDD DD L out DD L out L DD VDD VDD V C dv V C dt dt dv C V dt t i E 0 002)( ???====∞∞VDD DD L out out L out out L out VDD C V C dv v C dt v dt dv C dt v t i E 02002 )( 这两个等式说明电源提供的能量只有一半储存在电容里。另一半被PMOS 管消耗掉了。 为了计算总体能量消耗,我们不得不考虑器件的翻转。如果门每秒钟翻转10?→? f 次,那么 102 ?→?=f V C P DD L dyn 10?→?f 表示能量消耗的翻转频率。 随着数字电路集成度的提高,能量问题将成为人们关注的焦点。从以上分析看出,dyn P 跟电源电压的平方成正比,因此降低供电电压对降低功耗有非常显著的意义。 但是,降低供电电压对电路性能有一定的影响,这时我们可以考虑减小有效电容和减少翻转率。电容主要是由于晶体管的门和扩散电容引起的,因此降低由于电容的充放电引起的动态功耗方法之一是将晶体管设计得尽可能小,这种方法同样对提高电路的性能有很大的帮助。 SST技术机械式流量计和热量表 普遍认为,机械式热量表与电磁式热量表、超声波热量表相比,因其存在转动部件(流量计叶轮),使用寿命和测量精度相对低些。但合理设计出的机械式热量表的使用寿命和测量精度不比电磁式热量表和超声波热量表低,而且机械式热量表回避了二者的诸多劣势,特别是造价远低于二者的突出优势,使其更适合作为我国供暖建筑热计量的主流热量表。然而,现有机械式热量表受机械式流量计结构及我国供暖水质的制约,存在着严重的技术缺陷,表现为流量计堵塞、磨损、转速信号检测失灵和结垢[1~11]。因此,笔者提出SST技术构想,解决机械式流量计存在的问题。本文对采用SST技术的机械式流量计结构及SST技术热量表进行研究。 1 SST技术机械式流量计结构 ①对称设计 对称设计就是将机械式流量计设计成对称结构。机械式流量计主要分为单流束和多流束流量计,二者都采用两段式立轴叶轮结构。单流束流量计的结构见图1,受进水折流流道结构及两段式立轴叶轮结构的限制,很难设计成对称结构。多流束流量计的结构见图2,受进水分流通道结构及两段式立轴叶轮结构,尤其是多流束喷口方向的限制,不可能加工成对称结构。 对称设计方案为:不区分流量计的进水管和出水管,即流量计相当于有两个进水管,其中一个进水管根据现场状况选作进水管后,另外一个就自动变成了出水管,见图3。在两个进水管之间的叶轮腔中安装叶轮,在进水管与叶轮腔之间的过渡段设计为向下收缩的导水喷管,喷管出口的水流喷射方向对着叶轮的叶片。两个进水管和两个收缩导水喷管以同样的形状和尺寸对称分布在叶轮腔的两侧。 ②直通式进出水流道 现有机械式流量计大多为多流束流量计,由于多流束流量计比单流束流量计的流道复杂,存在着多处阻水结构,这些阻水结构表面常成为流体的缓流和滞流区。因此,多流束流量计比单流束流量计更易结垢。根据机械式流量计的抗结垢原理,采取直通式进出水流道设计,实现流量计的抗结垢性。直通式进出水流道设计结构见图3。直通式进出水流道使流量计中流体通畅流动,具有抗结垢、低压损的特性,避免了单流束流量计侧向水流对叶轮轴产生侧压而导致轴磨损加速。 ③独立横轴叶轮 由于我国供暖水中含有杂质,尤其是那些供暖系统难于排出的细小杂质,易导致热量表的测量精度迅速下降,甚至堵塞流量计。独立横轴叶轮设计结构使流量计的流道拥有足够的空间,含有细小杂质的流体可顺畅通过,解决了以上问题。 独立横轴叶轮结构,见图4。 叶轮由叶片、轮毂、轴套、单根叶轮轴组成,叶片固定在轮毂上,轮毂固定在轴套上,单根叶轮轴贯穿轴套并与轴套成活动连接。无磁金属片镶嵌在叶片上,定位环起到叶片定位作用,叶轮轴的两端固定在叶轮腔的两侧。叶轮与叶轮腔底部留有一定的间隙,与直通式进出水流道 Cache模拟器 一、实验目标: 程序运行时,都会对内存进行相关操作,所访问的内存地址可以被记录下来,形成memory trace文件。在本实验中,你将使用benchmark 程序产生的memory trace文件来测试Cache命中率,文件可以在https://www.360docs.net/doc/0f2703023.html,/classes/fa07/cse240a/proj1-traces.tar.gz上获得。每次存储器访问都包含了三个信息: 1.访问类型,’l’表示Load操作,’s’表示Store操作; 2.地址。采用32位无符号的十六进制表示; 3.存储器访问指令之间的间隔指令数。例如第5条指令和第10条指 令为存储器访问指令,且中间没有其他存储器访问指令,则间隔指令数为4。 通过写一段程序,模拟Cache模拟器的执行过程。 二、实验要求: 写一段程序模拟Cache模拟器的执行过程,并对5个trace文件进行测试,完成以下目标: 1.请统计Load类型指令和Store类型指令在这5个trace文件中的指令比例。 2.设Cache总容量为32KB,对以下所有参数进行组合(共有72种组合),测量相应5个文件的Cache命中率。通过对命中率的分析,可以发现什么规律。 行大小:32字节、64字节、128字节 相连度:8路相联、4路相联、2路相联、1路相联 替换策略:FIFO,随机替换,LRU 写策略:写直达、写回 3. 给出5个文件的最佳Cache命中率的参数组合。针对不同的trace 文件,最佳配置是否相同。 4. 测量各种组合下Cache和主存之间的数据传输量。 5. 给出5个文件的最小数据传输量的参数组合。这个组合和第3问中得到的组合是否一致。针对不同的trace文件,最佳配置是否相同。 6. Cache缺失有三种原因:1)强制缺失;2)容量缺失;3)冲突缺失。分析这三种缺失并说明你的分析方法。 7. 请给出5个trace文件在最优Cache命中率的情况下,这三种缺失所占的比例,并和教材图C.8给出的比例进行比较。 三、程序设计与实现: 本程序我打算采用java进行编写,因为java能够很好地体现面向对象编程的优点。首先需要定义相关的数据类型。 将指令定义为一个单独的指令类,好方便操作和记录统计,其中属性包括该指令的类型,比如是Load指令还是Store指令,还包括指令的地址。 class Instruction { String type; String addrs; } 状态机的概念 状态机是软件编程中的一个重要概念。比这个概念更重要的是对它的灵活应用。在一个思路清晰而且高效的程序中,必然有状态机的身影浮现。 比如说一个按键命令解析程序,就可以被看做状态机:本来在A状态下,触发一个按键后切换到了B状态;再触发另一个键后切换到C 状态,或者返回到A状态。这就是最简单的按键状态机例子。实际的按键解析程序会比这更复杂些,但这不影响我们对状态机的认识。进一步看,击键动作本身也可以看做一个状态机。一个细小的击键动作包含了:释放、抖动、闭合、抖动和重新释放等状态。 同样,一个串行通信的时序(不管它是遵循何种协议,标准串口也好、I2C也好;也不管它是有线的、还是红外的、无线的)也都可以看做由一系列有限的状态构成。 显示扫描程序也是状态机;通信命令解析程序也是状态机;甚至连继电器的吸合/释放控制、发光管(LED)的亮/灭控制又何尝不是个状态机。 当我们打开思路,把状态机作为一种思想导入到程序中去时,就会找到解决问题的一条有效的捷径。有时候用状态机的思维去思考程序该干什么,比用控制流程的思维去思考,可能会更有效。这样一来状态机便有了更实际的功用。 程序其实就是状态机。 也许你还不理解上面这句话。请想想看,计算机的大厦不就是建立在“0”和“1”两个基本状态的地基之上么? 状态机的要素 状态机可归纳为4个要素,即现态、条件、动作、次态。这样的归纳,主要是出于对状态机的内在因果关系的考虑。“现态”和“条件”是因,“动作”和“次态”是果。详解如下: ①现态:是指当前所处的状态。 ②条件:又称为“事件”。当一个条件被满足,将会触发一个动作,或者执行一次状态的迁移。 ③动作:条件满足后执行的动作。动作执行完毕后,可以迁移到新的状态,也可以仍旧保持原状态。动作不是必需的,当条件满足后,也可以不执行任何动作,直接迁移到新状态。 ④次态:条件满足后要迁往的新状态。“次态”是相对于“现态”而言的,“次态”一旦被激活,就转变成新的“现态”了。 如果我们进一步归纳,把“现态”和“次态”统一起来,而把“动作”忽略(降格处理),则只剩下两个最关键的要素,即:状态、迁移条件。 状态机的表示方法有许多种,我们可以用文字、图形或表格的形式来表示一个状态机。 纯粹用文字描述是很低效的,所以就不介绍了。接下来先介绍图形的方式。 毕业设计文献综述 电子信息科学与技术 集成电路低功耗设计方法研究 摘要:随着IC制造工艺达到纳米级,功耗问题已经与面积、速度一样受到人们关注,并成为制约集成电路发展的关键因素之一。同时,由于电路特征尺寸的缩小,之前相比于电路动态功耗可以忽略的静态漏功耗正不断接近前者,给电路低功耗设计提出了新课题,即低漏功耗设计。本文将分析纳米工艺下芯片功耗的组成和对低漏功耗进行研究的重要性,然后介绍目前主要的低功耗设计方法。此外,由于ASIC技术是目前集成电路发展的趋势和技术主流,而标准单元是ASIC设计快速发展的重要支撑,本文在最后提出了标准单元包低漏功耗设计方法,结合电路级的功耗优化技术,从而拓宽ASIC功耗优化空间。 关键字:低功耗,标准单元,ASIC设计 前言: 自1958年德克萨斯仪器公司制造出第一块集成电路以来,集成电路产业一直以惊人的速度发展着,到目前为止,集成电路基本遵循着摩尔定律发展,即集成度几乎每18个月翻一番。 随着制造工艺的发展,IC设计已经进入了纳米级时代:目前国际上能够投入大规模量产的最先进工艺为40nm,国内的工艺水平正将进入65nm;2009年,Intel酷睿i系列创纪录采用了领先的32nm 工艺,并且下一代22nm工艺正在研发中。但伴随电路特征尺寸的减小,电路功耗数值正呈指数上升,集成电路的发展遭遇了功耗瓶颈。功耗问题已经同面积和速度一样受到人们重视,成为衡量IC设计成功与否的重要指标之一。若在设计时不考虑功耗而功利地追求集成度的提高,则可能会使电路某些部分因功耗过大引起温度过高而导致系统工作不稳定或失效。如Intel的1.5GHz Pentium Ⅳ处理器,拥有的晶体管数量高达4200万只,功率接近95瓦,整机生产商不得不为其配上了特大号风扇来维持其正常工作。功耗的增大不仅将导致器件的可靠性降低、芯片的稳定性下降,同时也给芯片的散热和封装带来问题。因此,功耗已经成为阻碍集成电路进一步发展的难题之一,低功耗设计也已成为集成电路的关键设计技术之一。 一、电路功耗的组成 CMOS电路中有两种主要的功耗来源,动态功耗和静态功耗。其中,动态功耗包括负载电容的充放电功耗(交流开关功耗)和短路电流引起的功耗;静态功耗主要是由漏电流引起的功耗,如图1所示。Cache实验

超声波热量表

现代cache技术的研究 课程设计报告

基于超低功耗无线模块RFM64的无线远传水表、远传电表、远传燃气表、远传热量表设计方案

如何进行低功耗设计

cache性能分析实验报告

基于IEEE1801(UPF)标准的低功耗设计实现流程

Cache控制器设计实验

热量表设计方案

根据spim的cache实验

基于GP21+EFM32的超低功耗超声波热量表电路模块设计

《计算机体系结构》第六次实验 cache

5级流水无cache CPU实验计算机组成原理 课程设计报告

ASIC低功耗设计

SST技术机械式流量计和热量表

Cache模拟器实验报告

基于FPGA的Cache替换算法控制器设计++

集成电路低功耗设计方法研究【文献综述】