低死时间单道脉冲幅度分析器的设计与仿真

多道脉冲分析器原理与结构

多道脉冲分析器原理与结 构 Final revision by standardization team on December 10, 2020.

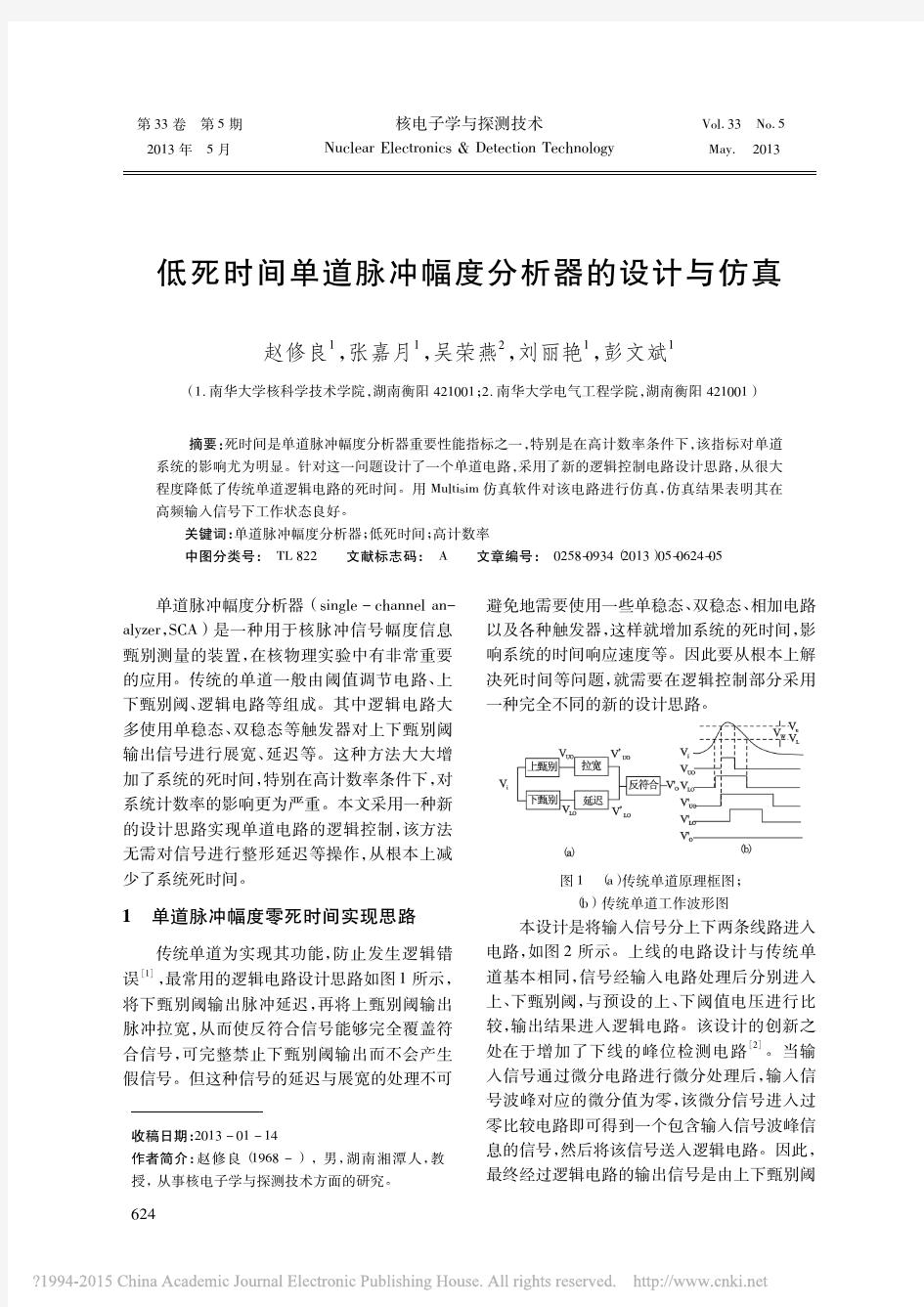

多道幅度分析器原理 在γ能谱测量中,线性脉冲放大器输出的脉冲幅度正比于入射射线的能量。分析脉冲的幅度就可以了解入射射线的能量,分析脉冲幅度的电路称为脉冲幅度分析器。其中,只测量一个幅度间隔内脉冲数的脉冲幅度分析器称为单道脉冲幅度分析器;可以同时测量多个幅度间隔内脉冲数的脉冲幅度分析器称为多道脉冲幅度分析器。 多道脉冲幅度分析器的原理框图,如图所示。它的原理是利用A/D转换将被测量的脉冲幅度范围平均分成2n个幅度间隔,从而把模拟脉冲信号转化成与其幅度对应的数字量,称之为“道址”。在存储器空间里开辟一个数据区,在该数据区中有2n个计数器,每个计数器对应一个道址。控制器每收到一个道址,控制器便将该道址对应的计数器加1,经过一段时间的累积,得到了输入脉冲幅度的分布数据,即谱线数据。这里提到的幅度间隔的个数就是多道脉冲幅度分析器的道数,它由n值决定。 根据上述多道脉冲幅度分析器的原理,可以得出多道脉冲幅度分析器要做的具体工作一方面是把前向通道输出的模拟信号进行模一数转换,并将其转换结果进行处理、存储和显示。 一台完整的核地球物理仪器,常可分为两部分:核辐射探测器和嵌入式系统。多道脉冲幅度分析器是嵌入式系统的核心部分。多道脉冲幅度分析器一方面采集来自放大器的信号并进行模数转换,同时存储转换结果;另一方面将存储的转换结果进行数据分析,并直接显示谱线,或者通过计算机接口送给计算机进行数据处理和谱线显示。 图多道脉冲幅度分析器框图 多道脉冲幅度分析器的原理结构框图如图2-2所示。脉冲信号在通过甄别电路和控制电路时,甄别电路给出脉冲的过峰信息,并启动A/D转换。A/D转换电路对脉冲信号峰值

简易波形发生器设计

摘要:单片机主要面对的是测控对象,突出的是控制功能,所以它从功能和形态上来说都是应测控领域应用的要求而诞生的。随着单片机技术的发展,它在芯片内部集成了许多面对测控对象的接口电路,如ADC、DAC、高速I/O接口、脉冲宽度调制器(Pulse Width Modulator,PWM)、监视定时器(Watch Dog Timer,WDT)等。这些对外电路及外设接口已经突破了微型计算机传统的体系结构,所以单片机也称为微控制器(Micro Controller)。 关键词:中央处理器;随机存储器;只读存储器

引言:一般函数发生器是由硬件组成的,它的输出频率范围宽,各项指标高,性能优良,因而在对输出波形要求较高的地方被广泛应用,这种仪器的缺点是电路复杂,成本高,输出波形种类不多,不够灵活。在对波形指标要求不高,频率要求较低的场合,可以用单片机构成一个波形发生器。产生所需要的各种波形,这样的函数发生器靠软件产生各种波形,小巧灵活,便于修改,且成本低廉,容易实现。 1设计概述 1.1 课程设计的目的 通过对本课题的设计,掌握A/D,D/A转换的应用,用单片机产生各种波形的方法及改变波形频率的方法。熟悉单片机应用系统的设计以及软硬件的调试。单片机本身并没有开发能力,必须借助开发工具即硬件开发环境才能进行开发。单片机的硬件开发环境有PC机、编程器和仿真机等。 1.2 设计的内容、要求 设计一个简易波形发生器,要求该系统能通过开关或按钮有选择性的输出正弦波、三角波、方波、及阶梯波等四种波形,并且这四种波形的频率均可通过输入电位器在一定范围内调节。 对于四种波形的切换,用两个开关的四种状态来表示(或用按钮)。选用常用的A/D转换芯片0809来实现模拟量的输入。D/A转换器选用0832来输出波形。

实验四 单道脉冲幅度分析器

实验四单道脉冲幅度分析器 一、实验目的 1、熟悉单道脉冲幅度分析器的工作原理 2、掌握单道脉冲幅度分析器的甄别阈及道宽线的测量方法 3、了解测量单道分析器分辨时间的方法。 二、实验仪器与装置: 1、NIM机箱和电源一套 2、BH1219型单道脉冲分析器一台 3、TDS1210型示波器一台 4、BH1220定标器插件一个 5、FH—442型滑移精密幅度脉冲发生器一台 6、MFS—70A型双脉冲信号发生器一台 7、EDM-82B型数字万用表一个 三、预习要求 1、参考核电子学,掌握单道脉冲幅度分析器的工作原理。 1、对照FH—1008A单道脉冲分析器熟悉仪器结构。 四、电路原理 单道脉冲幅度分析器要求只有输入脉冲幅度落入给定的电压(阈电平)范围(V U—V L)之内时,才输出逻辑脉冲。而输入脉冲幅度小于V L或大于V U时皆无输出脉冲。 单道脉冲幅度分析器组成框图如图4-1,共由6部分组示。电路原理图如图4-2。其中电压比较器用LM710,响应速度快(40ns),放大倍数高(1000V/V)。 图4-1 单道脉冲幅度分析器原理框图

(1) 输入衰减及双向输入 由于比较器的最大输入电压范围为±5V ,而一般放大器的满量程输出电压为10V 。为了达到满量程10V 的分析范围,在单道中引入了一个二比一衰减器,它由LM318型双端输入的差值单运算放大器构成。正的输入信号由电阻R32、R33分压,LM318的3脚和2脚为Vi/3,6脚输出为(Vi/3)/10*15=Vi/2;负的输入信号经R34输入到LM318的反向端,LM318的3脚和2脚为虚地,电压为0,输出信号为-Vi/2。

多通道可调脉宽脉冲发生器设计

《电子技术应用》2007年第5期本刊邮箱:eta@ncse.com.cn图2单片机和CPLD的硬件连接原理图 高重复频率的固体开关技术是脉冲功率领域研究的重点之一。在兆赫兹重复频率下,适合构成固体开关的功率电子器件有金属氧化物半导体场效应晶体管(MOS-FET)、 砷化镓光导开关(GaAs-PCSS)等。对于将功率MOS-FET器件作为固体开关的脉冲功率源,由于单个功率MOSFET器件的耐压和输出电流能力有限,为了得到更高的电压和更大的电流,需要对大量的功率MOSFET器件进行串联和并联。美国利弗莫尔国家实验室(LLNL)用于产生20kV、400A的脉冲功率源,一共使用了720个功率MOS-FET器件[1]。这些功率MOSFET器件在产生输出脉冲时是 同步触发的,这样就需要有多通道的同步触发信号。 功率MOSFET的开关速度非常快,一般为十几纳秒。因此,对同步输出的触发信号需要的时间抖动要小于MOSFET器件的开关时间, 否则将会引起并联的 MOSFET器件的电流不均匀,导致器件损坏。MOSFET器 件的开关完全是由输入栅极驱动信号决定的,为了能使功率MOSFET器件能在MHz的重复频率下工作,要求触发信号源有很小脉宽的输出能力。本文介绍了一种可用于兆赫兹重复频率的脉冲功率源上作为触发信号的多通道可调脉宽、频率的脉冲发生器的设计。 1系统的组成和工作原理 脉冲发生器的系统结构如图1,整个系统由控制部分和光纤发射电路部分组成。在控制部分中,单片机89S52和可编程逻辑器件(CPLD)ispLSI1032E组成了脉冲产生的逻辑硬件核心。单片机负责接收并解析上位机(PC机)的设置信息,如输出脉冲的宽度,频率和个数,通过运算得 到CPLD所需的分频数,并通过8位总线传输给CPLD,由 CPLD产生多个通道同步输出的脉冲信号。单片机还可以 读取CPLD中关于输出脉冲的设置,处理后返回到上位机作为诊断信息。CPLD的优点是可用I/O口多,可以实现多通道的同步输出。光纤发射电路将每一路控制产生的脉冲信号经驱动增强电路之后,分成12路的同步脉冲,用光纤发射器件以光信号的方式输出。 2硬件设计 控制部分的核心是单片机和CPLD器件,它们之间的接口方式一般有独立方式和总线方式两种。独立方式最大的优点是接口逻辑无须遵循单片机内固定的总线方式的读写时序。总线方式具有编程简单、速度快的优点。本设计采用8位总线方式,图2为硬件连接原理图。设计 多通道可调脉宽脉冲发生器设计 张良,秦玲,刘承俊,章林文 (中国工程物理研究院流体物理研究所,四川绵阳621900) 摘要:一种用于功率MOSFET器件触发信号产生的多通道可调脉宽脉冲发生器。该装置具有控制简单,多个通道时间抖动小的特点。 关键词:信号发生器多通道脉宽可调 29

顺序脉冲产生电路设计

沈阳航空航天大学 课程设计 (说明书) 顺序脉冲产生电路设计 班级计算机1304 学号2013040101178 学生姓名万延正 指导教师孙克梅

沈阳航空航天大学 课程设计任务书 课程名称数字逻辑课程设计 课程设计题目顺序脉冲产生电路设计 课程设计的内容及要求: 一、设计说明与技术指标 要求设计一个顺序脉冲产生电路,能将预先设定的并行数据转换为串行脉冲输出,具体要求如下: ①电路具有16个按键用来设定输入16个并行数据的高低电平; ②具有启动按键,每按一次启动键,电路就串行输出预先设定的16个数据; ③输出完16个数据位后电路停止,输出恒为0; ④具有输出信号指示灯,表明输出信号的高低电平,灯亮表示1,不亮表示0; ⑤具有时钟信号指示灯,在每个式中信号周期内闪烁一次。 二、设计要求 1.在选择器件时,应考虑成本。 2.根据技术指标,通过分析计算确定电路和元器件参数。 3.画出电路原理图(元器件标准化,电路图规范化)。 三、实验要求 1.根据技术指标制定实验方案;验证所设计的电路,用软件仿真。 2.进行实验数据处理和分析。 四、推荐参考资料 1.阎石主编.数字电子技术基础.[M]北京:高等教育出版社,2006年 2.赵淑范,王宪伟主编.电子技术实验与课程设计.[M]北京:清华大学出版社,2006年 3.孙肖子、邓建国等主编. 电子设计指南. [M]北京:高等教育出版社,2006年 4.杨志忠主编. 电子技术课程设计. [M]北京:机械工业出版社,2008年 五、按照要求撰写课程设计报告

成绩评定表: 指导教师签字: 2015 年7 月19 日

一、概述 在数控装置和数字计算机中,往往需要机器按照人们事先规定的顺序进行运算和操作,这就要求控制电路不仅能正确的发出各种控制信号,而且要求这些控制信号在时间上有一定的先后顺序,能完成这样功能的电路称为顺序脉冲发生器。该顺序脉冲由555定时器产生,用16个开关设定输入16个并行数据的高低电平,每次按键,电路就会串行输出预先设定的16个数,输出完16个数据位后电路停止,输出恒为0。该电路具有输出信号指示灯,灯亮的次数表示输入高电平的个数。在每个周期内,时钟指示灯只闪烁一次。 一、方案论证 根据实验要求,我选取两片74LS165芯片将其串联,74LS165芯片是并行输入, 串行输出移位寄存器。从而实现电路具有16个按键用来设定输入16个并行数据的高低电平。电路主要由顺序脉冲产生电路,移位寄存电路,状态指示电路,电源电路组成。原理图如图1所示: 图1 总电路框架图 二、电路设计 1、时钟脉冲产生电路如图2所示。 图2 时钟脉冲产生电路

基于51单片机的波形发生器的设计讲解

目录 1 引言 (1) 1.1 题目要求及分析 (1) 1.1.1 示意图 (1) 1.2 设计要求 (1) 2 波形发生器系统设计方案 (2) 2.1 方案的设计思路 (2) 2.2 设计框图及系统介绍 (2) 2.3 选择合适的设计方案 (2) 3 主要硬件电路及器件介绍 (4) 3.1 80C51单片机 (4) 3.2 DAC0832 (5) 3.3 数码显示管 (6) 4 系统的硬件设计 (8) 4.1 硬件原理框图 (8) 4.2 89C51系统设计 (8) 4.3 时钟电路 (9) 4.4 复位电路 (9) 4.5 键盘接口电路 (10) 4.7 数模转换器 (11) 5 系统软件设计 (12) 5.1 流程图: (12) 5.2 产生波形图 (12) 5.2.1 正弦波 (12) 5.2.2 三角波 (13) 5.2.3 方波 (14) 6 结论 (16) 主要参考文献 (17) 致谢...................................................... 错误!未定义书签。

1引言 1.1题目要求及分析 题目:基于51单片机的波形发生器设计,即由51单片机控制产生正弦波、方波、三角波等的多种波形。 1.1.1示意图 图1:系统流程示意图 1.2设计要求 (1) 系统具有产生正弦波、三角波、方波三种周期性波形的功能。 (2) 用键盘控制上述三种波形(同周期)的生成,以及由基波和它的谐波(5次以下)线性组合的波形。 (3) 系统具有存储波形功能。 (4) 系统输出波形的频率范围为1Hz~1MHz,重复频率可调,频率步进间隔≤100Hz,非正弦波的频率按照10次谐波来计算。 (5) 系统输出波形幅度范围0~5V。 (6) 系统具有显示输出波形的类型、重复频率和幅度的功能。

可控脉冲发生器的设计

可控脉冲发生器的设计 一、 实验目的 1、 了解可控脉冲发生器的实现机理。 2、 学会用示波器观察FPGA 产生的信号。 3、 学习用VHDL 编写复杂功能的代码。 二、 实验原理 脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周期和占空比可变的脉冲波形。可控脉冲发生器的实现原理比较简单,可以简单的理解为一个计数器对输入的时钟信号进行分频的过程。通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的。下面举个简单的例子来说明其工作原理。 假如有一个计数器T 对时钟分频,其计数的范围是从0~N ,另取一个 M (0≤M ≤N ),若输出为Q ,那么Q 只要满足条件 时,通过改变N 值,即可改变输出的脉冲波的周期;改变M 值,即可改变脉冲波的占空比。这样输出的脉冲波的周期和占空比分别为: 三、 实验内容 编写实现可控脉冲发生器程序,通过脉冲周期和占空比改变实现不同脉冲的输出。用Quartu s 软件对设计进行编译、综合、仿真,给出相应的时序仿真波形和硬件电路图。 四、 实验程序 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity exp10 is port( Clk : in std_logic; --时钟输入 Rst : in std_logic; --复位输入 ???≤≤<≤=N T M M T Q 001%1001 )1(?+=+=N M T N CLOCK 占空比周期

多种波形发生器的设计与制作

课题三 多种波形发生器的设计与制作 方波、三角波、脉冲波、锯齿波等非正弦电振荡信号是仪器仪表、电子测量中最常用的波形,产生这些波形的方法较多。本课题要求设计的多种波形发生器是一种环形的波形发生器,方波、三角波、脉冲波、锯齿波互相依存。电路中应用到模拟电路中的积分电路、过零比较器、直流电平移位电路和锯齿波发生器等典型电路。通过对本课题的设计与制作,可进一步熟悉集成运算放大器的应用及电路的调试方法,提高对电子技术的开发应用能力。 1、 设计任务 设计并制作一个环形的多种波形发生器,能同时产生方波、三角波、脉冲波和锯齿波,它们的时序关系及幅值要求如图3-3-1所示。 图3-3-1 波形图 设计要求: ⑴ 四种波形的周期及时序关系满足图3-3-1的要求,周期误差不超过%1±。 ⑵ 四种波形的幅值要求如图3-3-1所示,幅值误差不超过%10±。 ⑶ 只允许采用通用器件,如集成运放,选用F741。

要求完成单元电路的选择及参数设计,系统调试方案的选取及综合调试。 2、设计方案的选择 由给定的四种波形的时序关系看:方波决定三角波,三角波决定脉冲波,脉冲波决定锯齿波,而锯齿波又决定方波。属于环形多种波形发生器,原理框图可用3-3-2表示。 图3-3-2 多种波形发生器的方框图 仔细研究时序图可以看出,方波的电平突变发生在锯齿波过零时刻,当锯齿波的正程过零时,方波由高电平跳变为低电平,故方波发生电路可由锯齿波经一个反相型过零比较器来实现。三角波可由方波通过积分电路来实现,选用一个积分电路来完成。图中的u B电平显然上移了+1V,故在积分电路之后应接一个直流电平移位电路,才能获得符合要求的u B波形。脉冲波的电平突变发生在三角波u B的过零时刻,三角波由高电平下降至零电位时,脉冲波由高电平实跳为低电平,故可用一个同相型过零比较器来实现。锯齿波波形仍是脉冲波波形对时间的积分,只不过正程和逆程积分时常数不同,可利用二极管作为开关,组成一个锯齿波发生电路。由上,可进一步将图3-3-2的方框图进一步具体化,如图3-3-3所示。 图3-3-3 多种波形发生器实际框图 器件选择,设计要求中规定只能选用通用器件,由于波形均有正、负电平,应选择由正、负电源供电的集成运放来完成,考虑到重复频率为100Hz(10ms),故选用通用型运放F741(F007)或四运放F324均可满足要求。本设计选用F741。其管脚排列及功能见附录三之三。

简易波形发生器设计报告

电子信息工程学院 硬件课程设计实验室课程设计报告题目:波形发生器设计 年级:13级 专业:电子信息工程学院学号:201321111126 学生姓名:覃凤素 指导教师:罗伟华 2015年11月1日

波形发生器设计 波形发生器亦称函数发生器,作为实验信号源,是现今各种电子电路实验设计应用中必不可少的仪器设备之一。 波形发生器一般是指能自动产生方波、三角波、正弦波等电压波形的电路。产生方波、三角波、正弦波的方案有多种,如先产生正弦波,再通过运算电路将正弦波转化为方波,经过积分电路将其转化为三角波,或者是先产生方波-三角波,再将三角波变为正弦波。本课程所设计电路采用第二种方法,利用集成运放构成的比较器和电容的充放电,实现集成运放的周期性翻转,从而在输出端产生一个方波。再经过积分电路产生三角波,最后通过正弦波转换电路形成正弦波。 一、设计要求: (1) 设计一套函数信号发生器,能自动产生方波、三角波、正弦波等电压波形; (2) 输出信号的频率要求可调; (3) 根据性能指标,计算元件参数,选好元件,设计电路并画出电路图; (4) 在面包板上搭出电路,最后在电路板上焊出来; (5) 测出静态工作点并记录; (6) 给出分析过程、电路图和记录的波形。 扩展部分: (1)产生一组锯齿波,频率范围为10Hz~100Hz , V V 8p -p =; (2)将方波—三角波发生器电路改成矩形波—锯齿波发生器,给出设计电路,并记录波形。 二、技术指标 (1) 频率范围:100Hz~1kHz,1kHz~10kHz ; (2) 输出电压:方波V V 24p -p ≤,三角波V V 6p -p =,正弦波V V 1p -p ≥; (3) 波形特性:方波s t μ30r < (1kHz ,最大输出时),三角波%2V <γ ,正弦波y~<2%。 三、选材: 元器件:ua741 2个,3DG130 4个,电阻,电容,二极管 仪器仪表: 直流稳压电源,电烙铁,万用表和双踪示波器 四、方案论证 方案一:用RC 桥式正弦波振荡器产生正弦波,经过滞回比较器输出方波,方波在经过积分器得到三角波。

基于VHDL的可控脉冲发声器 设计

可控脉冲发生器的设计 1.设计要求: 实现周期、占空比均可调的脉冲发生器。 (1)采用1khz 的工作时钟; (2)脉冲周期0.5s~6s ,占空比10%~90%; (3)可初始化:周期2.5s ,占空比50%; 2.实验目的 1、了解可控脉冲发生器的实现机理。 2、学会用示波器观察FPGA 产生的信号。 3、学习用VHDL 编写复杂功能的代码。 3.实验原理: 脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周期和占空比可变的脉冲波形。可控脉冲发生器的实现原理比较简单,可以简单的理解为一个计数器对输入的时钟信号进行分频的过程。通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的。下面举个简单的例子来说明其工作原理。 假如有一个计数器T 对时钟分频,其计数的范围是从0~N ,另取一个 M (0≤M ≤N ),若输出为Q ,那么Q 只要满足条件 时,通过改变N 值,即可改变输出的脉冲波的周期;改变M 值,即可改变脉冲波的占空比。这样输出的脉冲波的周期和占空比分别为: 4.实验内容: 编写实现可控脉冲发生器程序,通过脉冲周期和占空比改变实现不同脉冲的输出。用Quartu s 软件对设计进行编译、综合、仿真,给出相应的时序仿真波形和硬件电路图。 ???≤≤<≤=N T M M T Q 001%1001)1(?+=+=N M T N CLOCK 占空比周期

5.程序设计及仿真: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity exp10 is port( Clk : in std_logic; --时钟输入 Rst : in std_logic; --复位输入 NU,ND : in std_logic; --输入:控制频率的改变 MU,MD : in std_logic; --输入:控制占空比的改变 Fout : out std_logic --波形输出 ); end exp10; architecture behave of exp10 is signal N_Buffer,M_Buffer : std_logic_vector(10 downto 0); signal N_Count :std_logic_vector(10 downto 0); signal clkin : std_logic; signal Clk_Count : std_logic_vector(12 downto 0); --产生一个低速时钟,用于按键判断 begin process(Clk) --计数器累加 begin if(Clk'event and Clk='1') then if(N_Count=N_Buffer) then N_Count<="00000000000"; else N_Count<=N_Count+1; end if; end if; end process; process(Clk) --波形判断

设计并实现频率可控的正弦波信号发生器 单片机课设

1Proteus软件简介 Proteus ISIS是英国Labcenter公司开发的电路分析与实物仿真软件。它运行于Windows 操作系统上,可以仿真、分析(SPICE)各种模拟器件和集成电路,该软件的特点是:①实现了单片机仿真和SPICE电路仿真相结合。具有模拟电路仿真、数字电路仿真、单片机及其外围电路组成的系统的仿真、RS232动态仿真、I2C调试器、SPI调试器、键盘和LCD系统仿真的功能;有各种虚拟仪器,如示波器、逻辑分析仪、信号发生器等。②支持主流单片机系统的仿真。目前支持的单片机类型有:68000系列、8051系列、A VR系列、PIC12系列、PIC16系列、PIC18系列、Z80系列、HC11系列以及各种外围芯片。③提供软件调试功能。在硬件仿真系统中具有全速、单步、设置断点等调试功能,同时可以观察各个变量、寄存器等的当前状态,因此在该软件仿真系统中,也必须具有这些功能;同时支持第三方的软件编译和调试环境,如Keil C51 uVision2等软件。④具有强大的原理图绘制功能。总之,该软件是一款集单片机和SPICE分析于一身的仿真软件,功能极其强大。 特点:支持ARM7,PIC ,A VR,HC11以及8051系列的微处理器CPU模型,更多模型正在开发中; 交互外设模型有LCD显示、RS232终端、通用键盘、开关、按钮、LED等; 强大的调试功能,如访问寄存器与内存,设置断点和单步运行模式; 支持如IAR、Keil和Hitech等开发工具的源码C和汇编的调试; 一键“make”特性:一个键完成编译与仿真操作; 内置超过6000标准SPICE模型,完全兼容制造商提供的SPICE模型; DLL界面为应用提供特定的模式; 14种虚拟仪器:示波器、逻辑分析仪、信号发生器、规程分析仪等; 高级仿真包含强大的基于图形的分析功能:模拟、数字和混合瞬时图形;频率;转换;噪声;失真;付立叶;交流、直流和音频曲线; 模拟信号发生器包括直流、正旋、脉冲、分段线性、音频、指数、单频FM;数字信号发生器包括尖脉冲、脉冲、时钟和码流; 集成PROTEUS PCB设计形成完整的电子设计系统。 Protues软件与Keil uVision的结合 对于初次使用Protues软件的人可能还不知道如何设置,现在把设置步骤简介如下,仅供参考(本文章只讨论在单机上结合,在两个联网机器使用由于篇幅限制不在此讨论):设置

简易波形发生器的设计

目录 第一章单片机开发板 (1) 1.1 开发板制作 (1) 1.1.1 89S52单片机简介 (1) 1.1.2 开发板介绍 (2) 1.1.3 89S52的实验程序举例 (3) 1.2开发板焊接与应用 (4) 1.2.1开发板的焊接 (4) 1.2.2开发板的应用 (5) 第二章函数信号发生器 (7) 2.1电路设计 (7) 2.1.1电路原理介绍 (7) 2.1.2 DAC0832的工作方式 (9) 2.2 波形发生器电路图与程序 (10) 2.2.1应用电路图 (10) 2.2.2实验程序 (11) 2.2.3 调试结果 (15) 第三章参观体会 (16) 第四章实习体会 (17) 参考文献 (18)

第一章单片机开发板 1.1 开发板制作 1.1.1 89S52单片机简介 图1.1 89s52 引脚图 如果按功能划分,它由8个部件组成,即微处理器(CPU)、数据存储器(RAM)、程序存储器(ROM/EP ROM)、I/O口(P0口、P1口、P2口、P3口)、串行口、定时器/计数器、中断系统及特殊功能寄存器(SF R)的集中控制方式。 各功能部件的介绍: 1)数据存储器(RAM):片内为128个字节单元,片外最多可扩展至64K字节。 2)程序存储器(ROM/EPROM):ROM为4K,片外最多可扩展至64K。 3)中断系统:具有5个中断源,2级中断优先权。 4)定时器/计数器:2个16位的定时器/计数器,具有四种工作方式。 5)串行口:1个全双工的串行口,具有四种工作方式。 6)特殊功能寄存器(SFR)共有21个,用于对片内各功能模块进行管理、监控、监视。 7)微处理器:为8位CPU,且内含一个1位CPU(位处理器),不仅可处理字节数据,还可以进行位变量的处理。 8)四个8位双向并行的I/O端口,每个端口都包括一个锁存器、一个输出驱动器和一个输入缓冲器。这四个端口的功能不完全相同。 A、P0口既可作一般I/O端口使用,又可作地址/数据总线使用; B、P1口是一个准双向并行口,作通用并行I/O口使用; C、 P2口除了可作为通用I/O使用外,还可在CPU访问外部存储器时作高八位地址线使用; D、P3口是一个多功能口除具有准双向I/O功能外,还具有第二功能。 控制引脚介绍: 1)电源:单片机使用的是5V电源,其中正极接40引脚,负极(地)接20引脚。 2)时钟引脚XTAL1、XTAL2时钟引脚外接晶体与片内反相放大器构成了振荡器,它提供单片机的时钟控制信号。时钟引脚也可外接晶体振荡器。 振蒎电路:单片机是一种时序电路,必须提供脉冲信号才能正常工作,在单片机内部已集成了振荡器,

多道脉冲分析器原理与结构

多道幅度分析器原理 在γ能谱测量中,线性脉冲放大器输出的脉冲幅度正比于入射射线的能量。分析脉冲的幅度就可以了解入射射线的能量,分析脉冲幅度的电路称为脉冲幅度分析器。其中,只测量一个幅度间隔内脉冲数的脉冲幅度分析器称为单道脉冲幅度分析器;可以同时测量多个幅度间隔内脉冲数的脉冲幅度分析器称为多道脉冲幅度分析器。 多道脉冲幅度分析器的原理框图,如图2.3所示。它的原理是利用A/D转换将被测量的脉冲幅度范围平均分成2n个幅度间隔,从而把模拟脉冲信号转化成与其幅度对应的数字量,称之为“道址”。在存储器空间里开辟一个数据区,在该数据区中有2n个计数器,每个计数器对应一个道址。控制器每收到一个道址,控制器便将该道址对应的计数器加1,经过一段时间的累积,得到了输入脉冲幅度的分布数据,即谱线数据。这里提到的幅度间隔的个数就是多道脉冲幅度分析器的道数,它由n值决定。 根据上述多道脉冲幅度分析器的原理,可以得出多道脉冲幅度分析器要做的具体工作一方面是把前向通道输出的模拟信号进行模一数转换,并将其转换结果进行处理、存储和显示。 一台完整的核地球物理仪器,常可分为两部分:核辐射探测器和嵌入式系统。多道脉冲幅度分析器是嵌入式系统的核心部分。多道脉冲幅度分析器一方面采集来自放大器的信号并进行模数转换,同时存储转换结果;另一方面将存储的转换结果进行数据分析,并直接显示谱线,或者通过计算机接口送给计算机进行数据处理和谱线显示。 图2.3 多道脉冲幅度分析器框图 多道脉冲幅度分析器的原理结构框图如图2-2所示。脉冲信号在通过甄别电路和控制电路时,甄别电路给出脉冲的过峰信息,并启动A/D转换。A/D转换电路对脉冲信号峰值幅度进行模数转换,并将转换结果存储在片上Flash中,由微控制器进行相应的数据处理。 峰值检测电路 峰值检测电路根据实际需求可分为两种类型:数字型和模拟型。数字式峰值检测电路要以高速处理器为核心,结合高速ADC,在采样脉冲的控制下,对信号进行连续测量,得到原始测量数据,再通过一种算法,解算出脉冲峰值信息。比如我们一个脉冲是l,us脉冲宽,那么我们至少在l,us内进行大于10次以上的ADC转换值,然后再对这些值进行处理,得到一个最大值,认为这个值是峰值,接着这个值与我们设定的阐值进行比较,如果是大于闭值,那么我们认为是一个脉冲峰值,否则,认为是干扰噪声,我们丢弃这个数据。这就要求我们的CPU有足够的处理速度,ADC有足够快的转换速度。典型的方案是DSP处理器结合FPGA 以及高速ADC。模拟型峰值检测电路相对就简单多了,只有在脉冲信号到来的时候,峰值

波形发生器课程设计

1.设计题目:波形发生电路 2.设计任务和要求: 要求:设计并用分立元件和集成运算放大器制作能产生方波和三角波波形的波形发生器。 基本指标:输出频率分别为:102H Z 、103H Z ;输出电压峰峰值V PP ≥20V 3.整体电路设计 1)信号发生器: 信号发生器又称信号源或振荡器。按信号波形可分为正弦信号、函数(波形)信号、脉冲信号和随机信号发生器等四大类。各种波形曲线均可以用三角函数方程式来表示,如三角波、锯齿波、矩形波(含方波)、正弦波。通过模拟电子技术设计的波形发生器是一个不需要外加输入信号,靠自身振荡产生信号的电路。2)电路设计: 整体电路由RC振荡电路,反相输入的滞回比较器和积分电路组成。 理由:a)矩形波电压只有两种状态,不是高电平,就是低电平,所以电压比较器是它的重要组成部分; b)产生振荡,就是要求输出的两种状态自动地相互转换,所以电路中必须引入反馈; c)输出状态应按一定的时间间隔交替变化,即产生周期性变化,所以电路中要有延迟环节来确定每种状态维持的时间。 RC振荡电路:即作为延迟环节,又作为反馈电路,通过RC充放电实现输出状态的自动转换。 反相输入的滞回比较器:矩形波产生的重要组成部分。 积分电路:将方波变为三角波。 3)整体电路框图: 为实现方波,三角波的输出,先通过 RC振荡电路,反相输入的滞回比较器得到方波,方波的输出,是三角波的输入信号。三角波进入积分电路,得出的波形为所求的三角波。其电路的整体电路框图如图1所示:

图1 4)单元电路设计及元器件选择 a ) 方波产生电路 根据本实验的设计电路产生振荡,通过RC 电路和滞回比较器时将产生幅值约为12V 的方波,因为稳压管选择1N4742A (约12V )。电压比较电路用于比较模拟输入电压与设定参考电压的大小关系,比较的结果决定输出是高电平还是低电平。滞回比较器主要用来将信号与零电位进行比较,以决定输出电压。图3为一种滞回电压比较器电路,双稳压管用于输出电压限幅,R 3起限流作用,R 2和R 1构成正反馈,运算放大器当u p >u n 时工作在正饱和区,而当u n >u p 时工作在负饱和区。从电路结构可知,当输入电压u in 小于某一负值电压时,输出电压u o = -U Z ;当输入电压u in 大于某一电压时,u o = +U Z 。运算放大器在两个饱和区翻转时u p =u n =0,由此可确定出翻转时的输入电压。u p 用u in 和u o 表示,有 2 1o 1in 22 1o 2 in 1p 111 1R R u R u R R R u R u R u ++= ++= 根据翻转条件,令上式右方为零,得此时的输入电压 th Z 2 1 o 21in U U R R u R R u ==-= U th 称为阈值电压。滞回电压比较器的直流传递特性如图4所示。设输入电压初始值小于-U th ,此时u o = -U Z ;增大u in ,当u in =U th 时,运放输出状态翻转,进入正饱和区。如果初始时刻运放工作在正饱和区,减小u in ,当u in = -U th 时,运放则开始进入负饱和区。 RC 振荡电路 积分电路 方波 三角波 反相输入的滞回比较 生成 生成 输入 积分电路 输入

单道脉冲分析课程设计

课程设计报告 课程设计题目: 实验单道脉冲分析器的改进 实验单道脉冲分析器的改进 一、设计时间:2011年6月06日-2011年6月17日 二、设计地点:核电子实验及宿舍 三、设计任务:以课本的理论为基础,到网上或图书馆查找相关资料,寻找自己感兴趣的电路进行模仿设计,设计完成后再进行仿真测试。 四、设计目的:通过Multisim的电路设计,对《核电子学与核辐射仪器》所学内容有更进一步的理解,加深印象,使所学知识得以巩固和提高,全面掌握核电子学各模块电路的设计,实现设计、模拟仿真的技术环节,提高分析问题解决问题的能力;培养我们的动手能力和遵守纪律的高尚情操还有对待工作严肃认真、一丝不苟、实事求是、不畏艰辛的优良作风,为今后从事技术工作奠定坚实的基础。 五、设计要求: 1、掌握Multisim的使用方法;

2、掌握所画电路的工作原理; 3、掌握Multisim电路图的设计; 4、基本掌握使用Multisim进行模拟仿真。 六、设计原理及方法: 单道脉冲分析器是一种对核脉冲信号幅度信息甄别测量的装置,虽然现在一般多用多道脉冲幅度分析器测量能谱,但由于单道具有结构简单、价格便宜,还可选择感兴趣的幅度范围或选取一定能量范围的信号作为测量对象等优点,所以它在核探测领域仍有用武之地。 单道脉冲幅度分析器(图1)包括两个甄别器,一个叫上甄别器,甄别阀用V上表示;另一个叫下甄别器,甄别阀用V下表示;上、下甄别阀之差称为道宽,用ΔV表示,即:ΔV = V上– V下;除了两个甄别器外,还有一个反符合电路。当信号V in 延时可控高压脉冲发生器的设计 延时可控高压脉冲发生器的设计 1引言 以往研制的高压脉冲发生器采用V型管作为高压脉冲形成级,该管为冷阴极结构形式,一般工作电压在10~15kV范围内,输出高压脉冲相对外触发的延时随直流供电电压的不同而有较大变化,抖动也较大,且长时间工作后,延时和抖动都要增大。 用于触发Marx发生器及高电压脉冲触发装置需要更高的高压触发脉冲,且需在5~30kV范围内连续可调,具有前沿快、延时准确稳定、抖动小、抗干扰能力强等性能。 设计高压脉冲形成级是本机的重点,关键是选择能满足本机各项技术指标要求的高电压、大电流、快速开关管。 为了提高触发系统的延时精度,采用精度为10ns的数字延时单元,延时在10ns~99μs范围,步进10ns,以CPU8031为控制核心的集成电路实现人机对话,增强可靠性和先进性。 直流高压供电采用DC/DC变换技术,封装在金属盒内,实现了电源小型化,增强了抗干扰能力。 2发生器的构成及其工作原理 2.1高压脉冲发生器结构 延时可控高压脉冲发生器结构框图,是由外触发控制电路、单片机控制电路、延时电路、驱动电路、直流高压电路及高压脉冲形成及 输出电路等组成。 图1高压脉冲发生器组成框图 外触发控制电路是将外触发信号通过内部的比较器进行电压比较,再通过光电隔离器使外触发信号的地与控制线路的地分开,以屏蔽和减弱外界的电磁干扰及地干扰,增强本机的抗干扰能力。 单片机控制电路、延时电路是通过单片机实现人机对话,来预置延时电路的延时时间,达到延时可控目的。 驱动电路是将延时电路输出幅度较低的脉冲信号变为较高幅度的脉冲信号,用以驱动后级高压脉冲形成电路。 直流高压电路采用DC/DC变换,低压24V经振荡电路产生频率较高交流信号,再经高频脉冲变压器升压及多级倍压输出5~30kV连续可调的直流高压,为高压脉冲形成电路供电。 高压脉冲形成输出电路是本机重要部分,主要是形成和输出负高压脉冲。 2.2工作原理 由键盘键入所要求的延时时间,通过8031芯片内部程序控制延时器所要求的动作时间。当外触发信号输入时,外触发控制电路开始工作,输出一个脉冲信号触发延时电路,延时器开始计数,当达到所设定的时间时,延时器停止工作,同时输出一个脉冲信号,触发驱动电路,使驱动电路输出一个正脉冲信号,使开关管S导通,储能电容C经S向负载电阻放电(见图2),从而在与同轴电缆相匹配的负载 波形发生器 徐威 (宁波大学信息科学与工程学院,浙江宁波315211) 摘要:使用题目指定的综合测试板上的NE555芯片和一片四运放LM324芯片制作一个频率可变的同时输出脉冲波、锯齿波、一次和三次正弦波。进行方案设计,制作出实际电路使其达到实验要求的各项指标。 一、设计任务与要求 使用题目指定的综合测试板上的NE555芯片和一片四运放LM324芯片,设计制作一个频率可变的同时输出脉冲波、锯齿波、正弦波Ⅰ、正弦波Ⅱ的波形产生电路。给出方案设计、详细电路图和现场自测数据及波形。 设计制作要求如下: 1、同时四通道输出、每通道输出脉冲波、锯齿波、正弦波Ⅰ、正弦波Ⅱ中的一种波形,每通道输出的负载电阻均为600欧姆。 2、四种波形的频率关系为1:1:1:3(3次谐波);脉冲波、锯齿波、正弦波Ⅰ输出频率范围为8KHz~10KHz,输出电压幅度峰峰值为1V;正弦波Ⅱ输出频率范围为24KHz~30KHz,输出电压幅度峰峰值为9V。脉冲波、锯齿波和正弦波输出波形应无明显失真(使用示波器测量时)。 频率误差不大于10%;通带内输出电压幅度峰峰值误差不大于5%。脉冲波占空比可调整。 3、电源只能选用+10V单电源,由稳压电源供给,不得使用额外电源。 4、要求预留脉冲波、锯齿波、正弦波Ⅰ、正弦波Ⅱ和电源的测试端子。 5、每通道输出的负载电阻600欧姆应标清楚、至于明显位置,便于检查。 6、翻译:NE555和LM324的数据手册(器件描述、特点、应用、绝对参数、电参数)。 二、方案设计与论证 1.原始方案: 在使用Multisim进行仿真设计的阶段,我想出了两种原始方案,两种方案的大体思路如下。 方案一:使用NE555芯片构成多谐振荡器,输出方波,通过锯齿波发生电路产生 快速脉冲群测试原理及对策 快速瞬变脉冲群干扰机理 1.实验的目的 电快速瞬变脉冲群EFT试验的目的是验证电子设备机械开关对电感性负载切换、继电器触点弹跳、高压开关切换等引起的瞬时扰动的抗干扰能力。这种试验方法是一种耦合到电源线路、控制线路、信号线路上的由许多快速瞬变脉冲组成的脉冲群试验。容易出现问题的场合有电力设备或监控电网的设备、使用在工业自动化上面的设备、医疗监护等检测微弱信号设备。 2.干扰的特点 EFT的特点是上升时间快,持续时间短,能量低,但具有较高的重复频率。EFT一般不会引起设备的损坏,但由于其干扰频谱分布较宽,会对设备正常工作产生影响。其干扰机理为EFT对线路中半导体结电容单向连续充电累积,引起电路乃至设备的误动作。 1)电快速瞬变脉冲群测试及相关要求 不同的电子、电气产品标准对EFT抗扰度试验的要求是不同的,但这些标准关于EFT抗扰度试验大多都直接或间接引用GB/T17626.4这一电磁兼容基础标准,并按其中的试验方法进行试验。下面就简要介绍一下该标准的内容。 2)信号发生器和试验波形 a)信号发生器 其中,U为高压直流电源,Rc为充电电阻,Cc为储能电容,Rs为内部的放电电阻,Rm为阻抗匹配电阻,Cd为隔直电容,R0为外部的负载电阻,Cc的大小决定了单个脉冲的能量,Cc和Rs的配合决定了脉冲波的形状(特别是脉冲的持续时间),Rm决定了脉冲群发生器的输出阻抗(标准规定是50Ω),Cd则隔离了脉冲群发生器输出波形中的直流成分,免除了负载对脉冲群发生器工作的影响。b)实验波形 试验发生器性能的主要指标有三个:单个脉冲波形、脉冲的重复频率和输出电压峰值。GB/T17626.4要求试验发生器输出波形应如图1,2所示。 正 文 1 选题背景 波形发生器又名信号源,广泛应用于电子电路、自动控制和科学试验等领域。雷达、通信、宇航、遥控遥测技术和电子系统等领域都随处可见波形发生器的应用。如今作为电子系统心脏的信号源的性能很大程度上决定了电子设备和系统的性能的提高,因此随着电子技术的不断发展,现今对信号源的频率稳定度、频谱纯度和频率范围以及信号波形的形状提出越来越高的挑战。 1.1指导思想 利用NE555构成多谐振荡器产生方波,根据LM324输出的锯齿波分别通入低通滤波器和高通滤波器就可以输出正弦波Ⅰ、正弦波Ⅱ。 1.2 方案论证 方案一:使用NE555芯片构成多谐振荡器,输出方波,通过锯齿波发生电路产生锯齿波,然后通过一个KHz f H 10=的低通滤波器,通过滤波产生一次,8KHz 到10KHz 的正弦波,然后再让锯齿波通过一个24KHz~30KHz 的带通滤波器,输出三次正弦波。其中滤出三次谐波的理论依据是,由于锯齿波是一个关于t 的周期函数,并且满足狄里赫莱条件:在一个周期内具有有限个间断点,且在这些间断点上,函数是有限值;在一个周期内具有有限个极值点;绝对可积。 方案二:使用功放构成文森桥式震荡电路,产生出8KHz~10KHz 的正弦波。接着是用NE555芯片,搭建出施密特触发电路,产生脉冲波输出;将脉冲波分别输入一个KHz f H 10=的低通滤波器和24KHz~30KHz 的带通滤波器电路中,产生一次和三次正弦波。 最初方案设计的大体思路在方案一和方案二之间犹豫不决,于是将两个电路的大体电路都进行了简单的设计,发现方案二存在很多的问题很难解决。 问题一:如果使用文森桥式震荡器产生正弦波,改变震荡频率就需要改变RC 常数,要同时改变两个R (在实际电路中,同时改变两个电容的值是很复杂的,而且这样也无法得到一个8KHZ~10KHz 的连续的频率),需要双滑动变阻器并且要保证滑动变阻器改变的值完全相同,有一定困难。 问题二:NE555芯片搭建出来的是一个简单的施密特触发器,输入正弦波之后,输出的脉冲波的占空比是不可以调整的,不满足实验要求的占空比可调的条件。要是施密特触发器产生的脉冲波的占空比可调会是该电路进一步复杂化。 问题三:LM324芯片的功放不够,由于有Ω600负载电阻的限制,输出波形的峰峰值不能简单的通过电阻的分压来实现。 鉴于方案二存在的问题能以解决,我们就确定选择方案一的整体思路进行方案的设计。 1.3 基本设计任务 用555 定时器和四运放LM324 设计并制作一个频率可变的、能够同时输出脉冲波、延时可控高压脉冲发生器的设计

2013电子设计竞赛复试题波形发生器资料

快速脉冲群测试原理与分析

波形发生器的设计全解