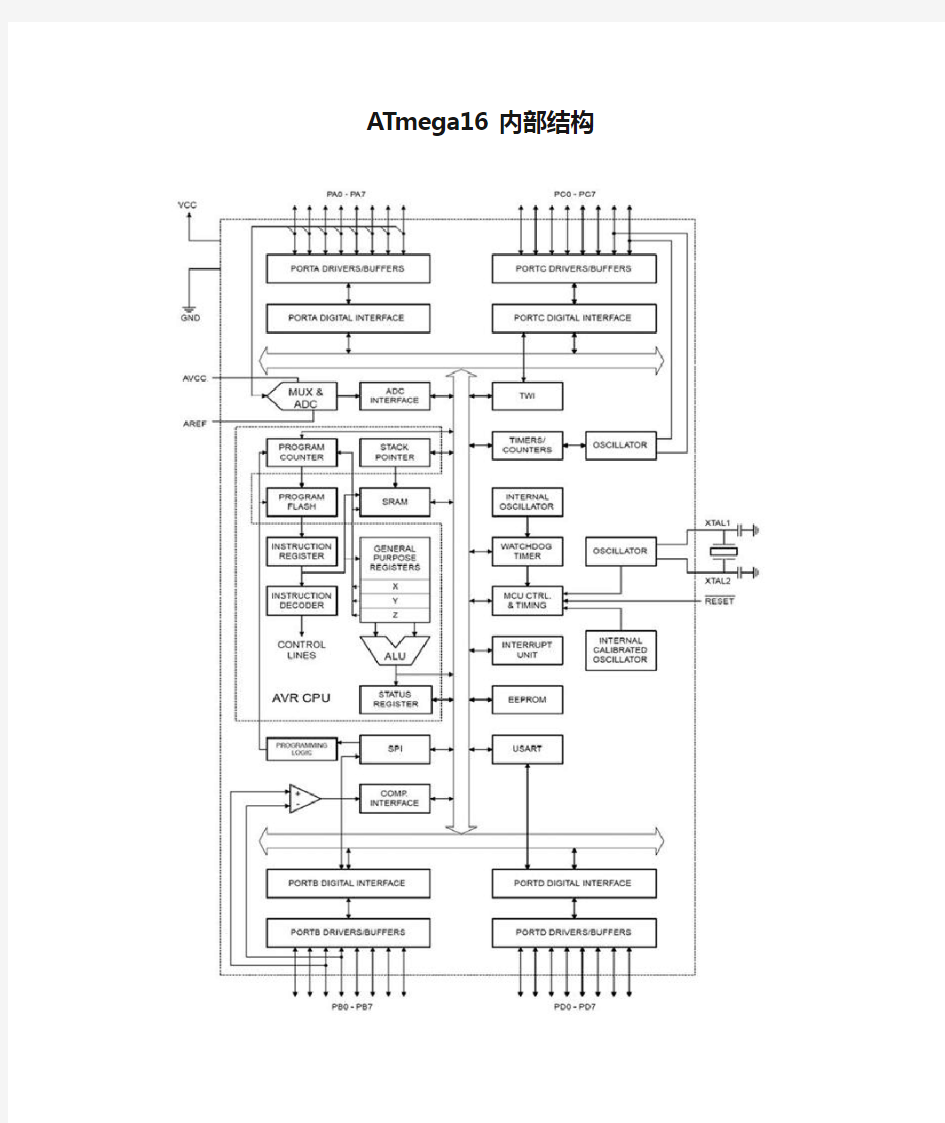

ATmega16内部结构

ATmega16内部结构

.3.1 A VR中央处理器CPU

A VR CPU是单片机的核心部分,它由运算逻辑单元ALU、程序计数器PC、指令寄存器、指令译码器等部件组成。

一.运算逻辑单元ALU

运算逻辑单元ALU的功能是进行算术运算和逻辑运算,可对半字节(4位)、单字节等数据进行操作。如能完成加、减、自动加1、自动减1、比较等算术运算和与、或、异或、

求补、循环移位等逻辑操作。操作结果的状态,如产生进位、结果为零等状态信息将影响到状态寄存器SREG相应的标志位。

运算逻辑单元ALU还包含一个布尔处理器,用来处理位操作。它可执行置位、清零、取反等操作。

ATmega16的ALU还能实现无符号数、有符号数以及浮点数的硬件乘法操作。一次硬件乘法操作的时间为2个时钟周期。

二.程序计数器PC、指令寄存器和指令译码器

程序计数器PC用来存放下一条需要执行指令在程序存储器空间的地址(指向Flash空间)。取出的指令存放在指令寄存器中,然后送入指令译码器产生各种控制信号,控制CPU

的运行(执行指令)。

A VR一条指令的长度大多数为16位,还有少部分为32位,因此A VR的程序存储器结构实际上是以字(16位)为一个存储单元的。ATmega16的程序计数器为13位,正好满足了对片内8K字(即手册上的16K字节)的Flash程序存储器空间直接寻址的需要,因此也不能(不支持)在外部扩展程序存储器。

A VR CPU在译码执行一条指令的同时,就将PC中指定的Flash单元中的指令取出,放入指令寄存器中(图中的Instruction Register),构成了一级流水线运行方式。A VR采用

一级流水线技术,在当前指令执行的时候,就取出下一条将要执行的指令,加上大多数AVR 指令的长度是一个字,就使得A VR CPU实现了一个时钟周期执行一条指令。采用这种结构,减少了取指令的次数,大大提高了CPU的运行速度,同时也提高了取指令操作的(系统的)可靠性。而在其它的CISC以及类似的RISC结构的单片机中,外部振荡器的时钟被分频降低

到传统的内部指令执行周期,这种分频最大达12倍(例如,标准8031结构的单片机)。三. 通用工作寄存器组

在A VR中,由命名为R0~R31的32个8位通用工作寄存器构成一个“通用快速工作寄存器组”,图2-5为通用快速工作寄存器组的结构图。

A VR CPU中的ALU与这32个通用工作寄存器组直接相连,为了使ALU能够高效和灵活地对寄存器组进行访问操作,通用寄存器组提供和支持ALU使用4种不同的数据输入/输出

的操作方式:

终提供一个8位源操作数,并保存的一个8位结果

终提供两个8位源操作数,并保存的一个8位结果

终提供两个8位源操作数,并保存的一个16位结果

终提供一个16位源操作数,并保存的一个16位结果

因此,A VR大多数操作工作寄存器组的指令都可以直接访问所有的寄存器,而且多数这样的指令的执行时间是一个时钟周期。例如,从寄存器组中取出两个操作数,对操作数实施处理,处理结果回写到目的寄存器中。这三个过程是在一个时钟周期内完成的,构成一个完整的ALU指令操作。

在传统的基于累加器结构的单片机中(如8051),则需要大量的程序代码来完成和实现在累

加器和存储器之间的数据传送。如上面所介绍的操作过程就需要三条指令来实现:第一条完成从寄存器中取出源操作数;第二条完成对操作数实施处理;第三条将处理结果回写。这样就构成了累加器和存储器之间数据传送的瓶颈,影响了指令运行效率。而在A VR单片机中,由于采用了32个通用工作寄存器构成快速存取寄存器组,相当于用32个通用工作寄存器代替了累加器,从而避免了在传统结构中的那种由于累加器和存储器之间频繁的数据传送交换而形成的瓶颈现象,又进一步提高了指令的运行效率和速度。

在A VR中,通用寄存器组与片内的数据存储器SRAM处在相同的空间,32个通用寄存器被直接映射到用数据空间的前32个地址,如图2-5所示。虽然寄存器组的物理结构与SRAM 不同,但是这种内存空间的组织方式为访问工作寄存器提供了极大的灵活性,如可以利用地址指针寄存器X、Y或Z实现对通用寄存器组的间接寻址操作。

Atmage 引脚图

引脚名称引脚功能说明

VCC 电源正

GND 电源地

端口A(PA7..PA0) 端口A 做为A/D 转换器的模拟输入端。端口A 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口A 处于高阻状态。

端口B(PB7..PB0) 端口B 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口B 处于高阻状态。

端口B 也可以用做其他不同的特殊功能.

端口C(PC7..PC0) 端口C 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口C 处于高阻状态。如果JTAG接口使能,即使复位出现引脚PC5(TDI)、PC3(TMS)与PC2(TCK)的上拉电阻被激活。端口C 也可以用做其他不同的特殊功能.

端口D(PD7..PD0) 端口D 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口D 处于高阻状态。端口D 也可以用做其他不同的特殊功能.

RESET 复位输入引脚。持续时间超过最小门限时间的低电平将引起系统复位。门限时间见P36Table 15。持续时间小于门限间的脉冲不能保证可靠复位。

XTAL1 反向振荡放大器与片内时钟操作电路的输入端。

XTAL2 反向振荡放大器的输出端。

AVCC AVCC是端口A与A/D转换器的电源。不使用ADC时,该引脚应直接与VCC 连接。使用ADC时应通过一个低通滤波器与VCC 连接。

AREF A/D 的模拟基准输入引脚。

2.1.3 ATmega16 内核介绍

右边为AVR 结构的方框图

为了获得最高的性能以及并行性,AVR 采用了Harvard 结构,具有独立的数据和程序总线。程序存储器里的指令通过一级流水线运行。CPU 在执行一条指令的同时读取下一条指令( 在本文称为预取)。这个概念实现了指令的单时钟周期运行。程序存储器是可以在线编程的FLASH。

快速访问寄存器文件包括32 个8 位通用工作寄存器,访问时间为一个时钟周期。从而实现了单时钟周期的ALU 操作。在典型的ALU 操作中,两个位于寄存器文件中的操作数同时被访问,然后执行运算,结果再被送回到寄存器文件。整个过程仅需一个时钟周期。

寄存器文件里有6 个寄存器可以用作3 个16 位的间接寻址寄存器指针以寻址数据空间,实现高效的地址运算。其中一个指针还可以作为程序存储器查询表的地址指针。这些附加的功能寄存器即为16 位的X、Y、Z 寄存器。

ALU支持寄存器之间以及寄存器和常数之间的算术和逻辑运算。ALU也可以执行单寄存器操作。运算完成之后状态寄存器的内容得到更新以反映操作结果。

程序流程通过有/ 无条件的跳转指令和调用指令来控制,从而直接寻址整个地址空间。大多数指令长度为16 位,亦即每个程序存储器地址都包含一条16 位或32 位的指令。

程序存储器空间分为两个区:引导程序区(Boot 区) 和应用程序区。这两个区都有专门的锁定位以实现读和读/ 写保护。用于写应用程序区的SPM 指令必须位于引导程序区。

在中断和调用子程序时返回地址的程序计数器(PC) 保存于堆栈之中。堆栈位于通用数据SRAM,因此其深度仅受限于SRAM 的大小。在复位例程里用户首先要初始化堆栈指针SP。这个指针位于I/O 空间,可以进行读写访问。数据SRAM 可以通过5 种不同的寻址模

式进行访问。

AVR 存储器空间为线性的平面结构。

AVR有一个灵活的中断模块。控制寄存器位于I/O空间。状态寄存器里有全局中断使能位。每个中断在中断向量表里都有独立的中断向量。各个中断的优先级与其在中断向量表的位置有关,中断向量地址越低,优先级越高。

I/O 存储器空间包含64 个可以直接寻址的地址,作为CPU 外设的控制寄存器、SPI,以及其他I/O 功能。映射到数据空间即为寄存器文件之后的地址0x20 - 0x5F。

Atmage 16最小系统及通信部分版图