基于AM335x SDK6.0去掉EEPROM

基于AM335x SDK6.0去掉EEPROM验证ID功能

以startkit为例,默认执行startkit配置。

I.Uboot

Board.c文件

?S_init函数,

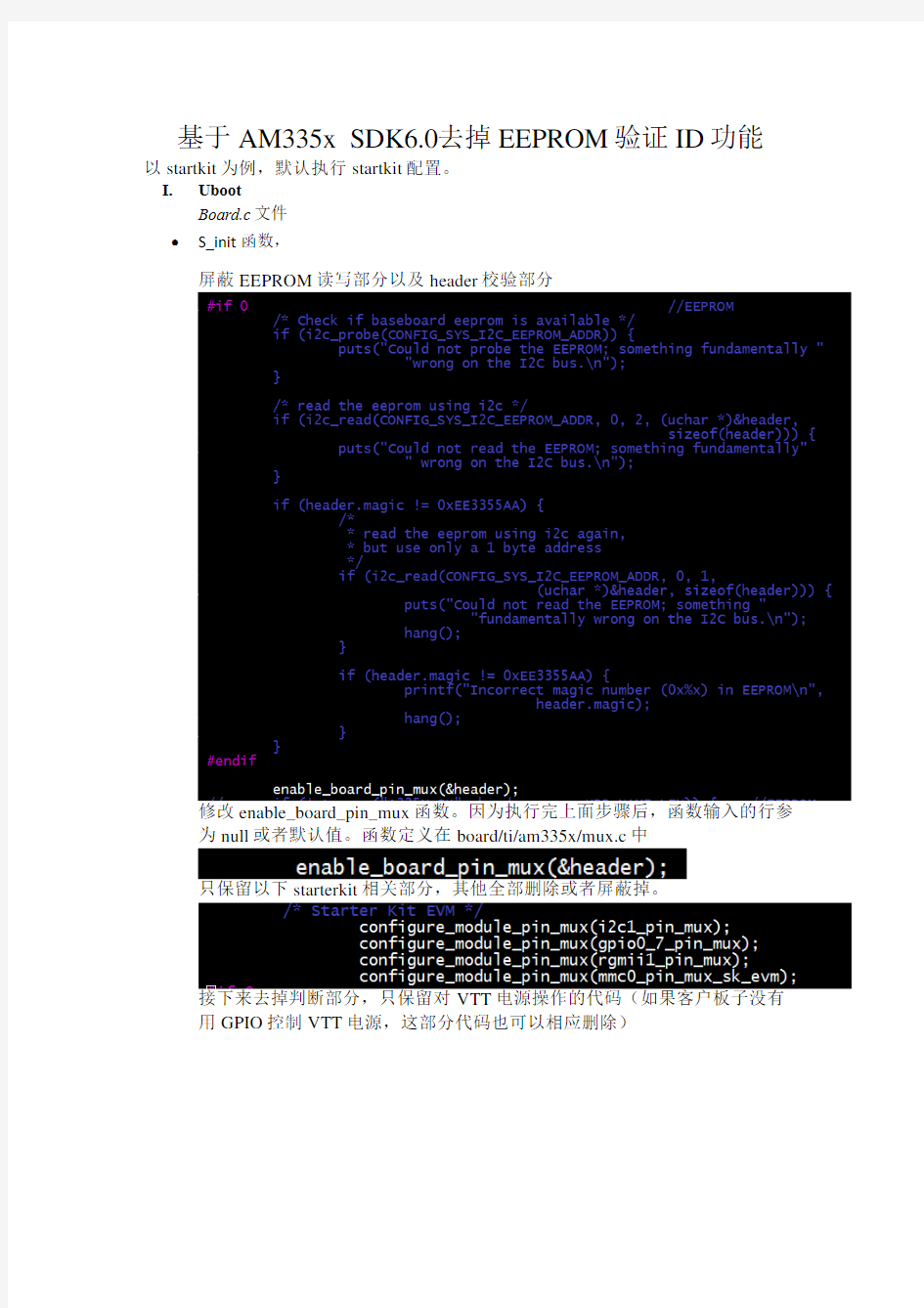

屏蔽EEPROM读写部分以及header校验部分

修改enable_board_pin_mux函数。因为执行完上面步骤后,函数输入的行参为null或者默认值。函数定义在board/ti/am335x/mux.c中

只保留以下starterkit相关部分,其他全部删除或者屏蔽掉。

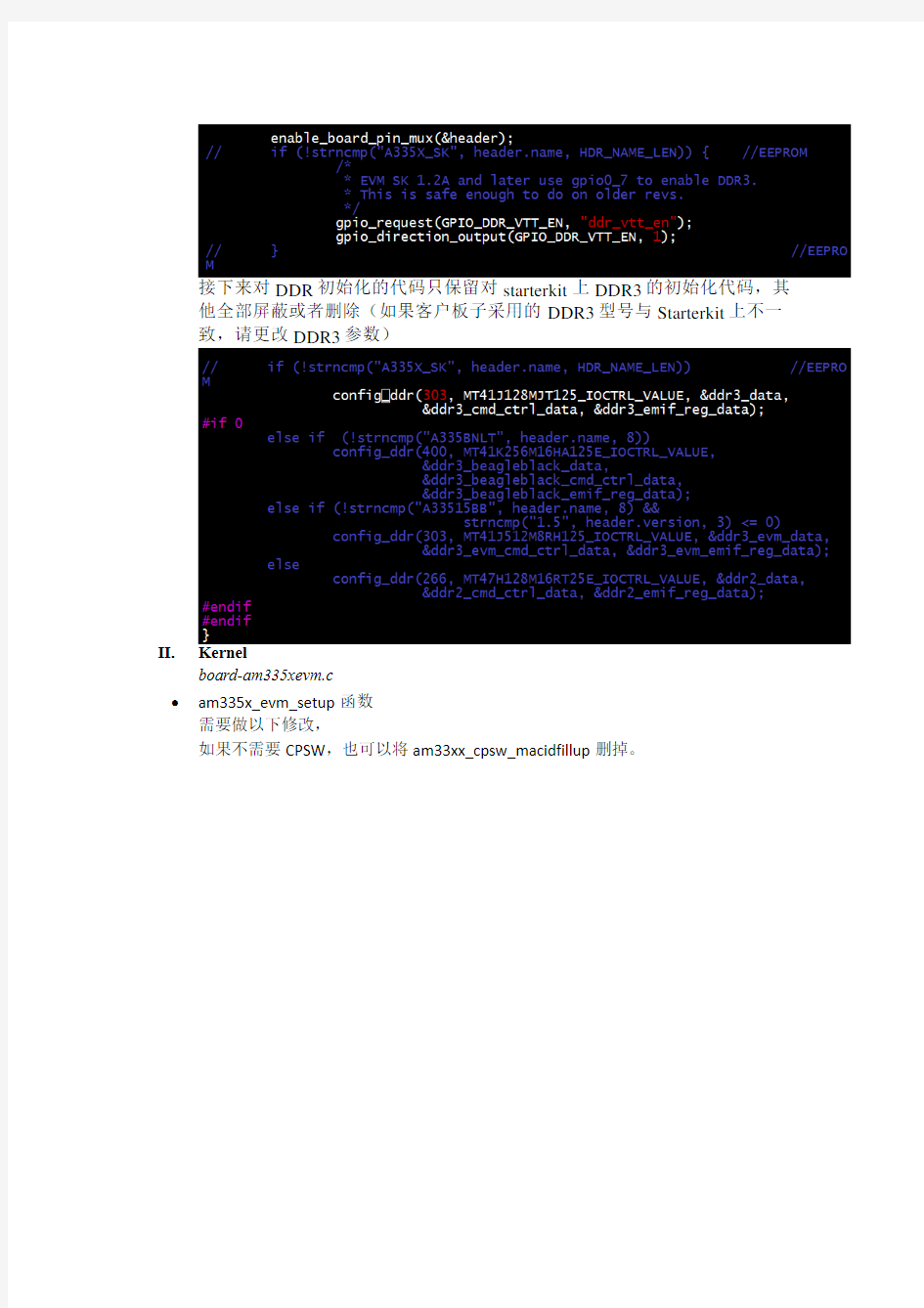

接下来去掉判断部分,只保留对VTT电源操作的代码(如果客户板子没有用GPIO控制VTT电源,这部分代码也可以相应删除)

接下来对DDR初始化的代码只保留对starterkit 上DDR3的初始化代码,其他全部屏蔽或者删除(如果客户板子采用的DDR3型号与Starterkit上不一致,请更改DDR3参数)

II.Kernel

board-am335xevm.c

?am335x_evm_setup函数

需要做以下修改,

如果不需要CPSW,也可以将am33xx_cpsw_macidfillup删掉。

去掉以下EEPROM检验代码

仅保留对starterkit初始化代码,

至此,EEPROM相关效验代码已经去掉,程序将默认执行starterkit EVM的初始化。

III.增加d_can驱动

这里再多提一点,在kernel里如何在starterkit基础上增加CAN的初始化,因为starterkit本身不支持CAN接口。

在board-am335xevm.c下

首先在结构体evm_sk_dev_cfg增加,

其次在d_can_init函数中增加“case EVM_SK:”并且去掉if(profile == PROFILE_1),如下,

I2C总线应用下的EEPROM测试

I2C总线应用下的EEPROM测试 作者:盛帅能 作者单位:华越微电子有限公司,浙江,绍兴,312000 刊名: 半导体技术 英文刊名:SEMICONDUCTOR TECHNOLOGY 年,卷(期):2004,29(4) 被引用次数:2次 本文读者也读过(10条) 1.李文雄.陆俭国.刘明生.商书元.LI Wen-xiong.LU Jian-guo.LIU Ming-sheng.SHANG Shu-yuan基于I2C总线的EEPROM在智能电器中的应用[期刊论文]-低压电器2005(11) 2.庞媛媛.崔建明.PANG Yuan yuan.CUI Jian-ming一种I2C总线接口设计在EEPROM的应用[期刊论文]-电脑知识与技术2011,07(30) 3.苏琦.刘宇.田敬民EEPROM基于I2C总线的一种读写方法[期刊论文]-山西电子技术2001(1) 4.郭文华.GUO Wen-hua基于I2C总线的串行E2PROM及其应用[期刊论文]-常熟理工学院学报2008,22(10) 5.麦胤.柳沁.Mai Yin.Liu Qin基于Nios Ⅱ的EEPROM Controller Core的设计[期刊论文]-自动化仪表 2008,29(1) 6.杨正进.王玉霞基于I2C总线的EEPROM与单片机接口技术[期刊论文]-重庆工学院学报2001,15(2) 7.刘冰.杜道山.周士侃.李从心基于I2C总线协议的EEPROM与DSP的接口技术[期刊论文]-电子工程师2004,30(9) 8.李和太.蒋晶鑫.陆虹.LI He-tai.JANG Jing-xin.LU Hong嵌入式串行EEPROM研究[期刊论文]-微处理机2007,28(1) 9.徐飞.贺祥庆.张莉.XU Fei.HE Xiang-qing.ZHANG Li一种40ns 16kb EEPROM的设计与实现[期刊论文]-微电子学2005,35(2) 10.意法半导体推出超小型封装的增强型512 kbit I2C和SPI低压串行EEPROM存储器[期刊论文]-电子与电脑 2005(5) 引证文献(2条) 1.沈华.王俞心基于FPGA的I2C总线主控器的设计与实现[期刊论文]-航空计算技术 2007(6) 2.张必超存储器测试技术及其在质量检验中的应用研究[学位论文]硕士 2005 本文链接:https://www.360docs.net/doc/0318601233.html,/Periodical_bdtjs200404018.aspx

单片机内的Flash与EEPROM作用及区别(精)

单片机内的 Flash 与 EEPROM 作用及区别 单片机运行时的数据都存在于 RAM (随机存储器中, 在掉电后 RAM 中的数据是无 法保留的,那么怎样使数据在掉电后不丢失呢?这就需要使用 EEPROM 或FLASHROM 等 存储器来实现。在传统的单片机系统中, 一般是在片外扩展存储器, 单片机与存储器之间通 过 IIC 或 SPI 等接口来进行数据通信。这样不光会增加开发成本,同时在程序开发上也要花 更多的心思。在 STC 单片机中内置了 EEPROM (其实是采用 IAP 技术读写内部 FLASH 来 实现 EEPROM ,这样就节省了片外资源,使用起来也更加方便。下面就详细介绍 STC 单 片机内置 EEPROM 及其使用方法。 flash 是用来放程序的,可以称之为程序存储器,可以擦出写入但是基本都是整个扇区进行的 . 一般来说单片机里的 flash 都用于存放运行代码,在运行过程中不能改; EEPROM 是用来保存用户数据,运行过程中可以改变,比如一个时钟的闹铃时 间初始化设定为 12:00,后来在运行中改为 6:00,这是保存在 EEPROM 里, 不怕掉电,就算重新上电也不需要重新调整到 6:00 下面是网上详细的说法,感觉不错:

FLASH 和 EEPROM 的最大区别是 FLASH 按扇区操作, EEPROM 则按字节操作, 二者寻址方法不同,存储单元的结构也不同, FLASH 的电路结构较简单,同样容量占芯片面积较小,成本自然比 EEPROM 低,因而适合用作程序存储器, EEPROM 则更多的用作非易失的数据存储器。当然用 FLASH 做数据存储器也行, 但操作比EEPROM 麻烦的多,所以更“人性化”的 MCU 设计会集成 FLASH 和 EEPROM 两种非易失性存储器,而廉价型设计往往只有 FLASH ,早期可电擦写型 MCU 则都是EEPRM 结构,现在已基本上停产了。 在芯片的内电路中, FLASH 和 EEPROM 不仅电路不同,地址空间也不同,操作方法和指令自然也不同, 不论冯诺伊曼结构还是哈佛结构都是这样。技术上, 程序存储器和非易失数据存储器都可以只用 FALSH 结构或 EEPROM 结构, 甚至可以用“变通”的技术手段在程序存储区模拟“数据存储区” ,但就算如此,概念上二者依然不同,这是基本常识问题。 EEPROM :电可擦除可编程只读存储器, Flash 的操作特性完全符合 EEPROM 的定义,属 EEPROM 无疑,首款 Flash 推出时其数据手册上也清楚的标明是EEPROM ,现在的多数 Flash 手册上也是这么标明的,二者的关系是“白马”和 “马” 。至于为什么业界要区分二者, 主要的原因是 Flash EEPROM 的操作方法和传统 EEPROM 截然不同,次要的原因是为了语言的简练,非正式文件和口语中Flash EEPROM 就简称为 Flash , 这里要强调的是白马的“白” 属性而非其“马” 属性以区别 Flash 和传统 EEPROM 。 Flash 的特点是结构简单, 同样工艺和同样晶元面积下可以得到更高容量且大数据量 下的操作速度更快,但缺点是操作过程麻烦,特别是在小数据量反复重写时, 所以在 MCU 中 Flash 结构适于不需频繁改写的程序存储器。 很多应用中,需要频繁的改写某些小量数据且需掉电非易失,传统结构的EEPROM 在此非常适合, 所以很多 MCU 内部设计了两种 EEPROM 结构, FLASH

常用串行EEPROM芯片

1 Features ?Serial Peripheral Interface (SPI) Compatible ?Supports SPI Modes 0 (0,0) and 3 (1,1) ?Low-voltage and Standard-voltage Operation –2.7 (V CC = 2.7V to 5.5V)? 3.0 MHz Clock Rate (5V) ?8-byte Page Mode ?Block Write Protection –Protect 1/4, 1/2, or Entire Array ?Write Protect (WP) Pin and Write Disable Instructions for Both Hardware and Software Data Protection ?Self-timed Write Cycle (10 ms max)?High Reliability –Endurance: One Million Write Cycles –Data Retention: 100 Years ?Automotive Grade Devices Available ? 8-lead PDIP and 8-lead JEDEC SOIC Packages Description The AT25010/020/040 provides 1024/2048/4096 bits of serial electrically erasable programmable read only memory (EEPROM) organized as 128/256/512 words of 8bits each. The device is optimized for use in many industrial and commercial applica-tions where low-power and low voltage operation are essential. The AT25010/020/040is available in space saving 8-lead PDIP and 8-lead JEDEC SOIC packages. The AT25010/020/040 is enabled through the Chip Select pin (CS) and accessed via a 3-wire interface consisting of Serial Data Input (SI), Serial Data Output (SO), and Serial Clock (SCK). All programming cycles are completely self-timed, and no sepa-rate ERASE cycle is required before WRITE. BLOCK WRITE protection is enabled by programming the status register with one of four blocks of write protection. Separate program enable and program disable instruc-tions are provided for additional data protection. Hardware data protection is provided via the WP pin to protect against inadvertent write attempts. The HOLD pin may be used to suspend any serial communication without resetting the serial sequence. Pin Configurations 8-lead PDIP

EEPROM电路设计原理与工艺分析

微 处 理 机 M I CROPROCE SSORS EEP ROM 电路设计原理与工艺分析 刘丽娜,程显侠,刘宝娟 (中国电子科技集团公司第四十七研究所,沈阳110032) 摘 要:EEPROM (electrica lly erasable ,prog ra mm ab le ,read-only m e m ory),是一种电可擦除可编程只读存储器电路,它具有易于使用、价格低廉等特点。由于它的可编程特性,加上能以非常低的成本获得,因此,几乎在每一种电子产品中都可见到EEPROM 的身影,是目前业界使用最普遍的非易失性存储器之一。介绍了EEPROM 电路的设计原理与生产工艺,并对其中的关键技术进行了分析。 关键词:可擦除;可编程;存储器 中图分类号:TN 47 文献标识码:B 文章编号:1002-2279(2008)03-0037-02 The Anal ysis of Theory and T echn i cs of EEPROM C ircu it LIU L i-na ,C HENG X ian-x ia ,LIU Bao-juan (T he 47th Research Instit ute of Ch i na E lectronics T echnology Group Corporation ,Shenyang 110032,Ch i na) Abstract :EEPROM (e lectrica ll y erasab le ,progra mm able ,read -on l y m e m ory ),is a m e m ory c ircuit of e lectric erasable an d read -on ly .It is pron e to use and its price is cheap .Because o f its progra mm ab le and cheap cos,t it is a l m ost used in each kind of e l e ctronic produc.t It is universal one o f nonvo latile m e m ory used i n se m iconductor fie l d no w .The arti c le introduces EEPROM electrocircuit 's desi g n princ i p le and production craf,t m eanw h ile ananlyzes its pivo tal technique i n si d e . K ey w ords :E rasable ;Prog ra mm ab le ;M e m ory 1 引 言 存储器是一种能存放数据和程序的器件,是计 算机的主要部件,在许多电子设备中,它是必不可少的。存储芯片是I C 市场的支柱产品,也是用量最多的VLSI 器件。随着集成电路技术的飞速发展,存储芯片的集成度、容量、可靠性得到了很大的提高,EEPRO M 制造技术也进一步成熟,由于EEPROM 存储器可以用电学方法在线将存储内容一次全部擦除,或者按字节擦除,然后再重新写入,与EPROM 相比,其存储单元所需的写入和擦除的能量低,擦写和读取的速度快,而且能在线擦写。另外,新一代的EEPRO M 已将编程所需的高电压发生器由片外置入片内,所以芯片只需单电源供电,因而广泛应用于整机及通讯系统中。 2 EEPROM 设计原理 2.1 EEPRO M 的分类 目前,市场上的EEPROM 主要有串行接口 EEPROM 和并行接口EEPROM 两种产品。2.1.1 串行接口EEPROM 串行接口EEPROM 是目前使用的非易失性存储器中灵活性最高的类型。与其它NVM 比较,串行接口EEPROM 器件提供更少的引脚数,更小的封装,更低的电压和更低的功耗。串行接口的EEPROM 被用于电子行业的各个领域,包括汽车,电信,医疗,工业和个人计算机等相关市场。主要用于存储个人优先数据和配置/调整数据。其主要的内部结构如图1所示。 其管脚说明如表1所示。 表1 串行接口EEPROM 管脚说明A 0-A1地址输入端口SDA 双向串行数据端口SCL 串行时钟输入端口 W P 写保护端口NC 悬空端口 作者简介:刘丽娜(1979-),女,辽宁省锦州市人,学士,助工,主研方向:计算机及电路设计。 收稿日期:2007-06-19 第3期 2008年6月 No .3 Jun.,2008

串行EEPROM AT24CXX芯片资料

串行EEPROM AT24CXX芯片资料 AT24CXX是美国ATMEL公司的低功耗CMOS串行EEPROM,典型的型号有 AT24C01A/02/04/08/16等5种,它们的存储容量分别是 1024/2048/4096/8192/16384位;也就是128/256/512/1024/2048字节;使用电压级别有5V,2.7V,2.5V,1.8V;本文主要介绍常用的AT24C02即256字节存储器的使用;它具有工作电压宽(2.5~5.5V)、擦写次数多(大于10000次)、写入速度快(小于10ms)等特点。 外行如图: AT24C02的1、2、3脚是三条地址线,用于确定芯片的硬件地址(实验板中直接接地只有一块器件);第8脚和第4脚分别为正、负电源。第5脚SDA 为串行数据输入/输出,数据通过这条双向I2C总线串行传送,SDA和SCL都需要和正电源间各接一个5.1K的电阻上拉。第7脚为WP写保护端,接地时允许芯片执行一般的读写操作。接电源端时不允许对器件写。 24C02中带有片内地址寄存器。每写入或读出一个数据字节后,该地址寄存器自动加1,以实现对下一个存储单元的读写。所有字节均以单一操作方式读取。为降低总的写入时间,一次操作可写入多达8个字节的数据。 ;这是将0100H地址中以下的8个数据写到24C02的01H为首址单元中去的汇编程序可直接在实验板上实验。 ORG 0000H SCL BIT P3.7;定义24C02的串行时钟线 SDA BIT P3.6;定义24C02的串行数据线 LJMP START START:LCALL STAR;调用

MOV R2,#08H;一个数据有8位 MOV DPTR,#0100H;定义源数据的位置LOOP:MOV A,#00H MOVC A,@A+DPTR LCALL SDATA LCALL ACK JC LOOP INC DPTR DJNZ R2,LOOP LCALL STOP;调用停止子程序STAR:SETB SDA SETB SCL NOP NOP NOP NOP CLR SDA NOP NOP NOP NOP CLR SCL RET SDATA:MOV R0,#08H LOOP0:RLC A MOV SDA,C NOP NOP SETB SCL

rom,ram,eeprom,flash区别

ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写。ROM在系统停止供电的时候仍然可以保持数据,而RAM 通常都是在掉电之后就丢失数据,典型的RAM就是计算机的内存。 RAM有两大类,一种称为静态RAM(Static RAM/SRAM),SRAM速度非常快,是目前读写最快的存储设备了,但是它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU 的一级缓冲,二级缓冲。另一种称为动态RAM(Dynamic RAM/DRAM),DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM 相比SRAM要便宜很多,计算机内存就是DRAM的。 DRAM分为很多种,常见的主要有FPRAM/FastPage、EDORAM、SDRAM、DDR RAM、RDRAM、SGRAM以及WRAM等,这里介绍其中的一种DDR RAM。 DDR RAM(Date-Rate RAM)也称作DDR SDRAM,这种改进型的RAM和SDRAM是基本一样的,不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。这是目前电脑中用得最多的内存,而且它有着成本优势,事实上击败了Intel的另外一种内存标准-Rambus DRAM。在很多高端的显卡上,也配备了高速DDR RAM来提高带宽,这可以大幅度提高3D加速卡的像素渲染能力。 内存工作原理:内存是用来存放当前正在使用的(即执行中)的数据和程序,我们平常所提到的计算机的内存指的是动态内存(即DRAM),动态内存中所谓的"动态",指的是当我们将数据写入DRAM后,经过一段时间,数据会丢失,因此需要一个额外设电路进行内存刷新操作。 具体的工作过程是这样的:一个DRAM的存储单元存储的是0还是1取决于电容是否有电荷,有电荷代表1,无电荷代表0。但时间一长,代表1的电容会放电,代表0的电容会吸收电荷,这就是数据丢失的原因;刷新操作定期对电容进行检查,若电量大于满电量的1/2,则认为其代表1,并把电容充满电;若电量小于1/2,则认为其代表0,并把电容放电,藉此来保持数据的连续性。 ROM也有很多种,PROM是可编程的ROM,PROM和EPROM(可擦除可编程ROM)两者区别是,PROM是一次性的,也就是软件灌入后,就无法修改了,这种是早期的产品,现在已经不可能使用了,而EPROM是通过紫外光的照射擦出原先的程序,是一种通用的存储器。另外一种EEPROM是通过电子擦出,价格很高,写入时间很长,写入很慢。 举个例子,手机软件一般放在EEPROM中,我们打电话,有些最后拨打的号码,暂时是存在SRAM中的,不是马上写入通过记录(通话记录保存在EEPROM中),因为当时有很重要工作(通话)要做,如果写入,漫长的等待是让用户忍无可忍的。 FLASH存储器又称闪存,它结合了ROM和RAM的长处,不仅具备电子可擦除可编程(EEPROM)的性能,还不会断电丢失数据同时可以快速读取数据(NVRAM的优势),U 盘和MP3里用的就是这种存储器。在过去的20年里,嵌入式系统一直使用ROM(EPROM)作为它们的存储设备,然而近年来Flash全面代替了ROM(EPROM)在嵌入式系统中的地位,用作存储Bootloader以及操作系统或者程序代码或者直接当硬盘使用(U盘)。 目前Flash主要有两种NOR Flash和NADN Flash。 NOR Flash的读取和我们常见的SDRAM的读取是一样,用户可以直接运行装载在NOR FLASH里面的代码,这样可以减少SRAM的容量从而节约了成本。 NAND Flash没有采取内存的随机读取技术,它的读取是以一次读取一块的形式来进行的,通常是一次读取512个字节,采用这种技术的Flash比较廉价。用户不能直接运行NAND Flash上的代码,因此好多使用NAND Flash的开发板除了使用NAND Flah以外,还作上了一块小的NOR Flash来运行启动代码。 一般小容量的用NOR Flash,因为其读取速度快,多用来存储操作系统等重要信息,而大容量的用NAND FLASH,最常见的NAND FLASH应用是嵌入式系统采用的DOC(Disk On Chip)和我们通常用的"闪盘",可以在线擦除。目前市面上的FLASH 主要来自Intel,AMD,Fujitsu和Toshiba,而生产NAND Flash的主要厂家有Samsung和Toshiba。 NAND Flash和NOR Flash的比较 NOR和NAND是现在市场上两种主要的非易失闪存技术。Intel于1988年首先开发出NOR flash技术,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年,东芝公司发表了NAND flash结构,强调降低每比特的成本,更高的性能,并且象磁盘一样可

I2C EEPROM读写设计与制作

四川理工学院 课程设计书 学院计算机学院 专业计算机科学与技术 班级2013级 4 班 课程嵌入式系统软硬件开发及应用实践 题目I2C EEPROM读写设计与制作 教师杨维剑 学生龚程金黄雨杨坤陈超王俊枭

摘要 随着计算机系统及电子系统的飞速发展,信息的存储也越来越重要,EEPROM (电可擦写可编程只读存储器)是可用户更改的只读存储器(ROM),其可通过高于普通电压的作用来擦除和重编程(重写),断电后存在其中的数据不会丢失,通常用于存放硬件信息,如mac地址、BIOS芯片等,并在嵌入式ARM系统中应用广泛,IIC作为一种常见的总线技术,其方便扩展外围设备的特性使得其应用广泛,AT24C02是一款性价比超高的IIC接口EEPROM,擦写次数多、稳点不易丢失数据,本文将设计并制作ARM系统,并在Linux中实现I2C EEPROM读写。 关键词:ARM,EEPROM,IIC,AT24C02,Linux

目录 一、LinuxI2C驱动--概述 (1) 1.1 设计任务与要求 (1) 1.2 I2C (1) 1.3 硬件 (1) 1.4 软件 (1) 二、硬件电路设计 (2) 2.1 电路设计要求 (2) 2.2 原理图的绘制 (2) 2.2.1电源接口 (2) 2.2.2UART接口 (3) 2.2.3AT24C02接口 (3) 2.3 PCB板的制作 (3) 三、LinuxI2C驱动--I2C总线 (5) 3.1 I2C总线物理结构 (5) 3.2 I2C总线特性 (5) 3.3 开始和停止条件 (6) 3.4 数据传输格式 (6) 3.5 响应 (7) 3.6 总线仲裁 (8) 四、LinuxI2C驱动--解析EEPROM的读写 (9) 4.1 概述 (9) 4.2 设备地址 (9) 4.3 读eeprom (9) 4.4 写eeprom (10) 五、LinuxI2C驱动--访问eeprom (10) 5.1 通过sysfs文件系统访问I2C设备 (10) 5.2 通过devfs访问I2C设备 (11) 5.3 总结 (11) 六、LinuxI2C驱动--浅谈LinuxI2C驱动架构.. 12 6.1 I2C体系结构 (13) 6.2 I2C重要数据结构 (13) 七、LinuxI2C驱动--I2C设备驱动 (14) 7.1 eeprom板级设备资源 (14) 7.2 AT24C02 EEPROM 的I2C设备驱动 (14)

EEPROM.

常用串行EEPROM的编程应用 EEPROM是"Electrically Erasable Programmable Read-only"(电可擦写可编程只读存储器)的缩写,EEPROM在正常情况下和EPROM一样,可以在掉电的情况下保存数据,所不同的是它可以在特定引脚上施加特定电压或使用特定的总线擦写命令就可以在在线的情况下方便完成数据的擦除和写入,这使EEPROM被用于广阔的的消费者范围,如:汽车、电信、医疗、工业和个人计算机相关的市场,主要用于存储个人数据和配置/调整数据。EEPROM又分并行EEPROM和串行EEPROM,并行EEPROM器件虽然有很快的读写的速度,但要使用很多的电路引脚。串行EEPROM器件功能上和并行EEPROM基本相同,提供更少的引脚数、更小的封装、更低的电压和更低的功耗,是现在使用的非易失性存储器中灵活性最高的类型。串行EEPROM按总线分,常用的有I2C,SPI,Microwire总线。本文将介绍这三种总线连接单片机的编程方法。 I2C总线 I2C总线(Inter Integrated Circuit内部集成电路总线)是两线式串行总线,仅需要时钟和数据两根线就可以进行数据传输,仅需要占用微处理器的2 个IO引脚,使用时十分方便。I2C总线还可以在同一总线上挂多个器件,每个器件可以有自己的器件地址,读写操作时需要先发送器件地址,该地址的器件得到确认后便执行相应的操作,而在同一总线上的其它器件不做响应,称之为器件寻址,这个原理就像我们打电话的原理相当。I2C总线产生80年代,由PHLIPS 公司开发,早期多用于音频和视频设备,如今I2C总线的器件和设备已多不胜数。最常见的采用I2C总线的EEPROM也已被广泛使用于各种家电、工业及通信设备中,主要用于保存设备所需要的配置数据、采集数据及程序等。生产I2C总线EEPROM的厂商很多,如ATMEL、Microchip公司,它们都是以24来开头命名芯片型号,最常用就是24C系列。24C系列从24C01到24C512,C后面的数字代表该型号的芯片有多少K的存储位。如ATMEL的24C64,存储位是64K位,也就是说可以存储8K(8192)字节,它支持1.8V到5V电源,可以擦写1百万次,数据可以保持100年,使用5V电源时时钟可以达到400KHz,并且有多种封装可供选择。我们可以很容易的在身边的电器设备中发现它们的身影,如电视中用于保存频道信息,电脑内存条中保存内存大小等相关信息,汽车里用于保存里程信息等等。图一就是ATMEL24C64芯片的PID封装和用于内存条SPD(Serial Presence Detect)上的24芯片。

EEPROM存储器 AT24C02的C语言程序设计

//at24c02头文件,基于IIC接口 #define AddWr 0xae //写数据地址,需要参考24c02芯片文档#define AddRd 0xaf //读数据地址 sbit Sda=P2^5; //定义总线连接端口 sbit Scl=P2^4; sbit WP=P2^0; //写保护,这里不使用 /*------------------------------------------------ 延时程序 ------------------------------------------------*/ void mDelay(unsigned char j) { unsigned int i; for(;j>0;j--) { for(i=0;i<125;i++) {;} } } /*------------------------------------------------ 启动IIC总线 ------------------------------------------------*/ void Start(void) { Sda=1; _nop_();_nop_(); Scl=1; _nop_();_nop_();_nop_();_nop_();_nop_(); Sda=0; _nop_();_nop_();_nop_();_nop_();_nop_();

} /*------------------------------------------------ 停止IIC总线 ------------------------------------------------*/ void Stop(void) { Sda=0; _nop_(); Scl=1; _nop_();_nop_();_nop_();_nop_();_nop_(); Sda=1; _nop_();_nop_();_nop_();_nop_();_nop_(); Scl=0; } /*------------------------------------------------ 应答IIC总线 ------------------------------------------------*/ void Ack(void) { Sda=0; _nop_();_nop_();_nop_(); Scl=1; _nop_();_nop_();_nop_();_nop_();_nop_(); Scl=0; _nop_();_nop_(); } /*------------------------------------------------ 非应答IIC总线 ------------------------------------------------*/ void NoAck(void) { Sda=1; _nop_();_nop_();_nop_(); Scl=1; _nop_();_nop_();_nop_();_nop_();_nop_(); Scl=0; _nop_();_nop_();

EEPROM的应用

导读: 1.EEPROM巧妙应用之单片机章程 2.基于I2C串行通信的EEPROM在电视中的设计应用 3.EEPROM的保护措施在MAXQ环境中 1.EEPROM巧妙应用之单片机章程 引言 全球各单片机生产厂商在MCS-51内核基础上,派生了大量的51内核系列单片机,极大地丰富了MCS-51的种群,致使MCS-51单片机是目前国内应用最广泛的一种单片机型.其中STC公司推出了STC89系列单片机,增加了大量新功能,提高了51的性能,是MCS-51家族中的佼佼者.早期的单片机控制系统,采用单片机加片外EEPROM配合,来存储一些需要预置的重要参数,并在数码管上显示出来.由于单片机控制的整流器要求实时性很强,而早期EEPROM的写周期在10 ms左右,因此运行参数的预置是在整流器待机的情况下进行的.而很多情况下需要在运行的同时记录数据,如用单片机控制的12脉波汽车电泳整流器要求在运行的同时实时记录重要数据,而且在掉电时不丢失.由于在12脉波整流器中运行的单片机程序,其周期必须小于1.67 ms(交流电网的1个周期是20 ms,除以12就是l_67 ms),这就要求实时记录的时间在1ms以下甚至更短(考虑到程序的执行时间).经查阅资料发现,目前很多EEPROM达不到这个要求[1],即使时间最短的AT89S8252单片机片内.EEP-ROM的写周期也是2.5 ms.本文通过对EEPROM的巧妙应用,实现了整流器在线记录数据的功能. 1 寻找符合要求的单片机 设备使用的是Atmel公司的AT89C52(40DIP封装)单片机和EEPROM芯片2817A.要想在不改变原设备电路板的情况下完成要求的功能,就只能在兼容的MCS-51系列单片机中想办法.AT89S8252片内含有2 KB的EEPROM,经编程测试发现,它虽然能实时记录数据并且断电不丢失,但是在向片内EEPROM中记录1个数据时,能引起输出电压和电流的波动,不能满足实际运行的需要.其原因是AT89S8252单片机片内EEPROM的写周期为2.5 ms,超过了1.67 ms的程序的执行周期,从而影响了程序的正常运行.所以执行周期是解决问题的关键. STC89C51RC/RD+系列单片机片内含有EEPROM(Data Flash),读1个字节/编程1个字节/擦除1个扇区(512字节)的时间分别为10/μs/60μs/10 ms.编程1个字节的时间为60μs,远小于AT89S8252片内EEPROM 2.5 ms的编程时间,这为解决问题提供了思路. 2问题的解决 单片机STC89C55RD+(40DIP封装),其引脚、功能完全与AT89C52兼容,与MCS-51程序也兼容,片内含有20KB的Flash程序存储器,16KB的EEPROM数据存储器.把原用于AT89C52中的程序写到STC89C255RD+中,放到原设备上运行,可长期稳定地运行.经修改的在整流器中运行的单片机程序,实时记录一些数据到 STC289C55RD+的EEPROM中,整流器可正常运行,但不能执行扇区擦除操作.执行扇区擦除操作将严重影响整流器的正常运行,引起输出电压和电流的很大波动.执行扇区擦除操作时,从示波器来看整流器的输出间断 了20 ms,电压电流显示很大的波动.用示波器捕捉到了EEPROM写时的波形,输出波形暂停了20 ms,1个周波电压,电压波形如图1所示,不执行扇区擦除操作时的波形如图2所示.从图中可以看出,问题得到了很好的解决.

EEPROM冗余纠错设计技术_张国贤

电子与第10卷第2期 收稿日期:2009-12-30EEPROM冗余纠错设计技术 张国贤,王晓玲,周昕杰 (中国电子科技集团公司第五十八研究所,江苏无锡 214035) 摘 要:随着CMOS工艺不断发展,芯片的集成度越来越高。存储器也向大容量、小体积发展。由于存储器容量的不断增加,存储器阵列在生产过程中出现缺陷的可能性将大大增加。为了提高产品的可靠性及经济利益,文章提出了利用硬件和软件冗余技术,将有误的数据及时发现并纠正。接下来分别介绍了硬件冗余和软件冗余的工作原理以及电路的实现方法,并验证了电路的正确性。此次工作,为目前的工作提供了技术基础,并为以后的EEPROM设计工作提供了良好的技术借鉴。 关键词:EEPROM;硬件冗余;软件冗余 中图分类号:TN402 文献标识码:A 文章编号:1681-1070(2010)02-0016-04 The Design Technology of EEPROM’s Redundant ZHANG Guo-xian, W ANG Xiao-ling, ZHOU Xin-jie (China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035, China) Abstract: With developing of CMOS technology, the density of chips is high. The memory also is developing to big capacity and small bulk. The possibilities of flaws in arrays of memory are increased in the production process. To improve the reliability, we used the technology of hardware redundant and software redundant to correct the errors. We introduced the mechanism and implement circuits of two designs. Then, the circuits correctness has been validated though the emulator. The designs not only satisfied the needs of present work, but supply a worthful reference for EEPROM design in future. Key words: EEPROM; hardware redundant; software redundant 1 引言 自摩尔定律提出以来,集成电路持续地按此定律增长,这是基于栅长不断缩小的结果,器件栅长的缩小基本上依照等比例缩小的原则,促进其他工艺参数的提高。目前集成电路CMOS基本单元已经进入纳米时代。和CMOS发展趋势一样,存储器具有更大容量、更小体积和更低功耗的发展前景。对于EEPROM来说,从问世至今几十年的时间里,发展速度惊人,目前容量已经发展到几十兆。EEPROM的发展是以EEPROM的单元结构的变革为基础的。良好的EEPROM单元结构具有以下特点[1]: (1)简化的工艺。如何采用简化的工艺做出EEPROM是进行EEPROM单元结构变革的首要考虑因素; (2)减少单元面积。在保证性能的前提下,面积必须做得尽可能小,以提高集成度; (3)提高可靠性。耐久度和保持特性是EEPROM 的两个重要的可靠性参数。单元的设计优化是保证EEPROM具有良好耐久性的基础。 第10卷,第2期V ol. 10,No.2 电子与封装 ELECTRONICS & P ACKAGING 总第82期 2010年2月 电 路 设 计 - 16 -

EEPROM

嵌入式系统中EEPROM文件系统的设计与实现 彭晓锋 北京邮电大学电信工程学院,北京(100876) 摘要:AT24CXX系列EEPROM在嵌入式领域有着广泛的运用。本文参考微机文件系统的原理实现能兼容AT24C08-AT24C1024的简单文件系统,实验结果证明本系统高效可行。关键词:EEPROM, 文件系统,嵌入式 1.引言 随着大量嵌入式设备的出现,在嵌入式系统中用于存储数据的EEPROM因其简单、方便、可靠的性能和低廉的价格而被广为使用。当今社会嵌入式系统无所不在,各种嵌入式设备品种繁多,差别巨大。因此各公司也推出多种不同容量不同型号的EEPROM适应多样的市场应用。人们一方面希望能像管理大容量存储器(如硬盘,FLASH等)中数据一样简单便捷的操作EEPROM中的数据(包括打开、关闭、读写文件等),同时也希望这种文件系统能兼容不同容量、型号,具有较强的通用性。而对于采用两线IIC总线读写方式[1]的EEPROM来说,无法使用类似与FLASH所支持的TFFS之类的文件系统,本文参照上述思想,实现了一种能兼容AT24C08-AT24C1024类似于文件系统的用于管理EEPROM中数据的方法,并在实践项目中得到良好运用。 2.AT24CXX系列EEPROM简介 AT24CXX系列是ATMEL公司生产的串行电可擦的可编程存储器,它采用8引脚封装,具有可掉电记忆,结构紧凑、存储容量大等特点,可以在2线总线上并接多片芯片,适用于具有大容量数据存储要求的嵌入式系统[2]。 ⅰ)封装及管脚说明 AT24C08-AT24C1024的封装如图1所示(对不同型号 A0-A2相应改为NC,详见表1),各引脚的功能如下: ⑴ A0、A1、A2:器件地址(device address)。IIC串行总线 需连接多个EEPROM芯片时,可用A0、A1、A2来区分各芯 片,悬空时为0。 ⑵ SDA:I2C 串行数据。图1. A T24CXX系列EEPROM封装 ⑶ SCL:I2C 串行时钟。一般在其上升沿将SDA上的数据写入存储器,而在下降沿从存储器读出数据并送往SDA。 ⑷ WP:写保护。此引脚接地时,允许写操作;与VCC相连时,所有写操作被禁止。如果不连,该脚将在芯片内部下拉到地。 ⑸ VCC:电源;GND:地;NC:悬空。 ⅱ)与处理器通信 AT24C系列的接口特性:一般A0-A2、WP接VCC或GND,SCL、SDA接处理器的IIC接口相应管脚,即可实现处理器对EEPROM的操作。 ⅲ)设备地址(device address) 对EEPROM读写数据前,需先发一个字节的device address以选择芯片进行读写。其中首部四比特的“1010”为固定值;A0- A2用于对多个EEPROM进行区分,注意对AT24C不同型号,

EEPROM存储器概述

非易失性存储器概述 一、介绍 这篇文章论述了非易失性存储器(NVM)基本概况。第1部分介绍了非易失性存储器的主要背景以及一些存储器的基本术语。第2部分主要阐述了非易失性存储器的工作原理(通过热电子注入实现编程)。第3部分包含了非易失性存储器的擦除原理,以及隧道效应。第4部分介绍了用于预测非易失性存储器的编程特性的模型,用“幸运电子”模型来表述热电子注入模式。第5部分主要介绍非易失性存储器可靠性,包括在数据保存、耐受力和干扰影响下的可靠性。 关键词:非易失性,存储器,热电子注入,隧道效应,可靠性,保存,存储干扰,EEPROM,Flash EEPROM。 存储器分为两大类:易失性存储器和非易失性存储器。易失性存储器在掉电后会失去其所存储的数据,故而需要继续不断的电源才能保存数据。大部分的随机存取存储器(RAM)都是易失性的。非易失性存储器则在掉电后不会丢失数据。一个非易失性存储器(NVM)本质上是一个MOS管,由一个源极、一个漏极、一个门极,以及一个浮栅。与常用的MOSFET 不同的是,NVM多了一个浮栅,浮栅与其它部分是绝缘的。非易失性存储器又细分为两个主要的分类:浮栅型和电子俘获型。Kahng 和Sze在1967年发明了第一个浮栅型器件。在这种器件中,电子受隧道效应的影响,通过一个3nm厚的二氧化硅层,从一个浮栅中转移到基层中。通过隧道效应,非易失性存储器可以更容易地被擦除或改写,通常隧道效应只在厚度小于12nm的氧化物中存在。浮栅中存储电子后,可以使得阈值电压被降低或者提高,而阈值电压的高低也就分别代表了逻辑值1或0。 在浮栅型存储器件中,电子(也即是数据)存储在浮栅中,故而掉电后,数据不会丢失。所有的浮栅型存储器件都是一样的存储单元结构,如下图1所示,一个存储单元由门极MOS 管堆叠而成。第一个门是浮栅门,被埋在栅氧化层(Gate Oxide)和内部多晶硅绝缘层(IPD)之间,位于控制门(Control Gate)的下方。内部多晶硅绝缘层将浮栅隔绝起来,它可以是氧化物,或者氧化物-氮化物-氧化物层(ONO)。SiO2绝缘层将MOS管包围起来,作为保护层,使其免受划伤和杂质污染。第二个门极是控制门,这个门是可以被外部所接触到的。浮栅门常用在EPROM里(Electrically Programmable Read Only Memory)和EEPROM 里(Electrically Erasable and Programmable Read Only Memory)。 图1:基本的浮栅门结构