PCIe XAPP859仿真波形分析

PCIe部分工作计划及总结

工作计划

基于PCIe + DMA的设计框架,以FPGA厂商Xilinx针对PCIe解决方案的参考设计为原型,结合本设计高速数据传输的需求,暂制定PCIe硬件部分的工作计划如下:

1、设备端DMA控制器设计(FPGA实现)。因为PCIe IP硬核是PCIe核心协议的封装,只

留给用户应用层接口用来开发,用户层只要把数据。设备端的DMA控制器就工作在PCIe 的应用层上,来实现数据的高效传输。

实现方式:以参考设计提供的DMA控制器为原型,结合本项目的实际需要设计自己的DMA控制器。

实现计划:看协议、读代码-> 改写代码 -> 仿真、验证

2、 DMA+PCIe上板调试。DMA控制器做好之后,开始上板调试,以能跑通、能传数据为主,

暂不考虑传输效率的问题。

3、提高PCIe传输效率。提高PCIe传输效率的关键在于实现流控制,电源管理等等PCIe

协议的细节上,这些控制都是以数据包的形式去配置和实现。另外,DMA部分的代码优化也很重要。

所以,在DMA控制器结合PCIe硬核实现数据传输的基础上,要想实现高速数据传输,这一部分的工作必不可少。

实现计划:读PCIe协议->改写代码->调试

*4、Scatter_Gather DMA。如果数据传输速率达不到要求的话,改进DMA控制器及驱动。

注:整个过程都是与PCIe驱动和GUI的实现分不开的。

工作进度

1、根据tb.v源代码,结合仿真波形和PCIe协议细节看完了TestBench。

TestBench相当于PC机上Driver+GUI的功能,属于上游的激励信号产生器的内容。发起的业务主要包括:读pcie配置空间,配置pcie寄存器,设备端DMA读操作,设备端DMA 写和设备端DMA读写全双工操作。

在知道PC端激励的情况下,观察设备端的响应的波形和数据,并结合PCIe协议的内容,验证了参考设计的正确性和通用性,加深了对系统框架和PCIe协议的理解。

2、顺着数据流动的方向,现在正在看设备端DMA控制器的接收引擎模块(RX Engine)的源代码

下一步打算

读DMA控制器原型的其他模块的源代码。

参考设计概述

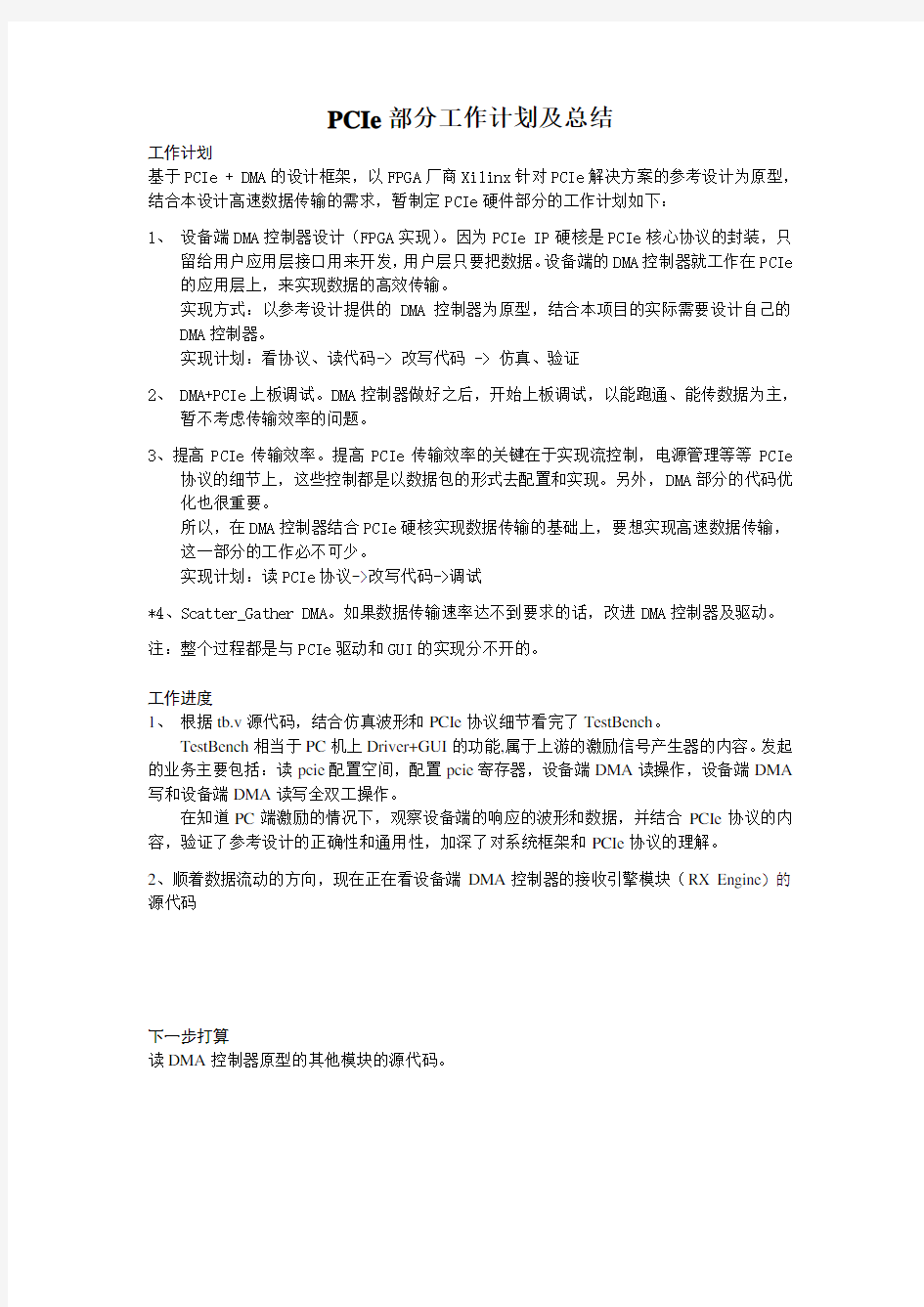

基于Xilinx Virtex5 的PCIe 硬核解决方案(Xilinx-XAPP859 源码公开)。 配置方式是PCIe1.0*8lane ,理论传输速率为2GB/s ;适用于低速数据传输。 系统框架

fig.01

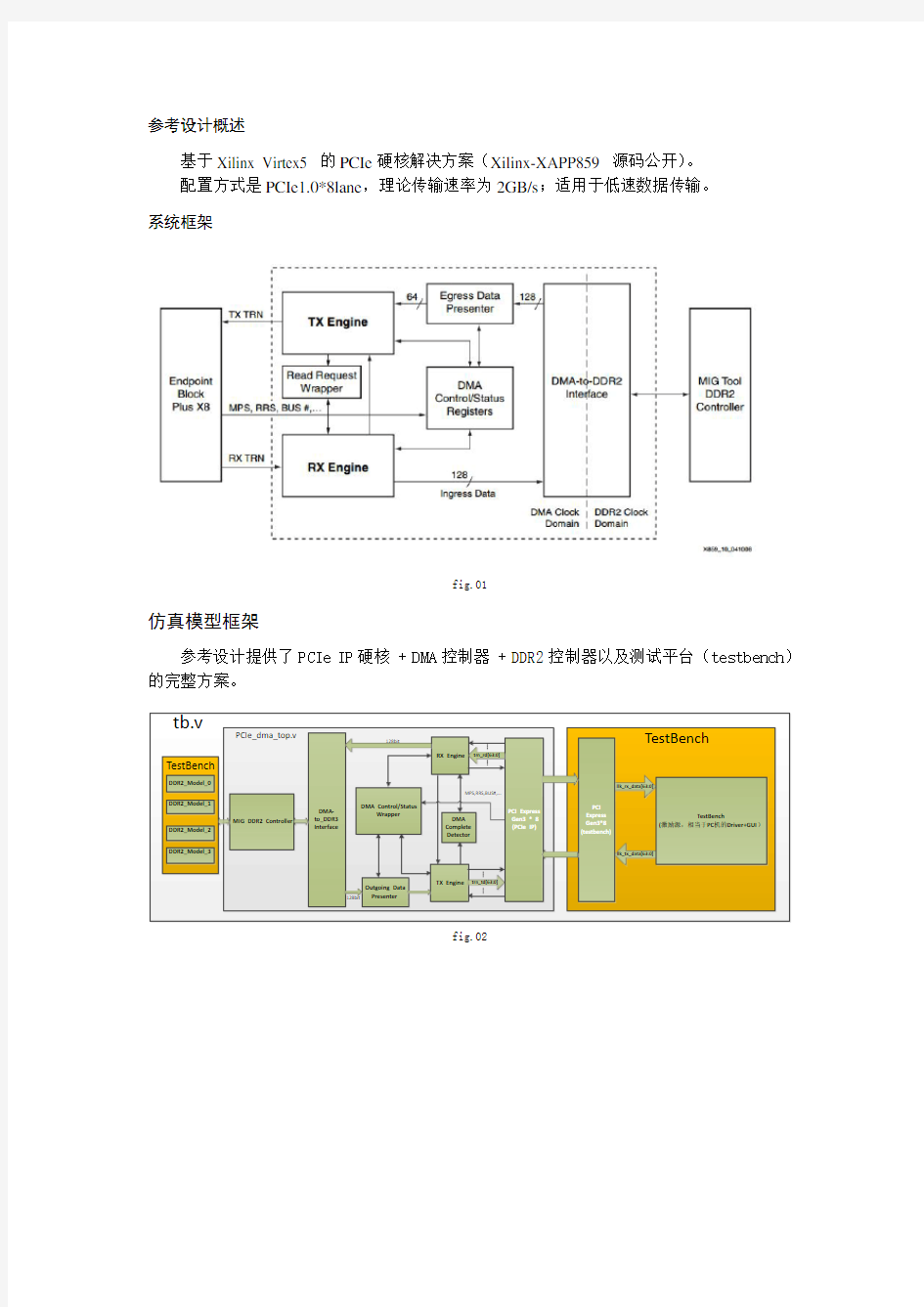

仿真模型框架

参考设计提供了PCIe IP 硬核 + DMA 控制器 + DDR2控制器以及测试平台(testbench )的完整方案。

DMA Control/Status

Wrapper

Outgoing Data Presenter

TX Engine

DMA Complete Detector

64bit

trn_td[63:0]

PCI Express Gen3 * 8(PCIe IP)

DMA-to_DDR3Interface

128bit

RX Engine

MPS,RRS,BUS#,...

128bit

trn_rd[63:0]

PCI Express Gen3*8(testbench)

MIG DDR2 Controller

DDR2_Model_0DDR2_Model_1

DDR2_Model_2DDR2_Model_3

TestBench

(激励源,相当于PC 机的Driver+GUI )

pci_tx_LVDS[1:8]

pci_rx_LVDS[1:8]

llk_rx_data[63:0]

llk_tx_data[63:0]

TestBench

TestBench

PCIe_dma_top.v

tb.v

trn_rsof_n

trn_rdst_rdy-n

trn_tdst_rdy-n

trn_rsof_n

fig.02

参考设计的工作流程概述及波形分析

该模型所有激励和行为均由测试平台(tb.v)发起,其实tb.v在该模型中相当于PC端的Driver 和GUI的功能,pcie_dma_top相当于设备端的PCIe硬核,DMA控制器和内存控制器。

此设计原型的工作流程如下:

1、tb.v在对待测模块(pcie_dma_top)复位,并去复位之后,就开始等待link_up_fe置位。link_up_fe(和 PCIe硬核的trn_lnk_up_n相连)低有效,当与核连接的上行链路合作伙伴端口已就绪并能够交换数据包时,事务上行链接置该位有效。表明链路完整,可以进行通信。上电自检过程代码提示信息如图fig.03,

fig.03

2、tb.v检测到link_up_fe有效之后,延时2000ns,调用find_capabilitie任务(读取pcie配置空间的任务)。

该任务执行读待测模块的PCIe扩展寄存器的功能,该请求以pcie事务包的形式从tb.v发往pcie_dma_top.v。tb.v的接收端口(llk_rd_data[63:0])等待并接收来自待测模块的响应事务包。

find_capabilitie任务用来确定链路宽度和一些必要的参数;如电源管理寄存器,流量控制和中断机制寄存器等。

代码运行消息提示框如下图fig.04,

fig.04

读pcie寄存器仿真波形如下图fig.05,

fig.05

其中第一个读请求放大如下图fig.06,

fig.06

由fig.06知发送的请求包数据位0x0400_0001_5500_030f + 0x2000_0034(共3 个双字)查找pcie协议手册发现,该包为配置0型读请求,目的是读取pcie基本配置空间0x34上的数据。由协议知0x34上存放着Capability Pointer的值,该值为Capabilities结构链表的头指针。

其中面向第一个读请求的响应包放大后如下图fig.07,

fig.07

由fig.07图知,接收到的完成包数据为0x4a00_0001_0000_0004 + 0x5500_0300_4000_0000根据pcie协议事务层包的内容知,该完成包为配置0型完成包,它携带的1DW的有效数据,且该数据为0x4000_0000;

根据请求包和完成包的数据可知,该pcie核的Capabilities结构链表的首地址为0x40。对比提示信息发现,该次读/写流程是完全正确,且符合pcie协议。

接下来的7个配置空间读请求,tb.v都是顺着这个Capabilities结构链表顺序的读下去,直到把该链表读完,并把Capabilities(扩展寄存器组)的信息保存起来。用于pcie传输过程中的控制。

3、当扩展寄存器内容全部读出来之后,tb.v首先发起的是设备端DMA读操作(使设备从PC主存上读取数据,并把读到的数据存到DDR2中)。发起该业务首先需要PC对设备端DMA控制器的相关寄存器初始化,这些寄存器包括dma要读取的主存地址,dma读数据的大小,dma读开始寄存器等。

最后通过把DMA读操作开始寄存器写1,来最终发起该次DMA读请求。

代码仿真提示信息如下图fig.08,

fig.08

PC发出的MWr包,即PC初始化设备端的DMA寄存器组的仿真波形如下图fig.09,

fig.09

放大第一个MWr包,波形如下图fig.10,

fig.10

由fig.10知,PC向设备端发的请求包数据:0x4000_0001_5500_000f + 0xff4f_fc10_0000_0000(共3DW),根据pcie协议分析得,该包为MWr TLP,携带1DW的有效数据,要写入地址为0xff4ffc10,写入数据为0x00000000。

结合DMA控制器源代码和参考设计手册知,pcie域的基地址0xff4ffc00,即基址寄存器BAR0的值为0xff4ffc00,其中0xff4ffc10存放的是DMA读操作时主存的地址。

所以该包的目的在于告知DMA控制器,从PC主存的0x00000000地址上开始读数据(当然这都是tb.v在模拟PC机的动作,不是真的从主存读数据,数据都是tb.v给定的)。

pcie_dma_top.v接收tb.v的MWr请求,波形如下图fig.11

fig.11

pcie_dma_top.v接收来自tb.v的MWr请求,根据包中的地址,把相应数据写入到DMA 控制寄存器组中。DMA寄存器组内的值改变如下图fig.12

fig.11

经验证,写入dma寄存器组的值与请求包所带的数据相同,表明DMA寄存器组初始化成功。

3、在tb.v置位DMA读开始寄存器后,该包被pcie_dma_top.v接收到后,pcie_dma_top立即响应一个MRd(读内存)请求到tb.v ; tb.v收到设备端的读内存请求之后,马上开始发送完成包(完成包中即包含读取的主存中的数据,该模型中一个完成包有64B的有效数据),pcie_dma_top.v从接收到的完成包中提取出数据,存到DDR2中。发送完成包过程中的代码提示信息如下图fig.12,

fig.12

tb.v向pcie_dma_top发送完成包的波形如下图fig.13所示,

Fig.13

因为pcie配置为了一次完成包支持的最大数据量为68B,而该次DMA读请求要求128B 数据,所以该次设备端的DMA读请求的完成包要分两次传输,第二次传输如图fig14——48921ns处。

把第一个包放大,波形如下图fig.14所示,

Fig.14

由fig.14,完成包携带的数据为:0x0100_0000_0200_0000 + 0x0300_0000_0400_0000, 即,要把这些数据写入到DDR2中。

下面打开DDR2模型的memory如下图fig.15所示,

Fig.15

经对比完成包所携带的数据和DDR2中的数据发现,完成包携带数据与写入数据完全一致。所以DMA读操作时成功的。

5、总结,tb.v依次发起了:

3DW 头——————

设备端DMA读请求:128B,256B,512B,1KB,2KB,4KB,12160 B;

设备端DMA写请求:128B,256B,512B,1KB,2KB,4KB,12160 B;

设备端DMA同时读写DMA(full-duplex): 128B,4KB,14464B;

4DW 头——————

设备端DMA读请求:128B,256B,512B,1KB,2KB,4KB,12160 B;

设备端DMA写请求:128B,256B,512B,1KB,2KB,4KB,12160 B;

设备端DMA同时读写DMA(full-duplex): 128B,4KB,14464B;

经验证,每次读写均完全符合pcie协议。

仿真报告,代码提示信息如下fig17,

wav信号的波形分析与合成

教学实验报告 电子信息学院_____ 专业通信工程2011年月19_日 实验名称wav信号的波形分析与合成指导教师_________ 姓名年级学号一成绩 ________ 预习部分 1.实验目的 2.实验基本原理 3.主要仪器设备(含必要的元器件、工具)

部分组成: 1 ?声音的采集 Matlab 提供了读入、录制和播放声音以及快速傅里叶变换的函数,分别是 wavread 、wavrecord 、wavplay 和fft 。阅读这几个函数的帮助文档,熟练使用。 2. 持续音的频谱分析 将Windows 的系统目录下的ding.wav 文件读入,这是一个双声道的声音, 选择任一声道的信号,使用fft 求取其频谱,并用plot 显示它的幅度谱, 观察主要的正弦分量; 参考代码: %% [y,fs]=wavread( 'di ng.wav' ) fs len g=le ngth(y) %取其中的一个声道,譬如说,右声道(左声道的格式 yr=y(:,2); %截取前1024个点 yr=yr(1:1024); %求取幅度普并显示,首先是 fs=2048 YR2048=fft(yr,2048); figure( 'numbertitle' , 'off' ,‘name' subplot(2,1,1) plot(li nspace(-pi,pi,2048),abs(YR2048)) title( 'FFT 的幅频特性') subplot(2,1,2) plot(li nspace(-pi,pi,2048),fftshift(abs(YR2048))) title( 'FFT 后幅频特性的 fftshift' ) %fs=1024 YR1024=fft(yr,1024); figure( 'numbertitle' , 'off' ,‘name' subplot(2,1,1) plot(li nspace(-pi,pi,1024),abs(YR1024)) title( 'FFT 的幅频特性') subplot(2,1,2) plot(li nspace(-pi,pi,1024),fftshift(abs(YR1024))) FFTSHIFT title( 'FFT 后幅频特性的 fftshift' ) ,'2048 ,'1024 yr=y(:,1) ) 点 FFT'); %FFT 的幅频特性 %FFT 的幅频特性FFTSHIFT 点 FFT'); %FFT 的幅频特性 %FFT 的幅频特性的

《解题思路》信号波形合成实验电路(2)

信号波形合成实验电路(C 题) 设计任务:设计制作一个电路,能够产生多个不同频率的正弦信号,并将这些信号再合成为近似方波和其他信号。 1.基本要求 (1)方波振荡器的信号经分频与滤波处理,同时产生频率为10kHz 和30kHz 的正弦波信号,这两种信号应具有确定的相位关系(要求2个信号来自同一信号源); 需要分频,所以振荡器产生150kHz 的信号。3分频得到50kHz ,5分频得到 30kHz 、15分频得到10kHz 。 (2)产生的信号波形无明显失真,幅度峰峰值分别为6V 和2V ; 方波的展开式:)7sin 7 15sin 513sin 31(sin 4)( ++++=t t t t h t f ωωωωπ 其中h 是方波的幅度(一半高度)h=2.36V ,方波高度4.71V 。 采用RLC 串联谐振电路作为选频电路,对方波进行频谱分解。其中RLC 分别选:对于10kHz 的基波,1、10mH 、25.36nF 、Q=100;对于30kHz 的3次谐波,1、10mH 、2.8nF 、Q=100。 采用低通开关电容滤波器TLC04,截止频率设为40kHz 需要2MHz 的时钟,20kHz 需要1MHz 的时钟。需要用运放组成带通滤波器。 (3)制作一个由移相器和加法器构成的信号合成电路,将产生的10kHz 和 30kHz 正弦波信号,作为基波和3次谐波,合成一个近似方波,波形幅度为5V 。 制作一个移相网络,使得两路信号同相,然后叠加即可(运放实现)。 2.发挥部分 (1)再产生50kHz 的正弦信号作为5次谐波,参与信号合成,使合成的波 形更接近于方波; 用运放组成带通滤波器(运放实现)。 (2)根据三角波谐波的组成关系,设计一个新的信号合成电路,将产生的 10kHz 、30kHz 等各个正弦信号,合成一个近似的三角波形; 三角波的展开式)7sin 7 15sin 513sin 31(sin 8)(2222 +-+-=t t t t h t f ωωωωπ, 将上一步中的3种波形按这一系数合成三角波。 (3)设计制作一个能对各个正弦信号的幅度进行测量和数字显示的电路,测 量误差不大于±5%; 采用平均值检波电路检波,然后用AD 采集、显示即可(MCU 实现)。 (4)其他。 可以添加语音功能(ISD1420实现)。

基于FPGA的FSK调制波形产生器仿真及设计1

基于FPGA的FSK调制波形产生器仿真及设计 一实验目的: 熟悉QUARTUS II的使用方法,学习VHDL编程方法、FPGA硬件资源的使用及控制以及D/A转换器件的应用,进一步将数字电路、模拟电路、EDA技术等课程的理论知识进行综合应用。综合运用编解码技术、FSK调制解调、DDS正弦载波合成技术及VHDL编程仿真技术等,完成基于FPGA 的FSK调制波形发生器的设计和实现。 二实验仪器、设备: GW48-CK EDA开发系统、PC机、20MHz示波器等 三实验内容及要求(具体内容祥见附录): 1、设计基于FPGA的FSK调制波形产生器的硬件原理图; (提示:应包含输入按键、FPGA芯片、D/A、滤波器、LED数码显示等) 2、EDA工具采用QUARTUS II; 3、FPGA芯片:EPD1K30T144-3; 4、D/A芯片:DA0832(8bit); 5、输出信号波形:FSK调制信号,其中正弦载波f1=625Hz表示“1”;正弦载波f2=125Hz表示“0”。 6、输出数据内容:7+学号后三位(共4位,每位都用BCD码表示,位间用1bit的低电平表示)。 7、输出信号幅度:5V, 9V 可用按键控制切换; 8、输出信号码率:24 bit/s; 24 bit/S-96 bit/s可调(8 bit步进,选作) 9、要求在QUARTUS II上完成FSK调制波形产生器设计,包括各模块输出仿真波形和资源利用情况,最后在实验系统上用示波器测试波形。 FPGA芯片配置说明 本次信号发生器设计采用VHDL语言设计并通过QUARTUS II 软件编译、仿真完成后,需将生成的配制文件下载到EDA实验箱中测试输出波形。有关配制情况说明如下: 1实验平台:GW48系列EDA/SOC实验开发系统 2 FPGA芯片型号:Altera EP1K30TC144-3 简介:系统以FPGA为核心,辅以必要的模拟电路,构成了两路基于DDS技术的正弦信号发生器。其主要模块有正弦波生成、幅度控制、D/A转换和后级处理等功能。同时通过VHDL语言编程在FPGA 上实现基带信号的产生、BCD编码、同步编码,然后送入FSK调制模块进行调制,调制后一方面通过QUARTUS II软件仿真,验证其正确性,同时送出到FPGA片外进行D/A转换处理,再采用低通

信号波形合成实验报告之欧阳家百创编

信号波形合成实验电路 欧阳家百(2021.03.07) 摘要:本设计包含方波振荡电路,分频电路,滤波电路,移相电路,加法电路,测量显示电路。题目要求对点频率的各参数处理,制作一个由移相器和加法器构成的电路,将产生的10KHz 和30KHz 正弦信号作为基波和三次谐波,合成一个波形幅度为5V、近似于方波的波形。振荡电路采用晶振自振荡并与74LS04 结 合,产生6MHz 的方波源。分频电路采用74HC164与74HC74分频出固定频率的 方波,作为波形合成的基础。滤波采用TI公司的运放LC084,分别设置各波形 的滤波电路。移相电路主要处理在滤波过程中相位的偏差,避免对波形的合成结 果造成影响。 关键词:方波振荡电路分频与滤波移相电路加法器 Experimental waveform synthesis circuit Abstract:The design consists of a square wave oscillator circuit, divider circuit, filtercircuit, phase shift circuits, addition circuits, measurement display circuit. Subject ofthe request of the point frequency of the various parameters of processing, productionof a phase shifter circuit consisting of adders, will have the 10KHz

波形分析

电控汽油喷射系统的波形分析 汽车用示波器 一、汽车示波器的功用 汽车上电子设备所占的比例越来越多,电子设备的修理工作也就越来越多,这就对今天的汽车维修技术提出了新挑战。现代的汽车修理工作已经不再是一个单纯的机械修理,而是机械和电子一体化的维修,如果一个汽车维修企业不具备有效地排除汽车电子设备的故障能力,这个企业必将面临被淘汰的危险。为了能有效地排除汽车电子设备的故障,保证汽车修理的质量,必须具备以下三个基本条件: (1)必备的测试设备; (2)必需的维修资料; (3)必要的技术培训; 汽车示波器的诞生为汽车修理技术人员快速判断汽车电子设备故障提供了有力了的工具。用普通的示波器去测试电子设备时,最大的困难是设定示波器(即调整示波器的各个按钮,使显示的波形更为清楚)和分析波形,而使用汽车示波器测试汽车电子设备非常简单,只要像点菜单一样,选择要测试的内容,无需任何设定和调整就可以直接观察波形。汽车示波器是专门为汽车维修人员设计的“傻瓜”示波器,它的设定和调整是全自动的,使用汽车示波器,就你使用一台“傻瓜”照相机一样方便。 示波器与万用表相比有着更为精确及描述细致的优点,万用表通常只能用1—2个电参数来反映电信号的特征,而示波器则用电压随时间的变化的图形来反映—‘个电信号,它显示电信号比万用表更准确、更形象达式 有些汽车电子设备的信号变化速率非常快,变化周期达到干分之一秒.通常测试仪器的扫描速度应该是被测试信号的5—10倍。还有许多故障信号是间歇的,时有时无,这就需要仪器的测试速度大大高于故障信号曲速度。汽车示波器不仅可以快速捕捉电信号,还对以用较慢的速度来显示这些波形,以便一面观察,一面分析。汽车示波器还可以以储存的方式记录信号波形,反复观察已经发生过的快速信号,这就为分析故障提供了极大方便。无论是高速信号(如喷油嘴、间歇性故障信号),还是慢速信号(如节气门位置变化及氧传感器信号),都可以用汽车示波器来观测被测设备的工作状况。 使用汽车示波器还可以判定故障是否已被排除,而不仅仅是知道故障码是否清除,这可以帮助维修人员提高修理水平。 二、汽车示波器(表)的应用 汽车示波器在汽车电子控制故障诊断中,有两种方式:

信号波形合成

信号波形合成设计报告 一、设计要求: 1、 方波振荡器的信号经分频与滤波处理,同时产生频率为10kHz 、30kHz 和50KHz 的正弦波信号,这三种种信号应具有确定的相位关系 2、 制作一个由移相器和加法器构成的信号合成电路,将产生的10kHz 和 30kHz 正弦波信号,作为基波和3次谐波,合成一个近似方波。 3、 根据三角波谐波的组成关系,设计一个新的信号合成电路,将产生的 10kHz 、30kHz 、50KHz 的正弦信号,合成一个近似的三角波形 (具体阐述设计的功能要求和指标要求) 二、方案设计: 傅里叶分析: 任何具有周期为T 的波函数f(t)都可以表示为三角函数所构成的级数之和即:∑∞=++=1 0)sin cos (21)(n n n t n b t n a a t f ωω。 此方波为奇函数,它没有常数项。数学上可以证明此方波可表示为: )7sin 715sin 513sin 31(sin 4)( ++++=t t t t h t f ωωωωπ ∑∞=--=1])12sin[()1 21( 4n t n n h ωπ 同样,对于三角波也可以表示为: )7sin 7 15sin 513sin 31(sin 8)(2222 +-+-=t t t t h t f ωωωωπ ∑∞=----=1212)12sin() 12(1)1(8n n t n n h ωπ。 (写出设计的整体思路构架,画出框图,说明各部分的主要作用.) 三、设计过程 由有源振荡器产生19.2MHz 信号经可编程逻辑器件EPM7128SLC84-7产生一个

300kHz的方波,再经3路分频器,最终输出50kHz、30kHz和10kHz的方波信号。四:测试数据 1、方波产生电路:

波形发生器

波形发生器 摘要: 使用题目指定的综合测试板上的NE555芯片和一片四运放LM324芯片制作一个频率可变的同时输出脉冲波、锯齿波、一次和三次正弦波。进行方案设计,制作出实际电路使其达到实验要求的各项指标。 一、设计任务与要求 使用题目指定的综合测试板上的NE555芯片和一片四运放LM324芯片,设计制作一个频率可变的同时输出脉冲波、锯齿波、正弦波Ⅰ、正弦波Ⅱ的波形产生电路。给出方案设计、详细电路图和现场自测数据及波形。 设计制作要求如下: 1、同时四通道输出、每通道输出脉冲波、锯齿波、正弦波Ⅰ、正弦波Ⅱ中 的一种波形,每通道输出的负载电阻均为600欧姆。 2、四种波形的频率关系为1:1:1:3(3次谐波);脉冲波、锯齿波、正弦波Ⅰ输出频率范围为8KHz ~10KHz ,输出电压幅度峰峰值为1V ;正弦波Ⅱ输出频率范围为24KHz ~30KHz ,输出电压幅度峰峰值为9V 。脉冲波、锯齿波和正弦波输出波形应无明显失真(使用示波器测量时)。 频率误差不大于10%;通带内输出电压幅度峰峰值误差不大于5%。脉冲波占空比可调整。 3、电源只能选用+10V 单电源,由稳压电源供给,不得使用额外电源。 4、要求预留脉冲波、锯齿波、正弦波Ⅰ、正弦波Ⅱ和电源的测试端子。 5、每通道输出的负载电阻600欧姆应标清楚、至于明显位置,便于检查。 6、翻译:NE555和 LM324的数据手册(器件描述、特点、应用、绝对参数、电参数)。 二、方案论证与设计 1.原始方案: 在使用Multisim 进行仿真设计的阶段,我想出了两种原始方案,两种方案的大体思路如下。 方案一:使用NE555芯片构成多谐振荡器,输出方波,通过锯齿波发生电路产生锯齿波,然后通过一个KHz f H 10 的低通滤波器,通过滤波产生一次,8KHz 到10KHz 的正弦波,然后再让锯齿波通过一个24KHz~30KHz 的带通滤波器,输出三次正弦波。其中滤出三次谐波的理论依据是,由于锯齿波是一个关于t 的周期函数,并且满足狄里赫莱条件:在一个周期内具有有限个间断点,且在这些间断点上,函数是有限值;在一

TI杯模拟电子设计大赛信号波形合成实验电路

TI杯模拟电子设计大赛 信号波形合成的设计与实现 参赛学校: 参赛队员: 指导老师:

摘要 生活中离不开信号,我们时时刻刻都在和信号打着交道,正弦波,方波这两种波是最基本的波形,我们通过设计方波的产生来更加深刻了解到信号的产生。 Abstract Life is inseparable from the signal, we all the time and signal name of dealings, sine wave, square wave are the two waves in the most basic waveform. Now we design a products to generate square wave signal to know the wave deeply . 一.设计思路 采用单片机430 来控制输出值的显示。基本的流程图如下所示:

又因为我们将方波傅利叶分解出得出如上的图,我们发现方波就是基波,三次谐波,五次谐波组成。 对三角波分解,如下图 从图中,我们知道三角波是三次谐波翻转180度,然后和基波与五次谐波相加所得,其中因

为别的谐波幅值不太,我们可以不做考虑。 二.方案论证 1、方波的产生方案论证和选择 方波是要设计的基础部分,下面产生的任何波形都是在这个波上产生的。 方案一:采用专用DDS芯片产生方波。优点:软件设计,控制方便,电路易实现。但是因为题目要求是“方波振荡器的信号经分频与滤波处理”,也就是说,软件控制不是题目想要的。 方案二:采用晶振来产生。用60M的晶振来产生方波,通过对60M的有源晶振分频来产生频率分别为10K Hz,30K Hz,50K Hz 的方波,但这样产生的分频电路过于复杂,不利于系统的搭建。 方案三:利用555产生出一定频率的方波。根据后面的要求,我们直接用555产生50K Hz 和60K Hz的方波 为了后面的设计,又因为555的技术已经很成熟了,选择方案三,使用555来直接产生方波。 2、分频与滤波 通过RC振荡来滤波,为了得到毛刺少的波,我们用三阶滤波。 3、移相电路设计方案论证和选择 方案一:由三相输入隔离变压器二次绕组接成12边形的移相电路t每相有3个绕组通过特殊的连接方法组成。其存在着如体积大移相变化率>5 等诸多缺点。 方案二:用运放和R,C 来调节翻转的角度。R ,C 电路在输入输出时会有90度的迟滞。 根据题目的要求,我们只要在0~90度可调与一个反向器就好。 4加法器的设计方案 根据题目要求,只要可调就好。 5.电源方案的选择与论证 方案一:采用升压型稳压电路。用两片MC34063芯片分别将3V的电池电压进行直流斩波调压,得到5V 和12V的稳压输出。只需使用两节电池,节省了电池,又减小了系统体积重量。但该电路供电电流沁,供电时间短,无法使用相对庞大的系统稳定运作。 方案二:采用三端稳压集成7805与7905分别得到5V和-5V的稳定电压。利用该方法方便简单,工作稳定可靠。 综上所述,选择方案二,采用三端集成稳压器电路7805和7905。 三.信号波形系统的组成: 1方波的产生的电路设计 方波是由555发生器,二极管,三极管以及电阻,电容组成。其原理图如图1,图2所示。

信号波形合成

信号波形合成实验电路 摘要:本作品主要用于非正弦信号的分解与合成实验验证,包括电源电路模块,方波信号产生模块,放大、移相、波形合成模块、测量显示模块等。通过1MHz晶振电路产生1MHz 方波信号,经计数、分频得到10kHz方波信号,利用LC并联谐振(滤波器)分离出10kHz、30kHz、50kHz正弦波信号,然后对三个正弦波信号进行放大、移相加到加法器中合成方波信号。把10kHz和30kHz正弦波信号送到减法器中合成三角波信号。三个正弦波信号的幅度通过单片机采样,由液晶屏显示出来。 关键词:方波信号,滤波器,正弦波信号,分解,合成 Signal waveform synthesis experiment circuit Abstract:This work is mainly used in the sine signal decomposition and synthetic experiment, including power circuit module, pulse signal generated module, amplification, phase and waveform synthesis module, measuring display module, etc. Through 1MHz crystals 1MHz circuit, signal by counting, pulse frequency, pulse signal 10kHz get by LC parallel resonant filter (10kHz isolated, 30kHz, 50kHz sine signals, then the three sine signals, adding to amplify the adder synthetic square-wave signal. The 10kHz and 30kHz sine signals to reduce time-multiplier synthetic triangular signal. Three sine signals by MCU, the amplitude of LCD display samples. Key words:Pulse signal,Filter,Sine signals,decomposition,Synthesis

信号波形合成实验电路(C题)

信号波形合成实验电路(C 题) 摘要:该系统由方波振荡电路产生300k 方波,经三分频和十分频,同时得到10K,30K,50K 的方波。使用TI 公司的四阶开关电容低通滤波器TLC041D ,可同时产生几路正弦信号,再经移相和加法器合成方波信号或三角波,由单片机采样峰值进行液晶显示.整个系统简易实现,性价比高。 关键字:方波振荡器 开关电容滤波器TLC041D 移相器 峰值检测 液晶显示 1. 方案设计 1.1 总体方案与系统框图 题目要求从方波中提取基波和三次谐波,五次谐波,再合成方波,为实现题目要求,本系统的各个模块如图1所示。由施密特触发器构成方波振荡电路,由简单的门电路和触发器构成分频电路,使用通用运放组成滤波,放大,移相电路合成方波或三角波。 图1 1.2 理论分析及TI 芯片选用依据 任何具有周期为T 的波函数f(t)都可以表示为三角函数所构成的级数之和,如式(1-1): ) (公式1) sin cos (21 )(1 0∑∞ =++=n n n t n b t n a a t f ωω 对于方波和三角波分别可以通过傅立叶展开,如式1-2,1-3所示: )(公式2)7sin 71 5sin 513sin 31(sin 4)( ++++= t t t t h t f ωωωωπ )(公式3)7sin 7 1 5sin 513sin 31(sin 8)(2222 +-+- = t t t t h t f ωωωωπ 结合题目要求,本系统主要需要以下器件: (1) 信号源施密特触发器CD40106产生300K 方波; (2) 300K 方波分别经分频器 得到50K ,30K ,10K 方波; (3) 滤波芯片TLC041,通用运算放大器OP 系列,以及电流监测芯片))

实验二、 波形合成与分解

实验二 波形合成与分解 1.实验目的 在理论学习的基础上,通过本实验熟悉信号的合成、分解原理,了解信号频谱的含义,加深对傅里叶变换性质和作用的理解。 2.实验原理 根据傅里叶分析的原理,任何周期信号都可以用一组三角函数)}cos();{sin(00t n t n ωω的组合表示,即: )2sin()2cos()sin()cos()(020201010t b t a t b t a a t x ωωωω++++= 即可以用一组正弦波和余弦波来合成任意形状的周期信号。 3.实验内容 (1) 方波的合成 图示方波是一个奇谐信号,由傅里叶级数可知,它是由无穷个奇次谐波分量 合成的,本实验用图形的方式来表示它的合成。方波信号可以分解为: ,9,7,5,3,1,1)2sin(2)(10=?=∑∞ =n n t nf A t x n ππ 用前5项谐波近似合成50Hz,幅值为3的方波,写出实验步骤。 a.只考察从 0=t s 到10=t s 这段时间内的信号。 b.画出基波分量)sin()(t t y =。 c.将三次谐波加到基波之上,并画出结果,并显示。 3/)*3sin()sin()(t t t y += d.再将一次、三次、五次、七次和九次谐波加在一起。 9/)*9sin(7/)*7sin(5/)*5sin(3/)*3sin()sin()(t t t t t t y ++++= e.合并从基波到十九次谐波的各奇次谐波分量。 f.将上述波形分别画在一幅图中,可以看出它们逼近方波的过程。注意“吉布斯现象”。周期信号傅里叶级数在信号的连续点收于该信号,在不连续点收敛于信号左右极限的平均值。如果我们用周期信号傅里叶级数的部分和来近似周期信号,在不连续点附近将会出现起伏和超量。在实际中,如果应用这种近似,就应该选择足够大的N ,以保证这些起伏拥有的能量可以忽略。 (2) 设计谐波合成三角波的实验,写出实验步骤,并完成实验。

信号波形合成

2010年全国大学生电子设计与创新大赛 ——信号波形合成实验电路 (C题) 参赛学校:武汉理工大学华夏学院 院系:信息工程系 专业班级:电信 07 级 参赛队员: 赛前指导教师: 2010年8月

摘要: 基于电路设计的要求,信号波形合成器的电路主要由方波振荡电路、分频和滤波电路、移相电路、加法器电路模块等电路模块组成。本次信号波形合成器是基于傅里叶变换的原理设计的,选择了MAX038集成函数信号发生器,实现基准信号的产生,电路结构简单,效率快、精度高;采用TI公司的MSP430F149单片机的定时计数器完成分频功能,搭建有源RC移相电路实现移相功能,最后利用运算加法器完成信号的合成。该系统电路简单,目的明确,具有很好的实用性。 关键词:方波振荡电路 MSP430F149 移相电路加法器电路 Abstract: Based on the circuit design requirements, signal waveform synthesis of circuit consists mainly of pulse oscillator circuit, frequency and phase filter circuits, circuit and adder circuits module circuit signal waveform synthesis is based on Fourier transform principle of design, chose MAX038 integrated function signal generator, realize the benchmark signals, such as simple structure, high precision and efficiency, The company adopts the MSP430F149 TI single-chip function complete timing counter frequency, phase shifting active RC circuit implementation phase function, and finally the computational adder complete synthesis of signal. The simple circuit system, purpose, have very good practicability.

信号分解与合成实验

深圳大学实验报告课程名称:信号与系统 实验项目名称:信号的分解与合成实验 学院:信息工程工程学院 专业:电子信息工程 指导教师: 报告人:学号:班级: 实验时间:

实验报告提交时间: 教务处制

具体方法:基波与各高次谐波相位比较(李沙育频率测试法) 把BFP-1ω处的基波送入示波器的X 轴,再分别把BFP-31ω、BFP-51ω处的高次谐波送入Y 轴,示波器采用X-Y 方式显示,观察李沙育图。 当基波与三次谐波相位差为0o 、90o 、180o 时,波形分别如图所示。 以上是三次谐波与基波产生的典型的李沙育图,通过图形上下端及两旁的波峰个数,确定频率比。 五、 实验步骤与相应实验结果: 1、把电信号分解与合成模块插在主板上,用导线接通此模块“电源插入”和主板上的电源,并打开此模块的电源开关。 2、调节函数信号发生器,使其输出10KHz 左右的方波,占空比为50%,峰峰值为6V

左右,如图(2)所示。将其接至该实验模块的“输入端”,用示波器观察各次谐波的输出即各次谐波,分别如图(3)、图(4)、图(5)、图(6)所示。 图(2)输出方波信号 图(3)基次谐波图(4)三次谐波 图(5)五次谐波图(6)七次谐波

3、信号的分解实验提供两种方式即分立元件模拟方式和数字方式。该实验采用数字方式。数字方式采用单片机输出各次谐波分量的采样值,然后经过DA转换出各次谐波,基波幅度已经固定,只需调节其他谐波的幅度,操作比较方便。数字方式需要同时打开电源开关S1、S2。 4、用示波器的两个探头,直接观察基波和三次谐波的相位关系,或者采用李沙育图的方法,看其相位差是否为180,同时考察其幅度关系,幅度之比是否为3:1. 采用李沙育图观察基波和三次谐波的相位关系如图(7),可知道其相位为180. 图(7) 从示波器中观察基波和三次谐波的峰峰值之比,可知其幅度比为3:1,如图(8)所示

一种波形产生数字电路设计及仿真

一种波形产生数字电路设计及仿真 1设计原理 DDS 直接频率合成技术是一种直接从相位的角度合成所需波形的技术。此设计旨在设计一个模拟波形的产生电路,采用quartus ii 软件作为可编程逻辑设计环境,该软件有两种设计方式,原理图输入和采用HDL 语言输入,实现模拟波形的产生。数字电路设计包含组合逻辑电路和时序逻辑电路设计,其中组合逻辑电路的设计是设计的重点。因此需要对时钟有较强的理解。本设计可以采用Verilog HDL 硬件描述语言编写程序实现波形的产生,可以产生三种波形,正弦波,方波以及三角波。其中正弦波调用quartus 自带的IP 核,通过单端口的ROM 来查表获得查表数据,通过调用ip 可以实现设计要求。方波和三角波虽然也可以通过此方式,但是也可以通过编写计数器分频实验来实现设计,方波可以直接通过半个周期信号为低电平,半个周期为高电平。三角波通过将计数器的值先增加后减少获得。波形产生电路在电子设计中占据很重要的地方,有一定的研究价值。 2功能描述 (1)实现正弦波、三角波、方波的输出; (2)信号输出通过各个波形的使能信号来区分输出何种波形; (3)信号调节方式可控,这里由于是仿真故没编写按键扫描程序; FPGA 的设计流程如下: 系统框图如图所示: 3设计定义

4 HDL语言编写流程 设计代码包含设计时钟分频进程、三角波产生进程、方波产生进程和信号输出电路进程。其中每个进程通过过程语句always来通过敏感信号如时钟上升沿和异步复位信号时钟下降沿来采样。其中设计流程图如下图所示: 5设计代码 见附录 6验证及仿真 仿真的方式有功能仿真和时序仿真,要设计这么一款电路,首先需要通过功能仿真。工具有quartus ii自带的波形仿真文件和编写顶层设计的testbench 测试程序来进行仿真。其中可以设置仿真时间、仿真精度、以及信号的输入类型定义和数值,设置好这些数据就可以进行仿真,不过采用testbench仿真相对复杂一点,需要用到modelsim软件来仿真,优点是仿真时间和仿真精度可以更高,仿真波形也相对较美观。 一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。编写Testbench的三个基本步骤: 1、对被测试设计的顶层接口进行例化; 2、给被测试设计的输入接口添加激励; 3、判断被测试设计的输出相应是否满足设计要求。

信号波形发生与合成实验

摘要 本系统主要以TL081A运放为核心,由方波发生器、滤波分频电路、移相电路、加法器电路模块组成。实现了产生多个不同频率的正弦信号与基于多个正弦波合成方波信号的电路功能。系统基本工作过程为:1kHz方波信号通过低通滤波器和带通滤波器得到按傅里叶级数展开的1kHz基波正弦波信号和3kHz三次谐波正弦波信号。而后将基波信号通过移相电路使其相位调整到与三次谐波相同,然后通过加法电路将信号合成近似的方波信号。输出波形结果表明,系统合成波形符合理论傅里叶分析结果,比较准确。正弦波及合成波的幅值测试误差小于5%,符合题目要求。 关键词:方波发生器;傅里叶级数;分频;滤波;移相 一.总体方案设计及论证 1.1题目设计任务 设计制作一个电路,能够产生多个不同频率的正弦信号,并将这些信号再合成为近似方波信号。系统框图如下图所示: 具体要求: 1.2方案论证比较 方波发生电路产生1kHz方波,对其中的基波和三次谐波分量进行提取,1kHz基波可用截止频率为1kHz的巴特沃斯低通滤波器滤波得到,3kHz谐波可用中心频率设为3kHz的高Q值带通滤波器滤波得到。最后再经相位调整重新合成近似方波。 本系统中的方波发生电路是实现后续各级电路功能的基础,对频率准确度和稳定度的要求较高。方案一:555定时器组成的多谐振荡器,直接调节至1KHz左右的对称方波。此方案成本低廉,实现方便,但其稳定性容易受到外部元件的影响,在振荡频率较高时频率稳定度不够。 方案二:使用石英晶振组成高稳定度的频率参考源,并使用计数器和集成锁相环芯片构成分频/倍频环,以产生1KHz的方波。该方法产生的信号稳定度高,但需要搭建石英晶体振荡电路,并进行锁相环分频、倍频,电路较复杂。 方案三:采用基于反相输入的滞回比较器和RC电路的方波产生电路。该电路结构简单,性能稳定,主要的限制因素在于比较器的速度。结合适当的RC参数,可达到1KHZ的振荡频率。 方案选择:本系统采用方案三,此电路结构简单,产生的方波稳定性较好。 1.2.3滤波电路的选择 本系统中所需正弦波均来自于方波信号,需使用低通滤波器和带通滤波器。 方案一:使用由LC网络组成的无源高阶巴特沃斯滤波器。其通带内相应最为平坦,衰减特性和相位特性都很好,对器件的要求也不高。但其在低频范围内有体积重量大、价格昂贵和衰减大等缺点。方案二:采用实时DSP数字滤波技术,数字信号灵活性大,可以在不增加硬件成本的基础上对信号进行有效的滤波,但要进行滤波,需要A/D、D/A既有较高的转换速率,处理器具有较高的运算速度,成本高。 方案三:以集成运放为核心的有源滤波电路,结构简单,所需元件少,成本低,且电路输入阻抗高、输出阻抗低,并有专门的设计软件。 方案选择:选择方案三作为系统的基波和三次谐波滤波方案。用集成运放TL081A和RC网络组成的二阶有源滤波电路器的滤波器结构清晰,幅频响应更接近理想特性,截止频率和增益可以进行充分调节,具有较好的滤波效果,可以产生非常理想的正弦波效果。 1.2.4移相电路的选择 移相电路对分频滤波后的基波正弦信号进行移相,使基波与三次谐波相位关系满足信号合成的需要。 方案一:采用无源RC移相网络。该方案电路简单,可以完成移相,但是通过移相网络后信号有衰

信号波形合成实验

信号波形合成实验电路 实验报告 组员:于兴家、俞宝智、黄艳霞指导教师:赵娟老师 目录 一、系统设计................................................................ . (2) 1、设计任务 (2) 2、基本要求 (2) 3、发挥部分 (2) 二、方案论证 (3) 1、信号发生器电路 (4) 2、分频电路 (4) 3、滤波电路 (4) 4、移相电路.............. . (4) 5、加法电路 (5) 三、整体设计 (5) 原理图:整体方案设计 (5) 1、方波发生器的设计与实现 (5) 2、分频电路的设计与实现 (5) 3、电压跟随器 (6) 4、滤波电路的设计与实现 (7) 5、移向电路的设计与实现 (7) 6、合成电路的设计与实现 (8) 7、合成电路的设计与实现 (9) 四. 实验测试与结果分析 (10) 1、测试仪器与设备 (10) 2、整机标准 (10) 3、系统试验结果与分析 (10) 五、实物图片 (10)

一、系统设计 1、任务 设计制作一个电路,能够产生多个不同频率的正弦信号,并将这些信号再合成为近似方波和其他信号。电路示意图如图1所示: 图1 电路示意图 2、要求 1.基本要求 (1)方波振荡器的信号经分频与滤波处理,同时产生频率为10kHz和30kHz的正弦波信号,这两种信号应具有确定的相位关系; (2)产生的信号波形无明显失真,幅度峰峰值分别为6V和2V; (3)制作一个由移相器和加法器构成的信号合成电路,将产生的10kHz和30kHz正弦波信号,作为基波和3次谐波,合成一个近似方波,波形幅度为5V,合成波形的形状如图2所示。 图2 利用基波和3次谐波合成的近似方波 2.发挥部分 (1)再产生50kHz的正弦信号作为5次谐波,参与信号合成,使合成的波形更接近于方波;(2)根据三角波谐波的组成关系,设计一个新的信号合成电路,将产生的10kHz、30kHz等各个正弦信号,合成一个近似的三角波形; (3)设计制作一个能对各个正弦信号的幅度进行测量和数字显示的电路,测量误差不大于±5%; (4)其他。

TI杯设计报告(赛区一等奖)信号波形合成实验电路

全国大学生电子设计竞赛 2010年TI杯模拟电子系统专题邀请赛设计报告 题目:信号波形合成实验电路(C题) 学校:武汉大学 指导老师: 参赛队员姓名: 日期:2010年08月24日

2010年TI杯模拟电子系统专题邀请赛试题 信号波形合成实验电路(C题) 一、课题的任务和要求 课题任务是对一个特定频率的方波进行变换产生多个不同频率的正弦信号,再将这些正弦信号合成为近似方波和近似三角波。 课题要求是首先设计制作一个特定频率的方波发生器,并在这个方波上进行必要的信号转换,分别产生10KHz、30KHz和50KHz的正弦波,然后对这三个正弦波进行频率合成,合成后的目标信号为10KHz近似方波和近似三角波。另外设计一个正弦信号幅度测量电路,以测量出产生的10KHz、30KHz和50KHz正弦波的的幅度值。 课题还给出了参考的实现方法,见下图。 图1 电路示意图 图1 课题参考实现方案 二、实现方案的分析 1.基本方波发生器方案的分析 方波的产生方法很多,如用运算放大器非线性产生、用反向器及触发器产生、也可用模数混合时基电路ICL7555产生等。本例采用第一种方案,最符合题意要求。 2.波形变换电路方案的分析 从某方波中提取特定频率的正弦波方案很多,如用窄带滤波器直接从方波中提取所需的基波或谐波;用锁相方法进行分频或倍频产生所需频率;用数字分频方案,从较高频率的方波或矩形波中通过分频获得所需频率方波并进行变换获得正弦波。本课题采用第三种方案。 3.移相方案分析 在方波——正弦波转换中,难免会产生附加相移,通过移相来抵消附加相依,以便信号合成时重新实现同步。根据微分电路实现相位超前、积分电路实现相位滞后的理论,因此,采用微伏和积分来实现移相。 4.信号合成方案分析 方波信号经过波形变换和移相后,其输出幅度将有不同程度的衰减,合成前需要将各成分的信号幅度调整到规定比例,才能合成为新的合成信号。本课题采用反向比利运算电路实

信号的产生分解与合成

东南大学电工电子实验中心 实验报告 课程名称:电子线路实践 第七次实验 实验名称:信号的产生、分解与合成 院(系):电子科学与工程学院专业: 姓名:姜勖学号:06A11315 实验室:104实验组别:27 同组人员:徐媛媛实验时间:年月日 评定成绩:审阅教师: 实验四信号的产生、分解与合成 一、实验内容及要求 设计并安装一个电路使之能够产生方波,并从方波中分离出主要谐波,再将这些谐波合成为原始信号或其他周期信号。 1.基本要求 (1)设计一个方波发生器,要求其频率为1kHz,幅度为5V; (2)设计合适的滤波器,从方波中提取出基波和3次谐波; (3)设计一个加法器电路,将基波和3次谐波信号按一定规律相加,将合成后的信号与原始信号比较,分析它们的区别及原因。 2.提高要求 设计5次谐波滤波器或设计移相电路,调整各次谐波的幅度和相位,将合成后的信号与原始信号比较,并与基本要求部分作对比,分析它们的区别及原因。 3.创新要求 用类似方式合成其他周期信号,如三角波、锯齿波等。 分析项目的功能与性能指标: 功能:通过振荡电路产生一个方波,并将其通过滤波得到1、3、5次谐波,最后通过加法电路合成新的波形。 性能指标: (1)方波:频率1KHz,幅度5V。 (2)滤波器:基础要求从方波中提取基波和三次谐波,提高要求提取五次谐波。 (3)移相电路:通过移相电路调节滤出来的1、3、5次谐波相位,使得其与原方波相位差近似为0。

(4)加法器电路:将基波和3次谐波和5次谐波信号按一定规律相加。 1、信号的产生 通过震荡电路产生1kHz ,幅度为5V 的方波信号。 2、滤波器的设计 根据方波的傅里叶展开式: 可知原信号分解只包含奇次谐波分量。因此设计不同中心频率的带通滤波器,可将各次谐波滤出。 3、相位校正电路 由于滤波器用到了对不同频率有不同响应的储能元件,对于滤除的波形会产生附加相位。若要让各次谐波叠加出原有信号,必须调节其相位使之同相。用全通滤波器可在不影响相对幅度的前提下改变相位。 4、加法电路 将滤除的基波、3次谐波、5次谐波相加,得到近似的方波信号。对于滤波器对不同频率分量不成比例的衰减,可在加法电路中选择合适的比例给予响应的补偿。 二、电路设计(预习要求) (1) 电路设计思想(请将基本要求、提高要求、创新要求分别表述): 1、信号发生电路: 利用运放和RC 回路构成振荡电路,通过分别调节正反向RC 回路的时间常数和运放同相输入端的参考电压来调节震荡电路的频率以及占空比。用一对稳压二极管限制输出电压幅度,并对稳压管导通压降进行一定的补偿。 2、有源带通滤波器: 根据实验要求,设计有源带通滤波器,将所需频率的信号以尽量小的衰减输出,同时对其它频率有非常大的衰减。因此需要增加滤波器的阶数。初步选择采用二阶有源带通滤波器,通过理论计算,调节其中一个电阻来改变中心频率。根据实际搭出的电路效果,可尝试使用四阶有源带通滤波器,以求获得更好的滤波效果。 3、相移电路: 由于滤波器难免对滤出的谐波分量产生附加相位,需要在选频电路之后加一全通网络校正相位,抵消相位差。移向电路有两种,分为正向移向和反向移向。 4、加法电路 将所得到的各次谐波分量叠加,得到近似的方波。同时,加法电路可对滤波对原信号分量的衰减进行补偿。 (2) 电路结构框图(请将基本要求、提高要求、创新要求分别画出): 基础要求:因基础要求与提高要求相比,除缺少5次滤波与移相电路外,其余部分均相同,其结构框图已包含在提高要求的框图中,故不单独列出。 提高要求: (3)电路原理图(各单元电路结构、工作原理、参数计算和元器件选择说明): 分工:徐媛媛(滤波电路的设计、搭建和调试);姜勖(方波产生、相移及加法电路设计搭建和调试) 方波振荡及鉴幅电路: 采用迟滞比较及RC 反馈回路以及比较器鉴幅电路,总电路图如下: 设从输出端的对输入端的负反馈电阻分别为1f R 和2f R ,则前部分方波的振荡周期为111222 ln(12)ln(12)f f R R T R C R C R R =+++,通过电位器分别调节1f R 和2f R 的阻值使方波的频率为1kHz ,占空比为50%。