DSP计算题王忠勇

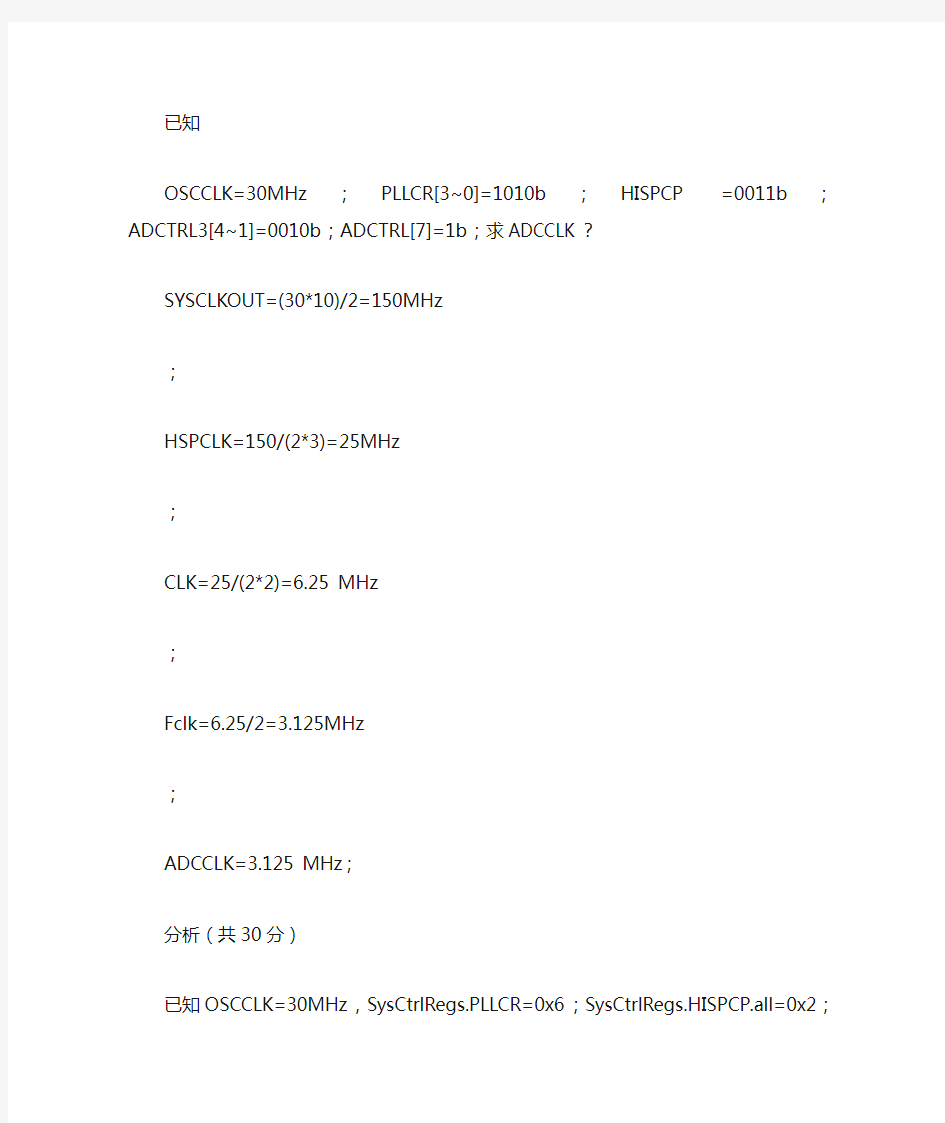

已知

OSCCLK=30MHz;PLLCR[3~0]=1010b;HISPCP =0011b;ADCTRL3[4~1]=0010b;ADCTRL[7]=1b;求ADCCLK?

SYSCLKOUT=(30*10)/2=150MHz

;

HSPCLK=150/(2*3)=25MHz

;

CLK=25/(2*2)=6.25 MHz

;

Fclk=6.25/2=3.125MHz

;

ADCCLK=3.125 MHz;

分析(共30分)

已知OSCCLK=30MHz,SysCtrlRegs.PLLCR=0x6;SysCtrlRegs.HISPCP.all=0x2;void init_eva()

{

EvaRegs.T1PR = 0xFFFF;

EvaRegs.T1CMPR = 0x3C00;

EvaRegs.T1CNT = 0x0000;

EvaRegs.T1CON.all = 0x1042;

EvaRegs.T2PR = 0x0FFF;

EvaRegs.T2CMPR = 0x03C0;

EvaRegs.T2CNT = 0x0000;

EvaRegs.T2CON.all = 0x1042;

EvaRegs.GPTCONA.bit.TCMPOE = 1;

EvaRegs.GPTCONA.bit.T1PIN = 1;

EvaRegs.GPTCONA.bit.T2PIN = 2;

EvaRegs.CMPR1 = 0x8000;

EvaRegs.CMPR2 = 0xC000;

EvaRegs.CMPR3 = 0x4000;

EvaRegs.ACTRA.all = 0x0666;

EvaRegs.DBTCONA.all = 0x0000; // Disable deadband

https://www.360docs.net/doc/193264663.html,CONA.all = 0xA600;

}

请分析SYSCLKOUT、HSPCLK、GPT2的工作时钟分别为多少,需指出它们跟那些寄存器的设置有关?

SYSCLKOUT=(30*6)/2=90MHz

;

HSPCLK=90/4=22.5MHz

;

GPT2CLK=22.5MHz

PLLCR、HISPCP、T1CON

2.请分析比较单元2产生的PWM波形的周期和占空比,计算过程中需给出相关的公式?

(T1PR+1)*T

定时器

=(65535+1)/22.5M=2.913ms

PWM1

占空比

=(T1PR+1-CMPR1)/(T1PR+1)=76%

一、填空(每空1分,共10分)

1.TMS320F2812的系统控制模块包括晶振、PLL、看门狗、低功耗等。2.ADC模块中,可以通过S/W 、EVA、EVB、外部引脚四种方式来启动ADC。3.F2812DSP内核总计有16根中断线,其中NMI和RS是不可屏蔽中断。4.在EVB中,GPT3为比较单元提供时钟基准。

5.在EV中,要产生对称PWM信号,需在连续递增/递减计数模式。

6.ADC模块中,16 个模拟输入通道。

二、用文字简要描述下面各寄存器的主要功能(每题4分,共20分)1.TxPR与TxCMPR TxPR:设置通用定时器的周期值;TxCMPR:设置通用定时器的比较值;

2.GPxDIR与GPxDAT GPxDIR设置数字量IO的方向;GPxDAT:设置数字量输出端口的数值;

3.TCR与PRD TCR:设置CPU定时器的相关参数;PRD:设置周期寄存器的装载值;4.PCLKCR与LOSPCP PCLKCR使能或禁止外部设备时钟;LOSPCP:低速预定表寄存器,设置低速时钟的分频系数;

5.MAXCONV与ADCRESULTn MAXCONV:设置ADC转换的最大通道数;ADCRESULTn: 存放ADC转换后的数值。

三、简答题(每题6分,共30分)

1.试说明:在程序中设置完PLLCR后为什么还需要延时。

需注意:在通过软件改变系统的工作频率时,必须等待系统时钟稳定后才可以继续完成其他操作。所以在程序中,配置完PLLCR中的倍频系数后,都需要一个延时程序。

3.CPU定时器产生中断的时间间隔跟那些寄存器有关。

PLLCR、HISPCP、PRD、PRC等

4.下图是EV中的比较单元产生对称PWM的波形,请描述其如何产生?

(提示:跳变点) 输出的

PWM波形:在一个周期内,两次比较匹配,两次跳变有效相位长度=TxPR-(TxCMPR)up+ TxPR-(TxCMPR)dn 递增/递减计数周期为2TxPR(所以可以计算出其占空比)

占空比=(正脉宽/PWM周期) 100%

5.简要说明F2812处理器上锁相环工作的配置模式。

答:锁相环配置模式如下:

a)当XPLLDIS引脚为低电平时,则PLL完全禁止。处理器直接使用引脚

X1/XCLKIN输入的时钟信号;

b)上电时的默认配置,如果PLL没有禁止,则PLL将变成旁路,在X1/XCLKIN

引脚输入的时钟经过2分频提供给CPU;

c) 使能PLL ,在PLLCR寄存器中写入一个非零值n。

上电复位后,中断向量表映射为哪种中断向量表?为什么在上电复位和boot引导结束后,要把中断向量表从BROM向量表或XINTIF向量表切换到PIE向量表呢?PIE向量表中存放什么中断服务程序地址?

上电复位时,ENPIE=“0”(PIE使能控制位复位状态),CPU向量表映射为BROM 向量表或XINTF向量表之一,由MP/MC引脚控制,当MP/MC=1,映射为XINTF 向量表。当MP/MC=1,映射为BROM向量表。切换到PIE向量表才能实现外设中断的最快响应。PIE向量表中存放特定外设中断中断服务程序入口地址。

数字信号处理考试试题及答案

数字信号处理试题及答案 一、 填空题(30分,每空1分) 1、对模拟信号(一维信号,是时间的函数)进行采样后,就是 离散时间 信号, 再进行幅度量化后就是 数字 信号。 2、已知线性时不变系统的单位脉冲响应为)(n h ,则系统具有因果性要求 )0(0)(<=n n h ,系统稳定要求∞<∑∞ -∞=n n h )(。 3、若有限长序列x(n)的长度为N ,h(n)的长度为M ,则其卷积和的长度L 为 N+M-1。 4、傅里叶变换的几种形式:连续时间、连续频率—傅里叶变换;连续时间离散频率—傅里叶级数;离散时间、连续频率—序列的傅里叶变换;散时间、 离散频率—离散傅里叶变换 5、 序列)(n x 的N 点DFT 是)(n x 的Z 变换在 单位圆上 的N 点等间隔采样。 6、若序列的Fourier 变换存在且连续,且是其z 变换在单位圆上的值,则序列 x(n)一定绝对可和。 7、 用来计算N =16点DFT ,直接计算需要__256___次复乘法,采用基2FFT 算 法,需要__32__ 次复乘法 。 8、线性相位FIR 数字滤波器的单位脉冲响应()h n 应满足条件 ()()1--±=n N h n h 。 9. IIR 数字滤波器的基本结构中, 直接 型运算累积误差较大; 级联型 运 算累积误差较小; 并联型 运算误差最小且运算速度最高。 10. 数字滤波器按功能分包括 低通 、 高通 、 带通 、 带阻 滤 波器。 11. 若滤波器通带内 群延迟响应 = 常数,则为线性相位滤波器。 12. ()?? ? ??=n A n x 73cos π错误!未找到引用源。的周期为 14 13. 求z 反变换通常有 围线积分法(留数法)、部分分式法、长除法等。 14. 用模拟滤波器设计IIR 数字滤波器的方法包括:冲激响应不变法、阶跃响 应不变法、双线性变换法。

数字信号处理试题和答案

一. 填空题 1、一线性时不变系统,输入为 x(n)时,输出为y(n);则输入为2x(n)时,输出为 2y(n) ;输入为x(n-3)时,输出为 y(n-3) 。 2、从奈奎斯特采样定理得出,要使实信号采样后能够不失真还原,采样频率fs与信号 最高频率f max 关系为: fs>=2f max 。 3、已知一个长度为N的序列x(n),它的离散时间傅立叶变换为X(e jw),它的N点离散傅立叶变换X(K)是关于X(e jw)的 N 点等间隔采样。 4、有限长序列x(n)的8点DFT为X(K),则X(K)= 。 5、用脉冲响应不变法进行IIR数字滤波器的设计,它的主要缺点是频谱的交叠所产生的现象。 6.若数字滤波器的单位脉冲响应h(n)是奇对称的,长度为N,则它的对称中心是(N-1)/2 。 7、用窗函数法设计FIR数字滤波器时,加矩形窗比加三角窗时,所设计出的滤波器的过渡带比较窄,阻带衰减比较小。 8、无限长单位冲激响应(IIR)滤波器的结构上有反馈环路,因此是递归型结构。 9、若正弦序列x(n)=sin(30nπ/120)是周期的,则周期是N= 8 。 10、用窗函数法设计FIR数字滤波器时,过渡带的宽度不但与窗的类型有关,还与窗的采样点数有关 11.DFT与DFS有密切关系,因为有限长序列可以看成周期序列的主值区间截断,而周期序列可以看成有限长序列的周期延拓。 12.对长度为N的序列x(n)圆周移位m位得到的序列用x m (n)表示,其数学表达式为x m (n)= x((n-m)) N R N (n)。 13.对按时间抽取的基2-FFT流图进行转置,并将输入变输出,输出变输入即可得到按频率抽取的基2-FFT流图。 14.线性移不变系统的性质有交换率、结合率和分配律。 15.用DFT近似分析模拟信号的频谱时,可能出现的问题有混叠失真、泄漏、栅栏效应和频率分辨率。 16.无限长单位冲激响应滤波器的基本结构有直接Ⅰ型,直接Ⅱ型,串联型和并联型四种。

数字信号处理试题及答案

数字信号处理试题及答案 一、填空题:(每空1分,共18分) 1、 数字频率ω是模拟频率Ω对采样频率s f 的归一化,其值是 连续 (连续还是离散?)。 2、 双边序列z 变换的收敛域形状为 圆环或空集 。 3、 某序列的 DFT 表达式为∑-==1 0)()(N n kn M W n x k X ,由此可以看出,该序列时域的长度为 N ,变换后数字频域上相邻两个频率样点之间的间隔是 M π 2 。 4、 线性时不变系统离散时间因果系统的系统函数为2 52) 1(8)(2 2++--=z z z z z H ,则系统的极点为 2,2 1 21-=-=z z ;系统的稳定性为 不稳定 。系统单位冲激响应)(n h 的初值 4)0(=h ;终值)(∞h 不存在 。 5、 如果序列)(n x 是一长度为64点的有限长序列)630(≤≤n ,序列)(n h 是一长度为128点 的有限长序列)1270(≤≤n ,记)()()(n h n x n y *=(线性卷积),则)(n y 为 64+128-1=191点 点的序列,如果采用基FFT 2算法以快速卷积的方式实现线性卷积,则FFT 的点数至少为 256 点。 6、 用冲激响应不变法将一模拟滤波器映射为数字滤波器时,模拟频率Ω与数字频率ω之间的 映射变换关系为T ω = Ω。用双线性变换法将一模拟滤波器映射为数字滤波器时,模拟频率Ω 与数字频率ω之间的映射变换关系为)2 tan(2ω T =Ω或)2arctan(2T Ω=ω。 7、当线性相位 FIR 数字滤波器满足偶对称条件时,其单位冲激响应)(n h 满足的条件为 )1()(n N h n h --= ,此时对应系统的频率响应)()()(ω?ω ωj j e H e H =,则其对应的相位函数 为ωω?2 1 )(-- =N 。 8、请写出三种常用低通原型模拟滤波器 巴特沃什滤波器 、 切比雪夫滤波器 、 椭圆滤波器 。 二、判断题(每题2分,共10分) 1、 模拟信号也可以与数字信号一样在计算机上进行数字信号处理,只要加一道采样的工序就可 以了。 (╳) 2、 已知某离散时间系统为)35()]([)(+==n x n x T n y ,则该系统为线性时不变系统。(╳)

14_DSP技术原理及应用教程_课后答案

1 .1 数字信号处理器与一般通用计算机和单片机的主要差别有哪些? 答:在通用的计算机上用软件实现该方法速度太慢, 适于算法仿真; 在通用计算机系统上加上专用的加速处理机实现该方法专用性较强,应用受限制,且不便于系统 的独立运行; 用通用的单片机实现这种方式多用于一些不太复杂的数字信号处理,如简单的PID控制算法; 用通用的可编程DSP芯片实现与单片机相比,DSP芯片具有更加适合于数字信号处理的软件及硬件资源,可用于复杂的数字信号处理算法; 用专用的DSP芯片实现在一些特殊场合, 要求信号处理速度极高, 用通用的DSP 芯片很难实现,而专用的DSP 芯片可以将相应的信号处理算法在芯片内部用硬件实现,不需要编程。 1 .4 什么是冯·诺埃曼结构计算机, 什么是哈佛结构计算机, 二者的特点是什么? 答:冯.诺曼结构:将指令、数据存储在同一个存储器中,统一编址,译稿指令计数器提供的地址来区分是指令还是数据。取指令和取数据都访问统一存储器,数据吞吐率低。 哈佛结构:程序和数据存储在不同的存储空间,程序存储空间和数据存储空间是两个相互独立的存储空间,每个存储空间独立编址,独立访问。 1 .8 DSP的工作电压越来越低,内核电压已低至1V,这样做有何意义?为什么DSP内核工作电压和I/O工作电压不一样? 答:集成电路速度越来越快,随之而来,功耗越来越大,这样散热就是很大的问题.在芯片走线尺寸不变的情况下,内部阻抗也不变,降低工作电压会降低功耗,这样能再较高频率下芯片发热较少。 内核不容易受到外部干扰,所以电压可以做的较低,但IO容易受外部信号干扰,保持较高电压容易是器件工作稳定,这是功耗和稳定性的折中。 1 .10 定点DSP和浮点DSP有什么区别?在具体应用中, 应如何选择? 答:在浮点DSP中,数据即可以表示成整数,也可以表示成浮点数。浮点数在运算中,表示数的范围由于其指数可自动调节,因此可避免数的规格化和溢出等问题。但浮点DSP 一般比定点DSP 复杂, 成本也较高。 在定点DSP中, 数据采用定点表示方法。它有两种基本表示方法:整数表示方法和小数表示方法。整数表示方法主要用于控制操作、地址计算和其他非信号处理的应用, 而小数表示方法则主要用于数字和各种信号处理算法的计算中 2 .4 当要使用硬中断INT3作为中断响应矢量时,请问可屏蔽中断寄存器IMR和中断标志寄存器IFR应如何设置? 答:IFR中INT3位=1,IMR中INT3位=1,使能中断。2 .5 若处理器方式寄存器PMST的值设为01A0H,而中断矢量为INT3,那么在中断响应时, 程序计数器指针PC的值为多少? 答:PMST中IPTR=(000000011)b,int3中断向量号为24H,做移量为后变为60H,则中断响应时程序计数器指针PC=01E0H. 2 .10 DSP如何与不同速度的片外存储器及其他外设进行数据交换? 答:软件可编程等待状态发生器可以将外部总线周期扩展到7个机器周期,以使’C54x能与低速外部设备接口。而需要多于7个等待周期的设备,可以用硬件READY线来接口。 2 .11 TMS320C54x可进行移位操作,它的移位范围是多少? 答:’C54x的移位操作最多可以左移31位,或右移16位。(-16~31) 2 .1 3 为什么说应尽量利用DSP的片内存储器? 答:与片外存储器相比,片内存储器不需要插入等待状态,因此成本低,功耗小。 2 .14 如何操作通用I/ O 引脚XF和BIO? 答:XF信号可以由软件控制。通过对STl中的XF位置1得到高电平,清除而得到低电平。对状态寄存器置位的指令SSBX和对状态寄存器复位的指令RSBX可以用来对XF置位和复位。同时XF引脚为高电平和低电平,亦即CPU向外部发出1和0信号。 程序可以根据BIO的输入状态有条件地跳转,可用于替代中断。条件执行指令(XC)是在流水线的译码阶段检测BIO的状态,其它条件指令(branch、call和return)是在流水线的读阶段检测BIO 的状态的。 4 .1 写出汇编语言指令的格式, 并说明应遵循怎样的规则? 答:助记符指令格式: [标号][:] 助记符[操作数列表] [;注释] 代数指令格式: [标号][:] 代数指令[;注释] 应遵循下列规则: ①语句的开头只能是标号、空格、星号或分号。 ②标号是可选项,如果使用,必须从第一列开始。 ③每个域之间必须由一个或多个空格来分开。制表符等同于空格的作用。

数字信号处理习题集(附答案)

第一章数字信号处理概述 简答题: 1.在A/D变换之前和D/A变换之后都要让信号通过一个低通滤波器,它们分别起什么作用? 答:在A/D变化之前为了限制信号的最高频率,使其满足当采样频率一定时,采样频率应大于等于信号最高频率2倍的条件。此滤波器亦称为“抗混叠”滤波器。 在D/A变换之后为了滤除高频延拓谱,以便把抽样保持的阶梯形输出波平滑化,故又称之为“平滑”滤波器。 判断说明题: 2.模拟信号也可以与数字信号一样在计算机上进行数字信号处理,自己要增加一道采样的工序就可以了。 () 答:错。需要增加采样和量化两道工序。 3.一个模拟信号处理系统总可以转换成功能相同的数字系统,然后基于数字信号处理理论,对信号进行等效的数字处理。() 答:受采样频率、有限字长效应的约束,与模拟信号处理系统完全等效的数字系统未必一定能找到。因此数字信号处理系统的分析方法是先对抽样信号及系统进行分析,再考虑幅度量化及实现过程中有限字长所造成的影响。故离散时间信号和系统理论是数字信号处

理的理论基础。 第二章 离散时间信号与系统分析基础 一、连续时间信号取样与取样定理 计算题: 1.过滤限带的模拟数据时,常采用数字滤波器,如图所示,图中T 表示采样周期(假设T 足够小,足以防止混叠效应),把从)()(t y t x 到的整个系统等效为一个模拟滤波器。 (a ) 如果kHz T rad n h 101,8)(=π截止于,求整个系统的截止频 率。 (b ) 对于kHz T 201=,重复(a )的计算。 采样(T) () n h () n x () t x () n y D/A 理想低通T c πω=() t y 解 (a )因为当0)(8=≥ω πωj e H rad 时,在数 — 模变换中 )(1)(1)(T j X T j X T e Y a a j ωω=Ω= 所以)(n h 得截止频率8πω=c 对应于模拟信号的角频率c Ω为 8 π = ΩT c 因此 Hz T f c c 625161 2==Ω= π

数字信号处理试卷及答案

A 一、 选择题(每题3分,共5题) 1、)6 3()(π-=n j e n x ,该序列是 。 A.非周期序列 B.周期6 π = N C.周期π6=N D. 周期π2=N 2、序列)1()(---=n u a n x n ,则)(Z X 的收敛域为 。 A.a Z < B.a Z ≤ C.a Z > D.a Z ≥ 3、对)70()(≤≤n n x 和)190()(≤≤n n y 分别作 20 点 DFT ,得)(k X 和)(k Y , 19,1,0),()()( =?=k k Y k X k F ,19,1,0)],([)( ==n k F IDFT n f , n 在 围时,)(n f 是)(n x 和)(n y 的线性卷积。 A.70≤≤n B.197≤≤n C.1912≤≤n D.190≤≤n 4、)()(101n R n x =,)()(72n R n x =,用DFT 计算二者的线性卷积,为使计算量尽可能的少,应使DFT 的长度N 满足 。 A.16>N B.16=N C.16 实验名称:多采样率数字信号处理 一.实验目的:1. 掌握信号抽取和插值的基本原理和实现; 2.掌握信号的有理数倍率转换。 二.实验原理: 多采样率数字信号处理共分为3方面的问题:信号的整数倍抽取、信号的整数倍插值和信号的有理数倍速率转换。 Matlab 信号处理工具箱提供了抽取函数decimate 用于信号整数倍抽取,其调用格式为: y=decimate(x,M) y=decimate(x,M,n) y=decimate(x,M,’fir’) y=decimate(x,M,n,’fir’) 其中y=decimate(x,M)将信号x 的采样率降低为原来的 M 1,抽取前缺省地采用8阶Chebyshev Ⅰ型低通滤波器压缩频带。 y=decimate(x,M,n)指定所采用Chebyshev Ⅰ型低通滤波器的阶数,通常13 n 。 y=decimate(x,M,’fir’)指定用FIR 滤波器来压缩频带。 y=decimate(x,M,n,’fir’) 指定所用FIR 滤波器的阶数。 Matlab 信号处理工具箱提供了插值函数interp 用于信号整数倍插值,其调用格式为: y=interp(x,L) y=interp(x,L,n,alpha) [y,b]=interp(x,L,n,alpha) 其中y=interp(x,L)将信号的采样率提高到原来的L 倍。 y=interp(x,L,n,alpha)指定反混叠滤波器的长度n 和截止频率alpha ,缺省值为4和0.5。 [y,b]=interp(x,L,n,alpha)在插值的同时,返回反混叠滤波器的系数向量。 信号的有理数倍速率转换是使信号的采样率经由一个有理因子M L 来改变,可以通过插值和抽取的级联来实现。Matlab 信号处理工具箱提供了重采样函数resample 用于有理倍数速率转换,其调用格式为: y=resample(x,L,M); 郑州航空工业管理学院 电子通信工程系 DSP原理及应用课程设计报告 设计题目:基于TMS320F2812 DSP微处理器的最小系统设计 学号:********** 专业:电子信息工程专业 设计日期:2012年6月14日 指导老师:赵成陈宇 设计任务 1、利用Protel软件绘制并添加TMS320F2812的原理图库; 2、利用Protel软件绘制TMS320F2812最小系统的电路原理图,包括时钟电路模块,电源模块、复位电路模块、JTAG接口模块; 3、安装最小系统电路,在CCS下建立工程,编译并将其下载到TMS320F2812最小系统中运行。 相关设备 PC机,CCS集成开发环境,最小系统电路板及元件,XDS510仿真调试器,外用表,示波器,稳压电源。 设计原理 TMS320F2812 DSP微处理器属于通用可编程微处理器,在应用时涉及硬件电路设计及软件设计,在理论课部分,主要是了解了F2812的体系架构及软件开发的相关知识,在具体使用时,需要绘制电路原理图及版图。 TMS320F2812 DSP微处理器运行的基本环境包括时钟电路、电源电路、复位电路及JTAG接口调试电路等,为了便于测试系统的运行情况,一般在其外围直接设计串口通信电路及相关的测试电路,这里即在外围配置了XF及串口通信电路。 可以使用Protel或其他电路版图设计软件绘图,其中需要用到学习过的F2812的封装、管脚分布、时钟电路、复位电路等知识。 可以参考教材附录部分的电路原理图。 通过F2812最小电路的设计,可以将理论与实践统一联系,更深入地理解F2812的开发方法。 应用基础 能使用Protel设计电路原理图; 了解F2812硬件的相关知识及电路设计; 能使用CCS建立并调试DSP工程。 设计报告 在课程设计的最后一次指导课上提交打印版。 目录 一、设计的目的和意义…………………………………………………………………3页 二、CCS软件概述………………………………………………………………………3页 此题为考试题型提示及部分复习范围,全部考试范围为最后讲义及课堂所讲有关内容, 一、填空题(本题共10小题,每小题4分,满分40分) 1. The sample rate is fs, the analysis frequencies of m-th bin in N-point DFT is ( )Hz 2. Using function of window can reduce the ripple level, but the ( ) is widened 3. Frequency sampling filters can be consider as a ( ) and more complex ( ) in cascade. 4. The terms FIR filter coefficients and ( ) are synonymous. 5. Half-band FIR filter stop pass f f =( ). 6. We hope to have more flexibility in trading off between, a window's main lobe width and (sidelobe levels ) in FIR filter designing 7. The number of complex multiplications, for an N-point FFT, is approximately ( ). 8. The spectrum of real signal is symmetrical about (zero ) Hz 9. FIR filter design technique include (Window Design ) Method and (Optimum )Method. 10. bandpass sampling is known as ( ) sampling, ( ) sampling, ( ) sampling, and ( ) sampling. 11. A sudden change in the values of the coefficient sequence, causes ripples, or (sidelobes), in the frequency response. 12. Decreasing the sampling rate is known as (decimation ),increasing the sampling rate is known as (interpolation ). 13. To upsample xold(n) by a factor of four, we typically insert (three zeros )between each sample. 14. In quadrature processing, by convention, the real part of the spectrum is called the ( ) component and the imaginary part of the spectrum is called the ( ) component. 江 苏 大 学 试 题 课程名称 数字信号处理 开课学院 使用班级 考试日期 江苏大学试题第2A页 江苏大学试题第3A 页 江苏大学试题第页 一、填空题:(每空1分,共18分) 8、 数字频率ω是模拟频率Ω对采样频率s f 的归一化,其值是 连续 (连续还是离散?)。 9、 双边序列z 变换的收敛域形状为 圆环或空集 。 10、 某序列的DFT 表达式为∑-== 10 )()(N n kn M W n x k X ,由此可以看出,该序列时域的长度为 N , 变换后数字频域上相邻两个频率样点之间的间隔是 M π 2 。 11、 线性时不变系统离散时间因果系统的系统函数为2 52) 1(8)(22++--=z z z z z H ,则系统的极点为 2,2 1 21-=-=z z ;系统的稳定性为 不稳定 。系统单位冲激响应)(n h 的初值4)0(=h ; 终值)(∞h 不存在 。 12、 如果序列)(n x 是一长度为64点的有限长序列)630(≤≤n ,序列)(n h 是一长度为128点的有限长 序列)1270(≤≤n ,记)()()(n h n x n y *=(线性卷积),则)(n y 为 64+128-1=191点 点的序列,如果采用基FFT 2算法以快速卷积的方式实现线性卷积,则FFT 的点数至少为 256 点。 13、 用冲激响应不变法将一模拟滤波器映射为数字滤波器时,模拟频率Ω与数字频率ω之间的映射变换 关系为T ω = Ω。用双线性变换法将一模拟滤波器映射为数字滤波器时,模拟频率Ω与数字频率ω之 间的映射变换关系为)2tan(2ωT = Ω或)2 arctan(2T Ω=ω。 当线性相位FIR 数字滤波器满足偶对称条件时,其单位冲激响应)(n h 满足的条件为)1()(n N h n h --= , Chapter 2 Solutions 2.1 最小采样频率为两倍的信号最大频率,即44.1kHz 。 2.2 (a)、由ω = 2πf = 20 rad/sec ,信号的频率为f = 3.18 Hz 。信号的奈奎斯特采样频率为6.37 Hz 。 (b)、3 5000π=ω,所以f = 833.3 Hz ,奈奎斯特采样频率为1666.7 Hz 。 (c)、7 3000π=ω,所以f = 214.3 Hz ,奈奎斯特采样频率为428.6 Hz 。 2.3 (a) 1258000 1f 1T S S ===μs (b)、最大还原频率为采样频率的一半,即4000kHz 。 2.4 ω = 4000 rad/sec ,所以f = 4000/(2π) = 2000/π Hz ,周期T = π/2000 sec 。因此,5个周期为5π/2000 = π/400 sec 。对于这个信号,奈奎斯特采样频率为2(2000/π) = 4000/π Hz 。所以采样频率为f S = 4(4000/π) = 16000/π Hz 。因此5个周期收集的采样点为(16000/π samples/sec )(π/400 sec) = 40。 2.5 ω = 2500π rad/sec ,所以f = 2500π/(2π) = 1250 Hz ,T = 1/1250 sec 。因此,5个周期为5/1250 sec 。对于这个信号,奈奎斯特采样频率为2(1250) = 2500 Hz ,所以采样频率为f S = 7/8(2500) = 2187.5 Hz 。采样点数为(2187.5 点/sec)(5/1250 sec) = 8.75。这意味着在模拟信号的五个周期内只有8个点被采样。事实上,对于这个信号来说,在整数的模拟周期中,是不可能采到整数个点的。 2.6 2.7 信号搬移发生在kf S ± f 处,换句话说,频谱搬移发生在每个采样频率的整数倍 0 10 20 30 40 50 60 70 80 90 100 110 120 130 140 150 频率/kHz 1、一线性时不变系统,输入为x (n)时,输出为y (n);则输入为2x (n)时,输出为2y(n) ;输入为x (n-3)时,输出为y(n-3) ________________________________ 。 2、从奈奎斯特采样定理得出,要使实信号采样后能够不失真还原,采样频率fs与信号最咼频率f max关系为:fS> = 2f max 。 3、已知一个长度为N的序列x(n),它的离散时间傅立叶变换为X(e jw),它的N点 离散傅立叶变换X ( K是关于X (e jw)的_N ________ 点等间隔采样。 4、有限长序列x(n)的8点DFT为X ( K),则X (K) = _________ 。 5、用脉冲响应不变法进行IIR数字滤波器的设计,它的主要缺点是频谱的交叠 所产生的混叠_________ 现象。 6、若数字滤波器的单位脉冲响应h(n)是奇对称的,长度为N,贝陀的对称中心是(N-1)/2_______ 。 7、用窗函数法设计FIR数字滤波器时,加矩形窗比加三角窗时,所设计出的滤波 器的过渡带比较窄,阻带衰减比较小。 8、无限长单位冲激响应(IIR )滤波器的结构上有反馈环路,因此是递归型结构。 9、若正弦序列x(n)=sin(30n n /120)是周期的,则周期是N二8 。 10、用窗函数法设计FIR数字滤波器时,过渡带的宽度不但与窗的类型有关,还与窗的采样点数有关 11、DFT与DFS有密切关系,因为有限长序列可以看成周期序列的主值区间截断,而周期序列可以看成有限长序列的周期延拓。 12、对长度为N的序列x(n)圆周移位m位得到的序列用Xn(n)表示,其数学表达式为x m(n)= x((n-m)) N R(n)。 13、对按时间抽取的基2-FFT流图进行转置,并将输入变输出,输出变输入即可得到按频率抽取的基 2-FFT流图。 14、线性移不变系统的性质有交换率、结合率和分配律。 第一章 1、DSP系统的组成:由控制处理器、DSPs、输入/输出接口、存储器、数据传输网络构成。P2图1-1-1 2、TMS320系列DSPs芯片的基本特点:哈佛结构、流水线操作、专用的硬件乘法器、特殊的DSP指令、快速的指令周期。 3、哈佛结构:是一种将程序指令储存和数据储存分开的储存器结构。特点:并行结构体系,是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。系统中设置了程序和数据两条总线,使数据吞吐率提高一倍。 4、TMS320系列在哈佛结构之上DSPs芯片的改进:(1)允许数据存放在程序存储器中,并被算数运算指令直接使用,增强芯片灵活性(2)指令储存在高速缓冲器中,执行指令时,不需要再从存储器中读取指令,节约了一个指令周期的时间。 5、冯诺依曼结构:将指令、数据、地址存储在同一存储器中,统一编址,依靠指令计数器提供的地址来区分是指令、数据还是地址,取指令和去数据都访问同一存储器,数据吞吐率低。 6、流水线操作:TMS320F2812采用8级流水线,处理器可以并行处理2-8条指令,每条指令处于流水线的不同阶段。 解释:在4级流水线操作中。取 指令、指令译码、读操作数、执 行操作可独立地处理,执行完全 重叠。在每个指令周期内,4条 不同的指令都处于激活状态,每 条指令处于不同的操作阶段。 7、定点DSPs芯片:定点格式工作的DSPs芯片。 浮点DSPs芯片:浮点格式工作的DSPs芯片。 (定点DSPs可以浮点运算,但是要用软件。浮点DSPs用硬件就可以)8、DSPs芯片的运算速度衡量标准:指令周期(执行一条指令所需时 一、单项选择题 1. 序列x(n)=Re(e jn π/12 )+I m (e jn π/18 ),周期为( )。 A. 18π B. 72 C. 18π D. 36 2. 设C 为Z 变换X(z)收敛域的一条包围原点的闭曲线,F(z)=X(z)z n-1 ,用留数法求X(z)的反变换时( )。 A. 只能用F(z)在C 的全部极点 B. 只能用F(z)在C 外的全部极点 C. 必须用收敛域的全部极点 D. 用F(z)在C 的全部极点或C 外的全部极点 3. 有限长序列h(n)(0≤n ≤N-1)关于τ= 2 1 -N 偶对称的条件是( )。 A. h(n)=h(N-n) B. h(n)=h(N-n-1) C. h(n)=h(-n) D. h(n)=h(N+n-1) 4. 对于x(n)= n )21(u(n)的Z 变换,( )。 A. 零点为z=21,极点为z=0 B. 零点为z=0,极点为z=21 C. 零点为z=21,极点为z=1 D. 零点为z=2 1 ,极点为z=2 5、)()(101n R n x =,)()(72n R n x =,用DFT 计算二者的线性卷积,为使计算量尽可能的少,应使DFT 的长度N 满足 。 A.16>N B.16=N C.16 A 一、选择题(每题3分,共5题) 1、 )6 3()(π-=n j e n x ,该序列是 。 A.非周期序列 B.周期6 π = N C.周期π6=N D. 周期π2=N 2、 序列)1()(---=n u a n x n ,则)(Z X 的收敛域为 。 A.a Z < B.a Z ≤ C.a Z > D.a Z ≥ 3、 对)70() (≤≤n n x 和)190()(≤≤n n y 分别作20 点 DFT ,得 )(k X 和)(k Y , 19,1,0),()()( =?=k k Y k X k F ,19,1,0)],([)( ==n k F IDFT n f , n 在 范围内时,)(n f 是)(n x 和)(n y 的线性卷积。 A.70≤≤n B.197≤≤n C.1912≤≤n D.190≤≤n 4、 )()(101n R n x =,)()(72n R n x =,用DFT 计算二者的线性卷积,为使计算量尽可能的少,应使DFT 的长度N 满足 。 A.16>N B.16=N C.16 第一章: 1、数字信号处理的实现方法一般有哪几种? 答:数字信号处理的实现是用硬件软件或软硬结合的方法来实现各种算法。(1) 在通用的计算机上用软件实现;(2) 在通用计算机系统中加上专用的加速处理机实现;(3) 用通用的单片机实现,这种方法可用于一些不太复杂的数字信号处理,如数字控制;(4)用通用的可编程 DSP 芯片实现。与单片机相比,DSP 芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法;(5) 用专用的 DSP 芯片实现。在一些特殊的场合,要求的信号处理速度极高,用通用 DSP 芯片很难实现( 6)用基于通用 dsp 核的asic 芯片实现。 2、简单的叙述一下 dsp 芯片的发展概况? 答:第一阶段, DSP 的雏形阶段( 1980 年前后)。代表产品: S2811。主要用途:军事或航空航天部门。第二阶段, DSP 的成熟阶段( 1990 年前后)。代表产品: TI 公司的 TMS320C20 主要用途:通信、计算机领域。第三阶段, DSP 的完善阶段( 2000 年以后)。代表产品:TI 公司的 TMS320C54 主要用途:各个行业领域。 3、可编程 dsp 芯片有哪些特点? 答: 1、采用哈佛结构( 1)冯。诺依曼结构,( 2)哈佛结构( 3)改进型哈佛结构2、采用多总线结构 3.采用流水线技术4、配有专用的硬件乘法-累加器5、具有特殊的 dsp 指令6、快速的指令周期7、硬件配置强8、支持多处理器结构9、省电管理和低功耗 4、什么是哈佛结构和冯。诺依曼结构?它们有什么区别? 答:哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。冯。诺依曼结构:该结构采用单存储空间,即程序指令和数据共 用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。 区别:哈佛:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。冯:当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。 5、什么是流水线技术? 答:每条指令可通过片内多功能单元完成取指、译码、取操作数和执行等多个步骤,实现多条指令的并行执行,从而在不提高系统时钟频率的条件下减少每条指令的执行时间。利用这种流水线结构,加上执行重复操作,就能保证在单指令周期内完成数字信号处理中用得最多的乘法 - 累加运算。(图)6、什么是定点 dsp 芯片和浮点 dsp 芯片?它们各有什么优缺点? 答:若数据以定点格式工作的称为定点 DSP 芯片。若数据以浮点格式工作的称为浮点 DSP芯片。 2009-2010学年第二学期 通信工程专业《数字信号处理》(课程)参考答案及评分标准 一、选择题(每空1分,共20分) 1.序列?? ? ??+??? ??=n n n x 6sin 4cos )(ππ的周期为(A)。 A .24 B. 2π C.8 D.不是周期的 2.有一连续信号)40cos()(t t x a π=,用采样间隔s T 02.0=对)(t x a 进行采样,则采样所得的时域离散信号 )(n x 的周期为(C) A.20 B. 2π C .5 D .不是周期的 3.某线性移不变离散系统的单位抽样响应为)(3)(n u n h n =,该系统是(B )系统。 A .因果稳定 B.因果不稳定 C.非因果稳定 D.非因果不稳定 4.已知采样信号的采样频率为s f ,采样周期为s T ,采样信号的频谱是原模拟信号频谱的周期函数,周期为(A),折叠频率为(C)。 A . s f B.s T C .2/s f D.4/s f 5.以下关于序列的傅里叶变换)(ωj e X 说法中,正确的是(B)。 A.)(ωj e X 关于ω是周期的,周期为π B .)(ωj e X 关于ω是周期的,周期为π2 C .)(ωj e X 关于ω是非周期的 D.)(ωj e X 关于ω可能是周期的也可能是非周期的 6.已知序列)1()()1(2)(+-+-=n n n n x δδδ,则0)(=ωωj e X 的值为(C)。 A.0 B .1 C .2 D.3 7.某序列的DF T表达式为∑-== 1 )()(N n nk M W n x k X ,由此可看出,该序列的时域长度是(A),变换后数字域上 相邻两个频率样点之间的间隔(C )。 A.N B.M C .M /2π D. N /2π 8.设实连续信号)(t x 中含有频率40Hz 的余弦信号,现用Hz f s 120=的采样频率对其进行采样,并利 用1024=N 点DFT 分析信号的频谱,得到频谱的谱峰出现在第(B)条谱线附近。 A.40 B .341 C.682 D .1024 9.已知{},3,421)(,=n x ,则()=-)()(66n R n x (A ),()=+)()1(66n R n x (C ) A .{},0,0,4,3,21 B .{},0,0,4,31,2 C .{}1,,3,4,0,02 D .{}0,3,42,,10, 10.下列表示错误的是(B)。 A .n k N N nk N W W )(--= B .nk N nk N W W =*)( C.k n N N nk N W W )(--= D. 12/-=N N W 11.对于L N 2=点的按频率抽取基2FFT 算法,共需要(A)级蝶形运算,每级需要(C)个蝶形运算。 A.L B.2 N L C. 2 N D.L N + 12.在I IR滤波器中,(C )型结构可以灵活控制零极点特性。 A.直接Ⅰ B.直接Ⅱ C.级联 D .并联 13.考虑到频率混叠现象,用冲激响应不变法设计IIR 数字滤波器不适合于(B)。 A.低通滤波器 B .高通、带阻滤波器 C.带通滤波器 D.任何滤波器 《DSP原理及应用》实验教学大纲 学习DSP的目的是应用其进行研发及工程实践,故实验是《DSP原理及应用》课程学习中的重要环节。通过实验,可以对DSP器件的功能进行实际操作,并在实际操作中熟悉器件的使用特性。实验是DSP应用的基本内容,为学生今后从事相关工作打下基础。 本实验有以下任务:(1)掌握如何使用DSP仿真平台;(2)掌握DSP内部结构和工作原理;(3)熟悉DSP 的指令系统;(4)熟悉用DSP实现各种基本算法。通过实验使学生加深对DSP基本理论、硬件系统、指令系统的理解,学会用仿真器进行开发,使书本上枯燥的内容变得生动,增加学生学习本课程的兴趣。此外学生的实验技能、动手能力、分析问题、解决问题的能力都将得到培养,为进一步进行工程实践奠定良好的基础。 三、实验方式 1、实际操作—要求根据目的要求完成各实验项目,对实验结果进行分析整理并写出实验报告。 2、上机设计仿真—学生先根据实验要求设计出实验电路和实验步骤,后上机进行设计仿真,最后记录仿真结果并分析写出实验报告。 3、基本要求: (1)掌握DSP仿真开发系统的结构。掌握仿真器的连接和安装,熟悉开发软件Code Composer Studio 的界面和基本操作。 (2)掌握TMS320C54x芯片的硬件结构,了解CPU、寄存器和存储器中各数据的含义。 (3)了解TMS320C54x芯片外部设备的工作原理,熟悉数据的处理过程和中断。 (4)了解TMS320C54x芯片的指令系统,熟悉各种指令和基本算法。 (5)能够独立完成简单小程序的编写和调试。 通过实验,使学生基本具有DSP的开发能力。 四、实验项目设置、学时分配及基本要求 数字信号处理复习题 一、选择题 1、某系统)(),()()(n g n x n g n y =有界,则该系统( A )。 A.因果稳定 B.非因果稳定 C.因果不稳定 D. 非因果不稳定 2、一个离散系统( D )。 A.若因果必稳定 B.若稳定必因果 C.因果与稳定有关 D.因果与稳定无关 3、某系统),()(n nx n y =则该系统( A )。 A.线性时变 B. 线性非时变 C. 非线性非时变 D. 非线性时变 4.因果稳定系统的系统函数)(z H 的收敛域是( D )。 A.9.0实验设计:多采样率数字信号处理

DSP原理及其应用技术_课程设计_报告

期末数字信号处理练习题

(完整版)数字信号处理试卷及答案

数字信号处理基础书后题答案中文版

数字信号处理》试题库答案

DSP原理与应用技术-考试知识点总结

数字信号处理试题

数字信号处理期末试卷及答案

DSP原理及应用-(修订版)--课后习题答案

数字信号处理期末考试试题以及参考答案

DSP原理及应用教学大纲

(完整word版)数字信号处理题库(附答案)