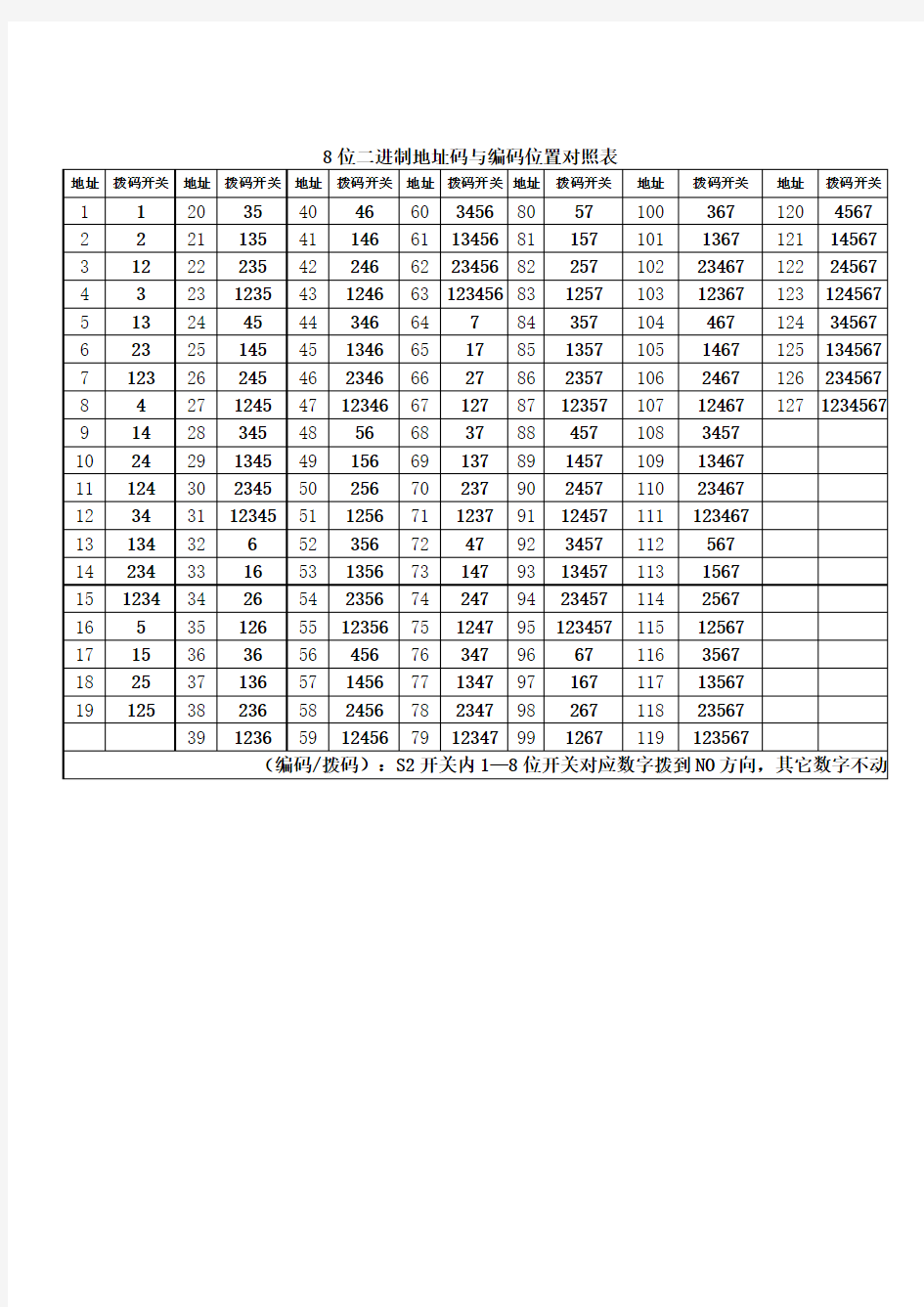

8位二进制地址码与编码位置对照表

四位二进制加法器课程设计

课题名称与技术要求 课题名称: 四位二进制加法器设计 技术要求: 1)四位二进制加数与被加数输入 2)二位数码管显示 摘要 本设计通过八个开关将A3,A2,A1,A0和B3,B2,B1,B0信号作为加数和被加数输入四位串行进位加法器相加,将输出信号S3,S2,S1,S0和向高位的进位 C3通过译码器Ⅰ译码,再将输出的Y3,Y2,Y1,Y0和X3,X2,X1,X0各自分别通过一个74LS247译码器,最后分别通过数码管BS204实现二位显示。 本设计中译码器Ⅰ由两部分组成,包括五位二进制译码器和八位二进制输出器。信号S3,S2,S1,S0和向高位的进位C3输入五位二进制-脉冲产生器,将得到的n(五位二进制数码对应的十进制数)个脉冲信号输入八位二进制输出器,使电路的后续部分得以执行。 总体论证方案与选择 设计思路:两个四位二进制数的输入可用八个开关实现,这两个二进制数经全加器求和后最多可以是五位二进制数。本题又要求用两个数码管分别显示求和结果的十进制十位和各位,因此需要两个译码器Ⅱ分别译码十位和

个位。综上所述,需要设计一个译码器Ⅰ,能将求和得到的五位二进制数译成八位,其中四位表示这个五位二进制数对应十进制数的十位,另四位表示个位。而译码器Ⅱ有现成的芯片可选用,此处可选74LS247,故设计重点就在译码器Ⅰ。 加法器选择 全加器:能对两个1位二进制数进行相加并考虑低位来的进位,即相当于3个1位二进制数相加,求得和及进位的逻辑电路称为全加器。或:不仅考虑两个一位二进制数相加,而且还考虑来自低位进位数相加的运算电路,称为全加器。 1)串行进位加法器 构成:把n位全加器串联起来,低位全加器的进位输出连接到相邻的高位全加器的进位输入。 优点:电路比较简单。 最大缺点:进位信号是由低位向高位逐级传递的,运算速度慢。 2)超前进位加法器 为了提高运算速度,必须设法减小或消除由于进位信号逐级传递所消耗的时间,于是制成了超前进位加法器。 优点:与串行进位加法器相比,(特别是位数比较大的时候)超前进位加法器的延迟时间大大缩短了。 缺点:电路比较复杂。 综上所述,由于此处位数为4(比较小),出于简单起见,这里选择串行进位加法器。 译码器Ⅱ选择 译码是编码的逆过程,将输入的每个二进制代码赋予的含意“翻译”过来,给出相应的输出信号。译码器是使用比较广泛的器材之一,主要分为:变量译码器和码制译码器,其中二进制译码器、二-十进制译码器和显示译码器三种最典型,使用十分广泛。显示译码器又分为七段译码器和八段

《信息理论与编码》,答案,考试重点(1--3章)

《信息理论与编码》习题参考答案 1. 信息是什么信息与消息有什么区别和联系 答:信息是对事物存在和运动过程中的不确定性的描述。信息就是各种消息符号所包含的具有特定意义的抽象内容,而消息是信息这一抽象内容通过语言、文字、图像和数据等的具体表现形式。 2. 语法信息、语义信息和语用信息的定义是什么三者的关系是什么 答:语法信息是最基本最抽象的类型,它只是表现事物的现象而不考虑信息的内涵。语义信息是对客观现象的具体描述,不对现象本身做出优劣判断。语用信息是信息的最高层次。它以语法、语义信息为基础,不仅要考虑状态和状态之间关系以及它们的含义,还要进一步考察这种关系及含义对于信息使用者的效用和价值。三者之间是内涵与外延的关系。 第2章 1. 一个布袋内放100个球,其中80个球是红色的,20个球是白色的,若随机摸取一个球,猜测其颜色,求平均摸取一次所能获得的自信息量 答:依据题意,这一随机事件的概率空间为 120.80.2X x x P ????=???????? 其中: 1 x 表示摸出的球为红球事件, 2 x 表示摸出的球是白球事件。 a)如果摸出的是红球,则获得的信息量是 ()()11log log0.8 I x p x =-=-(比特) b)如果摸出的是白球,则获得的信息量是 ()()22log log0.2 I x p x =-=-(比特) c) 如果每次摸出一个球后又放回袋中,再进行下一次摸取。则如此摸取n 次,红球出现的次数为 () 1np x 次,白球出现的次数为 () 2np x 次。随机摸取n 次后总共所获得信息量为 ()()()() 1122np x I x np x I x + d)则平均随机摸取一次所获得的信息量为 ()()()()()()()()()112211221 log log 0.72 H X np x I x np x I x n p x p x p x p x =+????=-+????=比特/次

8位串行二进制全加器

只用一位二进制全加器为基本元件和一些辅助的时序电路,设计一个8位串行二进制全加器。 Vhdl代码如下: 顶层文件如下: library ieee; use ieee.std_logic_1164.all; entity f8_adder is port(a,b:in std_logic_vector(7 downto 0); c0:in std_logic; s:out std_logic_vector(7 downto 0); c1:out std_logic); end f8_adder; architecture bhv of f8_adder is signal cout:std_logic_vector(7 downto 1); component f_adder is port(ain,bin,cin:in std_logic; cout,sum:out std_logic); end component; begin u1: f_adder port map(ain=>a(0),bin=>b(0),cin=>c0,sum=>s(0),cout=>cout(1)); u2: f_adder port map(ain=>a(1),bin=>b(1),cin=>cout(1),sum=>s(1),cout=>cout(2)); u3: f_adder port map(ain=>a(2),bin=>b(2),cin=>cout(2),sum=>s(2),cout=>cout(3)); u4: f_adder port map(ain=>a(3),bin=>b(3),cin=>cout(3),sum=>s(3),cout=>cout(4)); u5: f_adder port map(ain=>a(4),bin=>b(4),cin=>cout(4),sum=>s(4),cout=>cout(5)); u6: f_adder port map(ain=>a(5),bin=>b(5),cin=>cout(5),sum=>s(5),cout=>cout(6)); u7: f_adder port map(ain=>a(6),bin=>b(6),cin=>cout(6),sum=>s(6),cout=>cout(7)); u8: f_adder port map(ain=>a(7),bin=>b(7),cin=>cout(7),sum=>s(7),cout=>c1); end bhv; 全加器描述: library ieee; use ieee.std_logic_1164.all; entity f_adder is port(ain,bin,cin:in std_logic; cout,sum:out std_logic); end f_adder; architecture fd1 of f_adder is

8位二进制加法计算器

一:本实验设计的是一个8为二进制加法计算器,其功能就是对两个八位的二进制数执行加法运算,并可以异步清零。 二:电路可划分为三部分:半加器、全加器和复位电路。 1、半加器: 真值表 a b so co 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 电路图 2全加器:由半加器和或门组成 电路图 3复位电路: 复位电路通过en控制,当en为‘1’时,执行加法运算,输出正确的值,当en为‘0’时,输输出及结果为全0. 三:实验波形仿真和VHDL 1、仿真图:

2、VHDL代码 1)半加器h_adder: library ieee; use ieee.std_logic_1164.all; entity h_adder is port (a,b :in std_logic; co,so :out std_logic); end entity h_adder; architecture fh1 of h_adder is begin so <= not(a xor (not b));co <= a and b ; end architecture fh1; 2)或门or2a: library ieee; use ieee.std_logic_1164.all; entity or2a is port (a,b :in std_logic; c: out std_logic); end entity or2a; architecture one of or2a is begin c <= a or b ; end architecture one; 3)全加器f_adder: library ieee;

初中七年级信息技术13信息与二进制编码教案

初中七年级信息技术1.3信息与二进制编码教案 课时:1课时 课型:新授课 教学方法:讲练法 教学用具:课件、投影、 教学目标: 1、知识目标:实施传统的“讲练”法模式,使学生了解信息编码;安全使用计算机的方法。 2、能力目标:培养学生能对二进制做简单计算。 教学重点:计算机的安全使用;使用计算机的良好首先的培养。 教学难点:二进制的计算。 课前准备: 1、复习计算机系统的结构图;储存容量的基本计算; 2、课件、多媒体教室的试用。 教学过程 一、复习:(5分钟) 师:同学们,通过上节课的学习,我们知道计算机能够正常工作不但需要有硬件部分,还需要软件来支持,否则配置再高的计算机也如同一堆毫无生机的废品。下面请同学思考一下,试着画出计算机系统的结构图。 (可以请同学在黑板上画。) 师:通过大家的演示,再对比一下老师所给的正确结构图。(看大屏演示) (师生共同讨论总结) 计算机系统的组成: 运算器 中央处理器 控制器 主机 随机存储器 内存诸器 只读存诸器 硬件部分 输入设备 外部设备输出设备 计算机系统外存储器 系统软件 软件部分 应用软件

师:问题二,表示存储器存储容量的基本单位,常用的单位之间的换算关系是:1KB= B 1MB= KB 1GB= MB 生:回答。 二、新课导言: 师:大家在日常生活中是否能见到一些只存在两种状态的事或物存在?能否例举出来? 生:例举事物…… 师:能从大家所例举的事物中看出只存在两种状态的事物多存在于电子器件上,这是为什么呢?(由于学生为初一年级的学生,知识含量有限,所以由老师做以下简单的解答)电子器件最易形成两种稳定状态,如电压的高低、电流的通断。所以我们在计算机中采用了以0和1两个数字组成的二进制数的形式来表示计算机中所有的信息。(在大屏幕上展示十进制数的运算法则:逢十进一。启发学生说出二进制的运算法则。) 二、新课: 1、[以课件1展示二进制运算法则,与十进制进行转换运算。] 二进制的重点与难点就是同学们不易改变头脑中的十进制进位方式。 2、[以课件2展示病毒对计算机的危害。] 计算机病毒是指可以在计算机系统中起破坏作用的程序。通过课件的展示,使同学们认识到预防计算机病毒的重要性。同时使同学们在使用计算机的过程中,都应该遵循一定的道德标准,不应该有违反法律和法规的行为。 三、课堂练习: 1、把十进制的5、6、8、9转化为二进制的数。 2、(11)十=()二(15)十=()二 教学后记:

中华人民共和国学科分类与代码国家标准(GBT13745-2009)

目次 目次............................................................. 错误!未定义书签。前言............................................................. 错误!未定义书签。引言............................................................. 错误!未定义书签。1范围............................................................... 错误!未定义书签。 2 术语和定义......................................................... 错误!未定义书签。 3 学科分类原则....................................................... 错误!未定义书签。 4 学科分类依据....................................................... 错误!未定义书签。 5 学科分类代码体系的说明............................................. 错误!未定义书签。 6 编码方法........................................................... 错误!未定义书签。7学科分类代码表..................................................... 错误!未定义书签。110 数学............................................................. 错误!未定义书签。120 信息科学与系统科学............................................... 错误!未定义书签。130 力学............................................................. 错误!未定义书签。140 物理学........................................................... 错误!未定义书签。150 化学............................................................. 错误!未定义书签。160 天文学........................................................... 错误!未定义书签。170 地球科学......................................................... 错误!未定义书签。180 生物学........................................................... 错误!未定义书签。190 心理学........................................................... 错误!未定义书签。210 农学............................................................. 错误!未定义书签。220 林学............................................................. 错误!未定义书签。230 畜牧、兽医科学................................................... 错误!未定义书签。240 水产学........................................................... 错误!未定义书签。310 基础医学......................................................... 错误!未定义书签。320 临床医学......................................................... 错误!未定义书签。330 预防医学与公共卫生学............................................. 错误!未定义书签。340 军事医学与特种医学............................................... 错误!未定义书签。350 药学............................................................. 错误!未定义书签。360 中医学与中药学................................................... 错误!未定义书签。410 工程与技术科学基础学科........................................... 错误!未定义书签。413 信息与系统科学相关工程与技术..................................... 错误!未定义书签。416 自然科学相关工程与技术........................................... 错误!未定义书签。420 测绘科学技术..................................................... 错误!未定义书签。430 材料科学......................................................... 错误!未定义书签。440 矿山工程技术..................................................... 错误!未定义书签。450 冶金工程技术..................................................... 错误!未定义书签。460 机械工程......................................................... 错误!未定义书签。470 动力与电气工程................................................... 错误!未定义书签。480 能源科学技术..................................................... 错误!未定义书签。490 核科学技术....................................................... 错误!未定义书签。

八位二进制加法器课程设计

长安大学电子技术课程设计 课题名称______________ 班级______________ 姓名______________ 指导教师 日期______________

前言 8位二进制加法器,它的功能主要是实现两个8位二进制数的相加,其结果的范围应该在00000000到111111110之间,即000到510之间。加法器在实际应用中占据着十分重大的地位,从我们呱呱坠地起,到小学,到初中,到高中,到大学,到工作,等等。我们能离开加法吗,不能!加法可以说是一切运算的基础,因此8位二进制加法器的设计是很有必要的。 那么我们如何设计一个8位二进制加法器呢?在实际应用中,我们通常输入的是十进制数,一个八位二进制数所对应的最大的十进制数是255,于是输入两个范围在000到255之间的数,首先通过二-十进制编码器将输入的三位十进制数的个位、十位、百位分别转换为8421BCD码,得到两个十二位字码,再通过加法器将它们相加,逢10进1,得到一个新的十二位字码,再用7447数字显示译码器将这个十二位字码还原到原来的三位十进制数。最后输出的就是一个三位十进制数,其范围在000到510之间。通过上述方法我们实现了八位二进制数的相加,从而达到了题目的要求。 为实现上述目的,我们需要查阅相关资料。通过查阅,理解以及加以运用,我们认识到了收集资料的不易性,但同时也得到了不少收获,可以说是有苦有甜。同时,虽然我们基本设计出了这个八位二进制加法器,但是不必可避免地会产生一些问题,比如说在连线上可能有更简便的途径,在元件的选用上可能还有其它更简便的方法,在控制上可能还不够精简,等等。我们希望在以后的实践中能找出更好的方法,也希望能吸取这次设计中的不足,逐渐改善。另外,在电子设计的过程中,与同组同学之间的合作配和是十分重要的。我在此次设计中也充分认识到这一点的重要性,我相信这次的电子设计能够为我们将来的工作奠定一定的基础。

国家标准学科分类与代码表

学科分类与代码 共设5个门类、58个一级学科、573个二级学科、近6000个三级学科。 学科分类代码是基于一定原则对现实科学体系按其内在联系加以归类并以符合逻辑的排列形式表述出来且赋予代码的一种学科。《学科分类与代码》国家标准,是科学发展、教育、科技统计、学科建设等方面工作的一个重要依据。鉴于学科分类在科学发展中所具有的特殊地位,联合国、美国、德国和日本等国际组织与世界发达国家都很重视学科分类体系标准化工作,纷纷制定相应的学科分类与代码标准。 《学科分类与代码》使用说明 中华人民共和国国家标准学科分类与代码表GB/T13745-92。 Classification and code disciplines。 1.主题内容: 本标准规定了学科的分类与代码。 2. 适用范围: 本标准适用于国家宏观管理和科技统计。 本标准的分类对象是学科,不同于专业和行业,不能代替文献、情报、图书分类及学术上的各种观点。 3. 相关术语: 3.1 学科: 学科是相对独立的知识体系。 3.2 学科群: 学科群是具有某一共同属性的一组学科。每个学科群包含了若干个分支学科。 4. 分类原则: 4.1 科学性原则: 根据学科研究对象的客观的、本质的属性和主要特征及其之间的相关联系,划分不同的从属关系和并列次序,组成一个有序的学科分类体系。 4.2 实用性原则: 对学科进行分类和编码,直接为科技政策和科技发展规划,以及科研经费、科技人才、科研项目、科技成果统计和管理服务。 4.3 简明性原则: 对学科层次的划分和组合,力求简单明了。 4.4 兼容性原则: 考虑国内传统分类体系的继承性和实际使用的延续性,并注意提高国际可比性。 4.5 扩延性原则: 根据现代科学技术体系具有高度动态性特征,应为萌芽中的新兴学科留有余地,以便在分类体系相对稳定的情况下得到扩充和延续。 4.6 唯一性原则: 在标准体系中,一个学科只能用一个名称、一个代码。 5. 分类依据: 本标准依据学科研究对象,研究特征、研究方法,学科的派生来源,研究目的、目标等五方面进行划分。 6.编制原则: 6.1 本标准所列学科应具备其理论体系和专门方法的形成;有关科学家群体的出现;有关研究机构和教学单位以及学术团体的建立并展开有效的活动;有关专著和出版物的问世等条件。

国家标准编号字母有GB、GBT

国家标准编号字母有GB、GB/T还有什么字母,代表什么含义?chenhuacai121 11级分类:理工学科被浏览1624次2013.04.30 GB:为强制性国标 GB/T:推荐性国标 国家标准: GB 国家标准 JJF 国家计量技术规范 JJG 国家计量检定规程 GHZB 国家环境质量标准 GWPB 国家污染物排放标准 GWKB 国家污染物控制标准 GBn 国家内部标准 GBJ 工程建设国家标准 GJB 国家军用标准 行业标准: ZY 中医药行业标准 YZ 邮政行业标准 YY 医药行业标准 YS 有色冶金行业标准 YD 通信行业标准 YC 烟草行业标准 YB 黑色冶金行业标准 XB 稀土行业标准 WS 卫生行业标准 WM 外贸行业标准 WH 文化行业标准 WB 物资行业标准 TD 土地行业标准 TB 铁道行业标准 SY 石油行业标准 SN 商品检验行业标准 SL 水利行业标准 SJ 电子行业标准 SH 石油化工行业标准 SC 水产行业标准 SB 商业行业标准 QX 气象行业标准 QJ 航天行业标准 QC 汽车行业标准 QB 轻工业行业标准 NY 农业行业标准 MZ 民政行业标准 MT 煤炭行业标准

MH 民用航空行业标准 L Y 林业行业标准 LD 劳动行业标准 LB 旅游行业标准 JY 教育行业标准 JR 金融行业标准 JT 交通行业标准 JGJ 建筑行业工程建设规程JG 建筑行业标准 JC 建材行业标准 JB 机械行业标准 HS 海关行业标准 HJ 环保行业标准 HY 海洋行业标准 HGJ 化工行业工程建设规程HG 化工行业标准 HB 航空行业标准 GY 广播电影电视行业标准GH 供销合作行业标准 GA 公安行业标准 FZ 纺织行业标准 EJ 核工业行业标准 DZ 地质行业标准 DL 电力行业标准 DB 地震行业标准 DA 档案行业标准 CY 新闻出版行业标准 CJJ 城建行业工程建设规程CJ 城建行业标准 CECS 工程建设推荐性标准CH 测绘行业标准 CB 船舶行业标准 BB 包装行业标准

EDA课程设计八位二进制全加器

EDA课程设计八位二进制全加器

EDA设计说明书 课程名称: EDA技术实用教程 设计题目:八位二进制全加器 院系:电子信息与电气工程学院学生姓名: 学号: 专业班级: 指导教师:李响 年 6 月 1

1. 设计目的 熟悉利用QuartusⅡ的原理图输入法设计简单的组合电路,掌握层次化设计的方法,并经过一个八位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。 2. 设计原理 2.1 一位全加器的原理 一位全加器能够用两个半加器及一个或门连接而成,因此需要首先完成半加器的设计。在本设计中,将采用原理图输入法来完成设计。 一位全加器的设计步骤: ①为本项工程设计建立文件夹; ②输入设计项目和存盘; ③将设计项目设计成可调用的元件; ④设计全加器顶层文件; ⑤将设计项日设置成工程和时序仿真。 2.2 八位全加器的原理 一个八位全加器能够由八个一位全加器构成,加法器之间的进位能够用串行方式实现,即将低位加法器的进位输出cout 与相邻的高位加法器的最低进位输入信号cin 相接。

3. 设计方案与仿真 3.1 一位全加器的设计与仿真 全加器的实现是以半加器的实现为基础的,因此,要设计全加器应首先设计一个一位的半加器。半加器的实现方案为: ①为此项工程建立文件夹; ②在基本元件库中,选中需要的元件,将元件(包含元件 and2、not 、xnor 和输入输出引脚input、output)调入原理图编辑窗口中; ③将己设计好的原理图文件存盘; ④将所设计的半加器设置成可调用的元件。 用原理图输入法所设计的半加器原理图如图3-1所示,利用QuartusⅡ软件平台,根据图3-1所示电路,可生成一个半加器元件符号,如图3-2所示。在半加器的基础上,为了建立全加器的顶层文件,必须再打开一个原理图编辑窗口,方法同上。其中,所选择的元件包含半加器、或门和输入输出引脚,由此可得到如图3-3所示的全加器原理图;进而可生成个全加器元件符号,如图3-4所示。 图3-1 半加器原理图图3-2 半加器元件符号

国际国内标准分类及编号

国际国内标准分类及编号

国内标准分类及编号 ?国家标准GB ?化工HG ?机械JB ?核工业EJ ?电力DL ?石油SY ?船舶CB ?纺织FZ ?林业LY ?煤炭MT ?农业NY ?轻工QB ?汽车QC ?航天QJ ?电子SJ ?水利 ?商检SN ?铁道TB ?通信YD ?民用航空MH ?水产SC

?石化SH ?商业SB ?交通JT ?城建CJ ?地方标准DB ?环境保护HJ ?卫生WS ?烟草YC ?医药YY ?质监CCGF ?安全标准AQ ?包装标准BB ?CECS标准?地质矿产DZ ?公共安全GA ?建材标准JC ?建工标准JG ?计量标准JJ ?粮食标准LS ?冶金标准YB ?邮政标准YZ ?国军标GJB

?航空标准HB ?特种设备TSG ?有色金属YS ?海洋标准HY ?稀土标准XB ?体育标准TY ?金融标准JR ?文化行业WH ?档案标准DA ?物资标准WB ?新闻出版CY ?气象标准QX ?海关标准HS ?海军军标HJB ?外经贸WM ?广播电视GY ?劳动安全LD ?土地管理TD ?旅游标准LB ?民政标准MZ ?教育行业JY ?测绘标准CH

?兵工民品WJ ?能源标准NB ?宝山钢铁BQB ?中石油CNPC ?鞍山钢铁ASB ?深圳地方SZ ?专业标准ZB ?中文版标准 国外标准分类 ?英国标准BS ?德国标准DIN ?日本标准JIS ?美国ASME ?国际电工IEEE ?石油学会API ?国际标准ISO ?美国UL ?澳大利亚AS ?美国汽车SAE ?美国焊接AWS ?美国腐蚀NACE ?美国阀门MSS

EDA8位二进制并行加法器

实验二:8位加法器的设计 1.实验目的 (1)学习Quartus Ⅱ/ISE Suite/ispLEVER软件的基本使用方法。 (2)学习GW48-CK或其他EDA实验开发系统的基本使用方法。 (3)了解VHDL程序的基本结构。 2.实验内容 设计并调试好一个由两个4位二进制加法器级联而成的8位二进制并行加法器,并用GW48-CK或其他EDA实验开发系统(事先应选定拟采用的实验芯片的型号)进行硬件验证。3.实验要求 (1)画出系统的原理图,说明系统中各主要组成部分的功能。 (2)编写各个VHDL源程序。 (3)根据系统的功能,选好测试用例,画出测试输入信号波形或编号测试程序。 (4)根据选用的EDA实验开发装置编好用于硬件验证的管脚锁定表格或文件。 (5)记录系统仿真、逻辑综合及硬件验证结果。 (6)记录实验过程中出现的问题及解决办法。 4.实验条件 (1)开发条件:Quartus Ⅱ 8.0。 (2)实验设备:GW48-CK实验开发系统。 (3)拟用芯片:EPM7128S-PL84。 5.实验设计 1)系统原理图 为了简化设计并便于显示,本加法器电路ADDER8B的设计分为两个层次,其中底层电路包括两个二进制加法器模块ADDER4B,再由这两个模块按照图2.1所示的原理图构成顶层电路ADDER8B。 ADDER4B 图2.1 ADDER4B电路原理图

A8[7..0] 图 2.1 ADDER8B电路原理图 2)VHDL程序 加法器ADDER8B的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。ADDER4B的VHDL源程序: --ADDER4B.VHD LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ADDER4B IS PORT(C4:IN STD_LOGIC; A4:IN STD_LOGIC_VECTOR(3 DOWNTO 0); B4:IN STD_LOGIC_VECTOR(3 DOWNTO 0); S4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); CO4: OUT STD_LOGIC); END ENTITY ADDER4B; ARCHITECTURE ART OF ADDER4B IS SIGNAL S5:STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL A5,B5:STD_LOGIC_VECTOR(4 DOWNTO 0); BEGIN A5<='0'&A4; B5<='0'&B4; S5<=A5+B5+C4; S4<=S5(3 DOWNTO 0); CO4<=S5(4); END ARCHITECTURE ART; ADDER8B的VHDL源程序: --ADDER8B.VHD LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ADDER8B IS

键盘操作说明

用户手册 1 版权 Copyright ? 2010, GE Security , Inc. 版权所有 未经 GE Security 事先书面同意,除非美国版权法特别许可,否则不得全部或部分拷贝本文件或对其进行复制。 文件编号/修订本:0226-2010LPT (2010年 2 月) 免责声明 若该文件中所包含的信息有任何更改,恕不另行通知。GE Security 公司不对所出现不准确或疏漏承担任何责任;尤其要声明的是,对于因直接或间接使用或应用本文件内容而导致的个人或其它方面的损失或风险,我们也不会承担任何责任。最新的文件请联系您的本地供应商或访问 https://www.360docs.net/doc/1f17285850.html, 。 本发行版本中包含屏幕捕获示例和日常操作中使用的报告。可能内含虚构的个人和公司名的示例。任何名称(姓名)和地址如与企业或个人的名称(姓名)和地址雷同,纯属巧合。 商标和专利 GE 和 GE 标志是通用电气公司的注册商标。SCR-M409为GE 安防产品型号。 本文件中使用的其它商标名为相应产品制造商或厂商的商标或注册商标。 预定用途 按照产品原本的设计用途来使用;请参阅产品数据表和用户文档。最新的文件请联系您的本地供应商或访问 https://www.360docs.net/doc/1f17285850.html, 。

目录 第一章产品介绍———————————————————————————————3 第二章安装说明———————————————————————————————3 第三章操作必读———————————————————————————————6 第四章矩阵控制操作指南———————————————————————————8 第五章云台控制操作指南———————————————————————————16 说明: 本用户手册适用于GE 公司的SCR-M409矩阵控制键盘。本手册包括产品概述、详细说 明以及连接和安装方式。如果您有疑问或关心的问题,此文件也提供如何与技术支持 部门取得联系的信息。 若要有效使用该文档,您至少应具备以下资质条件:CCTV 系 统和元件的基础知识;电气配线和低压电气连接的基础知识。在安装或操作此产品之前,请完全阅读这些说明及所有附属文件。 注意:合格的服务人员应遵守所有适用的规程,以执行所需的硬件安装工作。

八位二进制加法器论文

前言 本次课程设计介绍了一种基于数字电子技术的八位二进制加法器,实现了如下功能: 1、八位二进制加数与被加数输入 2、三位数码管显示 3、三位十进制加数与被加数的输入 该电路系统主要分为八位二进制加法器和三位十进制加法器两个系统:八位二进制加法器系统由二进制输入电路、二进制加法运算电路、二进制码到十进制8421BCD码的转换电路和三位数码管显示输出4个模块组成; 三位十进制加法器系统由十进制的输入电路、三位十进制8421BCD码加法运算电路、四位数码管显示输出3个模块组成。 设计过程: 首先由本小组三名同学:夏程鉴,邢晓理,王维在互联网以及图书馆查阅了相关资料与文献,并参考了清华大学出版社06年版《数字电子技术基础》等参考教材,进行了资料整理以及设计构思。随后三名组员分工设计,由邢晓理同学设计输入系统电路,王维同学设计加法系统电路,夏程鉴同学设计二进制_十进制BCD码转换系统电路和输出系统。最后将电路模块整合为一个整体电路系统,并应用Multisim软件进行了设计电路图的绘制和仿真检验。

目录 前言 (1) 摘要 (3) 关键词 (3) 设计要求 (3) 一、设计方案简介 1、方案一 (4) 2、方案二 (5) 3、方案三 (6) 二、单元电路设计与分析 1、八位二进制加数与被加数输入(邢晓理) (7) 2、八位二进制数的加法运算(王维) (8) 3、二进制数转换为十进制8421BCD码(夏程鉴) (9) 4、八位二进制加法器总体电路图 (13) 5、十进制加数与被加数输入(邢晓理) (14) 6、三位BCD码加法器(王维) (15) 7、三位十进制加法器总体电路图 (16) 元件明细表 (17) 结束语 (18) 参考文献 (19) 鸣谢 (19) 评语 (20)

中华人民共和国国家标准《全国主要产品分类与代码 第1部分可运输

《全国主要产品分类与代码》国家标准发布实施 ———粮食行业相关代码介绍 中华人民共和国国家标准《全国主要产品分类与代码第1部分:可运输产品》(GB/T 7635.1-2002)(以下简称“可运输产品代码”标准)经中华人民共和国国家质量监督检验检疫总局发布,于2003年4月1日开始实施。 “可运输产品代码”标准是一项大型的基础性标准,是与国际通行产品目录协调一致的国家产品分类编码标准体系。规定了全国可运输产品的分类原则与方法、代码结构、编码方法、分类与代码。主要用于信息处理和信息交换。 一、《全国主要产品分类与代码》的组成 《全国主要产品分类与代码》由相对独立的两个部分组成,第一部分为可运输产品,第二部分为不可运输产品。第一部分由五大部类组成,与联合国统计委员会制定的《主要产品分类》(CPC)1998年10版的第1部分相对应,一致性程度为非等效。 “可运输产品代码”标准是对《全国工农业产品(商品、物资)分类与代码》(GB/T7635—1987)的修订。主要变化有: 1、对GB/T7635—1987标准名称进行了修改; 2、对代码结构和编码方法进行了修改。GB/T7635—1987代码结构是四层8位数字码,每层2位码,采用了平均分配代码的方法。“可运输产品代码”标准代码结构是六层8位数字码,前五 —1 —

层是一层1位码,第六层是3位码,采用了非平均分配代码方法; 3、产品分类和类目的设置进行了较大幅度的调整。 4、采用了GB/T10113-1988《分类编码通用术语》中确立的术语;产品类目采用了规范的产品名称。 二、我国主要粮食与机械产品分类代码介绍 在“可运输产品代码”标准中,与粮食行业相关的产品分类代码涉及我国原粮、米面油产品和粮油加工机械产品等三个方面。摘录如下: —2 —

四位二进制加法器电工电子课程设计

长安大学 电子技术课程设计 4位二进制加法器 专业车辆工程 班级22010901 姓名韩塽 指导教师顾樱华 日期2011、6、26

目录 一、技术要求 (2) 二、摘要 (2) 三、总体设计方案的论证及选择 (2) 1、加法器的选取 (2) 2、译码器的选取 (2) 3、数码管的选取 (3) 四.设计方案的原理框图,总体电路图,接线图及说明 (3) 1、总体原理图 (3) 2、总体接线图 (4) 五.单元电路设计,主要元器件选择与电路参数计算 (4) 1、逻辑开关 (4) 2、加法器设计 (5) 3、译码器设计 (7) 4、数码管设计 (9) 六、收获与体会 (10) 七、参考文献 (11) 八、附件(元器件清单) (12) 评语 (13)

一.技术要求 1.四位二进制加数与被加数输入 2.二位数码管显示 二.摘要 该设计主要包括两个部分:一是用加法器实现四位二进制加数与被加数的输入,二是将相加产生的二进制和数用二位数码管显示,在此设计中加法器是重点,数码显示是难点。数码显示采用计数器,译码器七段译码显示管来实现。加法器分为半加器和全加器,半加器只能实现两个一位二进制数的相加,其只考虑两个加数本身的求和而不考虑低位来的进数位。目前使用最广泛的二进制加法器是二进制并行加法器。 三.总体设计方案的论证及选择 1.加法器的选取 二进制并行加法器是一种能并行产生两个n位二进制算术和的组合逻辑电路。按其进位方式的不同,可分为串行进位二进制并行加法器和超前进位二进制并行加法器两种类型。所以根据加法器的工作速度选取超前进位加法器。这里供选取的超前进位加法器有74LS283,CT74LS283,SN74LS283,DM74LS283,HD74LS283,M74LS283 可供选择。由于我们是非电专业,对电子器件的选取要求不高,为使设计简单起见所以选74LS283加法器。 2.译码器的选取 译码器是一种具有“翻译”功能的逻辑电路,这种电路能将输入二进制代码的各种状态,按照其原意翻译成对应的输出信号。译码器是组合逻辑电路的一个重要的器件,在显示译码器的选择上有七段译码器和八段译码器。此

8位二进制加法器

8位二进制加法器 1.摘要: 本次设计主要是如何实现8位二进制数的相加,即两个000到255之间的数相加,由于在实际中输入的往往是三位十进制数,因此,被加数和加数是两个三位十进制数,范围在000到255之间,通过六个二-十进制编码器(即74LS147)分别将加数和被加数的个位、十位、百位转换为8421BCD码,于是得到了两个12位字码,将它们接入三个四位超前进位并行加法器(即74LS283),其中原加数三位十进制数的个位转换得到的四位BCD码与被加数三位十进制数的个位转换得到的四位BCD码相加,串入到第一个74LS283的接线端,得到一个四位8421BCD码。同理,原加数和被加数的十位转换得到的四位BCD码相加也得到一个8421BCD码。同理,百位也是如此。需要注意的是:由于这12位BCD码是由三位十进制数转换过来的,因此在用加法器相加时,要逢10进一。于是通过一些与非门、非门和加法器构成一个新的加法器,使该加法器能对这十二位BCD码进行计算,并且逢10进1,这样得到一个十二位BCD码,即相加结果三位十进制数所对应的BCD码,再通过7447数字显示译码器将这十二位8421BCD码还原成一个三位十进制数,用数码管显示出来,得到一个三位十进制数,即为所求的结果。另外,本次设计不仅可以适用加数和被加数是000到255的数字,同时也适用于加数和被加数是000到999的任何一个数,这是本次设计的创新之处。2.关键字: 二-十进制编码器、四位超前进位并行加法器、7447七段数码显示译码器、逢十进一、数码管。 3.设计要求: 1.八位二进制加数与被加数的输入; 2.三位数码管显示; 3.三位十进制加数与被加数的输入。 4.正文: 第一章系统概述 本次设计的目的是实现两个八位二进制数的相加,那么我们如何实现呢?通常在实际中输入的是三位十进制数,而要求是八位二进制数,八位二进制数换算成三位十进制数最大为

基于FPGA的八位加法器

课程实训报告 课程名称EDA 技术 设计题目基于FPGA的八位加法器院系名称机械电子工程学院 专业班级电子信息工程2014级 姓名 学号 成绩 指导教师 2016年12月

目录 1、设计目的、要求.................................................................................................................... - 2 - 1.1、设计目的.................................................................................................................... - 2 - 1.2、系统设计要求............................................................................................................ - 2 - 2、设计原理及相关硬件............................................................................................................ - 3 - 2.1、系统设计方案及原理................................................................................................ - 3 - 2.2、硬件原理.................................................................................................................... - 3 - 3、主要模块设计........................................................................................................................ - 5 - 3.1、模块Key-led............................................................................................................. - 5 - 3.2、模块Adder................................................................................................................. - 6 - 4、系统编译及仿真过程............................................................................................................ - 6 - 4.1、系统编译.................................................................................................................... - 6 - 4.2、仿真............................................................................................................................ - 7 - 5、硬件验证过程和分析............................................................................................................ - 8 - 5.1、引脚设置和保护........................................................................................................ - 8 - 5.2、硬件下载.................................................................................................................... - 8 - 5.3、硬件测试结果及分析................................................................................................ - 9 - 6、实验参考程序........................................................................................................................ - 9 - 6.1、模块key_led............................................................................................................. - 9 - 6.2、模块adder4b........................................................................................................... - 13 - 6.3、模块adder8b........................................................................................................... - 14 -总结 ......................................................................................................................................... - 15 -参考文献...................................................................................................................................... - 0 -附录 ........................................................................................................................................... - 1 -