一个16位RISC CPU设计

二.主要模块设计

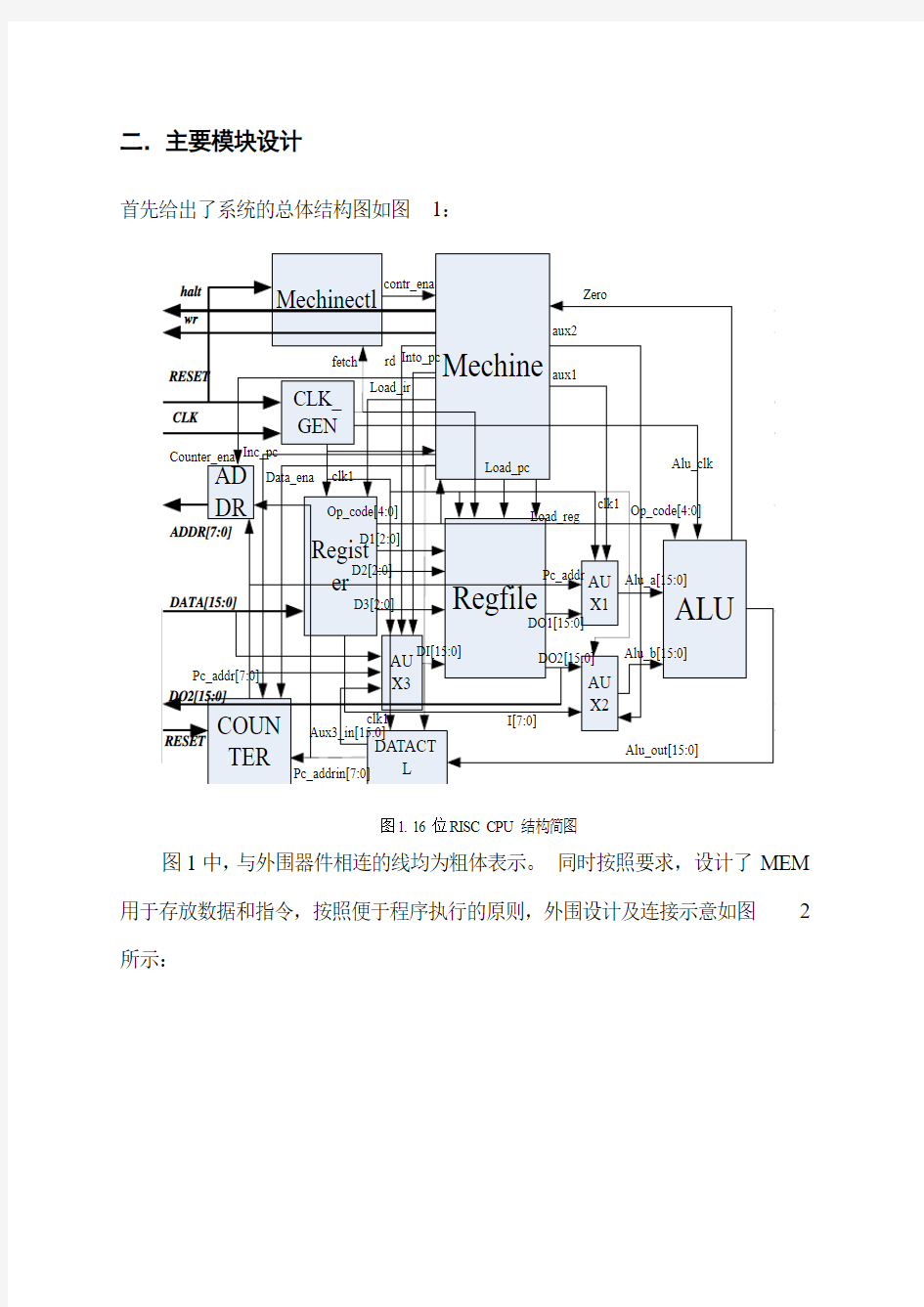

首先给出了系统的总体结构图如图1:

图1. 16位RISC CPU结构简图

图1中,与外围器件相连的线均为粗体表示。同时按照要求,设计了MEM 用于存放数据和指令,按照便于程序执行的原则,外围设计及连接示意如图2所示:

图2. CPU 外部电路及连接关系图

在设计的部件中,针对不同功能的实现,采取了比较繁琐的射击方式。在MEMORY之外存在几大设计部件。主要部件设计如下:

一.状态控制机:

contr_ena

clk1

Inc_pc Data_ena

aux1aux2rd Into_pc Load_pc Load_reg Load_ir

Zero Counter_ena halt wr

这是最关键的部件,而且,在选定8个状态为一个运行周期的格局以后,对所有指令包括HAL T 全部在用统一的指令周期。这不可避免的导致了单元和面积的增加。此处存在较大的改进余地。指令分为五部分:取指,译码,执行,存储器访问,结果写回。最后一部分很有可能进行第二次寄存器读写。

指令运行周期:(八个时钟周期) 第一周期:取指令 第二周期:指令译码 第三周期:空

第四周期:地址线跳转,需要运算的数据送到数据线。 第五周期:ALU 时钟信号,ALU 运算。

第六周期:根据情况,对不同指令,分别进行数据的寄存器读写。 第七周期:对于需要再次读写寄存器的操作,如跳转指令中的地址写回寄

存器,完成存储。

第八周期:FETCH信号,指令跳转到下面要运行得指令地址,包括正常PC+1和指令跳转地址,为下条指令取指做准备。

控制信号说明:

输入信号:

Op_code[4:0]:操作数,输入现在是什么指令。

Clk1:时钟信号,大多数的控制信号需要时钟信号的上跳沿触发。

Contro_ena:由控制机产生的信号,控制机复位。

Zero : 由ALU送来,用于条件转移指令(BZ,BNZ)的辅助信号。

输出信号:(十二个控制信号)

Halt:为“1”停机信号。

Wr:为“1”写存储器。

Load_ir:为“1”指令寄存器取指。

Rd&Into_pc:“11”则将PC输入到寄存器;“10”则选择存储器的数据到寄存器;“01”则选择ALU的数据到寄存器。

Load_pc:为“1”则将输入寄存器的值输出,“0”则为其他寄存器。

Load_reg:为“1”写寄存器。

Aux1:为“1”选择Pc地址输出到ALU的A端。为“0”则为寄存器输出。

Aux2:为“1”选择立即数地址输出到ALU的B 端。为“0”则为寄存器输出。

Inc_pc:为“1”则PC+1。

Counter_ena:为“1”地址计数器输出指令地址,“0”则输出数据地址。

Data_ena:为“1”则ALU输出地址,即跳转地址,“0”则为正常Pc。

二.在剩下的部件里,ALU是整个系统运行的基础,这里针对需要的指令,设计的ALU包括“+”“-”“&”“|”“>>”“<<”六种运算。

三.REGFILE的设计,按照数据进出的要求,设计了一条输入通道DI,两条输出通道DO1,DO2。及三个寄存器编码信号,并设计了两个控制信号,便于实现不同寄存器的写入写出操作和切换。

DI[15:0]

NUM1[2:0]NUM2[2:0]

四.REGISTER,,原本只想设计一个指令寄存器,由于设计的个体性,不惜耗费了大量资源在这里面。至少现在是这样认为。根据综合出来的结果看,这部分的电路远较想象的复杂,这里面有设计描述的问题,更应该是算法的架构问题。在设计过程中,后续电路不同操作指令的需要的操作数,全都在这里面进行了完善的准备。没有任何后期处理,这里的数值输出后直接可以进行相应的操作。在设计中没有想好这一步。现在初步认为可以独立设计专门的对数据进行处理的部件,例如,移位,扩展,而REGISTER 只作为指令寄存器,这样应该会有较大的性能改进。

D1[2:0]D3[2:0]I[15:0]

Op_code[4:0]

clk1Load_ir reset

五.其他部分多为多路选择器架构,不再赘述。