Ledit的使用教程

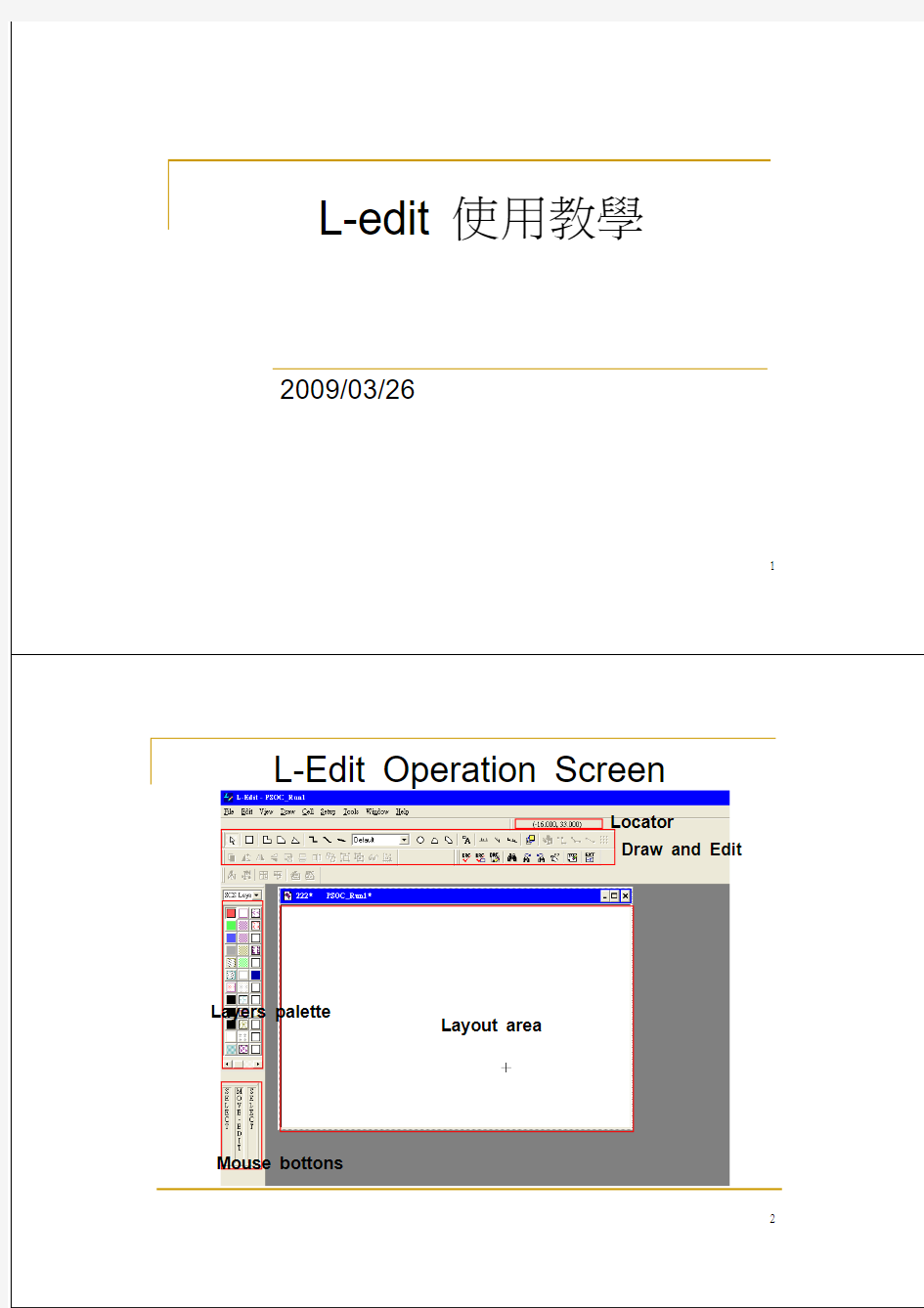

L-Edit Operation Screen

Locator

Draw and Edit

Layers palette

Layout area

Mouse bottons

.

.. . .. . ...

.

. . .

.

7

Example: Draw beam’s layout Beam完成後的側視圖:

由Coventorware產生的3D model

2.選取慾繪製圖形的形狀

3.用尺規確認線寬

繪製時按住滑鼠左鍵拖曳

基板部分

1.選取此層材質:

繼續進行anchor繪製動作:

基板+anchor部分Anchor部分

13 Substrate+anchor+beam

基板+anchor+beam部分beam部分

Save

可存成6.x或7.x版本L-edit可開啟之.tdb檔

TSMC工艺的_版图教程

目录 前端电路设计与仿真........................................................................................错误!未定义书签。 第一节双反相器的前端设计流程............................................................错误!未定义书签。 1、画双反相器的visio原理图 ........................................................错误!未定义书签。 2、编写.sp文件................................................................................错误!未定义书签。 第二节后端电路设计................................................................................错误!未定义书签。 一、开启linux系统..........................................................................错误!未定义书签。 2、然后桌面右键重新打开Terminal ...............................................错误!未定义书签。双反相器的后端设计流程................................................................................错误!未定义书签。 一、schematic电路图绘制 ..............................................................错误!未定义书签。 二、版图设计....................................................................................错误!未定义书签。 画版图一些技巧:............................................................................错误!未定义书签。 三、后端验证和提取........................................................................错误!未定义书签。 第三节后端仿真........................................................................................错误!未定义书签。 其它知识............................................................................................错误!未定义书签。

CMOS反相器版图设计

成绩评定表 学生姓名班级学号7 专业课程设计题目CMOS反相器评 语 组长签字: 成绩 日期20 年月日

课程设计任务书 学院信息科学与工程学院专业 学生姓名班级学号 课程设计题目CMOS反相器 实践教学要求与任务: 1.用tanner软件中的S-Edit编辑CMOS反相器。 2.用tanner软件中的TSpice对CMOS反相器电路进行仿真并观察波形。 3.用tanner软件中的L-Edit绘制CMOS反相器版图,并进行DRC验证。 4.用tanner软件中的TSpice对版图电路进行仿真并观察波形。 5.用tanner软件中的layout-Edit对电路网表进行LVS检验观察原理图与版图的匹配程度。 工作计划与进度安排: 第一周 周一:教师布置课设任务,学生收集资料,做方案设计。 周二:熟悉软件操作方法。 周三~四:画电路图 周五:电路仿真。 第二周 周一~二:画版图。 周三:版图仿真。 周四:验证。 周五:写报告书,验收。 指导教师: 201 年月日专业负责人: 201 年月日 学院教学副院长: 201 年月日

目录 目录............................................................................................................................ III 1.绪论 (1) 1.1设计背景 (1) 1.2设计目标 (1) 2.CMOS反相器 (2) 2.1CMOS反相器电路结构 (2) 2.2CMOS反相器电路仿真 (3) 2.3CMOS反相器的版图绘制 (4) 2.4CMOS反相器的版图电路仿真 (4) 2.5LVS检查匹配 (5) 总结 (7) 参考文献 (8) 附录一:原理图网表 (9) 附录二:版图网表 (10)

ASIC的版图设计实现方法

第八章 ASIC的版图设计实现方法 对于大规模、超大规模专用集成电路来说, 其实现方法可归纳为两大类:①版图设计法, ②器件编程法。版图设计法包括版图的全定制设计、半定制设计和定制设计, 适用于大批量的专用集成电路设计实现, 由本章介绍。下章介绍ASIC的器件编程实现方法, 包括ROM系列、PAL、GAL系列和FPGA系列的器件编程,适用于中小批量或样片的ASIC设计实现。 § 8-1 全定制设计方法(Full-Custom Design Approach) 全定制设计适用于对设计质量本身有着最严格要求的芯片, 比如要求有最小信号延迟、最小芯片面积, 最佳设计结果, 而对相应在设计周期、设计成本上所付出的代价却可以在所不惜。 这种设计方法主要以人工设计为主, 计算机作为绘图与规则验证的工具而起辅助作用。对所得版图的每一部分, 设计者将进行反复的比较、权衡、调整、修改: 对元器件, 要有最佳尺寸; 对拓扑结构, 要有最合理的布局; 对连线, 要寻找到最短路径, ... 。这样精益求精, 不断完善, 以期把每个器件和内连接都安排得最紧凑、最适当。在获得最佳芯片性能的同时, 也因为芯片面积最小而大大降低每片电路的生产成本, 以低价位而占领市场。 目前, 产量浩大的通用集成电路从成本与性能考虑而采用全定制设计方法。其它设计方法中最底层的单元器件(如标准单元法中的库单元、门阵列法中的宏单元), 因其性能和面积的要求而采用全定制设计方法。 模拟电路因其复杂而无规则的电路形式(相对于数字电路而言)在技术上只适宜于采用全定制设计方法。 简单、规模较小而又有一定批量的专用电路, 在设计者力所能及的情况下( 时间与正确性的把握) , 也建议采用全定制设计方法。 图8-1是一个由全定制设计方法设计的模拟集成电路的版图(7640电路) 需要给予解释的是, 对于大规模、超大规模集成电路, 全定制的设计方法似乎是不可思议的。事实上, 这确实需要许多人年的艰苦努力: 将一个庞大的电路系统按功能分解为若干个模块和更多个子模块, 具有丰富经验积累的设计人员分工合作, 每人负责一个部分 108

TSMC工艺的_版图教程

目录 前端电路设计与仿真 (2) 第一节双反相器的前端设计流程 (2) 1、画双反相器的visio原理图 (2) 2、编写.sp文件 (2) 第二节后端电路设计 (4) 一、开启linux系统 (5) 2、然后桌面右键重新打开Terminal (8) 双反相器的后端设计流程 (9) 一、schematic电路图绘制 (9) 二、版图设计 (32) 画版图一些技巧: (48) 三、后端验证和提取 (49) 第三节后端仿真 (58) 其它知识 (61)

前端电路设计与仿真 第一节双反相器的前端设计流程1、画双反相器的visio原理图 in M0 M1V DD M2 M3 out fa 图1.1 其中双反相器的输入为in 输出为out,fa为内部节点。电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。 2、编写.sp文件 新建dualinv.txt文件然后将后缀名改为dualinv.sp文件 具体实例.sp文件内容如下:

.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角*********** 划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。 划紫色线条处的端口名称和顺序一定要一致 MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同) MMX D G S B MNAME

版图设计期末复习

第一章绪论 1、什么是Scaling-down,它对集成电路的发展有什么重要作用?在器件按比例缩小过程中 需要遵守哪些规则(CE,CV,QCE),这些规则的具体实现方式 (1)为了保证器件性能不变差,衬底掺杂浓度要相应增大。通过Scaling-down使集成电路的集成度不断提高,电路速度也不断提高,因此Scaling-down是推动集成电 路发展的重要理论。 (2)在CE规则中,所有几何尺寸,包括横向和纵向尺寸,都缩小k倍;衬底掺杂浓度增大k倍;电源电压下降k倍。 (3)在CV规则中,所有几何尺寸都缩小k倍;电源电压保持不变;衬底掺杂浓度增大k2倍。 (4)在QCE规则中,器件尺寸k倍缩小,电源电压α/k倍(1<α 4、传输门结构,原理 (1)由两个增强型MOS管(一个P沟道,一个N沟道)组成。 (2)C=0,!C=1时,两个管子都夹断,传输门截止,不能传输数据。 (3)C=1,!C=0时,传输门导通。 (4)双向传输门:数据可以从左边传输到右边,也可以从右边传输到左边,因此是一个双向传输门。 成绩评定表 课程设计任务书 目录 目录 .......................................................................................................... 错误!未定义书签。 1.绪论 ....................................................................................................... 错误!未定义书签。 设计背景 ........................................................................................ 错误!未定义书签。 设计目标 ........................................................................................ 错误!未定义书签。 2.四输入或非门 ......................................................................................... 错误!未定义书签。 四输入或非门电路结构 ................................................................ 错误!未定义书签。 四输入或非门电路仿真 ................................................................ 错误!未定义书签。 四输入或非门的版图绘制 ............................................................ 错误!未定义书签。 四输入或非门的版图电路仿真 .................................................... 错误!未定义书签。 LVS检查匹配 ................................................................................. 错误!未定义书签。总结 .......................................................................................................... 错误!未定义书签。附录一:原理图网表 ................................................................................ 错误!未定义书签。附录二:版图网表 .................................................................................... 错误!未定义书签。 题目: cmos反相器的电路设计及版图设计 初始条件: Cadence ORCAD和L-EDIT软件 要求完成的主要任务: 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD和L-EDIT软件。 (2)设计一个cmos反相器电路。 (3)利用ORCAD和L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰 写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD和L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对CMOS反相器电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日系主任(或责任教师)签名:年月日 目录 摘要 (3) 绪论 (5) 1软件介绍及电路原理 (6) 1.1软件介绍 (6) 1.2电路原理 (6) 2原理图绘制 (8) 3电路仿真 (10) 3.1瞬态仿真 (10) 3.2直流仿真 (11) 4版图设计及验证 (12) 4.1绘制反相器版图的前期设置 (12) 4.2绘制反相器版图 (13) 4.3 DRC验证 (15) 结束语 (17) 参考文献 (18) 摘要 CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。本文将简单的介绍基于ORCAD和L-EDIT的CMOS反相器的电路仿真和版图设计,通过CMOS反相器的电路设计及版图设计过程,我们将了解并熟悉集成电路CAD的一种基本方法和操作过程。 关键词:CMOS反相器ORCAD L-EDIT版图设计 第九章 版图设计流程及设计方法学习指导 学习目标与要求 1.了解集成电路版图设计及验证相关EDA工具; 2.掌握集成电路版图设计及验证相关理论知识; 3. 掌握集成电路版图设计流程、方法及设计技巧 学习重点 1.集成电路版图设计及验证相关EDA工具 2.集成电路版图设计流程、方法及设计技巧 学习难点 1.集成电路版图设计及验证相关理论知识; 2.不同集成电路版图设计的方法及设计技巧 第一节版图设计概念 1.定义:版图设计是创建工程制图(网表)的精确的物理描述过程,而这一物理描述遵守 有制造工艺、设计流程以及通过仿真显示为可行的性能要求所带来的一系列约束。 2.各种类型集成电路版图 第二节版图设计工具-TANNER L-EDIT 集成电路设计近年来发展相当迅速,许多设计需要借助计算机辅助设计软件。 作为将来从事集成电路设计的工作人员,至少需要对版图有所了解,但是许多软件(如cadence)实在工作站上执行的,不利于初学者。 L-Edit软件是基于PC上的设计工具,简单易学,操作方便,通过学习,掌握版图的设计流程。 一、Tanner Pro 简介 Tanner Pro 是一套集成电路设计软件,包括S-EDIT 、T-SPICE 、W-EDIT 、L-EDIT 与LVS ,他们的主要功能分别如下: 1、S-Edit :编辑电路图; 2、T-Spice :电路分析与模拟; 3、W-Edit :显示T-Spice 模拟结果; 4、L-Edit :编辑布局图、自动配置与绕线、设计规则 检查、截面观察、电路转化; 5、LVS :电路图与布局结果对比。 版图设计工具-Tanner L-EDIT Tanner Layout Editor -版图编辑大师TANNER 最精华的部分在哪里 Virtuoso Layout Editor 界面漂亮友好 功能强大完备 操作方便高效 ASIC的版图设计实现方法 对于大规模、超大规模专用集成电路来说, 其实现方法可归纳为两大类:①版图设计法, ②器件编程法。版图设计法包括版图的全定制设计、半定制设计和定制设计, 适用于大批量的专用集成电路设计, 由本章介绍。下章介绍ASIC的器件编程实现方法, 包括ROM 系列、PAL、GAL系列和FPGA系列的器件编程。 §1 全定制设计方法(Full-Custom Design Approach) 全定制设计适用于对设计质量本身有着最严格要求的芯片, 比如要求有最小信号延迟、最小芯片面积, 最佳设计结果, 而对相应在设计周期、设计成本上所付出的代价却可以在所不惜。 这种设计方法主要以人工设计为主, 计算机作为绘图与规则验证的工具而起辅助作用。对所得版图的每一部分, 设计者将进行反复的比较、权衡、调整、修改:对元器件, 要有最佳尺寸; 对拓扑结构, 要有最合理的布局; 对连线, 要寻找到最短路径... 。这样精益求精, 不断完善, 以期把每个器件和内连接都安排得最紧凑、最适当。在获得最佳芯片性能的同时, 也因为芯片面积最小而大大降低每片电路的生产成本, 以低价位而占领市场。 目前, 产量浩大的通用集成电路从成本与性能考虑而采用全定制设计方法。其它设计方法中最底层的单元器件(如标准单元法中的库单元、门阵列法中的宏单元), 因其性能和面积的要求而采用全定制设计方法。 模拟电路因其复杂而无规则的电路形式(相对于数字电路而言)在技术上只适宜于采用全定制设计方法。 简单、规模较小而又有一定批量的专用电路, 在设计者力所能及的情况下( 时间与正确性的把握) , 也建议采用全定制设计方法。 图1是一个由全定制设计方法设计的模拟集成电路的版图(7640电路) 需要给予解释的是, 对于大规模、超大规模集成电路, 全定制的设计方法似乎是不可思议的。事实上, 这确实需要许多人年的艰苦努力: 将一个庞大的电路系统按功能分解为若干个模块和更多个子模块, 具有丰富经验积累的设计人员分工合作, 每人负责一个部分的设计, 最后拼接完成。即使对于每个人负责的子模块电路, 也要充分利用电路的规则性和重复性进行设计。比如寄存器可由一排D触发器构成, 只要精心设计好一只D触发器的版图, 就可以利用计算机图形软件中的复制功能, 拉出一排D触发器也就是一个寄存器的版图了。当然,每个D触发器还要考虑彼此之间版图的偶合度问题。 108 课程设计 题目 CMOS集成电路版图课程设计 学院专业电子科学与技术 年级班级 1011班 姓名学号 指导老师 2013年 6 月 首先在理论上介绍了集成电路版图设计方法的详细步骤以及设计规则的特点。并结合几个触发器的版图设计实例详细讲解了集成电路版图设计的基本步骤技巧与准则。由于模拟集成电路的性能与版图设计密切相关,所以着重介绍CMOS 模拟电路版图设计的一般思路,优化器件结构和平面布局使寄生效应对电路性能的影响降至最低。集成电路版图设计是把设计思想转化为设计图纸的过程,包括数字电路和模拟电路设计。本文针对版图设计过程,验证方法,以及如何通过合理的布局规划,设计出高性能、低功耗、低成本、能实际可靠工作的芯片版图。 关键词:版图设计;MOS; 面积; 设计规则 Abstract First of all, in theory, introduces the detailed steps of integrated circuit layout design method and the characteristics of the design rules. And combined with the landscape design of several triggers in detail the basic steps of integrated circuit layout design skills and standards. Due to the performance of the analog integrated circuit and layout design are closely related, so the landscape design of CMOS analog circuits is introduced the general train of thought, optimize the device structure and plane layout of parasitic effects on circuit performance impact to a minimum. Integrated circuit layout design is to put the design into the process of design drawing, including digital circuit and analog circuit design. This article in view of the landscape design process, the authentication methods, and how to through the reasonable layout planning, design a high performance, low power consumption, low cost, practical and reliable working of the chip layout. Key words: landscape design; MOS; Area; Design rules TSMC工艺的版图教程(DOC 43页) 目录 前端电路设计与仿真 (3) 第一节双反相器的前端设计流程 (3) 1、画双反相器的visio原理图 (3) 2、编写.sp文件 (3) 第二节后端电路设计 (5) 一、开启linux系统 (5) 2、然后桌面右键重新打开Terminal 7 双反相器的后端设计流程 (8) 一、schematic电路图绘制 (8) 二、版图设计 (22) 画版图一些技巧: (31) 三、后端验证和提取 (32) 第三节后端仿真 (38) 其它知识 (42) 前端电路设计与仿真 第一节双反相器的前端设计流程1、画双反相器的visio原理图 in M0 M1V DD M2 M3 out fa 图1.1 其中双反相器的输入为in 输出为out,fa为内部节点。电源电压V DD=1.8V,MOS管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。 2、编写.sp文件 新建dualinv.txt文件然后将后缀名改为dualinv.sp文件 具体实例.sp文件内容如下: 查看波形按钮按下后弹出以下对话框 单击此处 如果要查看内部节点的波形,双击 Top处 单击这些 节点即可 查看波形 如果有多 个子电路 请单击此 处的Top 查看 如果要查看测量语句的输出结果请查看.MTO文件(用记事本打开) 至此前端仿真教程结束 第二节后端电路设计 前序(打开Cadence软件) 一、开启linux系统 双击桌面虚拟机的图标 选择Power on this virtual machine 开启linux之后 在桌面右键选择 Open Terminal 输入 xhost local:命令按回车 之后输入 su xue命令按回车,这样就进入了xue用户四输入或非门电路和版图设计

集成电路设计cmos反相器的电路设计及版图设计

第09章版图设计流程及设计方法

定制版图设计基础

版图课程设计

TSMC工艺的版图教程(DOC 43页)