关于用ADS调用EMPro的方法

关于将ADS的layout导入到EMPro的设置步骤

1、找到ADS安装目录下的“hpeesof.cfg”文件,路径为

“D:\Agilent\ADS2013_06\config\hpeesof.cfg”

2、在文本添加(位置任意,我添加在文本末尾)

“ADS_EMPROHOME=D:/Agilent/EMPro2015_01/win32_64/bin”,该目录指向EMPro的执行程

序,如图

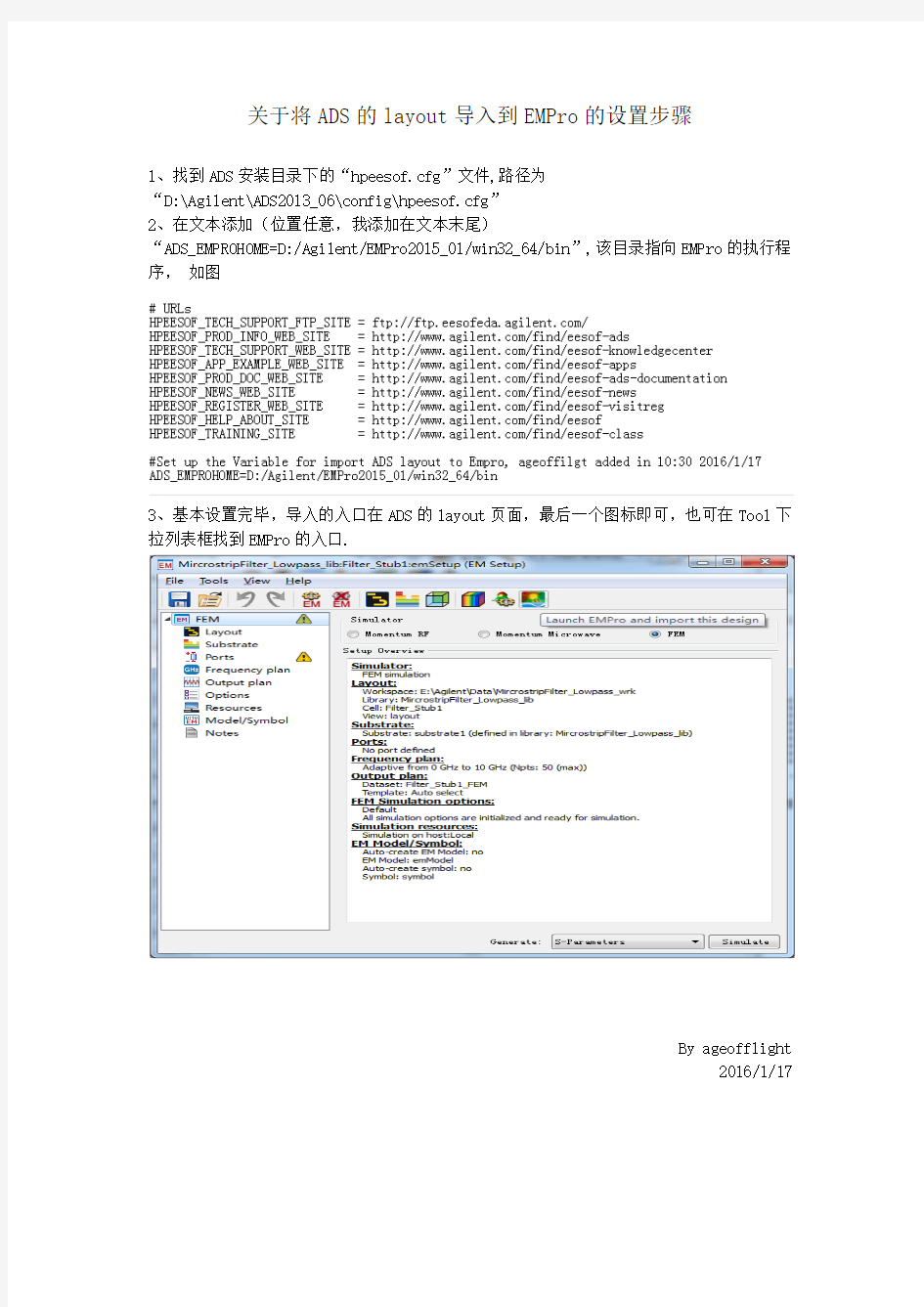

3、基本设置完毕,导入的入口在ADS的layout页面,最后一个图标即可,也可在Tool下

拉列表框找到EMPro的入口.

By ageofflight

2016/1/17

LoadPullConstPdel

ADS load pull simulations for constant output power Harmonic Balance 1-Tone simulation (HB1Tone_LoadPull_ConstPdel): This setup sweeps the load reflection coefficient in a circular region of the Smith Chart and optimizes the source power level for each load reflection coefficient until the desired power is delivered to the load. The data display shows contours of constant PAE, bias current, gain, and gain compression. The input reflection coefficient is also shown for a particular load that you specify. This allows you to pick the optimal load that produces the best PAE, gain, gain compression, or bias current, or make trade-offs amongst these specifications. The lower left SmallSignal and Sweep3 parameter sweeps are only used to obtain output powers when the device is being driven with a small signal. These output powers are used as references in the gain compression computations. When using this schematic, there are a number of different things you need to specify. First, you would replace the device with your device or amplifier. You have to set the bias voltages or modify the bias network, as needed. However, the data display calculates the DC power consumption assuming current probe Is_low is connected to supply voltage node Vs_low and current probe Is_high is connected to supply voltage node Vs_high. If you delete any of these or re-name them, you will have to modify the Pdc equation on the corresponding data display so the DC power consumption is computed correctly.

ADS2011_Load_Pull_官方设计指南

Enhancements to Agilent ADS’s Load Pull DesignGuide Andy Howard, 2/23/2012 After the ADS 2011.10 release, we have updated the Load Pull DesignGuide. We have added several simulation setups and re-organized the menus to make them easier to navigate. This document discusses what is new. This is the new menu structure: 1 ? Copyright Agilent Technologies, 2012

This shows some of the selections under the main menu selections: The (Maury) – Find Optimal Load for Specified Output Power and the selections under Mismatch Analysis are new. 2 ? Copyright Agilent Technologies, 2012

These are the rest of the menu selections, including the new ones under Mismatch Analysis: 3 ? Copyright Agilent Technologies, 2012

ADS1.2的详细使用步骤

ADS1.2的使用 0.ADS1.2的安装 略,详情参见“ADS1.2的详细安装步骤.doc” 1.新建工程 现在可以通过“开始”—“程序”—“ARM Developer Suite v1.2”—“CodeWarrior for ARM Developer Suite”来打开开发软件了,如图1-14所示。 图1-14 启动Metrowerks CodeWarrior for ARM Developer Suite v1.2后界面如图1-15所示。

图1-15 在CodeWarrior中新建一个工程的方法有两种,可以在工具栏中单击“New”按钮,如图1-16所示。也可以在“File”菜单中选择“New。。。”菜单,如图1-17所示。 图1-16

图1-17 这样打开一个如图1-18所示的窗口。该窗口有Project、File和Object 三个选项卡,现在我们新建工程,故选Project选项卡。这个对话框中为用户提供了7种可选择的工程类型。此7种工程类型已经在图中标出,大家熟悉一下。 这里我们选择第一种ARM Executable Image工程类型,在“Project name:”下输入工程名,如test,点击“Location:”文本框的“Set..”按钮,浏览选择想要将该工程保存的路径。如存放在E盘的armtest文件夹中,进入E盘后 按照图1-19,图1-20的步骤完成。

图1-18 图1-19

图1-20 改完名后,双击armtest文件夹再点击“保存”按钮,就会出现图1-21所示界面,此时点击“确定”按钮即可建立一个新的名为test的工程,这个时候会出现test.mcp的窗口,如图1-22所示。 图1-21

ADS负载牵引仿真心得

ADS中负载牵引的一些心得 加入ADS群半年多来,不时在群里面碰到有人问做负载牵引时出现的不收敛问题,虽然自己也自告奋勇的出来聊几句,奈何自己的文采有限,无法说清楚这个问题。其实我自己半年前也曾为此问题困扰一个星期之久,幸好有群里面的流星和羽纤二位大哥的指点,二位大哥对我在ADS操作和射频微波功放方面的困惑进行了无私的指点,加快了我完成了雷达发射机的研制进程,对此我深表感谢。前些时候,群里面部分同样如我半年前一样在负载牵引上遇到困惑的人邀请我写一个实例,用这个实例来说明如何解决负载牵引中碰到的不收敛问题,由于这几天我刚接手了另外两个雷达发射机的研制项目,一直没有抽出足够的时间来写,今天有时间就做个注解,写得不好,不要介意,但愿本文档对一些刚入门的新手在碰到负载牵引时出现的不收敛问题能提供一些帮助。 下面我以freescale的新一代功放管MRF6V2300作为例子来说明负载牵引问题。MRF6V2300是freescale推出的新一代功放管,CW输出功率为300W,额定漏工作电压为50V,工作频率为10-600MHz,价格仅500元一只,是米波雷达和广播电视发射机的廉价实用管子。其DATASHEET上提供了三个典型的频率点的输入和输出阻抗:27MHz,220MHz,450MHz。 参考静态偏置电压典型值为2.6V时,其静态偏置电流典型值是900mA,因为比较容易,这里面我不作静态电流的仿真了,直接采用静态偏置电压2.6V(ADS 仿真结果是919mA)。 先仿真频点f1=27MHz,datasheet上显示其输出负载Z load=3.50+j*0.19。我们打开ADS,新建一个空白原理图,在其工具栏的DesignGuide上点击下拉菜 单中选择Amplifier点1-Tone Nonlinear Simulations展开,选择Load-Pull-PAE,Output Power Contours然后点击OK按钮就行了,出来如图1-1所示的原始原理图和图1-2所示的原始仿真图:

基于ADS的功率放大器详解

说明档 写本文的目的在于如何用ADS设计大功率放大器,只是一个总结档。所用芯片为MW6S9060N, 参考其他资料文献,并用于ADS中一步一步进行仿真。 特别说明:因为本文并不是为了设计PA,而是学习之用,文中有些部分实际中并不需要,例如偏置电压,不需要仿真,设计之后具体调节偏置电压以达到最佳IP3要求等。线性度也是如此,因为当时就是想感受一下整个设计流程,就没调整线性度,真正设计的时候可以用功率回退10dB或者预失真技术解决线性度问题。 实际调试过程中,应该注重整体电路调整,不作描述。文中可能会出现一些问题和错误,希望大家指正。 衷心期待各位射频设计高手指点。 联系方式: QQ:64956883 E-mail: meet2005924@https://www.360docs.net/doc/229619192.html,

Topic: The Power Loadpull Technique For The Impedance Written by: Gaolong Sun Date: 11th Sep, 2009

1. Introduction This paper focus on a design of high power amplier in communication system. With the characteristic of high output power, high efficiency, gain, OIP3, power amplifier can be widely used in the world. This paper will use MW6S004N to show the procedure to how to design a power amplifier. 2. Basic knowledge a. RF amplifier block diagram: b. Maximum available power from source () is transferred to load when AVS P Ω==500Z Z IN c. Reflection factor: 00 Z Z Z Z V V IN IN +?==Γ+? d. Voltage standing wave ratio (VSWR): | |1||1||||Γ?Γ+= = MIN MAX V V VSWR 1 1 ||+?= ΓVSWR VSWR e. Return loss: ||log 20)(Γ?=dB RL

Load pull名词解释!!!

Load pull名词解释!!! LOAD PULL 是不是负载牵引啊,大功率测试是不是就常用负载牵引方法,具体这是一种什么现象或者方法,请高手指教 1 近年来由於微波通讯技术的进步,及通讯频宽与移动性越来越高的需求,使得无线区域网路(Wi reless LAN)在人类日常生活中之重要性大幅提昇,进而带动產学界纷纷投入此系统电路技术及產品之研发。 其中,尤以IEEE所制定的802.11a、g、HiperLAN通讯系统最受瞩目,均採用OFDM(Orthogonal Frequency Division Multiplexing;正交分频多工)的技术OFDM是一种数位展频调变技术,已成为新的无线通讯应用中最热门之传输调变选择,使用OFDM技术可增加宽频、降低杂讯、提高保密性与解决多路径衰弱等通讯障碍,OFDM技术可使设备在有动态和静态多路干扰的情况下,仍保持稳定可靠的性能,因而它在当今无线通讯领域中处於核心地位。而该技术当前的应用范围还包括了地面数位电视广播、及行动电话网路等。 此外,由於OFDM的调变方式为BPS K、QPSK、16QAM及64QAM,对於线性度要求较高,且调变讯号经过功率放大器產生的谐波将造成非线性失真,严重影响功率输出,继而决定了通讯距离的长短;又功率放大器之电源功率消耗几乎佔整个收发机之三分之一,故其效率往往是决定电池的续航力的重要因素;且大讯号操作时之阻抗变化及热效应之影响,导致製程厂目前所提供的Nonlinear Models之精确度已不符使用,均使得射频积体化功率放大器之设计困难度大幅提高。因此我们藉由负载拉移(Load-Pull)原理来改善增益压缩点,进而降低谐波的非线性失真,模拟功率放大器的最大输出功率负载点,继而实现高功率转换效率、高输出功率、高线性射频功率放大器之设计,且利用负载拉移量测系统(Load-Pull Measurement System)来进行验证,并建立相关之功率元件库(Pow er-cell Libraries)以达到电路模组化之研究发展目标。 2 负载拉移原理(Load-pull) : RF功率放大器在大讯号工作时,电晶体的最佳负载阻抗会随著输入讯号功率的增加而跟著改变。因此,我们必须在史密斯图(Smith chart)上,针对不同的输入功率準位,每给定一个输入功率值时绘製出在不同负载阻抗时的等输出功率曲线(Power contours),帮助我们找出最大输出功率时的最佳负载阻抗,这种方法称之为Load-Pull。 Load-pull模拟平台: 我们可以利用负载拉移(Load-pull)之观念,藉由高频电路设计辅助软体(Agilent ADS or Ansoft Desi gner)来建构模拟平台。功率放大器之设计最主要目的就是要能得到最大的输出功率,所以需要有良好的输出入阻抗匹配网路,输入阻抗匹配网路的主要目的是要提供够高的增益,而输出阻抗匹配网路是要达到所要求的输出功率。 由於电晶体工作在趋近饱和区与线性区之交界时,其AC load line会随著输入讯号的增加而改变,尤其S21参数会因输入讯号的增加而变小,因此转换功率增益将因电晶体工作在饱和区与线性区之交界而变小。所以,原本电晶体在小讯号状态下,输出入端都是设计在共軛匹配的GMAX最佳情况下,输出入讯号成正比关係;一旦电晶体於大讯号操作工作时,对输出功率之最佳负载阻抗匹配点会变动,所以电晶体就无法得到最大的功率输出,所以我们需藉由高频电路辅助软体,以Load-Pul l的原理有规则性的搜寻史密斯图上的每个区域,找出功率放大器最大功率输出时之最佳外部负载阻抗ZL点。 此模拟系统包含二个部份,分别为负载阻抗调节及阻抗匹配之参数粹取,其说明如下: (1)负载阻抗调节:此系统的主要观念是以极座标表示法,有规则性的以不同大小与相角的方式在史密斯图(Smith chart)上每一点进行模拟,藉由模拟不同的外部负载ZL所相对应的输出功率结

ads优化仿真电路心得与放大器设计步骤

ADS应用: 1. ads优化仿真电路的一点心得: 我主要做的是高频的匹配电路所以在这里也谈谈自己的一些经验不足的地方希望大家指正1,初值的选择:首先拿到有源器件模型后我都会在圆图上看看它的s参数主要还是11和22 找个中心频率点通过ads自带的tools smith chat 将这点匹配到50om 这样我们就会得到一个匹配电路的初值。 通过这个方法很快的能找到一个比较好的初值比有些人随便给了一组数然后去random优化要快并且合理。 2,目标的设置:目标设置不好就会出现不收敛等一些预期不到的结果,所以我建议优化剃度到一定结果后见好就收然后手动改变变量进行调试。 选择它的优化type 里面就有),将影响目标灵 最后我觉的变量的设置一定要精简,在优化过程中有些数值影响小的一定要定值,不要一直开着优化,这样能避免不收敛的问题。 很浅的一些经验希望大家一起探讨。

放大器设计步骤解析 1.首先估计所设计放大器需要达到的增益,输入输出VSWR, 一般业界都将VSWR做到2.0以下,除非是功率放大器的输出VSWR,可以不考虑这个限制。 2.选择适当的晶体管,确定晶体管的工作状态,在当前设计 的偏压条件下,计算晶体管的S参数,MSG等,确定在设计的频段内,MSG略大于所要设计的放大器增益的值,一般设计的增益值会比MSG小2dB左右,以避免引起振荡,并方便做匹配。 3.将晶体管的稳定系数K值全部提升至1以上,而并不是只 要保证工作频段K值大于1,带外的频段受到干扰也可能引起振荡,但在工作频段K值最好只能略大于1,一般去 1.05,1.1左右,K值越大,设计的放大器最大增益将变 小,而在带外频段,K值尽量大,K值随频率曲线最好呈现一个U字型。 4.如果是设计驱动放大器,一般设计成输入输出都共轭匹 配,这里很多人在设计中常采用下面不太高效的做法:输出先接上50欧姆,再设计输入匹配网络,然后设计输出匹配网络,由于输出电路已不是50欧姆,需要再调整输入匹配网络,同样的,输入匹配网络变了以后,需要再一次调整输出匹配网络,来回需要调谐很多次,才有可能达到指标。其实输入输出匹配网络设计成共轭匹配时有一个

一种基于AgilentADS的功率放大器输出匹配新方法

第23卷第1期重庆工商大学学报(自然科学版)2006年2月Vol .23 No .1J Chongqing Technol Business Univ .(Nat Sci Ed )Feb .2006收稿日期:2005-09-10;修回日期:2005-12-12。 作者简介:汪小路(1981-),男,湖北宜昌人,硕士研究生,从事射频集成电路研究。 文章编号:1672-058X (2006)01-0064-05 一种基于Agilent ADS 的功率放大器 输出匹配新方法 汪小路1,赵为粮1,李红霞2 (1.重庆邮电学院光电工程学院,重庆400065;2.重庆大学软件学院信息安全系统工程研究所,重庆400044) 摘 要:详细阐述了LOAD_P ULL 的基本工作原理,并对LOAD _P ULL 的设置,在单载波情 况下的仿真,在双载波情况下的仿真等的实现方法及使用中的关键点进行了全面、仔细的分析,指出了利用LOAD_P ULL 技术实现的功率放大器具有输出匹配准确性程度较高,应用方便、高效快捷,开发时间短的优点,而且其兼容性强,可以结合其他设计方法一起使用。 关键词:LOAD_P ULL;功率放大器;输出匹配;等高线 中图分类号:T N 722 文献标识码:A 1 功率放大器的背景 功率放大器P A (Po wer Amplifier )是无线发射机的核心部件。在设计功率放大器的时候,有几个指标根据实际情况需着重考虑[1]:静态工作点的稳定性、增益(Gain )、输出功率(delivered Po wer )、功率附加效率P AE (Po wer Added Efficiency )、输入信号的电压驻波比(VS WR )、三阶交调截止点(Third O rder I ntercept Point )和带宽等。匹配电路设计应该同时满足上述指标。输出匹配电路设计又是设计阻抗匹配电路的重点[2]。 在设计功率放大器的匹配电路上,目前普遍采用传统的最佳负载曲线方法,在此方法中一般采用手算分析求得,这种方法的缺点是不直观,比较复杂,花费的时间也比较长;另一种方法就是新的LOAD _P ULL 匹配手段,运用ADS2003C (Agilent Design Syste m )提供LOAD_P ULL 模拟的方式,可以同时看到多种关键指标跟随输出负载变化而变化的情况,从而根据需求得到最佳输出负载,此种方法的优点是匹配准确性程度高、直观、方便快捷和大大缩短开发时间。 2 LOAD _P ULL 在单载波下的运用 电路基本设置如图1所示,该电路的静态工作点都是绝对稳定的,也是功率放大器设计的前提条件。从图1可以看到:电源提供的功率(P dc )是由加在栅极的,以及加在漏级的电压源提供: P dc =I s_h V s_h +I s_1V s_1(1) 其中I s_h ,V s_h 以及I s_1,V s_1分别是在场效应管的栅极和漏级上的静态工作电压和静态工作电流。

Load-Pull Measurement System量测规范

Load-Pull Measurement System量測規範 一、量測項目: (1)量測頻率範圍:0.8GHz ~18GHz(Power量測只能Single Band, 而S-Parameter量測才可以Broad Band) (2)量測功率範圍:Input Power range:- 40dBm ~25dBm Output Power range:- 50dBm ~30dBm (>25 dBm需外加Attenuator) (3)主要量測元件及電路:Power-Cell (Impedance ≧ 15Ω)、 Power Amplifier (4)量測參數:S-Parameter、IV Curve、Power Contour、Output Power 、Power Gain、P1dB、Power Efficiency 二、系統架構及儀器型號: (1)Network Analyzer:Agilent 8510 (2)Bias System:Agilent 4142B (3)Tuners:MAURY 982B01 (4)Tuner Control:MAURY 986B (5)Switch Control:MAURY 998C (6)Signal Analyzer:Agilent 8241C

(7)Power Meter:Anritsu 2438A (8)RF Probe Station & Microscope(CCD) (9)Control Software:MAURY MT993 三、量測接線方式: (1) PCB Measurement: a.採用3.5mm calibration kit作為校驗基準. b.PCB Board量測RF Port僅提供雙埠(東西向),設備端Port1、 Port2接頭均為3.5mm male,故待測物兩端均需為3.5mm female 或SMA female. PS:量測前請務必確認接頭形式,以免造成無法量測。 (2) On Wafer Measurement: a.採用ISS calibration kit作為校驗基準. b.CIC所提供之RF Probe為GSG、Pitch:150um(center to center) 形式,如下圖(一)所示;且RF PAD大小需≧80um x 80um, 如下圖(二)所示,不接受其他Pitch規格之申請(包含自 行攜帶探針),以避免系統需重新校準而浪費太多時間.

cadence中Loadpull问题

virtuoso 用portadapter拉负载有意义么? 首先是拉得不准的问题因为谐波阻抗没有考虑 第二是拉完之后想用匹配网络实现这个阻抗值但是cadence又没有ADS中的方便的设计匹配的能力 所以我想是不是直接把匹配网络放上去然后扫描元件参数看输出功率这样我觉得更直接一些啊而且在仿真时就已经包括进了对负载谐波阻抗的考虑。我现在完全是自己 瞎猜。请问大家什么看法。谢谢啦 1. 谐波阻抗的问题确实存在,所以确实有一定误差。不过如果你是class A或AB的话,应该影响不大。如果是开关功放,load pull的确意义不是那么大了。 2. 用实际电路可以,但是如何去做这样一个二维扫描呢,因为通常来说你至少要3个元件(T或者Pi型),这个你可以思考一下。load pull实际上就是个二维扫描,你光去扫描C 和L对你的意义不大,看不到smith chart上的各种contour。 非线性pa中的load pull没那么多有用,更不要说谐波的load pull,就算你扫描出来了,匹配电路也没法做。 你已经是非线性pa了,不需要做一个二维的load pull,把Cds估算出来,纳入匹配电路,做一维的电阻扫描就够了。(其实作为开关型的PA,Cds的非线性也是很大的) 除非你的功率真的很高,>30dBm甚至40dBm,否则load pull稍微偏一点给你带来的功率损失不会超过0.5dB,测试时别的地方带来的不理想造成的误差都比这个影响大。 virtuoso进行loadpull是遇到有portadapter的电阻r为负值 拉负载当输入功率大到一定程度时在所扫描的portadapter的反射系数的所有幅度值中都有portadapter的电阻r为负值这是为啥啊 portadapter内部由L,c,r组成,r和外接的port的z0串联,如果扫描的gamma的模<1,则r+z0>0,-17.8996+50>0,没有任何问题,warning只是提示性的。 关于Cadence下负载牵引的问题 用负载牵引法在Smith原图上仿出等功率圆,如果求最优负载啊,然后如何匹配啊。 资料上说X点就是,在最小圆的圆心,但是为什么我把50欧的电阻匹配到那点后,S21就成负的了啊, 输出功率也很小啊。请教高人解答。谢谢 以前搞过,貌似伏在牵引法搞出来的却是不是最优的。。。用ADS试试看

用ADS设计PA

EEsof,Cheng-cheng,Xie 用ADS设计功率放大器 EEsof Cheng-cheng, Xie Application Engineer

EEsof,Cheng-cheng,Xie 主要内容: ?PA 的主要指标?DC 分析?偏置电路的建立?稳定性分析 ?输入输出匹配电路设计?优化设计?Layout ?PI4DQPSK 调制下测试ACPR

PA的主要指标 ?工作频带 ?稳定性稳定系数K ?输出功率饱和功率(Psat) 1dB压缩点输出功率(P -1 )?增益、增益平坦度 ?效率功率效率 功率附加效率 ?线性度三阶交调系数IM3 五阶交调系数IM5 二次、三次谐波 ACPR AltCPR(Alternate CPR) ?输入输出驻波比直流输入功率 射频输入功率 射频输出功率? = add η EEsof,Cheng-cheng,Xie

EEsof,Cheng-cheng,Xie 指标实例 ?输出功率: 50 W (47dBm )?输入功率: 1 W ?效率(η) > 50%?二次谐波抑制:40dBC ?偏置电压: 28 V ?选用放大器: MRF9045M

EEsof,Cheng-cheng,Xie FET Curve Tracer FSL_TECH_INCLUDE FTI FSL_TECH_INCLUDE I_Probe IDS VAR VAR1VGS =0 V VDS =0 V Eqn Var V_DC SRC2Vdc=VGS DC DC1 Step=0.1 Stop=28*2Start=0SweepVar="VDS"DC DisplayTemplate disptemp1 "FET_curve_tracer" Temp Disp VJ FSL_MRF_MET_MODEL MRF1 MODEL=MRF9045M V_DC SRC1Vdc=VDS ParamSweep Sweep1 Step=0.1 Stop=5.0Start=2.5SimInstanceName[6]=SimInstanceName[5]=SimInstanceName[4]=SimInstanceName[3]=SimInstanceName[2]=SimInstanceName[1]="DC1"SweepVar="VGS" PARAMETER SWEEP 设置需要的Vg 、Vd 扫描范围

应用 PA Loadpull 数据建立 PA模型进行输出匹配和发射链路设计

应用PA Loadpull 数据建立PA模型进行输出匹配和发射链路设计 杨国华,李坚 索尼爱立信移动通信产品(中国)有限公司 摘要:本文介绍了一种通过Maury tuner实测PA Loadpull数据导入ADS建立PA模型的方法,并将通过Momentum以电磁场仿真方式提取的PCB模型与器件模型进行共仿真设计PA输出匹配网络和射频发射链路。最后对整个发射链路的部分射频性能进行仿真分析。 关键字:ADS, PA Load pull, Maury Tuner, Co-simulation, Tx Link, S parameters, PA modeling 一、引言 在进行PA输出匹配和发射链路设计时往往需要PA模型。由于涉及知识产权,很难从PA供应商拿到PA精确的Spice模型。但是PA Load Pull数据却相对容易从供应商获得或者自行通过Tuner进行测量。我们能否使用Load Pull测量数据建立PA模型并进行输出匹配和发射链路设计呢?答案是肯定的。现在使用ADS软件不但可以轻松高效地完成整个电路建模和设计,还能利用Momentum 将电路模型放置在PCB Layout上进行电路和电磁共仿真,在设计时就把PCB Layout对电路的影响计算在内。下面以一个具体的移动电话射频设计为例详细说明这一方法。 二、设计需求 射频发射链路的框图和连接关系如图1-1所示,根据下列条件设计PA最大增益输出匹配网络并对发射链路射频性能进行分析。设计中需将印刷电路板的影响一并考虑。 图1-1 工作频率:1850-1910MHz PA源阻抗:50 ohm PA最大增益:>=25dB 三、器件模型建立 3.1 PA模型建立 3.1.1 用PA的S参数建模和设计匹配电路面临的问题 对于双向()器件,带有负载L的PA输入端的信号流图,如图3-1所示。从PA输出端向PA源端的信号流图,如图3-2所示 图3-1 图3-2 根据信号流图,图3-1和图3-2,得到PA输入端和输出端反射系数表达式,见式3-1和式3-2 式 3-1 式3-2 根据式3-1和式3-2可知PA输入阻抗与PA负载阻抗有关系,PA输出阻抗与PA的源阻抗有关。在设计PA输入输出匹配时需联立两式求解。 3.1.2 使用PA Load Pull数据为PA建立模型 通过ADS使用PA Load Pull模型进行匹配设计时无需解此方程,Load Pull数据在测量时已将源阻抗对PA 增益和功率的影响计入测量结果。Load Pull数据可以很直观的以等高线形式绘制在史密斯图上,并可将匹配网络设计目标直观的表示出来。 使用Maury Tuner搭建Load Pull测试环境,进行系统校准后对PA进行测量。应用ADS自带的Load Pull Utility 按照图2-1所示操作将测量数据导入。在Step6中点击图2-1红圈内Generate Contours按钮,即可看到PA增益

关于谐波Load Pull技术的综述

116 June 2013 1527-3342/13/$31.00?2013IEEE Digital Object Identifier 10.1109/MMM.2013.2248631 Andrea Ferrero (andrea.ferrero@polito.it) and Marco Pirola are with the Electronic and Telecommunication Department, Politecnico di Torino, Turin, Italy. Date of publication: 7 May 2013 Harmonic Load-Pull Techniques T he characterization of microwave devices under nonlinear conditions is fundamental for device technology development, to improve device large signal model accuracy and reliability, as well as an essential tool to support the design of power amplifiers (PAs). Since the input and output device terminations at fundamental and harmonics frequencies play a crucial role to set the device behaviors and performances, load-pull (LP) measurements are today one of the promi-nent characterization solutions at RF, micro-, and millimeter waves. I n this article, a concise but comprehensive overview of the most important LP techniques available today is presented and pros and cons of the several approaches are high-lighted and discussed. Introduction The term LP refers to the evaluation of a figure of merit (FOM) of a device under test (DUT), e.g., a GaN pseudomorphic HEMT rather than a com-plete power module, when the input and/or out-put loading conditions are changed. From the analysis of the measurement data, the loads able to provide the desired FOM can be identified straightforwardly and then synthesized in the design phase. LP measurements have become a de facto high-frequency characterization standard for several microwave and RF applications. They not only support PA designers but also provide feed-back for process amelioration and useful insights to nonlinear model developers for model improve-ments and refinements. For example, the design of PA matching networks can be accomplished in a Andrea Ferrero and Marco Pirola

WCDMA之PA Load-pull 收敛调校

由于Duplexer的封装结构特性,会使其成电容性,因此在WCDMA的电路中,常看到Duplexer输出端,会摆放一颗落地电感,来抵消其封装所造成的电容性,以加强其S11的收敛度,亦即Duplexer的输出端,看出去需为一个电感性负载。 但若未摆放该落地电感,或其落地电感离Duplexer输出端太远,则会因为走线与GND间的寄生效应,导致Duplexer的输出端,看出去为一个电容性负载,这会使其S11的收敛度变差,因此需特别注意[1-3]。

当然原则上,PA输出调试要根据厂家给的Load-pull,去作ACLR,输出功率,耗电流的取舍,但一般方便起见,多半都会调在50奥姆,因为50奥姆在各方面的性能,虽不是最好,但也不至于差到哪去,除非要特别针对某个特性去做优化[4, 6]。 而除非PA输出端有加Isolator,否则从输出端,一路到RF Switch,都算是Load-pull的一部分,因此以[5]的做法,会先量测PA输出端,一直到RF Switch 的Load-pull。 若发现Load-pull不收敛,则会先调校PA输出端的Matching,再调校Duplexer 输出端的Matching。

但因为Duplexer输出端的Matching,同时也会影响接收端的灵敏度,若之前已先调校好接收端的Matching,此时又去动到Duplexer输出端的Matching,则有可能使接收端的灵敏度变差,必须再作微调,以得到最佳灵敏度。但这么一来,Load-pull又有所变动,如此这样反复调适,有可能会没完没了,因此比较快的做法是反过来,亦即先做Duplexer输出端Matching,确保其S11跟S22,都收敛在50奥姆附近,之后不论要调校发射端或接收端的Matching,这段都不要再更动[6]。 最后再来调适PA的输出Matching,确保从PA输出到Connector,都在50奥姆附近。