赛灵思静态随机存储器型FPGA单粒子翻转检测_航天恒星_吕达

V ol .19 N o .6 96 航 天 器 工 程SPA CECRAF T EN GIN EERIN G

第19卷 第6期

2010年11月

赛灵思静态随机存储器型FPGA 单粒子翻转检测

吕 达 吴 飞 陆 华

(航天恒星科技有限公司,北京 100086)

摘 要 以XILINX XC2V3000现场可编程门阵列(FPGA )为例,分别通过ICAP 和Select -m ap 接口对配置存储器进行回读检测,并通过局部动态重构的方法实现了故障注入,对单粒翻转(SEU )检测方法进行验证。结果证明回读与重配置是进行FPGA 抗SEU 设计的有效方法。

关键词 现场可编程门阵列;单粒子翻转;配置存储器;检测

中图分类号:TN98 文献标志码:A 文章编号:1673-8748(2010)06-0096-06

Detecting Single -event Upsets for XILINX SRAM -Based FPG A

LU Da WU Fei LU H ua

(Space S tar Technolog y Co .Ltd .,Beijing 100086,China )

A bstract :The config uration memo ry of XC2V3000is readback thro ug h ICAP and Selectmap ,and the config ura tion data are verified .The sim ulation of S EU is im plemented by reconfig urating o ne

frame of co nfiguratio n memo ry w ith different data .The results show that readback and reconfi -guratio n of the S RAM based FPGA is an effective w ay to mitigate SEU .Key words :FPGA ;SE U ;config uration memo ry ;detectio n

收稿日期:2010-06-10;修回日期:2010-06-30作者简介:吕达(1980-),男,硕士,主要从事FP GA 的信号处理方面的研究。

1 引言

太空环境下,赛灵思(XILINX )静态随机存储器(S RAM )型的现场可编程门阵列(FPGA )容易受到单粒子翻转(SEU )的影响。FPGA 片内所有S RAM 都可能受到SEU 的影响,包括配置存储单元、用户逻辑单元、配置逻辑寄存器。配置存储单元的内容决定着FPGA 的功能,配置存储单元发生翻转会导致FPGA 功能持续改变,直至下次重新配置完成。用户逻辑单元包括块RAM (BRAM )以及可编程逻辑单元(CLB )、可编程IO 单元(IOB )中的触发器,这些存储单元的值在FPGA 运行过程中实时刷新,所以SE U 影响不大。配置控制逻辑寄存器发生翻转属于单粒子功能中断(SEFI )的内容,会导致FPGA 配置功能失效,但配置控制寄存器发生错误

概率极低。据NASA 测试数据显示,每70年才可

能发生一次[1]

。故配置存储单元SEU 是FPGA 抗

SEU 设计中最重要的内容。

目前抗SEU 的措施包括通过一定厚度的材料进行辐射屏蔽、冗余设计、擦洗(Scrubbing )以及系统监控与重配置等。

冗余的方法包括采用多个完成相同功能的器件进行备份以及在同一器件中三模冗余容错技术

(TM R )[2]

,冗余设计的假设前提是:任何两个存储单元的同一位不会在同一时间发生SEU 效应[3]

。采用多个完成相同功能的器件备份可以提高可靠性,但会造成体积和功耗的增加;三模冗余设计可以

带来可靠性的提高[4-5]

,但会使模块的速度降低、占用资源和功耗增加。

擦洗的方法是指周期性的刷新存储单元中的内容,可以减少受到SEU 而发生翻转的概率,这种方

法的优点是无需额外的硬件逻辑资源,实现简单,其缺点是无法对擦洗数据进行校验,不能判断是否发生过SEU ,而且只能恢复暂态故障[6]

。同时,如果擦洗的时间间隔越大,可靠性就会降低[7]。

对配置存储器进行回读和重配置是一种有效的抵抗SEU 的方法,在FPGA 实时运行过程中,回读配置存储器,并对读出的数据进行校验,如果发现错误则重新配置。目前NASA [8]、日本的智能卫星

(SmartSat )[9]

工作组都进行了基于这种结构的卫星

信号处理平台的研究,国内国防科技大学[10]

、航天恒星科技有限公司等单位也进行了这方面的研究,并取得了一定的进展。

本文以XILINX Virtex -II FPGA XC2V3000为例,分别通过内部访问接口(ICA P )和外部并行访问接口(SelectMap ),回读配置数据并校验,实现了S EU 检测。另外,通过局部动态重构的方法,在地面环境实现了故障注入。

2 原理与方案

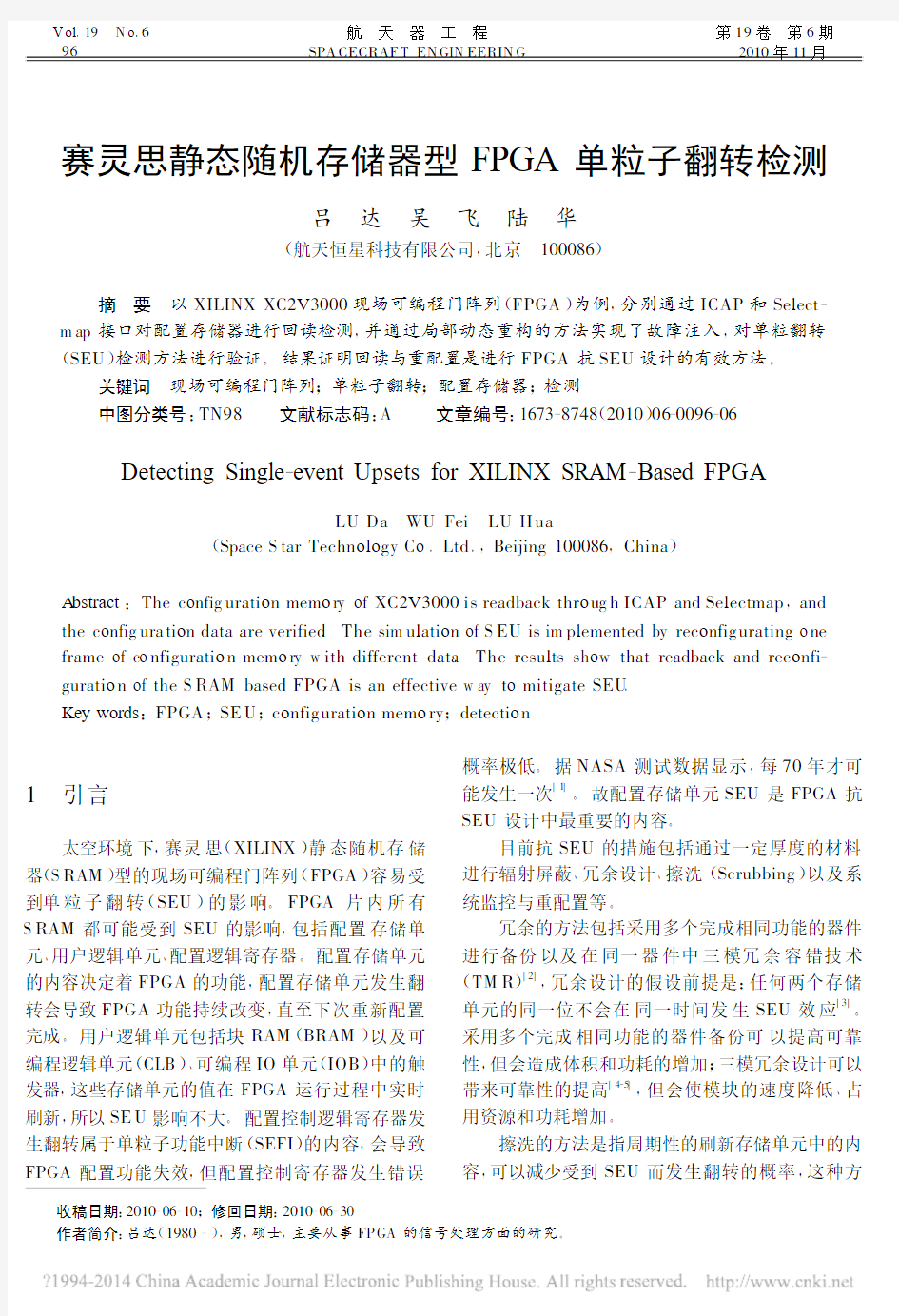

FPGA 抗SEU 设计框图如图1所示,包括如下4个模块

。

图1 F PG A 抗SEU 设计方案Fig .1 S tructure o f SEU mitig atio n

1)目标模块:指被检测以及故障注入的实体。它们具备检测以及故障注入的接口。

2)监控模块:对被检测目标进行监控,对情况进行判断;在出现故障之后报告故障处理模块。3)故障处理模块:检测出目标系统故障后,根据故障类型,进行相应的处理。可以是给出报错信息,也可能对错误予以纠正,也可能是既报错又给予纠正。

4)故障注入模块:在验证检测算法时使用,包括故障注入器和故障集。

故障注入器指对目标系统实施故障注入的实体。它根据故障注入模型条件,在故障注入时机到

来的情况下,对目标系统进行故障注入。

故障集由实际发生在系统中的故障组成。故障集是通过对故障模型进行分析得到的集合。对于单粒子故障集来说,故障集包括了SEU 、SEFI 、单粒子

锁定(SEL )等,其中SEU 故障集包括CLB 故障、IOB 故障、全局时钟(GCLK )故障以及BRAM In -terconnect 故障等。

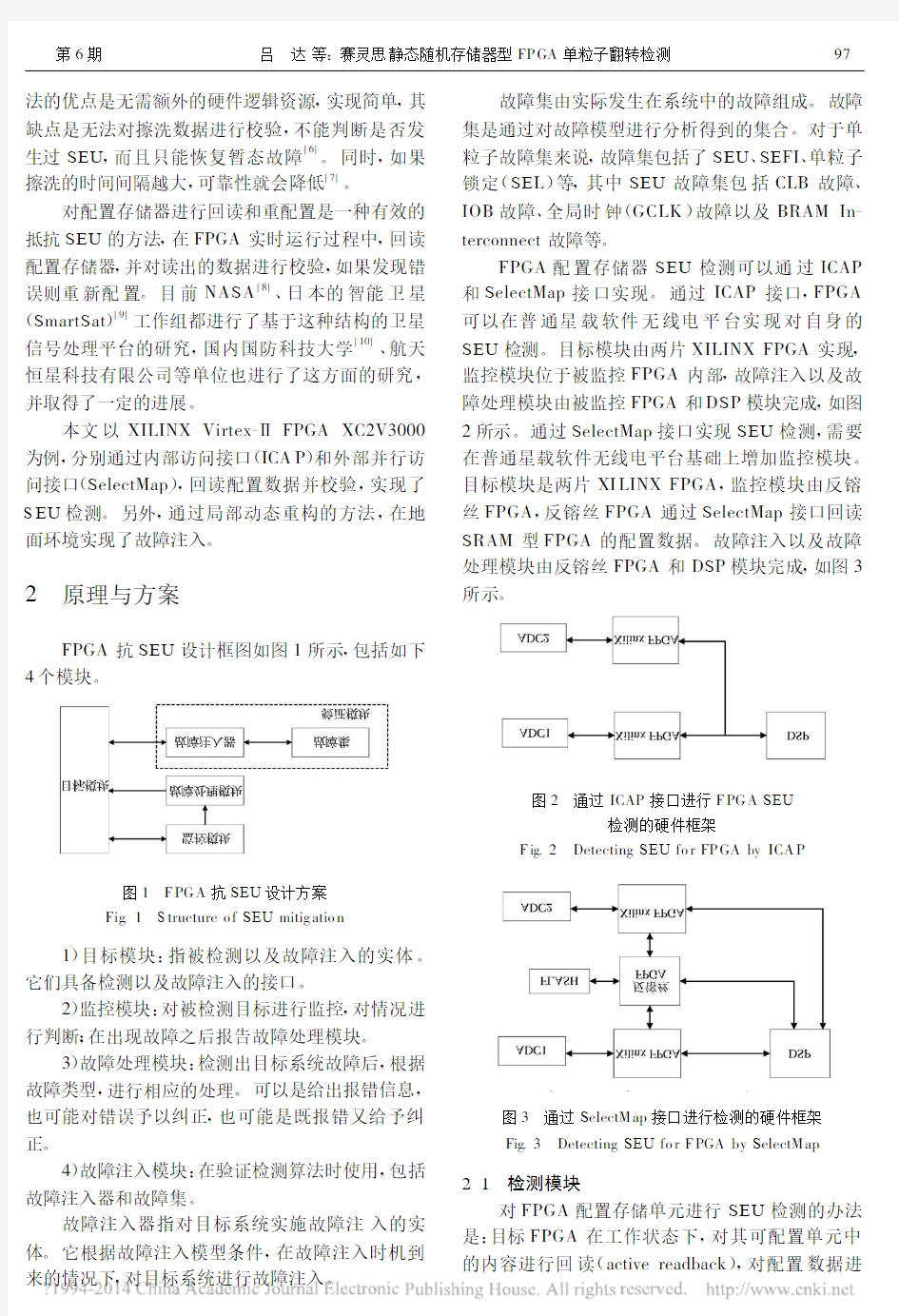

FPGA 配置存储器SEU 检测可以通过ICAP 和SelectMap 接口实现。通过ICAP 接口,FPGA 可以在普通星载软件无线电平台实现对自身的SEU 检测。目标模块由两片XILINX FPGA 实现,监控模块位于被监控FPGA 内部,故障注入以及故障处理模块由被监控FPGA 和DSP 模块完成,如图2所示。通过SelectMap 接口实现SEU 检测,需要在普通星载软件无线电平台基础上增加监控模块。目标模块是两片XI LINX FPGA ,监控模块由反镕丝FPGA ,反镕丝FPGA 通过SelectMap 接口回读SRAM 型FPGA 的配置数据。故障注入以及故障处理模块由反镕丝FPGA 和DSP 模块完成,如图3所示。

图2 通过ICAP 接口进行F PG A SEU

检测的硬件框架

F ig .2 Detecting SEU fo r FP GA by ICA P

图3 通过SelectM ap 接口进行检测的硬件框架Fig .3 Detecting SEU fo r F PGA by SelectM ap

2.1 检测模块

对FPGA 配置存储单元进行SEU 检测的办法是:目标FPGA 在工作状态下,对其可配置单元中的内容进行回读(active readback ),对配置数据进

97

第6期 吕 达等:赛灵思静态随机存储器型FP GA 单粒子翻转检测

行校验。为了避免破坏BRAM中的内容,只针对其他内容进行回读校验。

2.1.1 回读接口选择

Virtex II FPGA配置访问接口包括JTAG、Se-lectM ap,以及ICAP三种,其中ICAP是内部访问接口,监控模块在目标FPGA内部完成,通过ICAP 接口访问配置存储器,可以实现对目标FPGA自身的检测,电路结构最为简单,不需要另加监控模块,但监控模块自身也有发生SEU的可能,如图2所示。JTAG和Selectmap都是外部访问接口,外部设备通过这两个接口可以实现对目标FPGA进行回读,但Selectmap是并行接口,回读速度快,访问方便,如图3所示。本设计分别选择了ICAP接口和SelectM ap接口进行回读检测。

2.1.2 检测周期确定

根据NASA和XILINX一起对XILINX Vir-tex II器件(XC2V1000)进行辐照测试获得的参数,见表1[11]。以XC2V1000配置存储器的3M bit为例,根据该数据可知,平均每天就会发生1.3bit的位翻转错误,发生SEU的最长时间为18h, XC2V3000的配置存储器大约为9M bit,估算得发生SE U的最长时间约为6h。SEU检测速率至少是故障概率的10倍,所以最长检测时间为0.6h。

如果回读检测模块工作时钟为10M H z,通过SelectM ap接口,对XC2V3000配置存储器进行回读检测,完成1次检测大约需要的时间是110ms,因此最短周期就是110m s。

根据以上考虑,文章选定1s对配置存储器进行1次回读检测。

表1 Virtex II FPGA翻转概率

Table1 Virtex II cross section parameters

and upset rates

L1/e (MeV·c m2/mg)

σsat

(cm2/bit)

Upsets

Rates

C on figu ration

mem ory 8.55.5×10-8

4.4×10-7/

bit-day

Block SelectRAM 55×10-8

1.1×10-6/

bit-day

Flip-Flops51×10-62.1×10-5/ device-day

POR SEFI 76×10-6

7.0×10-5/

device-day

SelectM ap

SEFI 75×10-6

5.8×10-5/

device-day

2.1.3 检测内容确定

S EU检测的做法通常是对配置存储器的所有内容进行回读检测,但并不是所有回读数据都需要校验,如BRAM中的内容。XILINX提供了m ask 文件,表明了不需要校验的内容。但如果校验的时候使用mask文件,需要占用存储空间,XC2V300器件m ask文件大约9.2M bit,对星载电子设备来说是一个很大的空间。文章将m ask文件嵌入到配置以及回读中去,回读数据可以直接和原始bit文件进行校验或者进行C RC校验,节省了存储空间。2.2 故障注入模块

故障注入是模拟FPGA、SEU,以及单粒子功能中断等单粒子效应的一种有效方法。对FPGA 进行S EU模拟可以采用重离子辐射的方法,NASA 的喷气推进实验室(JPL)和单粒子效应(SEE)协会对大规模集成电路的单粒子效应进行了很多模拟试验,利用各种模拟源(粒子加速器提供的各种重离子和质子、脉冲激光等)对FPGA进行辐照,使FPGA 配置单元发生随机错误。在算法调试阶段,采用照射的方法会花费高额费用,另外也不利于实施。

利用Virtex II系列FPGA可局部动态重构的特点。局部动态重构技术指对于特定的基于SRAM结构的FPGA,在一定的控制逻辑的驱动下,对芯片的部分逻辑资源实现在系统的高速的功能变换。局部动态重构是指对重构器件或系统的一部分进行重新配置,而在此过程中,其余部分的工作状态不受影响。

XILINX Virtex II FPGA最小访问单元为1帧,因此对FPGA配置存储器每帧进行动态重构即可完成单粒子模拟。这种研究方法可以在很大程度上仿真地面单粒子模拟试验,缩短试验周期,提高试验的灵活性。基于FPGA配置文件的保密性要求,以及XILINX FPGA结构本身的保密性,XILINX 对配置文件中每一帧具体的逻辑资源以及如何组织这部分信息是不公布的。每一帧配置数据不但包含对逻辑资源的配置,即某些位不允许故障注入,可以参考mask文件对允许比较的位进行故障注入。

故障注入模块由三部分组成:故障模式寄存器、控制寄存器、故障发生器。故障模式寄存器和控制寄存器可以由处理器通过特权指令访问,可以很方便地设置故障模式,制造所期望的故障模式,并控制故障的注入。故障模式寄存器可以对FPGA的不同部位设置所期望的故障模式。如欲使CLB部分的第i帧第j位发生翻转,只要设置故障模式寄存器相应的数据位即可。控制寄存器可以控制故障的插入,再非调试模式下可以禁止故障的插入,保证被

98 航 天 器 工 程 19卷

监控FPGA 正常运行。在调试模式下,允许故障的插入,数据在经过故障注入器后,产生类似于SEU 效应的错误数据,写入到配置存储器,达到故障注入的目的。2.3 软件流程图

S EU 检测试验的软件流程如图4所示:秒脉冲下降沿到来时,检测故障注入标志,如果故障注入标志为1,则进行故障注入,即对配置存储器的一帧进行改写,否则对配置存储器进行检测

。

图4 S EU 检测试验软件流程图Fig .4 SEU detection alg o rithm flo w char t

3 试验结果及分析

3.1 SEU 检测试验

3.1.1 通过ICA P 实现SEU 检测

FPGA 对自身配置存储器进行检测结果如下:

被监控FPGA 实现点灯功能,未进行故障注入的时

候,回读数据的CRC 值保持恒定,如图5所示,CRC 值始终是0x A2E2,检测结果com pareout 信号也始终为低电平。

对配置存储器进行故障注入,配置存储器的Block Interco nnect 列的第一帧的第一个字节进行改写,将最初的一个字节0×00改为了0×07。故障注入后重新检测,回读数据的CRC 值变为F00F ,检测结果信号com pareout 也变为高电平,表明检测到SEU 翻转,如图6所示。

图5 未故障注入时候CRC 值始终不变Fig .5 CRC data ar e fixed w hen no SEU ha ppens

图6 故障注入后CRC 发生变化

Fig .6 CRC data a re changed when SEU happe ns

3.1.2 通过SelectM ap 接口实现SEU 检测目标FPGA 实现点灯功能。故障注入前始终未检测到SEU 。故障注入是通过对GCLK 前两帧数据进行改写实现的。对配置存储器前两帧数据第一个字节分别写入0×0C ,原来都是0×00;其余部分写入0×00。故障注入后小灯停止闪烁,开启回读检测模块,检测到SEU ,如图7所示。

图7 故障注入后后检测到单粒子翻转F ig .7 S EU is detected after bug is inse rted

图7中,从上至下第8个信号com pare o 表示

99

第6期 吕 达等:赛灵思静态随机存储器型FP GA 单粒子翻转检测

回读的配置数据与原始数据的比较结果,readnum 表示回读比特计数。由图中看出当readnum=666时,compare o为高电平,表示检测到了SEU。

3.2 资源使用情况

3.2.1 通过ICA P实现SEU检测

FPGA中实现的功能是通过ICAP对自身配置存储器进行回读,并对读出的数据进行CRC校验,所使用的资源如表2所示。

由表2可见,本文的FPGA抗SEU设计占用资源少。本设计在星载GPS接收机FPGA模块中进行了试验,FPGA设计在增加抗SEU的功能的同时,不会造成资源的显著增加。

表2 FPGA通过IC AP对自身配置存储器

SEU检测资源使用情况

Table2 Resource using condition when detecting

SEU in FPGA configuration memory through ICAP by itself

实际使用总数使用率/%触发器116286721

查找表221286721

用户IO44841

块状RAM1961

全局时钟1166

ICAP111

S lice160143361

3.2.2 通过SelectM ap接口SE U检测

本设计中选用Virtex II x c2v1500代替反镕丝器件,对S RAM型FPGA进行检测。监控FPGA 内部实现监控模块、判决等功能,使用资源见表3。可见,通过SelectM ap接口实现SEU检测占用资源很少。

表3 通过SelectMap回读检测SEU资源占用情况

Table3 Resource using condition when detecting SEU in FPGA conf iguration memory thro ugh Seletcmap

实际使用总数使用率/%触发器257153601

查找表417153602

用户IO20352838

块状RAM1482

全局时钟51631

DCM1812

S lice30376803

4 结论及展望

文章分析了S RAM型FPGA SEU的特点,以及FPGA抗SEU方法,并通过对配置数据进行回读校验的方法实现了SEU检测。

FPGA通过ICA P可以实现自身SE U检测,但由于检测模块运行于FPGA内部,也可能发生SEU,可以通过对检测模块进行三模冗余设计提高可靠性,另外可以采用片外反镕丝器件通过Select-M ap接口对FPGA配置存储器进行回读,实施SEU检测是更加可靠的办法。

参考文献(Refe rences)

[1]Ro osta R.A Co mpa riso n o f radiatio n-har d and radia-

tio n-tolerant F PG A s for space applicatio ns[R].N AS A,

D EC,2004

[2]Carmichael C.T riple module redundancy desig n tech-

niques fo r V ir tex series F PG A[EB/O L].(2006-07-

06).[2009-07-30]http://w ww.X ILI https://www.360docs.net/doc/3e3626628.html,/hv doe s/

apnotes/x app197.pdf

[3]贺朝会,陈晓华,李国政.高能质子单粒子翻转效应的模

拟计算[J].计算物理,2002,19(4):367-371

[4]Samudrala P K,Ramos J,K atko ori S.Selective triple

mo dula r redundancy(ST M R)ba sed sing le-event upset

(S EU)tolerant synthesis fo r F PG A s[J].IEEE T r ans-

actio ns on N uclear Science,2004,51(5)

[5]Fuller E,Caffrey M,Salazar A,et al.Radiatio n testing

update,SE U mitiga tion,and availability analy sis of the

V irtex F PG A for space reconfig urable com puting[C]//

4th Annual Co nfer ence on M ilitary and A er ospace P ro-

g rammable L ogic Devices(M A P LD).Wa shing ton DC:

N A SA O ffice of Log ic Desig n,September2000

[6]Carmichael C,Fuller E,Blain E A.SEU mitigation

techniques fo r Virtex F PG As in space applica tions

[C]//P roceeding of the M ilitary and A ero space P ro-

g rammable Log ic Device s and Technolo gy Conference,

1999

[7]Shubhe ndu S M,Emer J,F ossum T,et al.Cache

scrubbing in micro pr ocesso rs:my tho r necessity[C]//

P RDC'04:10th I EEE P acific Rim Inte rnational Sympo-

sium on Depe ndable Co mputing.T ahiti,F rench P oly-

ne sia,2004

[8]Rober t F,H odso n1,Some rvill K,et al.A n architec-

ture for reco nfigur able computing in space[C]//M ilitar-

y and Ae ro space Applica tions of P rog rammable Devices

and T echnolog ies Co nfer ence(M A P LD),Wa shing ton

DC:NA SA Office o f Lo gic De sign,Sepetmber2005 [9]N ishinaga N,T akeuchi M,Suzuki R.Reconfigur able

communicatio n equipment on sma rtSat-1[C].M ilitary

and A ero space A pplicatio ns of Pr og rammable Devices

and T echno lo gie s Co nference(M A P LD),Wa shing ton

100 航 天 器 工 程 19卷

DC :N A SA O ffice of Log ic Desig n ,Se ptember 2004[10]邢克飞,杨俊,王跃科,等.XI LIN X SRA M 型F PG A 抗

辐射技术研究[J ].宇航学报,2007,28(1)

[11]Y ui C ,Sw if t G ,Car michael C .Single eve nt upset sus -ceptibility testing of the XIL INX Virtex II F PGA [C ]//M ilitar y and A ero space A pplicatio ns of P ro -g rammable

Devices

and T echno lo gies Co nference

(M A P LD ).W ashing to n DC :N AS A O ffice o f L ogic Design ,Septembe r 2002

(编辑:朱丽)

科技成果

科通公司为美国军事卫星升级通信终端

据科通公司网站报道,科通电信公司(Com tech )2010年10月13日宣布,其位于美国加利福尼亚州的子公司Com tech EF 数据公司获得了一份价值320万美元的订单,向美国政府提供卫星通信设备。这些设备将被用来升级已部署的卫星终端,支持战术军事通信。提供的设备包括MB T -5003上/下变频器系统和S LM -5650A 卫星调制解调器

。

SLM -5650A 卫星调制解调器

MBT -5003上/下变频器系统提供L 频段中频和C /X /Ku 频段射频之间的频率转换。它封装在一个3RU 平台,采用单一机箱、冗余解决方案,提供高输出功率。该系统是专为坚固fly -aw ay 终端使用。

S LM -5650A 卫星调制解调器符合M IL -S TD -188-165A 的严格标准,调制解调器类型分为Ⅰ、Ⅱ、Ⅳ、Ⅴ和Ⅵ类,用于国防卫星通信系统(DSCS )卫星、宽带全球卫星通信(WGS )卫星和商业卫星。调制解调器具备先进的功能支持,较高的带宽效率和灵活性,包括传输安全(T RANSEC )和网络处理器模块。这种多用途产品可支持各种应用,最大限度地减少战术终端设置的后勤支持和培训。

欧洲借助航天技术开发新型牙科X 光仪器

据新华网报道,欧洲航天局10月11日宣布,欧洲企业借助太空微型器械制造技术,开发出了一种高分辨率、高对比度的小型牙科X 光仪器。

据欧洲航天局介绍,瑞典纳米太空公司将其生产航天产品的技术和经验进行转化,研制出了这种新型X 光仪器,其核心器件名为“闪烁器”,可以将X 光转化为可见光,得到的图像无论是分辨率还是对比度都远远高于目前牙科临床使用的X 光机。由于融入了太空微型器械制造技术,新的X 光仪器要比目前使用的牙科X 光机薄许多。这样牙医就能轻松地将仪器置于患者口中,为牙齿拍摄X 光片。

欧洲航天局表示,上述成果再次表明,航天领域的技术转化实际上大有可为。

101

第6期 吕 达等:赛灵思静态随机存储器型FP GA 单粒子翻转检测

静态存储器-实验报告

计算机科学与技术系 实验报告 专业名称计算机科学与技术 课程名称计算机组成与结构 项目名称静态随机存储器实验 班级 学号 姓名 同组人员无 实验日期 2015-10-24

一、实验目的与要求 掌握静态随机存储器RAM 工作特性及数据的读写方法 二、实验逻辑原理图与分析 2.1 实验逻辑原理图及分析 实验所用的静态存储器由一片6116(2K ×8bit)构成(位于MEM 单元),如下 图所示。6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS 常接地线。 由于存储器(MEM)最终是要挂接到CPU 上,所以其还需要一个读写控制逻辑,使得CPU 能控制MEM 的读写,实验中的读写控制逻辑如下图所示,由于T3的参与,可以保证MEM 的写脉宽与T3一致,T3由时序单元的TS3给出。IOM 用来选择是对I/O 还是对MEM 进行读写操作,RD=1时为读,WR=1时为写。 XMRD XIOR XIOW XMWR RD IOM WE T3 读写控制逻辑 实验原理图如下如所示,存储器数据线接至数据总线,数据总线上接有8 个LED 灯显示D7…D0的内容。地址线接至地址总线,地址总线上接有8个LED 灯显示A7…A0的内容,地址由地址锁存器(74LS273,位于PC&AR 单元)给出。数据开关(位于IN 单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。

实验四 静态随机存储器实验

实验四静态随机存储器实验 一.实验目的 掌握静态随机存储器RAM工作特性及数据的读写方法。 二.实验设备 TDN—CM++计算机组成原理教学实验系统一台,排线若干。 三.实验内容 1.实验原理 实验所用的半导体静态存储器电路原理如图所示,实验中的静态存储器一片6116 (2K﹡8)构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。 地址灯AD0—AD7与地址线相连,显示地址线内容。数据开关经一三态门(74LS245)连至数据总线,分时给出地址和数据。 因地址寄存器为8位,接入6116的地址A7—A0,而高三位A8—A10接地,所以 其实际容量为256字节。6116有三个控制线:CE(片选线)OE(读线)WE(写 线)。当片选有效(CE=0)时,OE=0时进行读操作,WE=0时进行写操作。本实 验中将OE常接地,在此情况下,当CE=0 WE=0时进行读操作,其写时间与T3 脉冲宽度一致。 实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可调,其它电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中SW—B为 低电平有效,LDAR为高电平有效。 2.实验步骤 (1)在时序电路模块中有两个二进制开关“STOP”和“STEP”,将“STOP” 开关置为“RUN”状态,将“STEP”开关置为“STEP”状态。 (2)按“图4 存储器实验连线图”连接实验线路,仔细查向无误后接通电源。 由于存储器模块内部的连线已经接好,因此只需完成电路的形成、控制信 号模拟开关、时钟脉冲信号T3与存储模块的外部连接。 (3)给存储器的00 01 02 03 04地址单元中分别写入数据11 12 13 14 15,具体操作步骤如下:(以向00号单元写入11为例)

计算机组成原理实验静态随机存储器

实验二SRAM 静态随机存储器实验 存储器是计算机各种信息存储与交换的中心。在程序执行过程中,所要执行的指令是从存储器中获取,运算器所需要的操作数是通过程序中的访问存储器指令从存储器中得到,运算结果在程序执行完之前又必须全部写到存储器中,各种输入输出设备也直接与存储器交换数据。把程序和数据存储在存储器中,是冯·诺依曼型计算机的基本特征,也是计算机能够自动、连续快速工作的基础。 一、实验目的 掌握静态随机存储器RAM工作特性及数据的读写方法。 二、实验设备 PC机一台,TD-CMA实验系统一套。 三、实验原理 实验所用的静态存储器由一片6116(2K×8bit)构成(位于MEM单元),如图2-1所示。6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如表2-1所示,当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS常接地。 图2-1 SRAM 6116引脚图 由于存储器(MEM)最终是要挂接到CPU上,所以其还需要一个读写控制逻辑,使得CPU能控制MEM 的读写,实验中的读写控制逻辑如图2-2所示,由于T3的参与,可以保证MEM的写脉宽与T3一致,T3由时序单元的TS3给出。IOM用来选择是对I/O还是对MEM进行读写操作,RD=1时为读,WR=1时为写。 表2-1 SRAM 6116功能表 CS WE OE功能 1 0 0 0× 1 × 1 不选择 读 写 写

XMRD XMWR XIOW XIOR RD T3WR 图2-2 读写控制逻辑 实验原理图如图2-3所示,存储器数据线接至数据总线,数据总线上接有8个LED 灯显示D7…D0的内容。地址线接至地址总线,地址总线上接有8个LED 灯显示A7…A0的内容,地址由地址锁存器(74LS273,位于PC&AR 单元)给出。数据开关(位于IN 单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。 RD WR 图2-3 存储器实验原理图 实验箱中所有单元的时序都连接至时序与操作台单元,CLR 都连接至CON 单元的CLR 按钮。实验时T3由时序单元给出,其余信号由CON 单元的二进制开关模拟给出,其中IOM 应为低(即MEM 操作),RD 、WR 高有效,MR 和MW 低有效,LDAR 高有效。

微控制器实验报告

微控制器技术实验报告 班级: 姓名: 学号:

微控制器技术实验说明 一、实验目的及要求: 1、学习Keil C51集成开发工具的操作及调试程序的方法,包括:仿真调试 与脱机运行间的切换方法; 2、熟悉TD-51单片机系统板及实验系统的结构及使用; 3、进行MCS51单片机指令系统软件编程设计与硬件接口功能设计; 4、学习并掌握Keil C51与Proteus仿真软件联机进行单片机接口电路的设 计与编程调试; 5、完成指定MCS51单片机综合设计题 二、实验基本内容(TD-51单片机实验系统实现) 实验一清零程序与拆字程序设计 根据实验指导书之“第二章单片机原理实验”(P17~P23页)内容,熟悉实验环境及方法,完成思考题1、2(P23)基础实验项目。 实验二拼字程序与数据传送程序设计 汇编语言完成实验指导书P24思考题3、4题的基础实验项目。 实验三排序程序与散转程序设计 汇编语言完成实验指导书P24思考题5、6题的基础实验项目。 实验四静态存储器扩展实验 基本部分:阅读、验证C语言程序功能。使用汇编语言编程,完成实验指导书之“4.1 静态存储器扩展实验”基本实验项目(P57)。 提高部分:阅读、验证C语言程序功能。使用汇编语言编程,完成实验指导书之“4.2 FLASH存储器扩展实验”实验项目(P60)。 实验五数字量输入输出实验 基本部分:阅读、验证C语言程序功能。使用汇编语言编程,完成实验指导书之“3.1 数字量输入输出实验”基本实验项目(P36),。 提高部分:(任选一题) 题目一:LED交通灯控制(使用8255接口芯片) 要求:使用汇编语言编程,功能为:通过开关实现LED灯工作方式即时控 制,完成LED交通灯的开关控制显示功能和LED交通灯自动循环显示功能。 题目二:LED灯控制(使用8255接口芯片) 要求:使用汇编语言编程,功能为:通过KK1实现LED灯工作方式即时控 制,完成LED开关控制显示和LED灯左循环、右循环、间隔闪烁功能。 题目三:键盘扫描与数码管显示设计( 要求:阅读、验证P69上的C 语言参考程序功能。使用汇编语言完成编程与功能调试。

计算机组成原理上机实验报告

《计算机组成原理实验》课程实验报告 实验题目组成原理上机实验 班级1237-小 姓名 学号 时间2014年5月 成绩

实验一基本运算器实验 1.实验目的 (1)了解运算器的组成原理 (2)掌握运算器的工作原理 2.实验内容 输入数据,根据运算器逻辑功能表1-1进行逻辑、移位、算术运算,将运算结果填入表1-2。 表 1-1运算器逻辑功能表 运算类 A B S3 S2 S1 S0 CN 结果 逻辑运算65 A7 0 0 0 0 X F=( 65 ) FC=( ) FZ=( ) 65 A7 0 0 0 1 X F=( A7 ) FC=( ) FZ=( ) 0 0 1 0 X F=( ) FC=( ) FZ=( ) 0 0 1 1 X F=( ) FC=( ) FZ=( ) 0 1 0 0 X F=( ) FC=( ) FZ=( ) 移位运算0 1 0 1 X F=( ) FC=( ) FZ=( ) 0 1 1 0 0 F=( ) FC=( ) FZ=( ) 1 F=( ) FC=( ) FZ=( ) 0 1 1 1 0 F=( ) FC=( ) FZ=( ) 1 F=( ) FC=( ) FZ=( ) 算术运算 1 0 0 0 X F=( ) FC=( ) FZ=( ) 1 0 0 1 X F=( ) FC=( ) FZ=( ) 1 0 1 0X F=( ) FC=( ) FZ=( ) 1 0 1 0X F=( ) FC=( ) FZ=( ) 1 0 1 1 X F=( ) FC=( ) FZ=( ) 1 1 0 0 X F=( ) FC=( ) FZ=( ) 1 1 0 1 X F=( ) FC=( ) FZ=( ) 表1-2运算结果表

静态随机存储器实验

实 验 项 目 静态随机存储器实验实验时间2015-11-14 实 验 目 的 掌握静态随机存储器RAM 工作特性及数据的读写方法。 实 验 设 备 PC机一台,TD-CMA实验系统一套 实验原理 实验所用的静态存储器由一片6116(2K×8bit)构成(位于MEM 单元),如图2-1-1 SRAM 6116引脚图所示。6116 有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如表2-1-1 所示,当片选有效(CS=0)时,OE=0 时进行读操作,WE=0 时进行写操作,本实验将CS 常接地。 图2-1-1 SRAM 6116引脚图 由于存储器(MEM)最终是要挂接到CPU上,所以其还需要一个读写控制逻辑,使得CPU 能控制MEM的读写,实验中的读写控制逻辑如图2-1-2所示,由于T3的参与,可以保证MEM的写脉宽与T3一致,T3由时序单元的TS3给出(时序单元的介绍见附录2)。IOM用来选择是对I/O 还是对MEM进行读写操作,RD=1时为读,WR=1时为写。

实 验 原 理 图2-1-2 读写控制逻辑 实验原理图如图2-1-3所示,存储器数据线接至数据总线,数据总线上接有8个LED灯显示D7…D0的内容。地址线接至地址总线,地址总线上接有8个LED灯显示A7…A0的内容,地址由地址锁存器(74LS273,位于PC&AR单元)给出。数据开关(位于IN单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。 图2-1-3 存储器实验原理图 实验箱中所有单元的时序都连接至时序与操作台单元,CLR都连接至CON单元的CLR按钮。 实验时T3由时序单元给出,其余信号由CON单元的二进制开关模拟给出,其中IOM应为低(即MEM操作),RD、WR高有效,MR和MW低有效,LDAR高有效。

零总线翻转静态随机存取存储器(ZBT)简介

ZBT是Zero Bus Turnaround SRAM的缩写,即“零总线翻转静态随机存取存储器”。属于SRAM的一种,SRAM的类型有很多种,如下图所示: 1).ASRAM是普通异步静态随机存取存储器,该器件内部无参考时钟,读写时序比较简单,只要将控制信号选中指定地址和数据线即可读取或写入数据; 2).SSRAM是同步静态随机存取存储器,与ASRAM相比,内部多了一个参考时钟; 3).DPSRAM即Double Port SRAM,双口SRAM的意思; 4).Synchronous Burst SSRAM即同步突发SSRAM,读写速率比异步SRAM 快,主要有Flow-Through(直通方式)和Pipeline(流水线方式)两种操作方式; 5).DDR SRAM即双数据速率SRAM; 6).QDR SRAM即四倍数据速率SRAM,前面已经专题介绍过了; 7).ZBT SRAM即零总线翻转SRAM,也是本文的重点介绍内容。 记得之前在介绍RAM器件的时候介绍过,RAM器件在读/写操作间进行状态转换的时候,需要一些空闲指令周期NOP(No Operation)来进行过渡,普通SRAM

进行读操作时,数据滞后两个时钟周期,而写操作是即时的,从写操作状态切换到读操作状态需要等待两个时钟周期。 如果在某些需要频繁进行读/写操作切换的系统中使用普通SRAM的话,总线利用效率将会变得非常低。 为此,IDT公司联合推出ZBT SRAM,该器件通过简单的接口控制逻辑消除了读写操作转换的等待时间,在读写操作状态转换过程中无需等待,直接切换,总线利用率可达100%,非常适合读写操作频繁切换的场合。普通SRAM和ZBT SRAM读写状态切换对比图下图所示: ZBT SRAM根据所带有的接口的不同,可分为两种即pipelined ZBT SRAM 和flow -through ZBT SRAM,在pipelined ZBT SRAM中,读命令发出两个时钟周期之后,可得到读取的数据,写命令发出两个时钟周期之后,可以写数据;在flow - through ZBT SRAM中读命令发出一个时钟周期之后,可得到读取的数据,写命令发出一个时钟周期之后,可以写数据。他们都支持TTL和COMS I/O口标准。其总线操作过程如下图所示。

旋转变压器与编码器的区别

从原理上讲,旋转变压器是采用电磁感应原理工作,随着旋转变压器的转子和定子角位置不同,输出信号可以实现对输入正弦载波信号的相位变换和幅值调制,最终由专用的信号处理电路或者某些具备一定功能接口的DSP和单片机,根据输出信号的幅值和相位与正弦载波信号的关系,解析出转子和定子间的角位置关系。 旋转变压器有单对极和多对极之分,n对极的又被习惯地称为n倍速。在一个极对的角度范围内(单对极就是一整圈),旋转变压器信号经处理后的结果一般都具有反映绝对位置的特性,即可反映当前角位置是处于0~360度(电角度)中的多少度上。目前商用分辨率可以做到2的12次方以上,直至2的16次方,再高就比较困难了。 典型的旋转变压器本体由硅钢片和漆包线构成,不包含任何电子元件,因而抗震能力和温度特性极佳,因而其抗恶劣环境的工作能力远胜于普通旋转编码器,在军工产品中具有广泛应用。 典型的旋转编码器采用光栅原理,用光电方法进行角位置检测,又可分为增量式和绝对式等类型. 旋转变压器 简称旋变,是一种输出电压随转子转角变化的信号元件。当励磁绕组以一定频率的交流电压励磁时,输出绕组的电压幅值与转子转角成正余弦函数关系,或保持某一比例关系,或在一定转角范围内与转角成线性关系。 按励磁方式分,多摩川旋转变压器分BRT和BRX两种,BRT是单相励磁两相输出;BRX是双相励磁单相输出。用户往往选择BRT型的旋变,因为它易于解码。 有增量型和绝对型 增量型只是测角位移(间接为角速度)增量,以前一时刻为基点.而绝对型测从开始工作后角位移量. 增量型测小角度准,大角度有累积误差 绝对型测小角度相对不准,但大角度无累积误差 说简单点的编码器更精确采用的是脉冲计数旋转变压器就不是脉冲技术而是模拟量反馈 据我所知区别如下:1、编码器多是方波输出的,旋变是正余弦的,通过芯片解算出相位差。2、旋变的转速比较高,可以达到上万转,编码器就没那么高了。 3、旋变的应用环境温度是-55到+155,编码器是-10到+70。 4、旋变一般是增量的。根本区别在于:数字信号和模拟正弦或余弦信号的的区别。resolver 有2组信号,可以分别处理成增量信号和绝对值型号。今后会越来越多地得到推广使用。

一文了解随机存取和非随机存取的区别

一文了解随机存取和非随机存取的区别 随机存取和非随机存取的区别1、随机存取就是直接存取,可以通过下标直接访问的那种数据结构,与存储位置无关,例如数组。非随机存取就是顺序存取了,不能通过下标访问了,只能按照存储顺序存取,与存储位置有关,例如链表。 2、顺序存取就是存取第N个数据时,必须先访问前(N-1)个数据(list),随机存取就是存取第N个数据时,不需要访问前(N-1)个数据,直接就可以对第N个数据操作(array)。 随机存取和非随机存取的结构1、顺序存储结构 在计算机中用一组地址连续的存储单元依次存储线性表的各个数据元素,称作线性表的顺序存储结构。 顺序存储结构是存储结构类型中的一种,该结构是把逻辑上相邻的节点存储在物理位置上相邻的存储单元中,结点之间的逻辑关系由存储单元的邻接关系来体现。由此得到的存储结构为顺序存储结构,通常顺序存储结构是借助于计算机程序设计语言(例如c/c++)的数组来描述的。 顺序存储结构的主要优点是节省存储空间,因为分配给数据的存储单元全用存放结点的数据(不考虑c/c++语言中数组需指定大小的情况),结点之间的逻辑关系没有占用额外的存储空间。采用这种方法时,可实现对结点的随机存取,即每一个结点对应一个序号,由该序号可以直接计算出来结点的存储地址。但顺序存储方法的主要缺点是不便于修改,对结点的插入、删除运算时,可能要移动一系列的结点。 2、随机存储结构 在计算机中用一组任意的存储单元存储线性表的数据元素(这组存储单元可以是连续的,也可以是不连续的)。 它不要求逻辑上相邻的元素在物理位置上也相邻。因此它没有顺序存储结构所具有的弱点,但也同时失去了顺序表可随机存取的优点。 链式存储结构特点

计算机组成原理实验报告(运算器组成、存储器)

计算机组成原理实验报告 一、实验1 Quartus Ⅱ的使用 一.实验目的 掌握Quartus Ⅱ的基本使用方法。 了解74138(3:8)译码器、74244、74273的功能。 利用Quartus Ⅱ验证74138(3:8)译码器、74244、74273的功能。 二.实验任务 熟悉Quartus Ⅱ中的管理项目、输入原理图以及仿真的设计方法与流程。 新建项目,利用原理编辑方式输入74138、74244、74273的功能特性,依照其功能表分别进行仿真,验证这三种期间的功能。 三.74138、74244、74273的原理图与仿真图 1.74138的原理图与仿真图 74244的原理图与仿真图

1. 4.74273的原理图与仿真图、

实验2 运算器组成实验 一、实验目的 1.掌握算术逻辑运算单元(ALU)的工作原理。 2.熟悉简单运算器的数据传送通路。 3.验证4位运算器(74181)的组合功能。 4.按给定数据,完成几种指定的算术和逻辑运算。 二、实验电路 附录中的图示出了本实验所用的运算器数据通路图。8位字长的ALU由2片74181构成。2片74273构成两个操作数寄存器DR1和DR2,用来保存参与运算的数据。DR1接ALU的A数据输入端口,DR2接ALU的B数据输入端口,ALU的数据输出通过三态门74244发送到数据总线BUS7-BUS0上。参与运算的数据可通过一个三态门74244输入到数据总线上,并可送到DR1或DR2暂存。 图中尾巴上带粗短线标记的信号都是控制信号。除了T4是脉冲信号外,其他均为电位信号。nC0,nALU-BUS,nSW-BUS均为低电平有效。 三、实验任务 按所示实验电路,输入原理图,建立.bdf文件。 四.实验原理图及仿真图 给DR1存入01010101,给DR2存入10101010,然后利用ALU的直通功能,检查DR1、

静态随机存储器实验实验报告

**大学 实验(实训)报告 实验名称运算器、存储器所属课程计算机组成与结构所在系计算机科学与技术班级 学号 姓名 指导老师 实验日期

**大学实验(实训)报告 实验静态随机存储器实验 2.1. 实验目的 掌握静态随机存储器RAM工作特性及数据的读写方法。 2.2. 实验内容 给存储器的00H、01H、02H、03H、04H 地址单元中分别写入数据 11H、12H、13H、14H、15H,再依次读出数据。 2.3. 实验设备 TDN-CM++计算机组成原理教学实验系统一台,排线若干。 2.4. 实验原理 实验所用的静态存储器由一片6116(2K×8bit)构成(位于MEM单元),如图2-1所示。6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如下图,当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS常接地。 图2-1 SRAM 6116 引脚图 由于存储器最终挂接到CPU上,所以还需要一个读写控制逻辑,使得CPU能控制MEM 的读写,实验中的读写控制逻辑如图2-2所示,由于T3的参与,可以保证MEM的写脉宽与T3一致,T3由时序单元的TS3给出。IOM用来选择是对 I/O还是对MEM进行读写操作,RD=1时为读,WR=1时为写。

实验原理如图2-3所示,存储器数据线接至数据总线,数据总线上接有8个LED 灯显示D7…D0 的内容。地址线接至地址总线,地址总线上接有8个LED 灯显示A7…A0的内容,地址由地址锁存器给出。数据开关经一个三态门连至数据总线,分时给出地址和数据。地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。 实验箱中所有单元的时序都连接至时序与操作台单元,CLR 都连接至CON 单元的CLR 按钮。实验时T3由时序单元给出,其余信号由CON 单元的二进制开关模拟给出,其中IOM 应为低(即MEM 操作),RD 、WR 高有效,MR 和MW 低有效,LDAR 高有效。 2.5.实验步骤 MR MW D7 —————D0D7 —————D0 A7 —————A0 OE CS T3 IOM RD WE 读写译码 RD WR 74LS27374LS245IN 单元 AD7 | || AD0 LDAR IOR IN_B A10 —A8————— ————— ——————————----—————6116

旋转变压器分类及接口电路

摘要:本文简要介绍编码器、旋转变压器应用特点和接口方法,其中重点介绍产品通信协议和硬件接口电路以及专用的接收芯片AU5561应用方法。 编码器发展历史 早期的编码器主要是旋转变压器,旋转变压器IP值高,能在一些比较恶劣的环境条件下工作,虽然因为对电磁干扰敏感以及解码复杂等缺点而逐渐退出,但是时至今日,仍然有其特有的价值,比如作为混合动力汽车的速度反馈,几乎是不可代替的,此外在环境恶劣的钢铁行业、水利水电行业,旋转变压器因为其防护等级高同样获得了广泛的应用。随着半导体技术的发展,后来便有霍尔传感器和光电编码器,霍尔传感器精度不高但价格便宜,而且不能耐高温,只适合用在一些低端场合,光电编码器正是由于克服了前面两种编码器的缺点而产生,它精度高,抗干扰能力强,接口简单使用方便因而获得了最广泛的应用。 编码器的生产厂家很多,这里以多摩川的产品为例进行介绍。 下面以旋转变压器、增量式编码器、绝对式编码器为例逐一进行介绍。 旋转变压器 简称旋变是一种输出电压随转子转角变化的信号元件。当励磁绕组以一定频率的交流电压励磁时,输出绕组的电压幅值与转子转角成正余弦函数关系,或保持某一比例关系,或在一定转角范围内与转角成线性关系。 按励磁方式分,多摩川旋转变压器分BRT和BRX两种,BRT是单相励磁两相输出;BRX是双相励磁单相输出。用户往往选择BRT型的旋变,因为它易于解码。 旋转变压器解码 图4旋转变压器电气示意图。 旋变的输入输出电压之间的具体函数关系如下所示: 设转子转动角度为θ,初级线圈电压(即励磁电压):ER1-R2=E*Sin2πft f:励磁频率,E:信号幅度 那么输出电压ES1-S3=K*E*Sin2πft*Cosθ; ES2-S4=K*E*Sin2πft*Sinθ K:传输比, θ:转子偏离原点的角度 令θ=ωt,即转子做匀速运动,那么其输出信号的函数曲线可表示为图5所示, 图中信号频率为f,即励磁信号频率,最大幅度为E,包络信号为Sinωt和Cosωt,解码器就是通过检测这两组输出信号获取旋变位置信息的。 不难看出,励磁频率越高,旋变解码精度也就越高,而励磁电压幅度则对解码没有很明显的影响。只需达到一定的电压数值即可,一般来讲3V~1.2倍额定电压都可满足解码需求。 多摩川为自己的旋变开发了专门的解码芯片AU6802N1,并且艾而特公司有现成的解码板可供使用,解码板支持10KHZ励磁频率,0.5的传输比,可以同时提供增量式和绝对式信号输出,增量式输出

静态存储器扩展实验报告

静态存储器扩展实验报告告圳大学实验报深

微机原理与接口技术 课程名称: 静态存储器扩展实验实验项目名称: 信息工程学院学院: 专业:电子信息工程

指导教师:周建华 32012130334 学号:班级:电子洪燕报告人:班 2014/5/21 实验时间: 实验报告提交时间:2014/5/26 教务部制. 一.实验目的与要求: 1. 了解存储器扩展的方法和存储器的读/写。 2. 掌握CPU对16位存储器的访问方法。

二.实验设备 PC机一台,TD-PITE实验装置或TD-PITC实验装置一套,示波器一台。 三.实验原理VCC28A141WE27A122A1326A73A8254A6存储器是用来存储信息的A924A55A1123A46OE22A3762256A10218A2CS209A1部件,是计算机的重要组成部D719A010D618D011D517D112D416D213D315GND14管组成的是由MOS分,静态RAM触发器电路,每个触发器可以存放1位

信息。只要不掉电,所储存的信息就不会丢失。因此,静态RAM工作稳定,不要外加刷新电路,使用方便。 但一般SRAM 的每一个触发器是由6个晶体管组成,SRAM 芯片的集成度不会太高,目前较常用的有6116(2K×8位),图4.1 62256引脚图6268位)622532位。本验平台上选. 用的是62256,两片组成32K×16位的形式,共64K字节。 62256的外部引脚图如图4.1所示。 本系统采用准32位CPU,具有16位外部

数据总线,即D0、D1、…、D15,地址总线为BHE#(#表示该信号低电平有效)、BLE #、A1、A2、…、A20。存储器分为奇体和偶体,分别由字节允许线BHE#和BLE#选通。 存储器中,从偶地址开始存放的字称为规则字,从奇地址开始存放的字称为非规则字。处理器访问规则字只需要一个时钟周期,BHE#和BLE#同时有效,从而同时选通存储器奇体和偶体。处理器访问非规则字却需要

《计算机组成原理》实验二报告

《计算机组成原理》 实验报告 学院:计算机学院 专业:软件工程 班级学号:130803 313002384 学生姓名:胡健华 实验日期:2014-11-13 指导老师:李鹤喜 五邑大学计算机学院计算机组成原理实验室

实验二 一、实验名称:SRAM 静态随机存储器实验 二、实验目的: 掌握静态随机存储器RAM工作特性及数据的读写方法。 三、实验内容: 1、向存储器中指定的地址单元输入数据,地址先输入AR寄存器,在地址灯上显示;再将数据 送入总线后,存到指定的存储单元,数据在数据显示灯显示。 2、从存储器中指定的地址单元读出数据, 地址先输入AR寄存器,在地址灯显示; 读出的数据送入 总线, 通过数据显示灯显示。 四、实验设备: PC机一台,TD-CMA实验系统一套。 五、实验步骤: 1、关闭实验系统电源,按图2-4 连接实验电路,并检查无误,图中将用户需要连接的信号用 圆圈标明。 2、将时序与操作台单元的开关KK1、KK3 置为运行档、开关KK2 置为‘单步’档。 3、将CON 单元的IOR 开关置为1(使IN 单元无输出),打开电源开关,如果听到有‘嘀’报 警声,说明有总线竞争现象,应立即关闭电源,重新检查接线,直到错误排除。 图2-4

4、给存储器的00H、01H、02H、03H、04H 地址单元中分别写入数据11H、12H、13H、14H、15H。 由前面的存储器实验原理图(图2-1-3)可以看出,由于数据和地址由同一个数据开关给出,因此数据和地址要分时写入,先写地址,具体操作步骤为:先关掉存储器的读写(WR=0,RD=0),数据开关输出地址(IOR=0),然后打开地址寄存器门控信号(LDAR=1),按动ST 产生T3 脉冲,即将地址打入到AR 中。再写数据,具体操作步骤为:先关掉存储器的读写(WR=0,RD=0)和地址寄存器门控信号(LDAR=0),数据开关输出要写入的数据,打开输入三态门(IOR=0),然后使存储器处于写状态(WR=1,RD=0,IOM=0),按动ST 产生T3脉冲,即将数据打入到存储器中。写存储器的流程如图2-5 所示(以向00 地址单元写入11H为例): 图2-5 5、依次读出第00、01、02、03、04 号单元中的内容,观察上述各单元中的内容是否与前面写 入的一致。同写操作类似,也要先给出地址,然后进行读,地址的给出和前面一样,而在进行读操作时,应先关闭IN 单元的输出(IOR=1),然后使存储器处于读状态(WR=0,RD=1,IOM=0),此时数据总线上的数即为从存储器当前地址中读出的数据内容。读存储器的流程如图2-6 所示(以从00 地址单元读出11H 为例): 图2-6 如果实验箱和 PC 联机操作,则可通过软件中的数据通路图来观测实验结果(软件使用说明请看附录1),方法是:打开软件,选择联机软件的“【实验】—【存储器实验】”,打开存储器实验的数据通路图,如图2-7 所示。 进行上面的手动操作,每按动一次ST 按钮,数据通路图会有数据的流动,反映当前存储器所做的操作(即使是对存储器进行读,也应按动一次ST 按钮,数据通路图才会有数据流动),或在软件中选择“【调试】—【单周期】”,其作用相当于将时序单元的状态开关置为‘单步’档

实验十四 存储器扩展机读写实验

实验十四存储器扩展机读写实验 一、实验目的 (1)通过阅读并测试示例程序,完成程序设计题,熟悉静态RAM的扩展方法。 (2)了解8086/8088与存储器的连接,掌握扩展存储器的读写方法。 二、实验内容 1.实验原理(62256RAM介绍) 62256是32*8的静态存储器,管脚如图所示。其中:A0~A14为地址线,DB0~DB7为数据线,/cs为存储器的片选,/OE为存储器数据输出选通信号,/WE为数据写入存储器信号。62256工作方式如下图。 /CS /WE /OE 方式DB-~DB7 H X X 未选中高阻 L H H 读写禁止高阻 L L H 写IN L H L 读OUT 2.实验内容 设计扩展存储电器的硬件连接图并编制程序,讲字符A~Z循环存入62256扩展RAM 中,让后再检查扩展存储器中的内容。 三、程序设计 编写升序,将4KB扩展存储器交替写入55H和0AAH。 程序如下: RAMADDR EQU 0000H RAMOFF EQU 9000H COUNT EQU 800H CODE SEGMENT ASSUME CS:CODE START: PROC NEAR MOV AX,RAMADDR MOV DS,AX MOV BX,RAMOFF MOV CX,COUNT MOV DL,55h MOV AX ,0AAH REP: MOV [BX],DL INC BX MOV [BX],AX INC BX LOOP REP JMP $ CODE ENDS END START 四、实验结果 通过在软件上调试,运行时能够看到内存地址的改变,证明此扩展的程序成功实现了。 五、实验心得

静态随机存储器实验实验报告

**大学 实验(实训)报告 实验名称运算器、存储器 所属课程计算机组成与结构 所在系计算机科学与技术 班级 学号 姓名 指导老师 实验日期 实验静态随机存储器实验 2、1、实验目的 掌握静态随机存储器RAM工作特性及数据的读写方法。 2、2、实验内容 给存储器的00H、01H、02H、03H、04H 地址单元中分别写入数据 11H、12H、13H、14H、15H,再依次读出数据。 2、3、实验设备 TDN-CM++计算机组成原理教学实验系统一台,排线若干。 2、4、实验原理 实验所用的静态存储器由一片6116(2K×8bit)构成(位于MEM单元),如图2-1所示。6116有三个控制线:CS(片选线)、OE(读线)、WE(写线),其功能如下图,当片选有效(CS=0)时,OE=0时进行读操作,WE=0时进行写操作,本实验将CS常接地。

的读写,一致,T3 时为读,WR=1 实验原理如图2-3所示,存储器数据线接至数据总线,数据总线上接有8个LED灯显示D7…D0 的内容。地址线接至地址总线,地址总线上接有8个LED灯显示A7…A0的内容,地址由地址锁存器给出。数据开关经一个三态门连至数据总线,分时给出地址与数据。地址寄存器为8位,接入6116的地址A7…A0,6116的高三位地址A10…A8接地,所以其实际容量为256字节。

MR MW D7 —————D0D7 —————D0 A7 —————A0 OE CS T3 IOM RD WE 读写译码 RD WR 74LS27374LS245IN 单元 AD7 ||| AD0 LDAR IOR IN_B A10 —A8————— ————— ——————————----—————6116 实验箱中所有单元的时序都连接至时序与操作台单元,CLR 都连接至CON 单元的CLR 按钮。实验时T3由时序单元给出,其余信号由CON 单元的二进制开关模拟给出,其中IOM 应为低(即MEM 操作),RD 、WR 高有效,MR 与MW 低有效,LDAR 高有效。 2、5.实验步骤

计算机组成原理静态随机存储器实验

实验报告 一、实验名称 静态随机储存器实验 二、实验目的 掌握静态随机储存器RAM的工作特性和数据的读写方法 三、实验设备 TDN-CM++计算机组成原理教学实验系统一套,导线若干。 四、实验原理 实验所用的半导体静态存储器电路原理如图1所示,实验中的静态存储器由一片6116(2K×8)构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。地址灯ADO~AD7与地址线相连,显示地址线内容。数据开关经三态门(74LS245)连至数据总线,分时给出地址和数据。 因地址寄存器为8位,接入6116的地址A7--AO,而高三位A8—A1O接地,所以其实际容量为256字节。6116有三个控制线:CE(片选线)、0E(读线)、WE(写线)。当片选有效(CE=O)时,OE=O时进行读操作,WE=0时进行写操作。本实 验中将0E常接地,因此6116的引脚信号WE=1时进行读操作,WE=0时进行写操作。 在此情况下,要对存储器进行读操作,必须设置控制端CE=O、WE=O,同时有T3脉冲到来,要对存储器进行写操作,必须设置控制端CE=O、WE=1,同时有T3脉冲到来,其读写时间与T3脉冲宽度一致。 实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可调,其它电平控制信号由“SWITCH UNIT”单元的二进制开关模拟,其中SW-B为低电平有效,LDAR为高电平有效。

图1 存储器实验原理图 五、实验内容 1. 向存储器中指定的地址单元输入数据,地址先输入AR寄存器,在地址灯 上显示;再将数据送入总线后,存到指定的存储单元,数据在数据显示灯和数码 显示管显示。 2. 从存储器中指定的地址单元读出数据, 地址先输入AR寄存器,在地址灯 显示; 读出的数据送入总线, 通过数据显示灯和数码显示管显示。 六、实验步骤 (1)将时序电路模块中的Φ和H23排针相连。 将时序电路模块中的二进制开关“STOP”设置为“RUN”状态、将“STEP”设置为"STEP"状态。 注意:关于stop和step的说明: 将“STOP”开关置为“Run"状态、“STEP”开关置为“EXEC”状态时,按动微动开关START,则T3输出为连续的方波信号,此时调节电位器W1,用示波器观察,使T3输出实验要求的脉冲信号。当“STOP”开关置为“RUN”状态、“STEP”开关置为"STEP"状态时,每按动一次微动开关START,则T3输出一个单脉冲,其脉冲宽度与连续方式相同。

RAM(随机存取存储器)

随机存取存储器RAM(随机存取存储器) RAM -random access memory 随机存储器 存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。 按照存储信息的不同,随机存储器又分为静态随机存储器(Static RAM,SRAM)和动态随机存储器(Dynamic RAM,DRAM)。 1、随机存储器特点 ①随机存取 所谓“随机存取”,指的是当存储器中的消息被读取或写入时,所需要的时间与这段信息所在的位置无关。相对的,读取或写入顺序访问(Sequential Access)存储设备中的信息时,其所需要的时间与位置就会有关系(如磁带)。 ②易失性 当电源关闭时RAM不能保留数据。如果需要保存数据,就必须把它们写入一个长期的存储设备中(例如硬盘)。RAM和ROM相比,两者的最大区别是RAM在断电以后保存在上面的数据会自动消失,而ROM不会。 ③高访问速度 现代的随机存取存储器几乎是所有访问设备中写入和读取速度最快的,取存延迟也和其他涉及机械运作的存储设备相比,也显得微不足道。

④需要刷新 现代的随机存取存储器依赖电容器存储数据。电容器充满电后代表1(二进制),未充电的代表0。由于电容器或多或少有漏电的情形,若不作特别处理,数据会渐渐随时间流失。刷新是指定期读取电容器的状态,然后按照原来的状态重新为电容器充电,弥补流失了的电荷。需要刷新正好解释了随机存取存储器的易失性。 ⑤对静电敏感 正如其他精细的集成电路,随机存取存储器对环境的静电荷非常敏感。静电会干扰存储器内电容器的电荷,引致数据流失,甚至烧坏电路。故此触碰随机存取存储器前,应先用手触摸金属接地。 2、RAM ROM 内存的区别 rom -read only memory 只读存储器 ①简单地说,在计算机中,RAM 、ROM都是数据存储器。RAM 是随机存取存储器,它的特点是易挥发性,即掉电失忆。ROM 通常指固化存储器(一次写入,反复读取),它的特点与RAM 相反。ROM又分一次性固化、光擦除和电擦除重写两种类型。 ②什么是内存呢? 在计算机的组成结构中,有一个很重要的部分,就是存储器。存储器是用来存储程序和数据的部件,对于计算机来说,有了存储器,才有记忆功能,才能保证正常工作。存储器的种

计算机组成原理与系统结构实验教程

实验一算术逻辑运算实验 一.实验目的 1.了解运算器的组成结构。 2.掌握运算器的工作原理。 3.学习运算器的设计方法。 4.掌握简单运算器的数据传送通路。 5.验证运算功能发生器74LS181 的组合功能。 二.实验设备 TDN-CM+或TDN-CM++教学实验系统一套。 三.实验原理 实验中所用的运算器数据通路图如图2.6-1。图中所示的是由两片74LS181 芯片以并/串形式构成的8 位字长的运算器。右方为低4 位运算芯片,左方为高4 位运算芯片。低位芯片的进位输出端Cn+4 与高位芯片的进位输入端Cn 相连,使低4 位运算产生的进位送进高4 位运算中。低位芯片的进位输入端Cn 可与外来进位相连,高位芯片的进位输出引至外部。两个芯片的控制端S0~S3 和M 各自相连,其控制电平按表2.6-1。 为进行双操作数运算,运算器的两个数据输入端分别由两个数据暂存器DR1、DR2(用锁存器74LS273 实现)来锁存数据。要将内总线上的数据锁存到DR1 或DR2 中,则锁存器74LS273 的控制端LDDR1 或LDDR2 须为高电平。当T4 脉冲来到的时候,总线上的数据就 被锁存进DR1 或DR2 中了。 为控制运算器向内总线上输出运算结果,在其输出端连接了一个三态门(用74LS245 实现)。若要将运算结果输出到总线上,则要将三态门74LS245 的控制端ALU-B 置低电平。否则输出高阻态。

2 图2.6-1 运算器通路图 数据输入单元(实验板上印有INPUT DEVICE)用以给出参与运算的数据。其中,输入开 关经过一个三态门(74LS245)和内总线相连,该三态门的控制信号为SW-B,取低电平时, 开关上的数据则通过三态门而送入内总线中。 总线数据显示灯(在BUS UNIT 单元中)已与内总线相连,用来显示内总线上的数据。 控制信号中除T4 为脉冲信号,其它均为电平信号。 由于实验电路中的时序信号均已连至“W/R UNIT”单元中的相应时序信号引出端,因 此,需要将“W/R UNIT”单元中的T4 接至“STATE UNIT”单元中的微动开关KK2 的输出 端。在进行实验时,按动微动开关,即可获得实验所需的单脉冲。 S3、S2、 S1、S0 、Cn、M、LDDR1、LDDR2、ALU-B、SW-B 各电平控制信号则使用“SWITCH UNIT”单元中的二进制数据开关来模拟,其中Cn、ALU-B、SW-B 为低电平有效,LDDR1、 LDDR2 为高电平有效。 对于单总线数据通路,作实验时就要分时控制总线,即当向DR1、DR2 工作暂存器打入 数据时,数据开关三态门打开,这时应保证运算器输出三态门关闭;同样,当运算器输出结 果至总线时也应保证数据输入三态门是在关闭状态。 四.实验步骤 1.按图2.6-2 连接实验电路并检查无误。图中将用户需要连接的信号线用小圆圈标明(其 它实验相同,不再说明)。 2.开电源开关。

存储器和IO扩展实验,计算机组成原理

科技学院 课程设计实验报告 ( 2014--2015年度第一学期) 名称:计算机组成原理综合实验题目:存储器和I/O扩展实验 院系:信息工程系 班级: 学号: 学生姓名: 指导教师:李梅王晓霞 设计周数:一周 成绩: 日期:2015 年1 月

一、目的与要求 1. 内存储器部件实验 (1)熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处;学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。 (2)理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案; (3)了解静态存储器系统使用的各种控制信号之间正常的时序关系; (4)了解如何通过读、写存储器的指令实现对58C65 ROM芯片的读、写操作; (5)加深理解存储器部件在计算机整机系统中的作用。 2. I/O口扩展实验 学习串行口的正确设置和使用。 二、实验正文 1.主存储器实验内容 1.1实验的教学计算机的存储器部件设计(说明只读存储器的容量、随机读写器的容量,各选用了什么型号及规格的芯片、以及地址空间的分布) 在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区(ROM,存放监控程序等) 和随读写存储区(RAM)两部分,ROM存储区选用4片长度8位、容量8KB 的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片 实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分 成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序, 2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作为监 控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩 展内存容量(存储器的字、位扩展)的教学实验。 1.2扩展8K字的存储空间,需要多少片58C65芯片,58C65芯片进行读写时的特殊要求 要扩展8K字的存储空间,需要使用2片(每一片有8KB容量,即芯片内由8192个单元、每个单元由8个二进制位组成)存储器芯片实现。对 58C65 ROM芯片执行读操作时,需要保证正确的片选信号(/CE)为低点平, 使能控制信号(/OE)为低电平,读写命令信号(/WE)为高电平,读58C65 ROM 芯片的读出时间与读RAM芯片的读出时间相同,无特殊要求;对58C65 ROM 芯片执行写操作时,需要保证正确的片选信号(/CE)为低电平,使能控制信 号(/OE)为高电平,读写命令信号(/WE)为低电平,写58C65 ROM芯片的 维持时间要比写RAM芯片的操作时间长得多。为了防止对58C65 ROM芯片执 行误写操作,可通过把芯片的使能控制引脚(/OE)接地来保证,或者确保读 写命令信号(/WE)恒为高电平。 1.3在实验中思考为何能用E命令直接写58C65芯片的存储单元,而A命令则有时不正确;