段成华数字集成电路第六次作业

数字集成系统第六次作业

1.For the VHDL model given below (Code List One), compare the FIFOs implementations on CPLD and FPGA.

(1)Synthesize and verify (simulate) the VHDL design of the FIFOs;

(2)For CPLD implementation (fit) of the FIFOs, how many MCs

(macrocells) and PTs (product terms) are needed? Which parameter is critical to the maximum internal clock working frequency? Try to find out this critical parameter and its corresponding circuit path.

(3)For FPGA implementation (place and route) of the FIFOs, how

many LBs (logic blocks)? Which parameter is critical to the maximum internal clock working frequency? Try to find out this critical parameter and its corresponding circuit path.

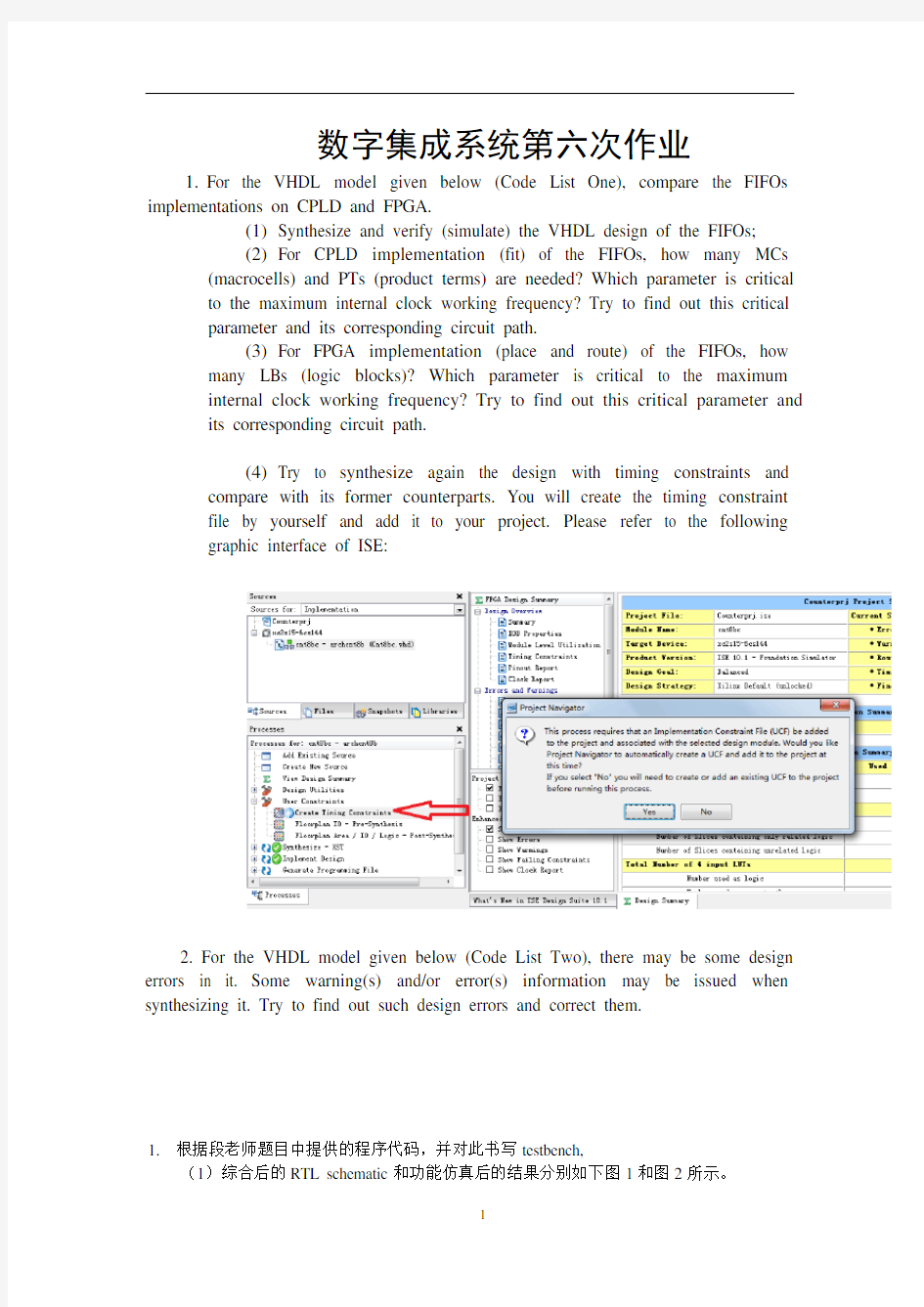

(4)Try to synthesize again the design with timing constraints and

compare with its former counterparts. You will create the timing constraint file by yourself and add it to your project. Please refer to the following graphic interface of ISE:

2. For the VHDL model given below (Code List Two), there may be some design errors in it. Some warning(s) and/or error(s) information may be issued when synthesizing it. Try to find out such design errors and correct them.

1.根据段老师题目中提供的程序代码,并对此书写testbench,

(1)综合后的RTL schematic和功能仿真后的结果分别如下图1和图2所示。

图 1 RTL schematic

图2仿真结果(功能仿真)

(2)设置芯片为XC9500 CPLDS系XC95108-7-PQ160,速度为-7,综合后报告分析如下

图 3 CPLD综合报告

由图3可以知道,对于本程序,一共使用了87个Macrocells,占总数的百分之八十一,使用了228个Pterms,占总数的百分之四十三,资源相对充裕,满足程序的设计要求。

图 4 CPLD时间报告

由图4可知,时钟的最小周期为15ns,受clock to setup delay影响最大,故关键路径为tcyc。延时为15ns,时钟的工作频率为66.67MHz。

(3) 更换芯片型号为Spartan3- xc3s200-5pq208,速度为-5,其综合报告如下

图 5 FPGA综合报告

查Spartan3的datasheet如下

图 6 Spartan3 datasheet

由上图知,对于选择的器件,其logic cell为4320,CLB 有24X20=480个,每个CLB包含4个slice,而对于我们的程序,一共使用了66个slice,占总数的百分之三(总slice共计1920个),故使用的CLB数为66/4=16.5,即使用了17个CLB

图7 时间报告

关键路径为clock to setup delay,延时为4.821ns,它对时钟的工作频率影响最大。时钟的工作频率为207.42MHz。

(4)

图8 timing constrain

图9 没有设置时序约束时的报告

图10 设置clk周期约束为5ns时的报告

图11 设置clk周期约束为4.5ns时的报告

图12 设置clk周期约束为4ns时的报告

图13 设置clk周期约束为3.5ns时的报告

由图10至13可以看到,当对CLK进行约束时,会对系统性能有所影响,随着条件的苛刻,best case achievable也越来越小,但当限制小到一定程度时,EDA工具可能会无法布

通,如3.5ns时timing error为31,score为9677.

2.

图14 对fifoxy进行综合后如下

主要有以上两个warning和一个错误:

(1) 程序中,输入端口rd没有使用到,其作用被oe所取代,因此可以将rd信号去掉,用oe来表示其功能,且不影响整个系统的设计。

(2) 程序中输入信号端口en也未被使用,因为直接在fifo(wrptr)中取得了写地址的值,因此信号en也应去掉。

(3) 语句dmuxout<=fifo(wrptr); 应改为dmuxout<=fifo(rdptr); 因为这时是读寄存器里的值,应该由读地址指针rdptr来指定应该读取哪个寄存器的值。

图15 修改后的波形图

备注,当时为了尽快看到波形,故使用了altera公司的quartus来对波形进行快速设置。上图为quartus的仿真波形图。

附录:fifo89—testbench

-----------------------------------------------------------------

---------------

-- Company:

-- Engineer:

--

-- Create Date: 20:04:55 12/06/2014

-- Design Name:

-- Module Name: D:/xilinx_workspace/test4/fifo89/fifo89_tb.vhd -- Project Name: fifo89

-- Target Device:

-- Tool versions:

-- Description:

--

-- VHDL Test Bench Created by ISE for module: fifo89

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

-- Notes:

-- This testbench has been automatically generated using type s std_logic and

-- std_logic_vector for the ports of the unit under test. Xilinx recommends

-- that these types always be used for the top-level I/O o f a design in order

-- to guarantee that the testbench will bind correctly to t he post-implementation

-- simulation model.

--------------------------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

use ieee.std_logic_unsigned.all;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY fifo89_tb IS

END fifo89_tb;

ARCHITECTURE behavior OF fifo89_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT fifo89

PORT(

clk : IN std_logic;

rst : IN std_logic;

rd : IN std_logic;

wr : IN std_logic;

rdinc : IN std_logic;

wrinc : IN std_logic;

rdptrclr : IN std_logic;

wrptrclr : IN std_logic;

data_in : IN std_logic_vector(8 downto 0);

data_out : OUT std_logic_vector(8 downto 0) );

END COMPONENT;

--Inputs

signal clk : std_logic := '0';

signal rst : std_logic := '0';

signal rd : std_logic := '0';

signal wr : std_logic := '0';

signal rdinc : std_logic := '0';

signal wrinc : std_logic := '0';

signal rdptrclr : std_logic := '0';

signal wrptrclr : std_logic := '0';

signal data_in : std_logic_vector(8 downto 0) := (others => '0');

--Outputs

signal data_out : std_logic_vector(8 downto 0);

-- Clock period definitions

constant clk_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: fifo89 PORT MAP (

clk => clk,

rst => rst,

rd => rd,

wr => wr,

rdinc => rdinc,

wrinc => wrinc,

rdptrclr => rdptrclr,

wrptrclr => wrptrclr,

data_in => data_in,

data_out => data_out

);

-- Clock process definitions

clk_process :process

begin

clock_loop:loop

clk <= transport'0';

wait for 10ns;

clk <= transport'1';

wait for 100ns;

clk <= transport'0';

wait for 90ns;

end loop clock_loop;

end process;

-- Stimulus process

stim_proc: process

begin

wait for 200 ns; --200ns rst<=transport'1';

wait for 200 ns; --400ns rst<=transport'0';

rdptrclr<=transport'1';

wrptrclr<=transport'1';

wait for 200 ns; --600ns

wrinc<=transport'1';

rdptrclr<=transport'0';

wrptrclr<=transport'0';

wait for 200 ns; --800ns

rd<=transport'1';

wr<=transport'1';

wait for 400 ns; --1000ns

rd<=transport'0';

wait for 1800 ns; --2800ns

rd<=transport'1';

wr<=transport'0';

rdinc<=transport'1';

wrinc<=transport'0';

wait for 800 ns; --3600ns rd<=transport'0';

wait for 200 ns; --3600ns

rd<=transport'1';

wait;

end process;

-- Clock process definitions

data_process :process

begin

wait for 50ns;

data_in<="000000001"; d_loop:loop

wait for 200ns; data_in<=data_in+'1'; end loop d_loop;

end process; END;

集成电路设计基础作业题解答

第五次作业 、改正图题所示TTL 电路的错误。 如下图所示: 解答: (a)、B A B A Y ??=?=0,A,B 与非输出接基极,Q 的发射极接地。从逻辑上把Q 管看作单管禁止门便可得到B A Y ?=。逻辑没有错误! 若按照题干中所示接法,当TTL 与非门输出高电平时,晶体管Q 的发射结要承受高压,必然产生巨大的电流。为了不出现这种情况,可以在基极加一电阻或者在发射极加一二极管。但发射极加二极管后会抬高输出的低电平电压。所以只能在基极加一大电阻,实现分压作用。 另外一种方法是采用题(a )图中的A 输入单元结构。 & & ≥1 1 1

(b)、要实现由,我们可以使用线与+得到和B A B A 。但题干中的线与功能不合理。若其中一个为高电平且另外一个为低电平时,高电平输出降会往低电平输出灌电流,从而容易引起逻辑电平混乱。为了消除这一效应,可以在各自的输出加一个二极管。 (c)、电阻不应该接地,应该接高电平 (d)、电阻不应该接VCC ,而应该接低电平 、试分析图题(a ),(b)所示电路的逻辑功能。 解答: 图(a )中,单元1实现了A 的电平输入,B 是A 的对称单元。 功能单元2实现了A 和B 输入的或逻辑 功能单元4充当了Q8管的泄放网络,同时抬高了Q3,Q4管的输入逻辑电平,另外该单元还将或的结果传递给了Q8管 功能单元3中的Q8管实现了非逻辑,Q6和Q7复合管加强了输出级的驱动能力。 综上所述,(a )电路实现功能为B A Y +=,即或非的功能 图(b)中,Q1,Q2管依然实现传递输入的功能,Q3,Q4管实现或非的功能 Q6管和Q5管以及R5,R7共同组成的泄放网络实现了电压的传递 Q9管实现了非功能,Q7,Q8管依然是用来驱动负载的。Q9管和Q7,Q8轮流导通 综上所述,(b )实现的功能为B A B A Y +=+=

《半导体集成电路》考试题目及参考答案

第一部分考试试题 第0章绪论 1.什么叫半导体集成电路? 2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写? 3.按照器件类型分,半导体集成电路分为哪几类? 4.按电路功能或信号类型分,半导体集成电路分为哪几类? 5.什么是特征尺寸?它对集成电路工艺有何影响? 6.名词解释:集成度、wafer size、die size、摩尔定律? 第1章集成电路的基本制造工艺 1.四层三结的结构的双极型晶体管中隐埋层的作用? 2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。 3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤? 4.简述硅栅p阱CMOS的光刻步骤? 5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足? 6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。 7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。 8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。 第2章集成电路中的晶体管及其寄生效应 1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。 2.什么是集成双极晶体管的无源寄生效应? 3. 什么是MOS晶体管的有源寄生效应? 4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响? 5. 消除“Latch-up”效应的方法? 6.如何解决MOS器件的场区寄生MOSFET效应? 7. 如何解决MOS器件中的寄生双极晶体管效应? 第3章集成电路中的无源元件 1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些? 2.集成电路中常用的电容有哪些。 3. 为什么基区薄层电阻需要修正。 4. 为什么新的工艺中要用铜布线取代铝布线。 5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。 第4章TTL电路 1.名词解释

集成电路制造技术-原理与工艺 课后习题答案

第一单元: 3.比较硅单晶锭CZ,MCZ和FZ三种生长方法的优缺点。 答:CZ直拉法工艺成熟,可拉出大直径硅棒,是目前采用最多的硅棒生产方法。但直拉法中会使用到坩埚,而坩埚的使用会带来污染。同时在坩埚中,会有自然对流存在,导致生长条纹和氧的引入。直拉法生长多是采用液相掺杂,受杂质分凝、杂质蒸发,以及坩埚污染影响大,因此,直拉法生长的单晶硅掺杂浓度的均匀性较差。 MCZ磁控直拉法,在CZ法单晶炉上加一强磁场,高传导熔体硅的流动因切割磁力线而产生洛仑兹力,这相当于增强了熔体的粘性,熔体对流受阻。能生长无氧、均匀好的大直径单晶硅棒。设备较直拉法设备复杂得多,造价也高得多,强磁场的存在使得生产成本也大幅提高。 FZ悬浮区熔法,多晶与单晶均由夹具夹着,由高频加热器产生一悬浮的溶区,多晶硅连续通过熔区熔融,在熔区与单晶接触的界面处生长单晶。与直拉法相比,去掉了坩埚,没有坩埚的污染,因此能生长出无氧的,纯度更高的单晶硅棒。 6.硅气相外延工艺采用的衬底不是准确的晶向,通常偏离[100]或[111]等晶向一个小角度,为什么? 答:在外延生长过程中,外延气体进入反应器,气体中的反应剂气相输运到衬底,在高温衬底上发生化学反应,生成的外延物质沿着衬底晶向规则地排列,生长出外延层。 气相外延是由外延气体的气相质量传递和表面外延两个过程完成的。表面外延过程实质上包含了吸附、分解、迁移、解吸这几个环节,表面过程表明外延生长是横向进行的,是在衬底台阶的结点位置发生的。因此,在将硅锭切片制备外延衬底时,一般硅片都应偏离主晶面一个小角度。目的是为了得到原子层台阶和结点位置,以利于表面外延生长。 7. 外延层杂质的分布主要受哪几种因素影响? 答:杂质掺杂效率不仅依赖于外延温度、生长速率、气流中掺杂剂的摩尔分数、反应室的几何形状等因素,还依赖于掺杂剂自身的特性。另外,影响掺杂效率的因素还有衬底的取向和外延层结晶质量。硅的气相外延工艺中,在外延过程中,衬底和外延层之间存在杂质交换现象,即会出现杂质的再分布现象,主要有自掺杂效应和互扩散效应两种现象引起。

数字电子技术试卷及答案(免费版)

第1页(共28页) 第2页(共28页) 姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________ 本试卷共 6 页,满分100 分;考试时间:90 分钟;考试方式:闭卷 题 号 一 二 三 四(1) 四(2) 四(3) 四(4) 总 分 得 分 1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码 时,它相当于十进制数( )。 2.三态门电路的输出有高电平、低电平和( )3种状态。 3.TTL 与非门多余的输入端应接( )。 4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。 5. 已知某函数??? ??+??? ??++=D C AB D C A B F ,该函数的反函数F =( ) 。 6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。 7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。 8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( ) 。 9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。该ROM 有( )根地址线,有( )根数据读出线。 10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。 11. 下图所示电路中, Y 1=( );Y 2 =( );Y 3 =( )。 12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。 13.驱动共阳极七段数码管的译码器的输出电平为( )有效。 二、单项选择题(本大题共15小题,每小题2分,共30分) (在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。错 选、多选或未选均无分。) 1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。 A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7) 2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ??的值是( )。 A .111 B. 010 C. 000 D. 101 3.十六路数据选择器的地址输入(选择控制)端有( )个。 A .16 B.2 C.4 D.8 4. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )。 A. 1011--0110--1100--1000--0000 B. 1011--0101--0010--0001--0000 C. 1011--1100--1101--1110--1111 D. 1011--1010--1001--1000--0111 5.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( ) 。 A. 11111101 B. 10111111 C. 11110111 D. 11111111 6. 一只四输入端或非门,使其输出为1的输入变量取值组合有( )种。 A .15 B .8 C .7 D .1 7. 随机存取存储器具有( )功能。 A.读/写 B.无读/写 C.只读 D.只写 8.N 个触发器可以构成最大计数长度(进制数)为( )的计数器。 A.N B.2N C.N 2 D.2N 9.某计数器的状态转换图如下, 其计数的容量为( ) A . 八 B. 五 C. 四 D. 三 A B Y 1 Y 2 Y 3 000 001 010 011 100 101 110 111

大连理工c语言第五次上机作业参考答案

第五次上机作业:(请用指针实现) 1.数据移位 有n(n<=10)个整数,使前面各数顺序向后移m(m<=n)个位置,最后m 个数变成最前面的m个数,如图所示。编写函数shift(a,n,m)实现上述功能,在主函数中输入n个整数和输出调整后的n个数。 SAMPLE OUTPUT Input n(n<=10):10 Input 10 integers:1 2 3 4 5 6 7 8 9 10 Output the original:1 2 3 4 5 6 7 8 9 10 Input m(m<=10):4 Output the shifted:7 8 9 10 1 2 3 4 5 6 #include

半导体集成电路习题及答案

第1章 集成电路的基本制造工艺 1.6 一般TTL 集成电路与集成运算放大器电路在选择外延层电阻率上有何区别?为什么? 答:集成运算放大器电路的外延层电阻率比一般TTL 集成电路的外延层电阻率高。 第2章 集成电路中的晶体管及其寄生效应 复 习 思 考 题 2.2 利用截锥体电阻公式,计算TTL “与非”门输出管的CS r 2.2 所示。 提示:先求截锥体的高度 up BL epi mc jc epi T x x T T -----= 然后利用公式: b a a b WL T r c -? = /ln 1ρ , 2 1 2?? =--BL C E BL S C W L R r b a a b WL T r c -? = /ln 3ρ 321C C C CS r r r r ++= 注意:在计算W 、L 时, 应考虑横向扩散。 2.3 伴随一个横向PNP 器件产生两个寄生的PNP 晶体管,试问当横向PNP 器件在4种可能 的偏置情况下,哪一种偏置会使得寄生晶体管的影响最大? 答:当横向PNP 管处于饱和状态时,会使得寄生晶体管的影响最大。 2.8 试设计一个单基极、单发射极和单集电极的输出晶体管,要求其在20mA 的电流负载下 ,OL V ≤0.4V ,请在坐标纸上放大500倍画出其版图。给出设计条件如下: 答: 解题思路 ⑴由0I 、α求有效发射区周长Eeff L ; ⑵由设计条件画图 ①先画发射区引线孔; ②由孔四边各距A D 画出发射区扩散孔; ③由A D 先画出基区扩散孔的三边; ④由B E D -画出基区引线孔; ⑤由A D 画出基区扩散孔的另一边;

⑥由A D 先画出外延岛的三边; ⑦由C B D -画出集电极接触孔; ⑧由A D 画出外延岛的另一边; ⑨由I d 画出隔离槽的四周; ⑩验证所画晶体管的CS r 是否满足V V OL 4.0≤的条件,若不满足,则要对所作 的图进行修正,直至满足V V OL 4.0≤的条件。(CS C OL r I V V 00 ES += 及己知 V V C 05.00ES =) 第3章 集成电路中的无源元件 复 习 思 考 题 3.3 设计一个4k Ω的基区扩散电阻及其版图。 试求: (1) 可取的电阻最小线宽min R W =?你取多少? 答:12μm (2) 粗估一下电阻长度,根据隔离框面积该电阻至少要几个弯头? 答:一个弯头 第4章 晶体管 (TTL)电路 复 习 思 考 题 4.4 某个TTL 与非门的输出低电平测试结果为 OL V =1V 。试问这个器件合格吗?上 机使用时有什么问题? 答:不合格。 4.5 试分析图题4.5所示STTL 电路在导通态和截止态时各节点的电压和电流,假定各管的 β=20, BEF V 和一般NPN 管相同, BCF V =0.55V , CES V =0.4~0.5V , 1 CES V =0.1~0.2V 。 答:(1)导通态(输出为低电平) V V B 1.21= , V V B 55.12= ,V V B 2.13= ,V V B 5.04= ,V V B 8.05= ,

上海交大网络第五次作业and答案

题目1 未回答 满分1.00 标记题目 题干 要在IE中返回上一页,应该()。 选择一项: a. 按F4键 b. 单击“后退”按钮 c. 按Ctrl+D键 d. 按Delete 键 反馈 正确答案是:单击“后退”按钮 题目2 未回答 满分1.00 标记题目 题干 下面关于电子邮箱的使用说法不正确的是()。 选择一项: a. 可以通过网站来收发邮件,也可以通过Outlook和Foxmail等软件来收发邮件 b. 使用电子邮箱的附件可以发送附加文件、图片资料等 c. 电子邮件地址的结构为:用户帐号后置该用户所连接主机的邮箱地址,如 d. 进行收发电子邮件之前必须先要申请一个电子邮箱地址 反馈 正确答案是:电子邮件地址的结构为:用户帐号后置该用户所连接主机的邮箱地址,如题目3 未回答 满分1.00 标记题目 题干 在Internet上收发E-mail的协议不包括()。 选择一项: a. IMAP b. SMTP c. ARP d. POP3 反馈 正确答案是:ARP 题目4 未回答 满分1.00 标记题目 题干

下面关于搜索引擎的说法,不正确的是()。 选择一项: a. D.搜索引擎主要任务包括信息搜集、信息处理、信息查询三部分 b. A.搜索引擎既是用于检索的软件又是提供查询、检索的网站 c. B.搜索引擎按其工作方式分为两类:全文搜索引擎和基于关键词的搜索引擎 d. C.现在很多搜索引擎提供网页快照的功能,当这个网页被删除或链接失效时,用户仍可使用网页快照来查看这个网页的主要内容 反馈 正确答案是:B.搜索引擎按其工作方式分为两类:全文搜索引擎和基于关键词的搜索引擎题目5 未回答 满分1.00 标记题目 题干 要在IE中停止下载网页,请按()。 选择一项: a. Ctrl+W键 b. Esc键 c. Delete键 d. BackSpace键 反馈 正确答案是:Esc键 题目6 未回答 满分1.00 标记题目 题干 如果想在Internet 上搜索有关Detroit Pistons(底特律活塞)篮球队方面的信息,用()关键词可能最终有效。 选择一项: a. Sports(体育) b. Detroit pistons c. “Detroit Pistons” d. basketball(篮球) 反馈 正确答案是:“Detroit Pistons” 题目7 未回答 满分1.00 标记题目 题干 要打开IE窗口,可以双击桌面上的图标()。 选择一项: a. 我的电脑

1篇3章习题解答浙大版集成电路课后答案

第三章场效应晶体管及其电路分析 题1.3.1绝缘栅场效应管漏极特性曲线如图题1.3.1(a)~(d)所示。 (1)说明图(a)~(d)曲线对应何种类型的场效应管。 (2)根据图中曲线粗略地估计:开启电压V T、夹断电压V P和饱和漏极电流I DSS或I DO 的数值。 图题1.3.1 解:图(a):增强型N沟道MOS管,V GS(th)≈3V,I DO≈3mA; 图(b):增强型P沟道MOS管,V GS(th)≈-2V,I DO≈2mA; 图(c):耗尽型型P沟道MOS管,V GS(off)≈2V,I DSS≈2mA; 图(d):耗尽型型N沟道MOS管,V GS(off)≈-3V,I DSS≈3mA。 题1.3.2 场效应管漏极特性曲线同图题1.3.1(a)~(d)所示。分别画出各种管子对应的转移特性曲线i D=f(v GS)。 解:在漏极特性上某一V DS下作一直线,该直线与每条输出特性的交点决定了V GS和I D的大小,逐点作出,连接成曲线,就是管子的转移特性了,分别如图1.3.2所示。 图1.3.2 题1.3.3 图题1.3.3所示为场效应管的转移特性曲线。试问:

图题1.3.3 (1) I DSS 、V P 值为多大? (2) 根据给定曲线,估算当i D =1.5mA 和i D =3.9mA 时,g m 约为多少? (3) 根据g m 的定义:GS D m dv di g ,计算v GS = -1V 和v GS = -3V 时相对应的g m 值。 解: (1) I DSS =5.5mA ,V GS(off)=-5V ; (2) I D =1.5mA 时,g m ≈0.88ms ,I D =3.9mA 时,g m ≈1.76ms ; (3) v GS =-1V 时,g m ≈0.88ms ,v GS =-3V 时,g m ≈1.76ms 。 题1.3.4 由晶体管特性图示仪测得场效应管T 1和T 2各具有图题1.3.4的(a )和(b )所示的输出 特性曲线,试判断它们的类型,并粗略地估计V P 或V T 值,以及v DS =5V 时的I DSS 或 I DO 值。 图题1.3.4 解: 图(a):耗尽型PMOS 管,V GS(off)=3V ;当V DS =5V 时,I DSS =2mA ; 图(b):增强型PMOS 管,V GS(th)=-4V ;当V DS =5V 时,I DO ≈1.8mA 。 题1.3.5 某MOS 场效应的漏极特性如图题1.3.5所示。试画出v DS =9V 时的转移特性曲线,并定性分析跨导g m 与I D 的关系。 图题1.3.5

集成电路设计练习题

集成电路设计练习题2009 1、说明一个半导体集成电路成本的组成。 2、简述CMOS 工艺流程。简述CMOS 集成电路制造的过程中需要重复进行的工艺步骤。 3、描述你对集成电路工艺的认识。列举几种集成电路典型工艺。工艺上常提到0.25,0.18 指的是什么?简述CMOS 工艺技术的发展趋势。 4、你知道的集成电路设计的表达方式有哪几种? 5、现有一用户需要一种集成电路产品,要求该产品能够实现如下功能:y=lnx其中,x为4位二进制整数输入信号。y 为二进制小数输出,要求保留两位小数。电源电压为3~5v 假设公司接到该项目后,交由你来负责该产品的设计,试讨论该产品的设计全程。 6、请谈谈对一个系统设计的总体思路。针对这个思路,你觉得应该具备哪些方面的知识? 7、描述你对集成电路设计流程的认识。 8、集成电路前端设计流程,后端设计流程,相关的工具。 9、从RTL synthesis 到tape out 之间的设计flow ,并列出其中各步使用的tool. 10、简述FPGA 等可编程逻辑器件设计流程。 11、简述半定制数字电路的设计流程。 12、简要说明并比较数字集成电路几种不同的实现方法。 13、什么是集成电路的设计规则。 14、同步电路和异步电路的区别是什么? 15、画出CMOS 电路的晶体管级电路图,实现Y=AB+C(D+E) 16、在CMOS电路中,要有一个单管作为开关管精确传递模拟低电平,这个单管你会用P管还是N 管,为什么? 17、硅栅COMS工艺中N阱中做的是P管还是N管,N阱的阱电位的连接有什么要求? 18、名词解释:VLSI, CMOS, EDA, VHDL, DRC, LVS, DFT, STA

《数字集成电路》期末试卷(含答案)

浙江工业大学 / 学年第一学期 《数字电路和数字逻辑》期终考试试卷 A 姓名 学号 班级 任课教师 一、填空题(本大题共10小题,每空格1分,共10分) 请在每小题的空格中填上正确答案。错填、不填均无分。 1.十进制数(68)10对应的二进制数等于 ; 2.描述组合逻辑电路逻辑功能的方法有真值表、逻辑函数、卡诺图、逻辑电路图、波形图和硬件描述语言(HDL )法等,其中 描述法是基础且最直接。 3.1 A ⊕可以简化为 。 4.图1所示逻辑电路对应的逻辑函数L 等于 。 A B L ≥1 & C Y C 图1 图2 5.如图2所示,当输入C 是(高电平,低电平) 时,AB Y =。 6.两输入端TTL 与非门的输出逻辑函数AB Z =,当A =B =1时,输出低电平且V Z =0.3V ,当该与非门加上负载后,输出电压将(增大,减小) 。 7.Moore 型时序电路和Mealy 型时序电路相比, 型电路的抗干扰能力更强。 8.与同步时序电路相比,异步时序电路的最大缺陷是会产生 状态。 9.JK 触发器的功能有置0、置1、保持和 。 10.现有容量为210×4位的SRAM2114,若要将其容量扩展成211×8位,则需要 片这样 的RAM 。 二、选择题(本大题共10小题,每小题2分,共20分) 在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。错选、多选或未选均无分。 11.十进制数(172)10对应的8421BCD 编码是 。 【 】 A .(1111010)8421BCD B .(10111010)8421BCD C .(000101110010)8421BC D D .(101110010)8421BCD 12.逻辑函数AC B A C B A Z +=),,(包含 个最小项。 【 】

北京中医药大学远程教育《马克思主义基本原理概论》第5次作业答案

北京中医药大学远程教育《马克思主义基本原理概论》第5次作业答案

《马克思主义基本原理概论》第5次作业 您本学期选择了“马克思主义基本原理概论” 说明:本次作业的知识点为:第二部分(53--104题),总分为52分,您的得分为52分 A型题: 请从备选答案中选取一个最佳答案 1. 资本主义经济危机的实质是()[1分] A.生产严重不足 B.消费严重不足 C.生产相对过剩 D.消费严重超前 2. 资本积累的重要源泉是[1分] A.扩大再生产 B.简单再生产 C.剩余价值 D.资本集中 3. 下列关于纸币的说法中不正确的是()[1分] A.纸币是由国家发行并强制流通的价值符号 B.纸币代表贵金属执行流通手段职能 C.纸币流通也要遵循货币流通规律 D.纸币流通必然导致通货膨胀

9. 资本主义工资的本质是( ) [1分] A.劳动者的全部劳动报酬 B.劳动者创造的全部价值 C.劳动的价值或价格 D.劳动力的价值或价格 10. 能够划分为固定资本和流动资本形态是( ) [1分] A.商品资本 B.货币资本 C.生产资本 D.银行资本 11. 资本主义扩大再生产的基本实现条件是[1分] A.I(c+v+m)=I[v+ ⊿v +(m/x)]+II(v+⊿v十m) B.II (c十v十m)=I(c十⊿c)十II (c十⊿c) C.I[v+⊿v+(m/x)]=II(c+⊿c) D.II [v+⊿v+(m/x) ]=I(c+⊿c) 12. 在货币和资本的关系上,正确的论断是()[1分] A.货币本身就是资本

B.任何数量的货币都能成为资本 C.凡是用来购买生产资料的货币都是资本 D.只有增殖自身价值的货币才是资本 13. 资本主义经济制度被社会主义经济制度所取代是[1分] A.价值规律作用的结果 B.资本主义平均利润规律作用的结果 C.社会主义基本经济规律作用的结果 D.生产关系一定要适合生产力状况规律作用的结果 14. 绝对剩余价值生产和相对剩余价值生产都是依靠()[1分] A.延长工作日获得的 B.提高劳动生产率获得的 C.减少工人的必要劳动时间获得的 D.增加工人的剩余劳动时间获得的 15. 在资本主义工资形式上,工人的全部劳动都表现为()[1分] A.必要劳动 B.剩余劳动 C.无酬劳动 D.抽象劳动 16. 商品的本质因素是[1分] A.使用价值 B.交换价值 C.价值

集成电路设计习题答案-章 精品

CH1 1.按规模划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律? 晶体管-分立元件-SSI-MSI-LSI-VLSI-ULSI-GSI-SOC。MOORE定律 2.什么是无生产线集成电路设计?列出无生产线集成电路设计的特点和环境。 拥有设计人才和技术,但不拥有生产线。特点:电路设计,工艺制造,封装分立运行。 环境:IC产业生产能力剩余,人们需要更多的功能芯片设计 3.多项目晶圆(MPW)技术的特点是什么?对发展集成电路设计有什么意义? MPW:把几到几十种工艺上兼容的芯片拼装到一个宏芯片上,然后以步行的方式排列到一到多个晶圆上。意义:降低成本。 4.集成电路设计需要哪四个方面的知识? 系统,电路,工具,工艺方面的知识 CH2 1.为什么硅材料在集成电路技术中起着举足轻重的作用? 原材料来源丰富,技术成熟,硅基产品价格低廉 2.GaAs和InP材料各有哪些特点? P10,11 3.怎样的条件下金属与半导体形成欧姆接触?怎样的条件下金属与半导体形成肖特基接触? 接触区半导体重掺杂可实现欧姆接触,金属与掺杂半导体接触形成肖特基接触 4.说出多晶硅在CMOS工艺中的作用。P13 5.列出你知道的异质半导体材料系统。 GaAs/AlGaAs, InP/ InGaAs, Si/SiGe, 6.SOI材料是怎样形成的,有什么特点? SOI绝缘体上硅,可以通过氧隔离或者晶片粘结技术完成。特点:电极与衬底之间寄生电容大大减少,器件速度更快,功率更低 7. 肖特基接触和欧姆型接触各有什么特点? 肖特基接触:阻挡层具有类似PN结的伏安特性。欧姆型接触:载流子可以容易地利用量子遂穿效应相应自由传输。 8. 简述双极型晶体管和MOS晶体管的工作原理。P19,21 CH3 1.写出晶体外延的意义,列出三种外延生长方法,并比较各自的优缺点。 意义:用同质材料形成具有不同掺杂种类及浓度而具有不同性能的晶体层。外延方法:液态生长,气相外延生长,金属有机物气相外延生长 2.写出掩膜在IC制造过程中的作用,比较整版掩膜和单片掩膜的区别,列举三种掩膜的制造方法。P28,29 3.写出光刻的作用,光刻有哪两种曝光方式?作用:把掩膜上的图形转换成晶圆上的器件结构。曝光方式有接触与非接触两种。 4.X射线制版和直接电子束直写技术替代光刻技术有什么优缺点? X 射线(X-ray)具有比可见光短得多的波长,可用来制作更高分辨率的掩膜版。电子束

集成电路作业

1、集成电路制造工艺发展水平的衡量指标是什么? a. 在设计和生产中可达到的最小线宽(或称特征尺寸L)。 b. 所使用的硅晶圆片的直径。 c. DRAM的储存容量。 2、简述电路制造工艺的发展趋势。 a.趋势性的变化越来越明显,速度越来越快。 特征尺寸越来越小,电源电压越来越低,芯片尺寸越来越大,布线层数越来越多,单片上的晶体管数越来越多,I/O引线越来越多,时钟速度越来越快 b.集成电路朝着两个方向发展。 c.从另一个角度来说,进入90年代以来,电子信息类产品的开发明显地出现了两个 特点。 3、简述集成电路产业结构经历的三次重大变革。 第一次变革是以加工制造为主导的初级阶段 a.这一时期半导体制造在IC产业中充当主角。 b.这一时期IC设计和半导体工艺密切相关且主要以人工为主。 第二次变革以Foundry和IC设计公司的崛起为标志 a.集成电路产业的一次大分工。 b.IC产业进入了以客户为导向的阶段。 c.EDA工具的发展,使IC设计工程可以独立于生产工艺。 第三次变革以设计、制造、封装和测试四业分离为标志 a.集成电路产业的又一次大分工。 b.IC产业进入了以竞争为导向的高级阶段。 c.系统设计与IP核设计逐渐开始分工。 4、1个门相当于几个晶体管?以门的数量来划分集成电路有哪些分类? 1个门相当于4个晶体管,等效于一个二输入与非门 a. 小规模集成电路(SSI:Small Scale Integrated Circuit)>1-10个门,基本的与非和或非逻辑。 b. 中规模集成电路(MSI: Middle Scale Integrated Circuit)>1万门以内,含有计数器和逻辑功能块等电路。 c. 大规模集成电路(LSI:Large Scale Integrated Circuit)>几万门,含有更多更大逻辑功能块,如4位CPU等。 d. 超大规模集成电路(VLSI:Very Large Scale Integrated Circuit)>近十万门,如64位CPU等电路。 e. 特大规模集成电路(ULSI:Ultra Large Scale Integrated Circuit)>几百万门以上,如DSP、CPU等电路。 f. 巨大规模集成电路(GSI:Giga Scale Integrated Circuit)>千万门以上,如SoC等电路。 5、集成电路系统设计需具备哪些要素? 人才、工具、库和资金。

集成电路工艺原理试题总体答案

目录 一、填空题(每空1分,共24分) (1) 二、判断题(每小题1.5分,共9分) (1) 三、简答题(每小题4分,共28分) (2) 四、计算题(每小题5分,共10分) (4) 五、综合题(共9分) (5) 一、填空题(每空1分,共24分) 1.制作电阻分压器共需要三次光刻,分别是电阻薄膜层光刻、高层绝缘层光刻和互连金属层光刻。 2.集成电路制作工艺大体上可以分成三类,包括图形转化技术、薄膜制备技术、掺杂技术。 3.晶体中的缺陷包括点缺陷、线缺陷、面缺陷、体缺陷等四种。 4.高纯硅制备过程为氧化硅→粗硅→ 低纯四氯化硅→ 高纯四氯化硅→ 高纯硅。 5.直拉法单晶生长过程包括下种、收颈、放肩、等径生长、收尾等步骤。 6.提拉出合格的单晶硅棒后,还要经过切片、研磨、抛光等工序过程方可制备出符合集成电路制造要求的硅衬底 片。 7.常规的硅材料抛光方式有:机械抛光,化学抛光,机械化学抛光等。 8.热氧化制备SiO2的方法可分为四种,包括干氧氧化、水蒸汽氧化、湿氧氧化、氢氧合成氧化。 9.硅平面工艺中高温氧化生成的非本征无定性二氧化硅对硼、磷、砷(As)、锑(Sb)等元素具有掩蔽作用。 10.在SiO2内和Si- SiO2界面存在有可动离子电荷、氧化层固定电荷、界面陷阱电荷、氧化层陷阱等电荷。 11.制备SiO2的方法有溅射法、真空蒸发法、阳极氧化法、热氧化法、热分解淀积法等。 12.常规平面工艺扩散工序中的恒定表面源扩散过程中,杂质在体内满足余误差函数分布。常规平面工艺扩散工序中的有限表 面源扩散过程中,杂质在体内满足高斯分布函数分布。 13.离子注入在衬底中产生的损伤主要有点缺陷、非晶区、非晶层等三种。 14.离子注入系统结构一般包括离子源、磁分析器、加速管、聚焦和扫描系统、靶室等部分。 15.真空蒸发的蒸发源有电阻加热源、电子束加热源、激光加热源、高频感应加热蒸发源等。 16.真空蒸发设备由三大部分组成,分别是真空系统、蒸发系统、基板及加热系统。 17.自持放电的形式有辉光放电、弧光放电、电晕放电、火花放电。 18.离子对物体表面轰击时可能发生的物理过程有反射、产生二次电子、溅射、注入。 19.溅射镀膜方法有直流溅射、射频溅射、偏压溅射、磁控溅射(反应溅射、离子束溅射)等。 20.常用的溅射镀膜气体是氩气(Ar),射频溅射镀膜的射频频率是13.56MHz。 21.CVD过程中化学反应所需的激活能来源有?热能、等离子体、光能等。 22.根据向衬底输送原子的方式可以把外延分为:气相外延、液相外延、固相外延。 23.硅气相外延的硅源有四氯化硅(SiCl4)、三氯硅烷(SiHCl3)、二氯硅烷(SiH2Cl2)、硅烷(SiH4)等。 24.特大规模集成电路(ULIC)对光刻的基本要求包括高分辨率、高灵敏度的光刻胶、低缺陷、精密的套刻对准、对大尺寸硅片 的加工等五个方面。 25.常规硅集成电路平面制造工艺中光刻工序包括的步骤有涂胶、前烘、曝光、显影、坚膜、腐蚀、 去胶等。 26.光刻中影响甩胶后光刻胶膜厚的因素有溶解度、温度、甩胶时间、转速。 27.控制湿法腐蚀的主要参数有腐蚀液浓度、腐蚀时间、腐蚀液温度、溶液的搅拌方式等。 28.湿法腐蚀Si所用溶液有硝酸-氢氟酸-醋酸(或水)混合液、KOH溶液等,腐蚀SiO2常用的腐蚀剂是HF溶液,腐蚀 Si3N4常用的腐蚀剂是磷酸。 29.湿法腐蚀的特点是选择比高、工艺简单、各向同性、线条宽度难以控制。 30.常规集成电路平面制造工艺主要由光刻、氧化、扩散、刻蚀、离子注入(外延、CVD、PVD)等工 艺手段组成。 31.设计与生产一种最简单的硅双极型PN结隔离结构的集成电路,需要埋层光刻、隔离光刻、基区光刻、发射区光刻、引线区 光刻、反刻铝电极等六次光刻。 32.集成电路中隔离技术有哪些类? 二、判断题(每小题1.5分,共9分) 1.连续固溶体可以是替位式固溶体,也可以是间隙式固溶体(×) 2.管芯在芯片表面上的位置安排应考虑材料的解理方向,而解理向的确定应根据定向切割硅锭时制作出的定位面为依据。(√) 3.当位错线与滑移矢量垂直时,这样的位错称为刃位错,如果位错线与滑移矢量平行,称为螺位错(√) 4.热氧化过程中是硅向二氧化硅外表面运动,在二氧化硅表面与氧化剂反应生成二氧化硅。(×) 5.热氧化生长的SiO2都是四面体结构,有桥键氧、非桥键氧,桥键氧越多结构越致密,SiO2中有离子键成份,氧空位表现为带正

第五次作业参考答案

1、灰口铸铁和白口铸铁在组织和性能上有何区别? (1)组织区别:白口铸铁中的碳全部以渗透碳体(Fe3c)形式存在,断口呈亮白色。灰口铸铁碳大部或全部以自由状态片状石墨存在,断口呈灰色。 (2)性能区别:白口铸铁由于有大量硬而脆的Fe3c,故其硬度高、脆性大、韧性差,很难加工。灰口铸铁因石墨存在,具有良好铸造性能、切削加工性好,减震性、减磨性好。 灰铸铁最适宜制造什么类型和用途的零件毛坯? 根据牌号的不同可分别制造:(1)低负荷和不重要的零件,如防护罩、小手柄、盖板和重锤等;(2)承受中等负荷的零件,如机座、支架、箱体、带轮、轴承座、法兰、泵体、阀体、管路、飞轮和电动机座等;(3)承受较大负荷的重要零件,如机座、床身、齿轮、汽缸、飞轮、齿轮箱、中等压力阀体、汽缸体和汽缸套等;(4)承受高负荷、要求耐磨和高气密性的重要零件,如重型机床床身、压力机床身、高压液压件、活塞环、齿轮和凸轮等。 2、孕育铸铁将如何生产?孕育铸铁有何组织和性能特点? 孕育铸铁生产:在浇注前向铁液中加入少量孕育剂(如硅铁和硅钙合金),形成大量的、高度弥散的难熔质点,成为石墨的结晶核心,促进石墨的形核,得到细珠光体基体和细小均匀分布的片状石墨。这种方法称为孕育处理,孕育处理后得到的铸铁叫做孕育铸铁。 孕育铸铁组织和性能特点:组织是细珠光体基体和细小均匀分布的片状石墨;性能特点:强度和韧性都优于普通灰铸铁,而且孕育处理使得不同壁厚铸件的组织比较均匀,性能基本一致。故孕育铸铁常用来制造力学性能要求较高而截面尺寸变化较大的大型铸件。 3、铸铁石墨化的意义是什么?影响铸铁石墨化的因素有哪些? (1)铸铁石墨化的意义:石墨化可将高硬度、性脆的白口铸铁转化为具有较高强度及其他性能的灰铸铁、球铁、可锻铸铁、蠕墨铸铁。 (2)影响铸铁石墨化的因素: 铸铁的组织取决于石墨化进行的程度,为了获得所需要的组织,关键在于控制石墨化进行的程度。实践证明,铸铁化学成分、铸铁结晶的冷却速度及铁水的过热和静置等诸多因素都影响石墨化和铸铁的显微组织。 4、(1)球墨铸铁是如何获得的? 通过在浇注之前,往铁液中加入少量球化剂(通常为镁、稀土镁合金或含铈的稀土合金)和孕育剂(通常为硅铁),使铁水凝固后形成球状石墨而获得的。 (2)球墨铸铁有何组织和性能特点? 组织:珠光体+球状石墨或铁素体+球状石墨;即P + F少+G球或F + P少+G球 性能:具有优良机械性能,球铁的强度和韧性比其他铸铁高。 (3)说明球墨铸铁在汽车制造中的应用 东风汽车公司采用铸态珠光体球铁制造曲轴,东风汽车公司与南京汽车厂分别用铸态铁素体球铁大量制造汽车底盘零件。 5、对比分析铸钢和球墨铸铁在力学性能、铸造性能、生产成本以及应用上的区别。 铸钢的综合机械性能好于球铁,尤其是抗拉强度和抗冲击性能。但球墨铸铁具有更高的屈服强度和较好的疲劳强度,其屈服强度最低为40k,而铸钢的屈服强度只有36k。球墨铸铁的耐腐蚀性和抗氧化性都超过铸钢。由于球墨铸铁的球状石墨微观结构,在减弱振动能力方面,球墨铸铁优于铸钢;球墨铸铁铸造性能好于铸钢;球墨铸铁比铸钢生产成本低。 球墨铸铁以其优良的性能,在使用中有时可以代替昂贵的铸钢,在机械制造工业中得到广泛应用,甚至能代替锻钢做成曲轴,齿轮等重要零件,抗蚀性能也优于普通铸钢,通常做阀门、减压阀。但在重型机械中用于制造承受大负荷的零件,如轧钢机机架、水压机底座等;在铁路车辆上用于制造受力大又承受冲击的零件如摇枕、侧架、车轮和车钩等,建议使用铸

数电期末试卷及答案(共4套)

XX大学信息院《数字电子技术基础》 期终考试试题(110分钟)(第一套) 一、填空题:(每空1分,共15分) 1.逻辑函数Y AB C =+的两种标准形式分别为()、 ()。 2.将2004个“1”异或起来得到的结果是()。 3.半导体存储器的结构主要包含三个部分,分别是()、()、()。 4.8位D/A转换器当输入数字量10000000为5v。若只有最低位为高电平,则输出电压为()v;当输入为10001000,则输出电压为()v。 5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。 6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。 二、根据要求作题:(共15分) 1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。 2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。 三、分析图3所示电路:(10分) 1)试写出8选1数据选择器的输出函数式; 2)画出A2、A1、A0从000~111连续变化时,Y的波形图; 3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。(15分) 五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。(8分) B C 六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。 (6分) 七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。ROM 中的数据见表1所示。试画出在CP信号连续作用下的D3、D2、D1、D0输出的电压波形,并说明它们和CP信号频率之比。(16分) 表1:

医古文第五次作业及其答案

A型题: 1.在“不谋而遐迩自同,勿约而幽明斯契”中,“契”之义为:符合 2.在“文字昭晰,义理环周”中,“环周”之义为:完备周密 3.在“幸遇真经,式为龟镜”中,“龟镜”喻:养生之借鉴 4.以下不含有与“命世奇杰”中“命”义相同的词的是:含灵之所保曰命 5.在“施行不易,披会亦难”中,“披”之义为:翻阅 6.在“传万祀而无昧,悬百王而不朽”中,“悬”之义为:传布 7.以下不是“岁月既淹”中“淹”的反义词的是:长久 8.在“幸遇真经,式为龟镜”中,“式”之义为:用 9.在“稽其言有征,验之事不忒”中,“忒”之义为:差错 10.在“寻注会经,开发童蒙”中,“童蒙”之义为:初次学医的人 11.以下除……之外,都不能用以比喻技术精熟,运用自如:目牛无全 12.在“蒇谋虽属乎生知”中,“蒇谋”之义为:完备的见解 13.在“兼旧藏之卷,合八十一篇二十四卷,勒成一部”中,“勒”之义为:汇总 14.在“俾工徒勿误,学者惟明”中,“工徒”之义为:.医生 15.在“恐散于末学,绝彼师资”中,“师资”之义为:教学的依据 16.在“不谋而遐迩自同”中,与“遐迩”义通的是:交赊 B型题: 1.“同死生之域”中“同”的活用类型是:形容词意动用法 2.“乃燔灭文章,以愚黔首”中“愚”的活用类型是:形容词使动用法 3.“有如列宿高悬,奎张不乱”中“宿”的用法是:名词,星宿 4.“余宿尚方术,请事斯语”中“宿”的用法是:.副词,向来 5.“盖教之著矣,亦天之假也”中“假”的用法是:动词,借助 6.“假若天机迅发”中“假”的用法是:假设连词,假如 7.“委付凡医”中的“委付”属于:同义复词 8.“告穷归天,束手受败”中的“归天”属于:同形词语 9. “庶以网罗今古”中的“网罗”属于:同义复词 10.“或两论并吞,而都为一目”中的“并吞”属于:同义复词 11.“不刊之书也”中的“不刊”属于:同形词语 12.“询谋得失,深遂夙心”中的“得失”属于:偏义复词 13.“今其技术晻昧”中的“晻”属于:异体字 14.“多闻博识,知之次也”中的“知”属于:古今字 15.“犹慈石取铁”中的“慈”属于:通假字 16.“兼《灵枢》九卷,迺其数焉”中的“迺”属于:异体字 17.“并平脉辨证”中的“平”属于:.通假字 18.“大济蒸人”中的“蒸”属于:.通假字 19.“孔安国序《尚书》”中“序”的活用类型是:为动用法 20.“或识契真要,则目牛无全”中“目”的活用类型是:名词用作动词 21.“自非才高识妙,岂能探其理致哉”中“识”的用法是:名词,见解 22.“谨拟一法,略效丹溪,未识如何”中“识”的用法是:动词,知道 23.“蒇谋虽属乎生知”中“属”的用法是:动词,归属 24.“至道流行,徽音累属”中“属”的用法是:动词,连接 25.“惟名利是务”的特殊语序是:强调句宾语前置 26.“下此以往,未之闻也”的特殊语序是:否定句宾语前置