基于CPLDFPGA的半整数分频器的设计

基于CP LD/FPG A 的半整数分频器的设计

夏继军

(黄冈职业技术学院 湖北 黄冈 438002)

摘 要:本文以分频比为2.5的半整数分频器的设计为例,介绍了在M AX +plus II 开发软件下,利用VH D L 硬件描述语言以及原理图的输入方式来实现半整数分频器的过程和方法。

关键词:VH D L ;CP LD/FPG A ;半整数分频;仿真

中图分类号:TP331.1 文献标识码:A 文章编号:1672-1047(2005)04-0081-03

The Design of Semi -integer Frequency Divider B ased on CPLD/FPGA

Xia Ji -jun

(Huanggang Polytechnice Huangzhou Hubei 438002)

Abstract :This paper takes the design of semi -integer frequency divider at the rate of 2.5as an example.It introduces the procedures and methods of semi -integer frequency divider in M AX +plus ,using VH D L and the input ways of the principle chart.

K ey w ords :Vhdl ;C pld/F pag ;Semi -integer frequency divider ;Emulation

1 引言

随着半导体技术的发展,可编程逻辑器件在结构、工艺、集成度、功能、速度和灵活性等方面有了很大的改进和提高,从而为高效率、高质量、灵活地设计数字系统提供了可靠性。CP LD 或FPG A 技术的出现,为DSP 系统的设计又提供了一种崭新的方法。在数字逻辑电路设计中,分频器是一种基本电路。通常用来对某个给定频率进行分频,以得到所需的频率。整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编程逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,比如:时钟源信号为50MH z ,而电路中需要产生一个20MH z 的时钟信号,其分频比为2.5,此时整数分频将不能胜任。为了解决这一问题,可以利用VH D

L 硬件描述语言和原理图输入方式,通过M AX +plus II 开发软件和A L 2TER A 公司的F LEX 系列FPG A 方便地完成了半整数分频器电路的设计。

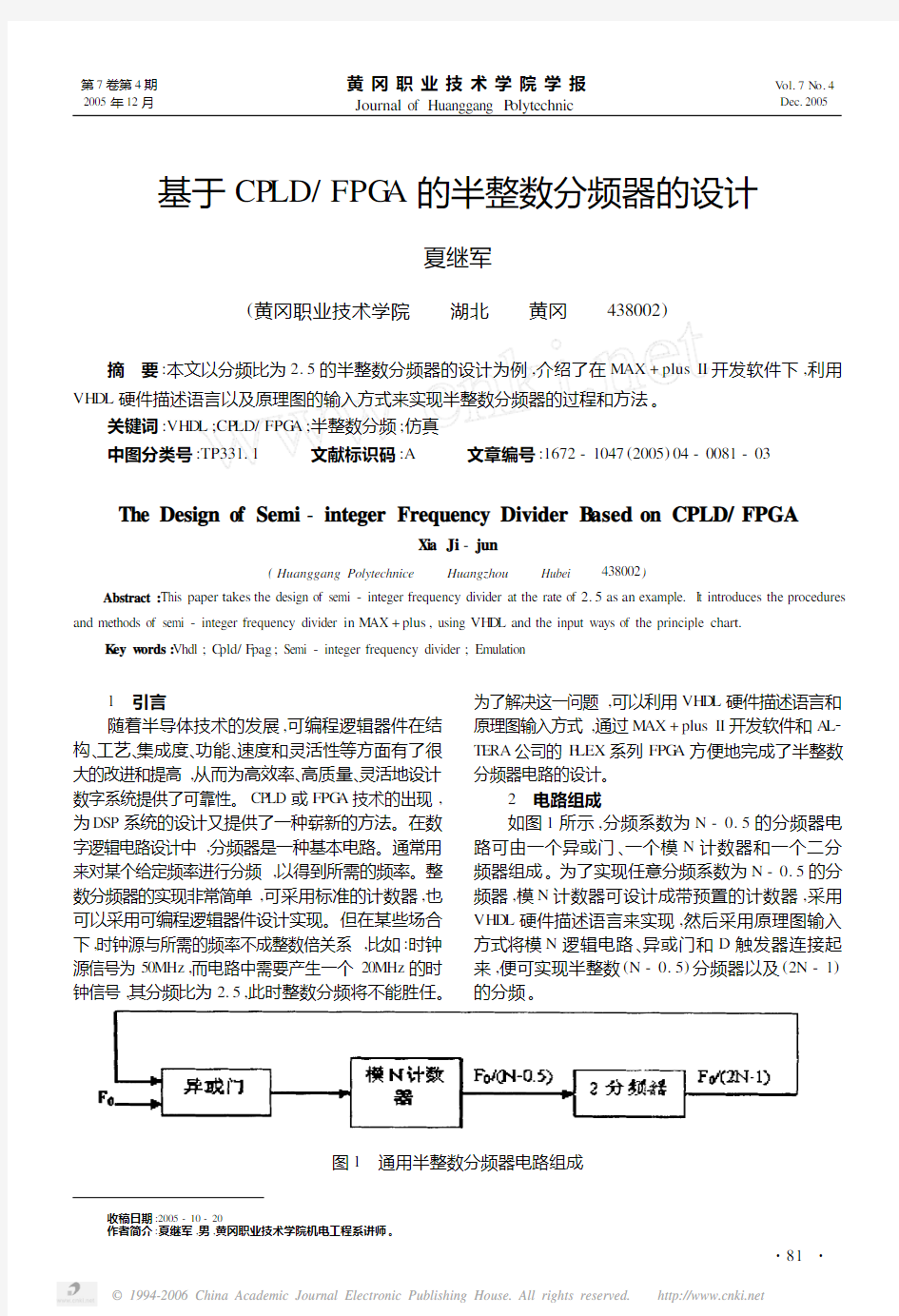

2 电路组成

如图1所示,分频系数为N -0.5的分频器电路可由一个异或门、一个模N 计数器和一个二分频器组成。为了实现任意分频系数为N -0.5的分频器,模N 计数器可设计成带预置的计数器,采用VH D L 硬件描述语言来实现,然后采用原理图输入方式将模N 逻辑电路、异或门和D 触发器连接起来,便可实现半整数(N -0.5)分频器以及(2N -1)的分频。

图1 通用半整数分频器电路组成

?

18?第7卷第4期2005年12月

黄冈职业技术学院学报Journal of Huanggang P olytechnic

V ol.7N o.4

Dec.2005

收稿日期:2005-10-20

作者简介:夏继军,男,黄冈职业技术学院机电工程系讲师。

3 半整数分频器设计

下面通过设计一个分频系数为2.5的分频器给出用FPG A 设计半整数分频器的一般方法。该2.5分频器由模3计数器、异或门和D 触发器组

成。

首先利用VH D L 硬件描述语言实现模3计数器。该计数器可产生一个分频系数为3的分频器,并产生一个默认的逻辑符号C OUNTER3。其输入端口为RESET 、E N 和C LK;输出端口为QA 和QB 。下面给出模3计数器VH D L 描述代码:

library ieee ;

use ieee.std -logic -1164.all ;use ieee.std -logic -unsigned.all ;entity counter3is

port (

clk ,reset ,en :in std -logic

;qa ,qb :out std -logic );end counter3;

architecture behavior of counter3is

signal count :std -logic -vector (1downto 0);begin

process (reset ,clk )begin

if reset =’1’then

count (1downto 0)<=”00”;else

if (clk ’event and clk =’1’)then if (en =’1’)then if (count =”10”)then count <=”00”;else

count <=count +1;end if ;end if ;end if ;end if ;end process ;qa <=count (0);qb <=count (1);end behavior ;

任意模数的计数器与模3计数器的描述结构完全相同,所不同的仅仅是计数器的状态数。上面的程序经编译、时序模拟后,在M AX +P LUS II 可得到如图2所示的仿真波形。

图2 模3计数器仿真波形

图3 2.5分频器电路原理图

?

28?

以上完成模3计数器的设计,再将C OUNTER3、异或门和D 触发器通过图3所示的电

路逻辑连接关系,并用原理图输入方式调入图形编辑器,然后经逻辑综合即可得到如图4所示的仿真波形。由图中outclk 与inclk 的波形可以看出,out 2

clk 会在inclk 每隔2.5个周期处产生一个上升沿,

从而实现分频系数为2.5的分频器。设inclk 为50MH z ,则outclk 为20MH z 。因此可见,该电路不仅

可得到分频系数为2.5的分频器(outclk ),而且还

可得到分频系数为5的分频器(Q1)

。

图4 2.5分频器仿真波形图

4 结束语

本例中的计数器为2位宽的位矢量,即分频系数为4以内的半整数值。若分频系数大于4,只需增大count 的位宽使用相同的方法便可实现。

参考文献:

[1]贾新章.电子电路C AD 技术基于Orcad9.2[M].西

安:西安电子科技大学出版社,2002.

[2]潘松.VH D L 实用教程[M].成都:电子科技大学出

版社,2000.

[3]童诗白.模拟电子技术基础[M].北京:高等教育出

版社,2001.

[4]辛春艳.VH D L 硬件描述语言[M].北京:国防工业

出版社

,2002.

[责任编辑:张孝忠]

(上接85页)

1)在Visual Basic 的“外接程序”菜单里选择

“可视化数据管理器”,再在“新建”中选择“ODBC ”。

2)打开“ODBC 数据源”来配置数据库,在数据

库名称里填入在S Q L Server 里建的数据库名称。

3)设置登录数据库的方式,这里最主要是要弄

清楚S Q L Server 本身是使用的哪种登录方式,那么就选择哪种登录方式。

但是有时还需在“控制面板”的“ODBC 数据源”里设置。

4.2 利用ADO 连接到S Q L Server 数据库

通过ADODC 属性或者在属性页找到C onnec 2tionString 属性,在数据源连接方式中选择“使用连

接字符串”,单击“生成”,在数据连接属性里找到

“提供者”项,选中“Micros oft O LE DB Provider for S Q L Server ”,然后分别选择或输入服务器名称、输入登

录服务器的信息和在服务器上选择数据库。

总之,Visual Basic 数据库技术的优势,突出地表现在其对数据库的基本操作上,可以方便地与一些主流数据库建立连接,进行数据显示、存取、动态编辑、分类查询、报表生成等操作,其操作技术简洁明了,代码开发效率高,周期短,易于维护和升级。

参考文献:

[1]郑阿奇.Visual Basic 实用教程[M].电子工业出版

社,2001.

[2]段兴.Visual Basic 数据库实用程序设计[M].人民邮

电出版社,2002.

[责任编辑:张孝忠]

?

38?

分频器

第36卷第2期信息化研究Vo l.36 No. 2 2010年2月I nfo r m a t iza t ion R e s ea r ch Feb. 2010 基于FPGA 的任意数值分频器的设计 周殿凤,康素成,王俊华 (盐城师范学院物理科学与电子技术学院,江苏省盐城市224002 ) 摘要:介绍了基于FPG A 的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3 类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL 语言进行了编译并且给出了仿真图。本设计中的分频器没有竞争冒险,可移植性强,占用的FPG A资源少。本设计在A l2 te ra 公司的Cyc l o neⅡ系列EP2C35 型FPG A芯片中完全可实现,结果表明设计是正确和可行的。由于分频器应用非常广泛,故本设计具有很强的实用价值。 关键词: FPG A; VHDL;分频器 中图分类号: TP277 0 引言 FPG A 作为未来数字系统的 3 大基石( FPG A、D SP、CPU ) 之一, 成为目前硬件设计研究的重点[ 1 ] 。 在数字系统的设计中,设计人员会遇到各种形式的分频需求,如偶数分频、奇数分频、半整数分频、小数分频率的1 / 10。从图1可看出当j = 5 = m/ 2时输出时钟占空比为50 %。 图110分频器波形图 和分数分频等。在某些设计中,系统不仅对频率有要求,而且对占空比也有严格的要求。由计数器或计数器的级联构成各种形式的偶数分频及非等占空比的奇数分频实现起来较为简单, 但对半整数分频及等占空比的奇数分频实现较为困难,小数分频和分数分频更 占空比为50 %的奇数分频实现起来较为困难,实现的方法较多,文中介绍了一种占用资源较少的方法。假设要实现占空比为50 %的m = 2 n+ 1 分频, 选择两个2 n+ 1进制计数器控制两个中间时钟c lk1 和c l k2 , 1 号计数器在输入时钟c l k的上升沿计数, 2 号在c l k 的 困难[ 2 ] 。为了解决这一问题,本文首先分析了各种分下降沿计数。当计数器1 输出为0 ~n - 1 时c l k1 为 频器的设计方法,然后将其综合起来成为一个通用分频器。通过分析分频器的原理,探索出了一套简单明了的设计方法,设计了一个任意数值通用分频器,该分频器没有毛刺且占用的逻辑资源较少。 1 整数分频器 偶数分频器的设计较为简单,可以利用计数器实1 ,输出为n ~2 n 时c l k1为0 且计数器1 输出为 2 n时计数器1清0 , 如此循环下去; 当计数器2输出为0 ~n - 1 时c l k2为1 ,输出为n ~2 n 时c l k2为0且计数器2输出为 2 n时计数器 2 清0 ,如此循环下去。可见2种计数器实现方法一样,只是翻转的边沿不一样,最终输出的时钟c l kou t = c l k1 + c l k2。占空比为50 %的奇数分频仿真图见图2 ,图中m = 9 ,因此是9 分频电路, 现[ 3 ] 。假设要实现m = 2 n分频, 当计数器的值为0 ~通过预置值m 可以非常方便的对分频系数进行设置 j - 1时,输出时钟为 1 ,计数器的值为j~2 n- 1 时,输出时钟为0 ,在计数器值为2 n - 1 时复位计数器,如此循环下去,即可实现占空比为j/2 n的分频, m 和j都是预置数, j用于调节占空比, m 调节分频系数。m 的值不同,分频系数也就不同, 如果预置数m 是奇数则可实现占空比不等于50 %的奇数分频。图1 中m 取值10,故实现的是10 分频, 输出时钟频率是输入时钟频收稿日期: 2009212 220; 修回日期: 2010201 209。 基金项目:江苏省高校自然科学基金资助项目( 08KJD140005) ;盐城师范学院校级基金资助项目( 09YCK L 016) 。而不需要重新编程。 图29分频器波形图 2小数分频器 小数分频器是通过可变分频和多次平均的方法得到的[ 4 25 ] 。假设要进行m . n分频( m 、n都是整数, 且n < 10 ),因为只有一位小数,所以总共要进行1 0次分 ·59·

分频器设计实验报告

竭诚为您提供优质文档/双击可除分频器设计实验报告 篇一:n分频器分析与设计 一、实验目的 掌握74190/74191计数器的功能,设计可编程计数器和n分频器,设计(n-1/2)计数器、分频器。 二、实验原理 分频是对输入信号频率分频。1、cD4017逻辑功能 2、74190/74191逻辑功能 3、集成计数器级联 当所需计数器模数超过所选计数器最大计数状态时,需要采取多片计数器级联。方法分为异步级联和同步级联。4、集成计数器的编程 在集成计数器的时序基础上,外加逻辑门电路等,反馈集成计数器的附加功能端,达到改变计数器时序的目的。可采用复位编程和置数编程两种。5、多片74190/74191计数器级联 可根据具体计数需求和增减需求,选用74190或74191,

选择不同功能、同步或异步设计等。 6、74190/74191计数器编程 由于没有复位端,因此只能使用置数编程,置数端置为0即可异步置数。可根据需求设计n进制加法或减法计数器。 n与译码逻辑功能如下。 7、74191组成(n-1/2)分频器电路如下图: u3 计数器的两个循环中,一个循环在cp的上升沿翻转;另一个是在cp的下降沿翻转,使计数器的进制减少1/2,达到(n-1/2)分频。 三、实验仪器 1、直流稳压电源1台 2、信号发生器1台 3、数字万用表1台 4、实验箱1台 5、示波器1台 四、仿真过程 1、按照cD4017和74191功能表验证其功能。 2、74191组成可编程计数器 (1)构成8421bcD十进制加法计数器,通过实验验证正确性,列出时序表。设计图如下 仿真波形如下 (2)构成8421bcD十进制减法计数器,通过实验验证正确性,列出时序表。设计图如下: 仿真波形如下

基于VHDL的全数字分数分频器设计

第6卷第12期2006年6月1671—1815f2006112—1609—04科学技术与工程 ScienceTechnologyandEngineering V01.6No.12Jun.2006 ⑥2006 Sci.Tech.Engng. 通信技术 基于VHDL的全数字分数分频器设计 尹辉炳张涛 (中国科学院上海技术物理研究所.上海200083) 摘要介绍了,全数字化的分数分频器的两种设计方法.分析了它们的特点.然后采用VHDL硬件描述语言设计了全数字化的分数分频器,并且给出了设计任意分数分频器的方法。 关键词VHDLFPGA/CPI.D分数分频器 中图法分类号TN742.1:艾献标识码A 在数字电路设计中.经常需要用到分频电路。一般的整数分频器可以很容易地通过D触发器或者模Ⅳ计数器来实现。但是.有时候电路中需要用到各种不同的频率.而时钟源通常只有有限的一两个.这时候就会碰到需要分数分频的情况。文献『1,2]中给出了一种实现半整数分频器的方法.这里通过对该电路进行建模和分析,对其进行扩展.得到更为一般的形式,使其能实现(N一1/M)分频。另外,根据文献fI1中分数分频的基本原理,设计了一种通用分数分频器.并且给出了确定分数分频器参数的方法。最后对这两种分数分频器进行了比较说明。 1(Ⅳ_1肋)型分频器设计 1.1基本原理 文献『1,2]中给出了一种半整数分频器,其电路组成如图1所示,由一个异或门,一个模Ⅳ计数器,以及一个2分频器组成。 图1半整数分频器电路组成 2006年1月16日收到 第一作者简介:尹辉炳(1980一),男,江苏丹阳人,中国科学院上海技术物理研究所硕十研究生,研究方向:红外信号与信息处理。其慨。=志≯。^=寿。 网23.5分频器仿真波j髟 采用VHDL语言设计上述电路(令N=4).并进行仿真得到波形如图2所示.图中clkin为输入波形.比锨五和clk—in可以得出:勘的每个周期中f.kgclk.in少一个正脉冲。但是.观察模Ⅳ计数器输出temp.就可以发现,实际上在矗的每个周期中£是ELelkin多了一个正脉冲j分析如下:没此时刻为图中五的第一个高电平下降沿前一刻,^=1,然后clkin由1变为0,导致异或门的输出£变为1,£的上升沿使模Ⅳ(模4)计数器计数.计数器结果加1。由于计数器计到了最大值,故clkout输出高电平1.elkout的上升沿又促使2分频器工作,使磊由1变为0,然后兀反馈回异或门得输人端,与cklin通过异或门使7:变为0.反馈使得‘由0变为1.以后经过一段时问又返回0。 根据上面的分析.可以将异或门看作是频率加法器.于是可以得到半整数分频器如下的数学模型 框图(图3)。

小数分频器原理

基于CPLD/FPGA的半整数分频器的设计 在数字逻辑电路设计中,分频器是一种基本电路。通常用来对某个给定频率进行分频,以得到所需的频率。整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编程逻辑器件设计实现。但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。比如:分频系数为2.5、3.5、7.5等半整数分频器。笔者在模拟设计频率计脉冲信号时,就用了半整数分频器这样的电路。由于时钟源信号为50MHz,而电路中需要产生一个20MHz的时钟信号,其分频比为2.5,因此整数分频将不能胜任。为了解决这一问题,笔者利用VIDL硬件描述语言和原理图输入方式,通过MAX+plus II开发软件和ALTERA公司的FLEX系列EPF10K10LC84-4型FPGA方便地完成了半整数分频器电路的设计。 2 小数分频的基本原理 小数分频的基本原理是采用脉冲吞吐计数器和锁相环技术先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。如设计一个分频系数为10.1的分频器时,可以将分频器设计成9次10分频,1次11分频,这样总的分频值为: F=(9×10+1×11)/(9+1)=10.1 从这种实现方法的特点可以看出,由于分频器的分频值不断改变,因此分频后得到的信号抖动较大。当分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,以使输出成为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。 3 电路组成 分频系数为N-0.5的分频器电路可由一个异或门、一个模N计数器和一个二分频器组成。在实现时,模N计数器可设计成带预置的计数器,这样可以实现任意分频系数为N-0.5的分频器。图1给出了通用半整数分频器的电路组成。

基于VHDL数控分频器设计

目录 一、设计任务与要求 (3) 二、总体框图 (3) 三、选择器件 (4) 四、功能 (5) 1、数控分频器 (5) 2、BCD译码器 (6) 3、扫描器 (11) 4、3-8译码器 (13) 5、7段数码管显示译码器 (16) 五、总体设计电路图 (19) 1总体(顶层)电路原理图 (19) 2仿真结果 (19) 3管脚分配图 (20) 4.硬件连接情况 (20) 六.心得体会 (20)

数控分频器设计 一、设计任务与要求 数控分频器的功能就是当输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,以实现所需的输出频率。 基本功能: 1、实现8位分频器,依据输入的8位2进制数的不同,有不同的分频比。如输入10010000,即对输入的时钟信号进行144分频,如输入01001000,即对输入的时钟信号进行72 分频。 2、输出的波形应为占空比位50%的方波。 3、有显示功能,显示当前的分频比,即,输入的二进制数的大小。 总体框图 设计思路:数控分频器用计数值可并行预置的加法器设计完成,当在输入端给定不同输入数据时将对输入的时钟信号有不同的分频比。把输入端输入的八位二进

制数直接通过BCD译码器转换为十位BCD码表示的十进制数,通过扫描器对3个数码管进行选通扫描,最后7段数码管显示译码器对选中数码管的赋值进行译码,并驱动数码管显示该数据。 模块的功能: 1、数控分频器:实现8位分频器,依据输入的8位2进制数的不同,有不同的分频比。如输入10010000,即对输入的时钟信号进行144分频。 2、BCD译码器:把输入端的8位2进制数转换成10位BCD码表示的十进制数。 3、扫描器:when “000”=>daout<=dout(3 downto 0); when “001”=>daout<=dout(7 downto 4); when “010”=>daout<=dout(3 downto 2)<="00"; daout(1 downto 0)<=dout(9 downto 8); when others=>null; 4、3-8译码器:当sel=0时,q=11111110;选择个位数码管亮。 当sel=1时,q=11111101;选择十位数码管亮。 当sel=2时,q=11111011;选择百位数码管亮。 5、7段数码管显示译码器:把BCD码表示的十进制数转换成驱动数码管显示的段信号,使数码管显示数字。 三、选择器件 1、装有QuartusII软件的计算机一台。 2、芯片:使用altera公司生产的Cyclone系列芯片,如EP1C12Q240C8芯片 。 此次设计实验采用ALTERA公司的cyclone系列的FPGA芯片EP1C12,设计和仿真采用ALTERA公司的QUARTUS II软件,EP1C12各项参数参照上表。 Cyclone的性能特性 (1)、新的可编程体系结构,实现低成本设计。

VHDL非整数分频器设计实验报告

非整数分频器设计 一、 输入文件 输入时钟CLK: IN STD_LOGIC 二、 设计思路 1. 方法一:分频比交错 (1) 确定K 值 先根据学号S N 确定M 和N :为了保证同学们的学号都不相同,取学号的后四位,即N S =1763 ()mod 1920(mod 17)0 17mod 17 S S S N N if N then M else M N =+=== 由以上公式,得N=(1763 mod 19)+20=35 M=(1763 mod 17)=12 然后根据下式计算分频比K 的值: 8()9N M M K N -+= = =8.34285714 (2) 确定交错规律 使在35分频的一个循环内,进行12次9分频和23次8分频,这样,输出F_OUT 平均为F_IN 的8.34285714分频。为使分频输出信号的占空比尽可能均匀,8分频和9分频应‘交替’进 (3) 设计框图:要求同步时序设计

(4)代码 在实体内定义两个进程(PROCESS P1和PROCESS P2),一个进程控制输出8/9分频,一个进程控制35分频周期比例输出。控制器输出FS_CTL信号控制输出是8分频还是9分频,分频器输出C_ENB信号来控制35分频计数器计数。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; ENTITY DIV IS--定义实体,实体名DIV PORT(F_IN: IN STD_LOGIC;--输入时钟信号 F_OUT: OUT STD_LOGIC--输出时钟信号 ); END DIV; ARCHITECTURE A OF DIV IS SIGNAL CN1: INTEGER RANGE 0 TO 7;--8分频计数器 SIGNAL CN2: INTEGER RANGE 0 TO 8;--9分频计数器 SIGNAL CN: INTEGER RANGE 0 TO 34;--整体计数器 SIGNAL C_ENB: STD_LOGIC;--整体计数器时钟驱动信号 SIGNAL FS_CTL: STD_LOGIC;--控制8、9分频比例信号,高电平8分频,低电平9分频 BEGIN P1:PROCESS(F_IN)--8、9分频计数进程 BEGIN IF (F_IN'EVENT AND F_IN='1') THEN IF(FS_CTL='0') THEN--9分频 IF CN2=8 THEN--计数 CN2<=0; ELSE CN2<=CN2+1; END IF; IF CN2>4 THEN--控制输出,占空比0.5 F_OUT<='1'; ELSE F_OUT<='0'; END IF; IF CN2=8 THEN--控制整体计数器驱动信号 C_ENB<='1'; ELSE C_ENB<='0'; END IF; ELSE IF CN1=7 THEN--8分频计数,同上 CN1<=0; ELSE CN1<=CN1+1; END IF; IF CN1>3 THEN F_OUT<='1'; ELSE F_OUT<='0'; END IF; IF CN1=7 THEN C_ENB<='1'; ELSE C_ENB<='0'; END IF; END IF; END IF; END PROCESS P1; P2:PROCESS(C_ENB)--整体计数进程 BEGIN IF (C_ENB'EVENT AND C_ENB='1') THEN--由驱动信号驱动 IF CN=34 THEN--计数 CN<=0; ELSE CN<=CN+1; END IF; IF (CN=34 OR CN=2 OR CN=5 OR CN=8 OR CN=11 OR CN=14 OR CN=17 OR CN=20 OR CN=23 OR CN=26 OR CN=29 OR CN=32) THEN FS_CTL<='0'; ELSE FS_CTL<='1'; END IF;--8、9分频比例分配 ELSE CN<=CN; END IF; END PROCESS P2; END A;

课程设计基于FPGA的半整数分频器设计

课程设计报告 设计名称EDA(VHDL)课程设计 专业班级电子0942 姓名姬鹏冲 学号0904451213 成绩评定 电气与信息工程学院 二0一二年一月 课程设计要求和成绩考核办法 (要求和成绩考核办法在封皮背面打印) 1.不允许在教室或实验室内吸烟、吃零食,不准带无关人员到教室或实验室活动,否则扣平时表现分。 2.凡病事假超过3天(每天7小时),或迟到早退三次以上,或旷课两次(1天)以上,不得参加本次考核,按不及格处理,本次课程设计不能通过。 3.病事假必须有请假条,需经班主任或有关领导批准,否则按旷课处理。 4.课程设计的考核由指导教师根据设计表现(出勤、遵守纪律情况等)、设计报告、设计成果、答辩等几个方面,给出各项成绩或权重,综合后给出课程设计总成绩。该设计考核须经教研室主任审核,主管院长审批备案。 5.成绩评定采用五级分制,即优、良、中、及格和不及格。 6.课程设计结束一周内,指导教师提交成绩和设计总结。 7.设计过程考核和成绩在教师手册中要有记载。

实习报告要求 实习报告内容、格式各专业根据实习(设计)类别(技能实习、认识实习、生产实习、毕业实习等)统一规范,经教研室主任审核、主管院长审批备案。 注意: 1.课程设计任务书和指导书在课程设计前发给学生,设计任务书放置在设计报告封面后和正文目录前。 2.为了节省纸张,保护环境,便于保管设计报告,统一采用A4纸,课程设计报告建议双面打印(正文采用宋体五号字)或手写,左侧装订,订两个钉。 基于FPGA的半整数分频器设计 一、系统设计任务及功能概述 本系统是利用VHDL硬件描述语言和原理图输入方式,通过MUX+PLUSⅡ开发软件和ALTER 公司的FLEX系列EPF10K10LC84-4型FPGA方便的完成了半整数分频器电路的设计。本系统是通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。 二、系统设计方案和程序设计 1.系统设计方案 我们采用脉冲吞吐计数器和锁相环技术,先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的5.5分频值。该分频器电路可由一个异或门、一个模6数器和二分频器组成。这样可以实现分频系数为5.5分频器以及11分频。 设计框图如下所示 2.VHDL程序设计 (1)模6计数器VHDL描述设计 该计数器可产生一个分频系数为5.5分频器,并产生一个默认的逻辑符号cont6。其输入端口为rst、en和clk;输出端口为qa,qb,qc。下面给出模6数器的VHDL描述代码:libraryieee; use ieee.std_logic_1164.all; useieee.std_logic_unsigned.all; entity cont6 is port(clk:instd_logic; rst:instd_logic; en:instd_logic; qa,qb,qc:outstd_logic); end entity cont6; architecturewode of cont6 is signalcount:std_logic_vector(2 downto 0); begin process(clk,rst,en)is begin

实验五 数控分频器

实验五数控分频器 一、实验目的 1、学会数控分频器的设计、分析和测试方法; 2、根据仿真结果分析设计的优缺点。 二、实验原理 数控分频器的功能就是当输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY DIV IS PORT(CLK:IN STD_LOGIC; K_OR:OUT STD_LOGIC); END ENTITY DIV; ARCHITECTURE BHV OF DIV IS SIGNAL C1,C2:STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL M1,M2:STD_LOGIC; BEGIN PROCESS(CLK,C1) BEGIN IF RISING_EDGE(CLK) THEN IF (C1="100") THEN C1<="000";ELSE C1<=C1+1;END IF; IF (C1="001") THEN M1<=NOT M1;ELSIF C1="011" THEN M1<=NOT M1; END IF; END IF; END PROCESS ; PROCESS(CLK,C2) BEGIN IF FALLING_EDGE(CLK) THEN IF (C2="100") THEN C2<="000";ELSE C2<=C2+1;END IF; IF (C2="001") THEN M2<=NOT M2;ELSIF C2="011" THEN M2<=NOT M2;

分频器实验

实验一分频器设计 一、实验项目 分频器设计实验:利用QuatusII仿真实现分频器设计。 二、实验仪器及器件 计算机、USB-BLASTER下载线、数字系统实验箱、5V稳压电源。 三、实验目的 1、熟悉教学实验板的使用,初步了解掌握Verilog HDL语言和VHDL语言。 2、掌握分辨器原理,熟悉分频器的功用,学习分频器的设计、掌握用 Verilog HDL 或者VHDL 语言描述分频器的方法。 3、熟悉和掌握FPGA开发软件QuatusII的基本操作,用QuatusII编译Verilog 和VHDL语言。 4、掌握USB-BLASTER下载工具的安装、以及程序下载方法。 5、学会FPGA I/O引脚分配和实现过程。 四、实验要求及内容 1、首先下载给定的VHDL硬件描述语言编写的分频器示例程序,读懂程序, 编译并仔细观察在实验板上的现象。 2、在QuatusII平台上进行波形仿真。 3、扩展内容:设计分频电路得到3分频器、8分频器和32分频器。编写分 频器的Verilog 或VHDL代码,并仿真,同时给出3、8、32分频仿真波 形。 五、实验原理 一个数字系统中往往需要多种频率的时钟脉冲作为驱动源,这样就需要对FPGA的系统时钟(频率较高)进行分频。比如在进行流水灯、数码管动态扫描设计时不能直接使用系统时钟(太快而肉眼无法识别),或者需要进行通信时,由于通信速度不能太高(由不同的标准限定),这样就需要对系统时钟分频以得到较低频率的时钟。 分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的分频需要。 在对时钟要求不是很严格的FPGA系统中,分频通常都是通过计数器的循环计数来实现的。 偶数分频(2N)

数控分频器实验报告

《数控分频实验》 姓名:谭国榕班级:12电子卓越班学号:201241301132 一、实验目的 1.熟练编程VHDL语言程序。 2.设计一个数控分频器。 二、实验原理 本次实验我是采用书上的5分频电路进行修改,通过观察其5分频的规律进而修改成任意奇数分频,再在任意奇数分频的基础上修改为任意偶数分频,本次实验我分为了三个部分,前两部分就是前面所说的任意奇数分频和任意偶数分频,在这个基础上,再用奇数输入的最低位为1,偶数最低位为0的原理实现合并。 三、实验步骤 1.任意奇数分频 程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; ENTITY DIV1 IS PORT(CLK:IN STD_LOGIC; D:IN INTEGER RANGE 0 TO 255; K1,K2,K_OR:OUT STD_LOGIC ); END; ARCHITECTURE BHV OF DIV1 IS SIGNAL TEMP3,TEMP4:STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL M1,M2:STD_LOGIC; --SIGNAL OUT1,OUT2,OUT3:STD_LOGIC; BEGIN PROCESS(CLK,TEMP3) BEGIN IF RISING_EDGE(CLK) THEN IF(TEMP3=D-1) THEN TEMP3<="00000000"; ELSE TEMP3<=TEMP3+1; END IF; IF(TEMP3=D-(D+3)/2) THEN M1<=NOT M1; ELSIF (TEMP3=D-2) THEN M1<=NOT M1; END IF; END IF; END PROCESS; PROCESS(CLK,TEMP4) BEGIN IF FALLING_EDGE(CLK) THEN IF(TEMP4=D-1) THEN TEMP4<="00000000"; ELSE TEMP4<=TEMP4+1; END IF; IF(TEMP4=D-(D+3)/2) THEN M2<=NOT M2; ELSIF (TEMP4=D-2) THEN M2<=NOT M2;

EDA数控分频器的设计报告

数控分频器的设计 1、实验目的: 学习数控分频器的设计、分析和测试方法。 2、实验原理: 数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相接即可,详细设计程序如例下文所示。 1) VHDL及语句分析 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY DVF IS --定义实体DVF PORT ( CLK : IN STD_LOGIC; --时钟输入 D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --7位预置数 FOUT : OUT STD_LOGIC ); --输出的频率 END DVF; ARCHITECTURE one OF DVF IS --定义结构体one SIGNAL FULL : STD_LOGIC; --定义信号full BEGIN P_REG: PROCESS(CLK) --进程P_REG中CNT8从预置数D开始 逐步累加到255后,FULL置1;再将 CNT8置为D,循环以获得一个新的周期 脉冲序列FULL,即产生新的频率V ARIABLE CNT8 : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN IF CLK'EVENT AND CLK = '1' THEN IF CNT8 = "11111111" THEN CNT8 := D; FULL<='1'; ELSE CNT8 := CNT8 + 1; FULL <= '0'; END IF; END IF; END PROCESS P_REG ; P_DIV: PROCESS(FULL) --进程P_DIV中,FOUT是占空比为50%的周期

半整数分频器的设计

22.半整数分频器的设计 一、实验原理: 1小数分频的基本原理 设有一个5 MHz的时钟源,但电路中需要产生一个2 MHz的时钟信号,由于分频比为2.5,因此整数分频器将不能胜任。 采用可编程逻辑器件实现分频系数为2.5的分频器,可采用以下方法:设计一个模3的计数器,再设计一个扣除脉冲电路,加在模3计数器输出之后,每来两个脉冲就扣除一个脉冲(实际上是使被扣除的脉冲变成很窄的脉冲,可由异或门实现),就可以得到分频系数为2.5的小数分频器。采用类似方法,可以设计分频系数为任意半整数的分频器。 小数分频的基本原理为脉冲吞吐计数法:设计两个不同分频比的整数分频器,通过控制单位时间内两种分频比出现的不同次数,从而获得所需的小数分频值。例如设计一个分频系数为10.1的分频器,可以将分频器设计成9次10分频,1次11分频,这样总的分频值为 (9×10+1×11)/(9+1) =10.1 从这种实现方法的特点可以看出,由于分频器的分频值在不断改变,因此分频后得到的信号抖动较大。 当分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,使输出为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。 1.2 电路组成 设需要设计一个分频系数为N-0.5的分频器,其电路可由一个模N计数器、一个二分频器和一个异或门组成,如图1所示。在实现时,模N计数器可设计成带预置的计数器,这样就可以实现任意分频系数为N-0.5的分频器。 二、半整数分频器代码: VHDL程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY deccount IS PORT ( inclk: IN STD_LOGIC; --时钟源 preset: IN STD_LOGIC_VECTOR(3 DOWNTO 0); --预置分频值N outclk1: OUT STD_LOGIC; outclk2: BUFFER STD_LOGIC ); --输出时钟

实验八 数控分频器的设计

实验八数控分频器的设计 1、实验目的 1 学习数控分频器的设计; 2 熟悉VHDL常用语句的意义和使用; 3 练习引脚分配和时序分析。 2、实验内容 1 设计8位数控分频器; 三、实验原理 对于一个N分频器,分频出的时钟周期原时钟周期的N倍,频率是原时钟频率的1/N。 对于一个8位计数器,如果开始预置一个数D,然后启动计数器工作,则经过11111111-D个时钟周期计数器的值又变为11111111,当计数器为该数值时,下一个时钟沿到来之时,又将计数器预置为D,然后开始正常计数。如此通过计数、预置的周期性操作,可以得到一个周期信号(即分频信号),其周期为11111111-D+1,即分频比为R= 11111111-D+1。所以改变D,则可以控制分频比。 数控分频器的VHDL代码见教材P146-147。仿真波形如图8-1所示。 图8-1 数控分频器仿真波形

图8-2 数控分频器芯片引脚分配 三、实验步骤 (一)8位数控分频器的设计 1 建立一个设计工程,工程名为PULSE; 2 打开文本编辑器,建立一个VHDL设计文件,其VHDL代码见教材 P166例6-22,文件名存为PULSE.VHD。注意文件的扩展名要选 为.vhd,而且要求工程名、文件名和设计实体名必须相同。 3 选器件:将器件型号选为; 4 编译; 5 建立波形文件,然后保存,其文件名必须与工程名一致;【波形

设置:①设置仿真时间为500us:②设置输入信号的波形:时钟周期设置为50ns,其他输入信号的波形设置参看图8-1。】 6 仿真,观察输出波形是否正确【参看图8-1中的输出波形】。 7 引脚分配;【将引脚分配到如图8-2所示的位置,然后再编译。 编译通过才算成功】 8 时序分析:分析芯片所能达到的最高时钟频率。【打开时序分析器,然后执行菜单命令:analysis/register performance /start】 五、思考题 1 按本实验所示的方法进行分频,输出的分频信号FULL和FOUT是奇数分频还是偶数分频?分别说明之。 2 将本实验的8位数控分频器扩展为16位分频器; 3 在本实验的设计基础上,如果设置2个预置数D和D1,则可以控制输出信号FULL的占空比,使时钟信号变得比较均匀。试在原来的VHDL 代码基础上进行改进,使用D和D1来控制FULL信号的占空比。 4 设计一个5分频器,使其分频时钟的占空比位3/5,写出VHDL设计代码。 【提示:对于一个5分频器的设计,可以先设计一个4位5进制计数器,则计数器的值在0,1,2,3,4上周期性循环。设计方法是:当计数器为4时,如果下一个时钟沿到来则将计数器置0,然后开始正常计数。另外定义一个分频信号CLK_DIV5,当计数器值为0,1,2时,使CLK_DIV5=1,当计数器值为3,4时,使CLK_DIV5=0,则CLK_DIV5为5分频信号,其占空比为3/5。】

通用分频器基本原理

通用分频器基本原理 整数分频包括偶数分频和奇数分频,对于偶数N分频,通常是由模N/2计数器实现一个占空比为1:1的N分频器,分频输出信号模N/2自动取反。对于奇数N分频,上述方法就不适用了,而是由模N计数器实现非等占空比的奇数N分频器,分频输出信号取得是模N计数中的某一位(不同N值范围会选不同位)。这种方法同样适用于偶数N 分频,但占空比不总是1:1,只有2的n次方的偶数(如4、8、16等)分频占空比才是1:1。这种方法对于奇数、偶数具有通用性。半整数分频器也是在这种方法基础上实现的。除了一个模N计数器,还需要一个异或模块和一个2分频模块。半整数分频器原理如图1所示:半整数分频器设计思想:通过异或门和2分频模块组成一个改变输入频率的脉冲添加电路,也就是说N-0.5个输入信号周期内产生了N个计数脉冲,即输入信号其中的一个含一个脉冲的周期变为含两个脉冲的周期。而这一改变正是输入频率与2分频输出异或的结果。由2分频输出决定一个周期产生两个脉冲有两种方式:当一个输入信号来一个脉冲(前半周期)时,2分频输出变为‘1’,clk_in 取反,后半周期就会产生一个脉冲;2分频输出由‘1’变为‘0’时,clk_in刚把一个周期(前半周期)内低电平变为高电平产生一个脉冲,而后半周期的脉冲与‘0’异或不变。从而实现N-0.5分频。要实现奇数、偶数、半整数通用分频器只需再加一个控制选择信号sel。当sel=‘1’时,clk_in与2分频输出异或,实现半整数分频;当sel=‘0’时,只选通clk_in,实现整数分频。通用分频器原理如图

2所示:Verilog语言的实现本设计采用层次化的设计方法,首先设计通用分频器中各组成电路元件,然后通过元件例化的方法,调用各元件,实现通用分频器。1、选择异或门模块half_select:modulehalf_select(sel,a,b,c); outputc; inputsel,a,b; xoru1(w,a,b); assignc=sel?w:a; (当sel=‘1’时,clk_in与2分频输出异或,实现半整数分频;当sel=‘0’时,只选通clk_in,实现整数分频。)endmodule 2、模N计数器counter_n:实现参数化设计N可取2~256,也可增加count位数使N可取更大的值。以N=7为例通过设置sel分别实现奇数7分频和半整数 6.5分频。modulecounter_n(reset,en,clk_in,clk_out,count); parameterN=7;inputreset,en,clk_in;outputclk_out; output[7:0]count;regclk_out;reg[7:0]count; always@(posedgeclk_in)begin if(reset)begin count[7:0]=0;end elseif(en)begin if(count==(N-1))count=0;else count=count1; end end always begin if(N clk_out=count[0]; elseif(N clk_out=count;elseif(N clk_out=count; elseif(N 在复杂数字逻辑电路设计中,经常会用到多个不同的时钟信号。介绍一种通用的分频器,可实现2~256之间的任意奇数、偶数、半整数分频。首先简要介绍了FPGA器件的特点和应用范围。接着介绍了通用分频器的基本原理和分类,并以分频比为奇数7

EDA 半整数分频器的设计实验报告

EDA技术实验项目报告 项目题目: 半整数分频器的设计 姓名: 院系:应用技术学院 专业:电子信息工程(职教) 学号: 指导教师: 综合成绩: 完成时间: 2012 年 6 月13 日一、项目实验内容摘要 基于FPGA硬件开发板,利用QuartusII软件通过VHDL输入的方式实现2.5分频器的设计并用示波器观察; 试验目的:

1、掌握半整数分频器的VHDL设计原理与方法。 2、掌握在QUARTUS II中进行简单数字系统设计的全过程。 实验原理: 设有一个5MHz的时钟源,但电路中要产生一个2MHz的时钟信号,由于分频比为2.5,因此整数分频器将不能胜任。 采用可编程逻辑器件实现分频系数为2.5的分频器,可采用以下方法:设计一个模3的计数器,再设计一个扣除脉冲电路,加在模3计数器输出之后,每来两个脉冲就扣除一个脉冲(实际上是使被扣除的脉冲变成很窄的脉冲,可由异或门实现),就可以得到分频系数为2.5的小数分频器。采用类似方法,可以设计分频系数为任意半整数的分频器。 当分频系数为N—0.5(N为整数)时,可控制扣除脉冲的时间,是输出为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。 二、项目实验源代码 分频器代码 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY deccount IS PORT ( inclk: IN STD_LOGIC; --时钟源 preset: IN STD_LOGIC_VECTOR(3 DOWNTO 0); --预置分频值N outclk1: OUT STD_LOGIC; outclk2: BUFFER STD_LOGIC ); --输出时钟 END deccount; ARCHITECTURE deccount_arch OF deccount IS SIGNAL clk, divide2: STD_LOGIC; SIGNAL count: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN clk<=inclk XOR divide2; --inclk与divide2异或后作为模N计数器的时钟 outclk1<=inclk; PROCESS(clk) BEGIN IF(clk'event AND clk='1') THEN IF(count="0000") THEN count<=preset-1; --置整数分频值N outclk2<='1'; ELSE count<=count-1; --模N 计数器减法计数 outclk2<='0'; END IF; END IF; END PROCESS; PROCESS(outclk2)

数控分频器的设计

数控分频器的设计 一、实验目的: 学习数控分频器的设计和测试方法。 二、实验原理: 数控分频器的功能为在不同输入信号时,对时钟信号进行不同的分频,在输出端输出不同频率的信号。该电路可以用具有并行预置功能的加法计数器实现,方法是对应不同的输入信号,预置数(初始计数值)设定不同的值,计数器以此预置数为初始状态进行不同模值的计数,当计数器的状态全为1时,计数器输出溢出信号。用计数器的溢出信号作为输出信号或输出信号的控制值,使输出信号的频率受控于输入的预置数。 电路输出波形图: 三、实验内容: 1)根据实验原理画出电路框图,并计算在不同预置数时输出信号的频率与时钟频率的比值。 ------------------------------------------------------------------------------------------------------------- 原理图:

数控分频器输出频率与输入时钟的关系: 当输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比。 任意小数都可以表示成a n b +形式,其中a奇数和半整数分频器

奇数分频器 1 引言 分频器在CPLD/FPGA设计中使用频率非常高,尽管目前大部分设计中采用芯片厂家集成的锁相环资源,但是对于要求奇数倍分频、小数倍分频的应用场合却往往不能满足要求。硬件工程师希望有一种灵活的设计方法,根据需要,在实验室就能设计分频器并马上投入使用,更改频率时无需改动原器件或电路板,只需重新编程,在数分钟内即可完成。 对于偶数分频,使用一模N计数器模块即可实现,即每当模N计数器从0开始计数至N时,输出时钟进行翻转,同时使计数器复位,使之从0开始重新计数,以此循环即可实现。但对于奇数分频,实现50%的占空比却是比较困难的。下面给出占空比50%的奇数分频器的设计源程序和仿真结果。 2 VHDL程序 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;--添加库 ENTITY fdiv IS --设计实体PORT( clk,reset : IN STD_LOGIC;--端口说明preset: IN INTEGER;--preset:分频预置数clkout : OUT STD_LOGIC);- -clkout :分频后得到的时钟END fdiv; ARCHITECTURE behave OF fdiv IS--设计构造体SIGNAL s1,s2 : STD_LOGIC;--内部信号s1,s2 SIGNAL cnt : INTEGER RANGE 0 TO preset-1;--模为preset的计数信号BEGIN P1: PROCESS(clk,reset) --计数器BEGIN IF reset='1' THEN cnt<=0; ELSIF clk'event AND clk='1' THEN IF cnt=0 THEN