CMOS、TTL逻辑门电路测试 实验报告(有数据)

实验二 CMOS 、TTL 逻辑门电路测试

一、实验目的

1、掌握CMOS 、TTL 逻辑门电路特性测试的方法。

2、掌握CMOS 、TTL 逻辑门电路的主要技术指标。

3、比较CMOS 门和TTL 门的特点。

二、实验仪器及器件

1、双踪示波器、数字万用表、实验箱

2、实验用元器件:① 74LS00 1片 ② CD4001B 1片

三、实验内容及结果分析

1.CD4069逻辑电平测试及功能测试

本实验采用CD4069芯片,分别选择电源电压V dd = 5V 和V dd = 12V 验证其逻辑功能。根据CMOS 芯片的特性参数,在输入端A 加不同的逻辑电平V A .用电压表测出相应输出端的逻辑电平Vo .记录测试结果,并根据测试结果列成真值表,写出逻辑表达式,验证其逻辑功能。

表 1.1A 表1.1B 表1.1 输入 输出

V DD =5V

V DD =12V

输入 输出 A O V A /V V O /V V A /V V O /V A O 0 1 0.000 5.053 0.000 11.94 0 1 1

5,067

0.020

11.99

0.101

1

逻辑表达式:L A = 2. CD4069电压传输特性

按图3.1所示接线。令芯片的电源电压V dd = 10V 。调节电位器Rw 的阻值.使V I 在+0~+10V 变化,观察输出电压的变化,指出ViL 、ViH 、VoL 、VoH 、转折点输入电平Vth 、抗干扰容限。

表1.2

V I /V 0.006 0.375 1.115 2.022 3.105 4.021 5.001 5.251 5.439 5.63 V O /V 9.96 9.96 9.96 9.93 9.66 9.20 8.20 7.70 7.03 5.387 V I /V 5.808 6.08 6.69 7.24 7.64 8.13 8.64 9.00 9.27 9.97 V O /V

2.729

1.751

1.1011

0.647

0.460

0.293

0.167

0.110

0.083

0.066

V IL =2.022V V OL =0.066V

V IH =8.13V V OH =9.96V V th =5.63V

输入高电平的噪声容限 (min)(min)9.968.13 1.83NH OH IH V V V V V V =-=-= 输出低电平的噪声容限 (max)(max) 2.0220.066 1.956NL IL OL V V V V V V =-=-=

3.74LS00逻辑电平测试及功能测试

TTL 集成电路电源电压V cc = 5V 。本实验采用TTL 逻辑门电路74LS00芯片,根据TTL 芯片的特性参数,在输入端A 、B 加不同的逻辑电平V A 、V B .用电压表测出相应输出端的逻辑电平Vo .记录测试结果,并根据测试结果列成真值表,写出逻辑表达式,验证其逻辑功能。 表1.3A 表1.3B 表1.3 A B O

V A /V

V B /V

V O /V

A

B

O

0 0 1 0.001 0.001 4.173 0 0 1 0 1 1 0.001 4.982 4.210 0 1 1 1 0 1

4.961 0.001 4.210

1 0 1 1 1 0

5.069

5.069

0.191

1

1

逻辑表达式:L A B = 4. 74LS00电压传输特性

测试电路参照图3.1,测试芯片换成74LS00,芯片的电源电压V cc = 5V 。调节电位器Rw 的阻值.使V I

在+0~+5V 变化,观察输出电压的变化,指出V iL 、V iH 、V oL 、V oH 、转折点输入电平V th 、抗干扰容限。

表1.4 V I /V 0.268 0.683 0.780 0.877 0.939 0.988 1.028 1.078 1.134 1.645 2.706 V O /V

4.211 4.208 4.187 4.062 3.725 3.159 2.126 0.183 0.175 0.171 0.171

1.645IL V V =

2.706IH V V =

0.171OL V V = 4.211OH V V = th 1.028V V = 输入高电平的噪声容限 (min)(min) 4.211 2.706 1.505NH OH IH V V V V V V =-=-= 输出低电平的噪声容限 (max)(max) 1.6450.1710.474NL IL OL V V V V V V =-=-=

5.门电路的驱动能力测试

扇出系数N O 是衡量门电路负载能力的一个参数,有低电平扇出系数N OL 和高电平扇出系数N OH ,通常N OH >N OL ,故常以N OL 作为门电路的扇出系数。

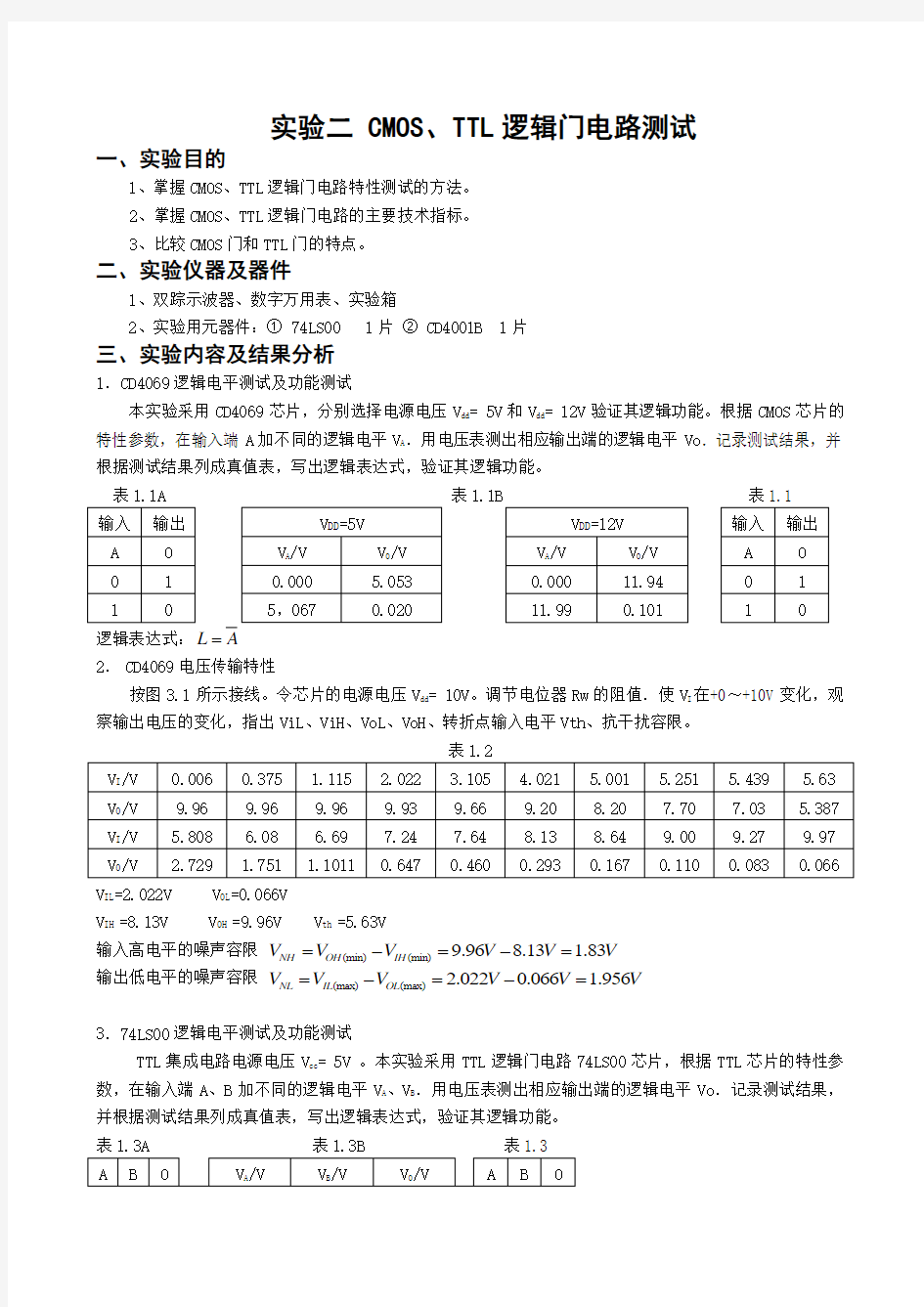

I IL 的测试电路如图3.2所示,

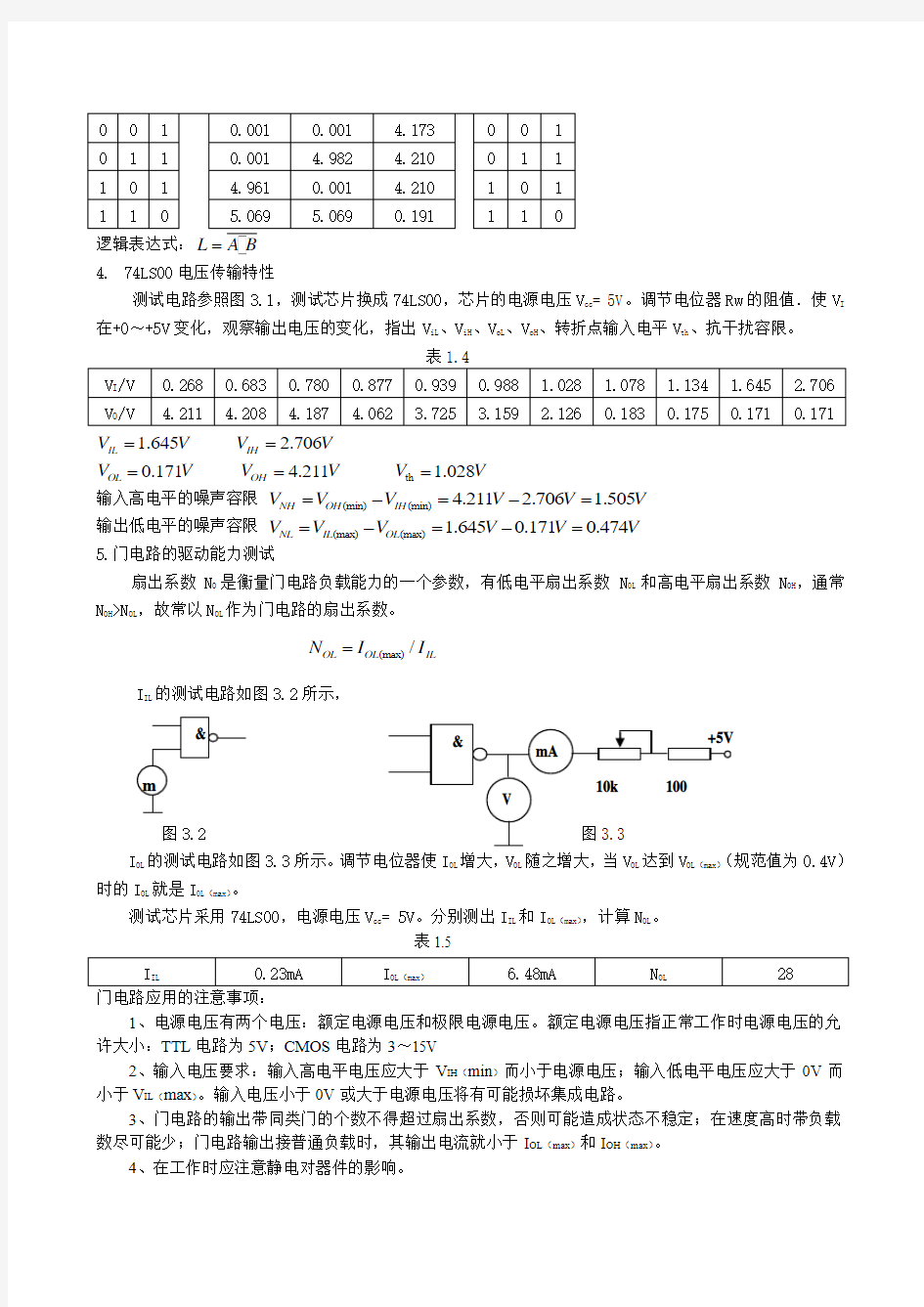

图 3.2 图3.3

I OL 的测试电路如图3.3所示。调节电位器使I OL 增大,V OL 随之增大,当V OL 达到V OL (max )(规范值为0.4V )时的I OL 就是I OL (max )。

测试芯片采用74LS00,电源电压V cc = 5V 。分别测出I IL 和I OL (max ),计算N OL 。 表1.5

门电路应用的注意事项:

1、电源电压有两个电压:额定电源电压和极限电源电压。额定电源电压指正常工作时电源电压的允许大小:TTL 电路为5V ;CMOS 电路为3~15V

2、输入电压要求:输入高电平电压应大于V IH (min )而小于电源电压;输入低电平电压应大于0V 而小于V IL (max )。输入电压小于0V 或大于电源电压将有可能损坏集成电路。

3、门电路的输出带同类门的个数不得超过扇出系数,否则可能造成状态不稳定;在速度高时带负载数尽可能少;门电路输出接普通负载时,其输出电流就小于I OL (max )和I OH (max )。

4、在工作时应注意静电对器件的影响。

I IL 0.23mA I OL (max ) 6.48mA N OL 28 (max)/OL OL IL

N I I =&

m

+5V

mA

&

V

10k

100

数字逻辑电路实验报告

数字逻辑电路 实验报告 指导老师: 班级: 学号: 姓名: 时间: 第一次试验一、实验名称:组合逻辑电路设计

二、试验目的: 1、掌握组合逻辑电路的功能测试。 2、验证半加器和全加器的逻辑功能。 3、、学会二进制数的运算规律。 三、试验所用的器件和组件: 二输入四“与非”门组件3片,型号74LS00 四输入二“与非”门组件1片,型号74LS20 二输入四“异或”门组件1片,型号74LS86 四、实验设计方案及逻辑图: 1、设计一位全加/全减法器,如图所示: 电路做加法还是做减法是由M决定的,当M=0时做加法运算,当M=1时做减法运算。当作为全加法器时输入信号A、B和Cin分别为加数、被加数和低位来的进位,S 为和数,Co为向上的进位;当作为全减法时输入信号A、B和Cin分别为被减数,减数和低位来的借位,S为差,Co为向上位的借位。 (1)输入/输出观察表如下: (2)求逻辑函数的最简表达式 函数S的卡诺图如下:函数Co的卡诺如下: 化简后函数S的最简表达式为: Co的最简表达式为:

(3)逻辑电路图如下所示: 2、舍入与检测电路的设计: 用所给定的集成电路组件设计一个多输出逻辑电路,该电路的输入为8421码,F1为“四舍五入”输出信号,F2为奇偶检测输出信号。当电路检测到输入的代码大于或等于5是,电路的输出F1=1;其他情况F1=0。当输入代码中含1的个数为奇数时,电路的输出F2=1,其他情况F2=0。该电路的框图如图所示: (1)输入/输出观察表如下: B8 B4 B2 B1 F2 F1 0 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1 1 0 0 0 1 0 0 1 0 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 1 1 0 0 0 1 1 1 0 0 1 0 1 1 0 1 0 0 1 1 0 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 1

实验一 常用基本逻辑门电路功能测试

实验一常用基本逻辑门电路功能测试 一、实验目的 1.验证常用门电路的逻辑功能。 2.了解常用74LS系列门电路的引脚分布。 3.根据所学常用集成逻辑门电路设计一组合逻辑电路。 二、实验原理 集成逻辑门电路是最简单、最基本的数字集成元件。任何复杂的组合电路和时序电路都可用逻辑门通过适当的组合连接而成。目前已有门类齐全的集成门电路,例如“与门”、“或门”、“非门”、“与非门”等。虽然,中、大规模集成电路相继问世,但组成某一系统时,仍少不了各种门电路。因此,掌握逻辑门的工作原理,熟练、灵活地使用逻辑门是数字技术工作者所必备的基本功之一。 TTL门电路 TTL集成电路由于工作速度高、输出幅度较大、种类多、不易损坏而使用较广,特别对学生进行实验论证,选用TTL电路比较合适。因此,本书大多采用74LS(或74)系列TTL 集成电路。它的工作电源电压为5V土0.5V,逻辑高电平1时≥2.4V,低电平0时≤0.4V。2输入“与门”,2输入“或门”,2输入、4输入“与非门”和反相器的型号分别是:74LS08:2输入端四“与门”,74LS32:2输入端四“或门”,74LS00:2输入端四“与非门”,74LS20:4输入端二“与非门”和74LS04六反相器(“反相器”即“非门”)。各自的逻辑表达式分别为:与门Q=A?B,或门Q=A+B,与非门Q=A.B,Q=A.B.C.D,反相器Q=A。

TTL集成门电路集成片管脚分别对应逻辑符号图中的输入、输出端,电源和地一般为集成片的两端,如14管脚集成片,则7脚为电源地(GND),14脚为电源正(V cc),其余管脚为输入和输出,如图1所示。 管脚的识别方法是:将集成块正面(有字的一面)对准使用者,以左边凹口或小标志点“ ? ”为起始脚,从下往上按逆时针方向向前数1、2、3、…… n脚。使用时,查找IC 手册即可知各管脚功能。 图1 74LS08集成电路管脚排列图 三、实验内容与步骤 TTL门电路逻辑功能验证 (1)与门功能测试:将74LS08集成片(管脚排列图1)插入IC空插座中,输入端接逻辑开关,输出端接LED发光二极管,管脚14接+5V电源,管脚7接地,即可进行实验。将结果用逻辑“0”或“1”来表示并填入表1中。

数字实验一 门电路逻辑功能与测试

数字实验一门电路逻辑功能与测试

实验一门电路逻辑功能及测试 一、实验目的: 1.熟悉常用集成门电路的逻辑功能及测试方法。 2. 熟悉各种门电路的管脚排列,进一步熟悉仿真软件和数字试验箱的使用。 3.学习利用与非门组成其它逻辑门电路并验证其逻辑功能。 二、实验仪器及设备 1.数字电路实验箱 2.万用表 3.集成芯片: 74LS00 2输入端四与非门 2片 74LS86 2输入端四异或门 1片 三、实验原理 1. TTL集成电路的输入端和输出端均为三极管结构,所以称作三极管、三极管逻辑电路(Transistor -Transistor Logic )简称TTL电路。54 系列的TTL 电路和74 系列的TTL电路具有完全相同的电路结构和电气性能参数。所不同的是54 系列比74 系列的工作温度范围更宽,电源允许的范围也更大。74 系列的工作环境温度规定为0—700C,电源电压工作范围为5V±5%V,而54 系列工作环境温度规定为-55—±1250C,电源电压工作范围为5V±10%V。 54H 与74H,54S 与74S 以及54LS 与74LS 系列的区别也仅在于工作环境温度与电源电压工作范围不同,就像54 系列和74 系列的区别那样。在不同系列的TTL 器件中,只要器件型号的后几位数码一样,则它们的逻辑功能、外形尺寸、引脚排列就完全相同。 TTL 集成电路由于工作速度高、输出幅度较大、种类多、不易损坏而使用较广,特别对我们进行实验论证,选用TTL 电路比较合适。因此,本实训教材大多采用74LS(或74)系列TTL 集成电路,它的电源电压工作范围为5V±5%V,逻辑高电平为“1”时≥2.4V,低电平为“0”时≤0.4V。 2. 集成逻辑门有许多种,如:与门、或门、非门、与非门、或非门、与或非门、异或门等等。但其中与非门用途最广,74LS00是“TTL系列”中的与非门,是四-2输入与非门电路,即在一块集成电路内含有四个独立的与非门。每个与非门有2个输入端。 3. 利用与非门可以组成其它许多逻辑门。要实现其它逻辑门的功能,只要将该门的逻辑函数表达式化成与非-与非表达式,然后用多个与非门连接起来就可以达到目的。例如,要实现或门Y=A+B,根据摩根定律,或门的逻辑函数表

数字电路组合逻辑电路设计实验报告

数字电路组合逻辑电路设 计实验报告 The Standardization Office was revised on the afternoon of December 13, 2020

实验三组合逻辑电路设计(含门电路功能测试)

一、实验目的 1.掌握常用门电路的逻辑功能 2.掌握小规模集成电路设计组合逻辑电路的方法 3.掌握组合逻辑电路的功能测试方法 二、实验设备与器材 Multisim 、74LS00 四输入2与非门、示波器、导线 三、实验原理 TTL集成逻辑电路种类繁多,使用时应对选用的器件做简单逻辑功能检查,保证实验的顺利进行。 测试门电路逻辑功能有静态测试和动态测试两种方法。静态测试时,门电路输入端加固定的高(H)、低电平,用示波器、万用表、或发光二极管(LED)测

出门电路的输出响应。动态测试时,门电路的输入端加脉冲信号,用示波器观测输入波形与输出波形的同步关系。 下面以74LS00为例,简述集成逻辑门功能测试的方法。74LS00为四输入2与非门,电路图如3-1所示。74LS00是将四个二输入与非门封装在一个集成电路芯片中,共有14条外引线。使用时必须保证在第14脚上加+5V电压,第7脚与底线接好。 整个测试过程包括静态、动态和主要参数测试三部分。 表3-1 74LS00与非门真值表 1.门电路的静态逻辑功能测试 静态逻辑功能测试用来检查门电路的真值表,确认门电路的逻辑功能正确与否。实验时,可将74LS00中的一个与非门的输入端A、B分别作为输入逻辑变量,加高、低电平,观测输出电平是否符合74LS00的真值表(表3-1)描述功能。

实验一基本门电路的逻辑功能测试

实验一基本门电路的逻辑功能测试 一、实验目的 1、测试与门、或门、非门、与非门、或非门与异或门的逻辑功能。 2、了解测试的方法与测试的原理。 二、实验原理 实验中用到的基本门电路的符号为: 在要测试芯片的输入端用逻辑电平输出单元输入高低电平,然后使用逻辑电平显示单元显示其逻辑功能。 三、实验设备与器件 1、数字逻辑电路用PROTEUS 2、显示可用发光二极管。 3、相应74LS系列、CC4000系列或74HC系列芯片若干。 四、实验内容 1.测试TTL门电路的逻辑功能: a)测试74LS08的逻辑功能。(与门)000 010 100 111 b)测试74LS32的逻辑功能。(或门)000 011 101 111 c)测试74LS04的逻辑功能。(非门)01 10 d)测试74LS00的逻辑功能。(两个都弄得时候不亮,其他都亮)(与非门)(如果只接一个的话,就是非门)001 011 101 110 e)测试74LS02(或非门)的逻辑功能。(两个都不弄得时候亮,其他不亮)001 010 100 110 f)测试74LS86(异或门)的逻辑功能。 2.测试CMOS门电路的逻辑功能:在CMOS 4000分类中查询 a)测试CC4081(74HC08)的逻辑功能。(与门) b)测试CC4071(74HC32)的逻辑功能。(或门) c)测试CC4069(74HC04)的逻辑功能。(非门) d)测试CC4011(74HC00)的逻辑功能。(与非门)(如果只接一个的话,就是非门)

e)测试CC4001(74HC02)(或非门)的逻辑功能。 f) 测试CC4030(74HC86)(异或门)的逻辑功能。 五、实验报告要求 1.画好各门电路的真值表表格,将实验结果填写到表中。 2.根据实验结果,写出各逻辑门的逻辑表达式,并分析如何判断逻辑门的好坏。 3.比较一下两类门电路输入端接入电阻或空置时的情况。 4.查询各种集成门的管脚分配,并注明各个管脚的作用与功能。 例:74LS00 与门 Y=AB

基本门电路实验报告处理

43121556423156实验三:基本门电路及触发器 实 验 室: 实验台号: 日 期: 2016.10.7 专业班级: 姓 名: 学 号: 一、 实验目的 1.了解TTL 门电路的原理,性能好使用方法,验证基本门电路逻辑功能。 2.掌握门电路的设计方法。 3.验证J-K 触发器的逻辑功能。 4.掌握触发器转换的设计方法。 二、实验内容 (一)验证以下门电路的逻辑关系 1. 用与非门(00)实现与门逻辑关系:F=AB 2. 异或门(86): (二):门电路的设计(二选一) 1.用74LS00和74LS86 设计半加器. 2.用TTL 与非门设计一个三人表决电路。 A B C 三个裁判,当表决某个提案时,多数人同意提案为通过。 (1为同意,0为不同意) 要求:用74LS00和 74LS10芯片。 (三)验证JK 触发器的逻辑关系 1.J-K 触发器置位端、复位端及功能测试。 图3-1 JK 触发器(74LS112)和D 触发器(74LS74) 2、设计J-K 触发器转化成D 触发器的电路 利用与非门和J-K 触发器设计并测试逻辑功能。 B A B A B A F ⊕=+=n n n n n n n B A B A B A S ⊕=+=' n n n B A C ='

A B F 三、实验原理图 图3-2与门电路 图3-3 异或门电路 图3-4半加器 四、实验结果及数据处理 1. 直接在实验原理图上标记芯片的引脚。 2. 写出实验结果。 (1)与门、异或门实验结果表(用数字万用表测量高低电平1、0的电压值。) (2)半加器实验结果 (3) 表决电路结果 =1A B F

逻辑门电路实验报告(精)

HUBEI NORMAL UNIVERSITY 电工电子实验报告 电路设计与仿真—Multisim 课程名称 逻辑门电路 实验名称 2009112030406 陈子明 学号姓名 电子信息工程 专业名称 物理与电子科学学院 所在院系 分数

实验逻辑门电路 一、实验目的 1、学习分析基本的逻辑门电路的工作原理; 2、学习各种常用时序电路的功能; 3、了解一些常用的集成芯片; 4、学会用仿真来验证各种数字电路的功能和设计自己的电路。 二、实验环境 Multisim 8 三、实验内容 1、与门电路 按图连接好电路,将开关分别掷向高低电平,组合出(0,0)(1,0)(0,1)(1,1)状态,通过电压表的示数,看到与门的输出状况,验证表中与门的功能: 结果:(0,0)

(0,1) (1,0) (1,1) 2、半加器 (1)输入/输出的真值表

输入输出 A B S(本位和(进位 数)0000 0110 1010 1101 半加器测试电路: 逻辑表达式:S= B+A=A B;=AB。 3、全加器 (1)输入输出的真值表 输入输出

A B (低位进 位S(本位 和) (进位 数) 0 0 0 0 0 00110 01010 01101 10010 10101 11001 11111(2)逻辑表达式:S=i-1;C i=AB+C i-1(A B) (3)全加器测试电路:

4、比较器 (1)真值表 A B Y1(A>B Y2(A Y3(A=B 0 0 0 0 1 0 1 0 1 0 1 0 1 0 0 1 1 0 0 1 (2)逻辑表达式: Y1=A;Y2=B;Y3=A B。 (3)搭接电路图,如图: 1位二进制数比较器测试电路与结果:

实验三 CMOS集成逻辑门的逻辑功能与参数测试

实验三CMOS集成逻辑门的逻辑功能与参数测试 一、实验目的 1、掌握CMOS集成门电路的逻辑功能和器件的使用规则 2、学会CMOS集成门电路主要参数的测试方法 二、实验原理 1、CMOS集成电路是将N沟道MOS晶体管和P沟道 MOS晶体管同时用于 一个集成电路中,成为组合二种沟道MOS管性能的更优良的集成电路。CMOS集成电路的主要优点是: (1)功耗低,其静态工作电流在10-9A数量级,是目前所有数字集成电路中最低的,而TTL器件的功耗则大得多。 (2)高输入阻抗,通常大于1010Ω,远高于TTL器件的输入阻抗。 (3)接近理想的传输特性,输出高电平可达电源电压的 99.9%以上,低电平可达电源电压的0.1%以下,因此输出逻辑电平的摆幅很大,噪声容限很高。 (4)电源电压范围广,可在+3V~+18V范围内正常运行。 (5)由于有很高的输入阻抗,要求驱动电流很小,约0.1μA,输出电流在+5V电源下约为 500μA,远小于TTL电路,如以此电流来驱动同类门电路,其扇出系数将非常大。在一般低频率时,无需考虑扇出系数,但在高频时,后级门的输入电容将成为主要负载,使其扇出能力下降,所以在较高频率工作时,CMOS电路的扇出系数一般取10~20。 2、CMOS门电路逻辑功能 尽管CMOS与TTL电路内部结构不同,但它们的逻辑功能完全一样。本实验将测定与门CC4081,或门CC4071,与非门CC4011,或非门CC4001的逻辑功能。各集成块的逻辑功能与真值表参阅教材及有关资料。 3、CMOS与非门的主要参数 CMOS与非门主要参数的定义及测试方法与TTL电路相仿,从略。

4、CMOS 电路的使用规则 由于CMOS 电路有很高的输入阻抗,这给使用者带来一定的麻烦,即外来的干扰信号很容易在一些悬空的输入端上感应出很高的电压,以至损坏器件。CMOS 电路的使用规则如下: (1) V DD 接电源正极,V SS 接电源负极(通常接地⊥),不得接反。CC4000系列的电源允许电压在+3~+18V 范围内选择,实验中一般要求使用+5~+15V 。 (2) 所有输入端一律不准悬空 闲置输入端的处理方法: a) 按照逻辑要求,直接接V DD (与非门)或V SS (或非门)。 b) 在工作频率不高的电路中,允许输入端并联使用。 (3) 输出端不允许直接与V DD 或V SS 连接,否则将导致器件损坏。 (4) 在装接电路,改变电路连接或插、拔电路时,均应切断电源,严禁带电操作。 (5) 焊接、测试和储存时的注意事项: a 、电路应存放在导电的容器内,有良好的静电屏蔽; b 、焊接时必须切断电源,电烙铁外壳必须良好接地,或拔下烙铁,靠其余热焊接; c 、所有的测试仪器必须良好接地; 三、实验设备与器件 1、+5V 直流电源 2、双踪示波器 3、连续脉冲源 4、逻辑电平开关 5、逻辑电平显示器 6、直流数字电压表 7、直流毫安表 8、直流微安表 9、CC4011、CC4001、CC4071、CC4081、电位器 100K 、电阻 1K 四、实验内容 1、CMOS 与非门CC4011参数测试(方法与TTL 电路相同)

数电实验报告 实验二 组合逻辑电路的设计

实验二组合逻辑电路的设计 一、实验目的 1.掌握组合逻辑电路的设计方法及功能测试方法。 2.熟悉组合电路的特点。 二、实验仪器及材料 a) TDS-4数电实验箱、双踪示波器、数字万用表。 b) 参考元件:74LS86、74LS00。 三、预习要求及思考题 1.预习要求: 1)所用中规模集成组件的功能、外部引线排列及使用方法。 2) 组合逻辑电路的功能特点和结构特点. 3) 中规模集成组件一般分析及设计方法. 4)用multisim软件对实验进行仿真并分析实验是否成功。 2.思考题 在进行组合逻辑电路设计时,什么是最佳设计方案? 四、实验原理 1.本实验所用到的集成电路的引脚功能图见附录 2.用集成电路进行组合逻辑电路设计的一般步骤是: 1)根据设计要求,定义输入逻辑变量和输出逻辑变量,然后列出真值表; 2)利用卡络图或公式法得出最简逻辑表达式,并根据设计要求所指定的门电路或选定的门电路,将最简逻辑表达式变换为与所指定门电路相应的形式; 3)画出逻辑图; 4)用逻辑门或组件构成实际电路,最后测试验证其逻辑功能。 五、实验内容 1.用四2输入异或门(74LS86)和四2输入与非门(74LS00)设计一个一位全加器。 1)列出真值表,如下表2-1。其中A i、B i、C i分别为一个加数、另一个加数、低位向本位的进位;S i、C i+1分别为本位和、本位向高位的进位。 2)由表2-1全加器真值表写出函数表达式。

3)将上面两逻辑表达式转换为能用四2输入异或门(74LS86)和四2输入与非门(74LS00)实现的表达式。 4)画出逻辑电路图如图2-1,并在图中标明芯片引脚号。按图选择需要的集成块及门电路连线,将A i、B i、C i接逻辑开关,输出Si、Ci+1接发光二极管。改变输入信 号的状态验证真值表。 2.在一个射击游戏中,每人可打三枪,一枪打鸟(A),一枪打鸡(B),一枪打兔子(C)。 规则是:打中两枪并且其中有一枪必须是打中鸟者得奖(Z)。试用与非门设计判断得奖的电路。(请按照设计步骤独立完成之) 五、实验报告要求: 1.画出实验电路连线示意图,整理实验数据,分析实验结果与理论值是否相等。 2.设计判断得奖电路时需写出真值表及得到相应输出表达式以及逻辑电路图。 3.总结中规模集成电路的使用方法及功能。

实验1门电路的功能测试

实验一门电路的功能测试 1.实验目的 (1)熟悉数字电路实验装置,能正确使用装置上的资源设计实验方案; (2)熟悉双列直插式集成电路的引脚排列及使用方法; (3)熟悉并验证典型集成门电路逻辑功能。 2.实验仪器与材料 (1)数字电路实验装置1台; (2)万用表1块 (3)双列直插集成电路芯片74LS00、74LS86、74LS125各1片,导线若干。 3.知识要点 (1)数字电路实验装置的正确使用 TPE-D6A电子技术学习机是一种数字电路实验装置,利用装置上提供的电路连线、输入激励、输出显示等资源,我们可以设计合理的实验方案,通过连接电路、输入激励信号、测试输出状态等一系列实验环节,对所设计的逻辑电路进行结果测试。该实验装置功能模块组成如图1.1所示。 图中①为集成电路芯片区,有15个IC插座及相应的管脚连接端子,其中A13是8管脚插座,A11、A12是14管脚插座,A1、A2、A3、A7、A8是16管脚插座,A4、A5是18管脚插座,A9、A14、A16、A7、A8是20管脚插座,A10、A15是24管脚插座。根据双列直插式集成电路芯片的管脚数可以选择相同管脚数的IC插座,并将集成电路芯片插入IC插座(凹口侧相对应),可以通过导线将管脚引出的接线端相连,实现电路的连接。 图中②为元件区,内有多个不同参数值的电阻、电容以及二极管、三极管、稳压管、蜂鸣器等元件可供连接电路时选择。 图中③为电位器区,内有1k、10k、22k、100k、220k阻值的电位器等元件可供连接电路时选择。 图中④为直流稳压电源区,是装置内部的直流稳压电源提供的+5V、-5V、+15V、-15V 电源输出引脚,可以为有源集成芯片提供工作电源电压。

组合逻辑电路实验报告.docx

篇一:培养基的制备与灭菌实验报告 陕西师范大学远程教育学院 生物学实验报告 报告题目培养基的制备与灭菌 姓名刘伟 学号 专业生物科学 批次/层次 指导教师 学习中心培养基的制备与灭菌 一、目的要求 1.掌握微生物实验室常用玻璃器皿的清洗及包扎方法。 2.掌握培养基的配置原则和方法。 3.掌握高压蒸汽灭菌的操作方法和注意事项。 二、基本原理 牛肉膏蛋白胨培养基: 是一种应用最广泛和最普通的细菌基础培养基,有时又称为普通培养基。由于这种培养基中含有一 般细胞生长繁殖所需要的最基本的营养物质,所以可供细菌生长繁殖之用。 高压蒸汽灭菌: 主要是通过升温使蛋白质变性从而达到杀死微生物的效果。将灭菌的物品放在一个密闭和加压的灭 菌锅内,通过加热,使灭菌锅内水沸腾而产生蒸汽。待蒸汽将锅内冷空气从排气阀中趋尽,关闭排 气阀继续加热。此时蒸汽不溢出,压力增大,沸点升高,获得高于100℃的温度导致菌体蛋白凝固 变性,而达到灭菌的目的。 三、实验材料 1.药品:牛肉膏、蛋白胨、nacl、琼脂、1mol/l的naoh和hcl溶液。 2.仪器及玻璃器皿:天平、高压蒸汽灭菌锅、移液管、试管、烧杯、量筒、三 角瓶、培养皿、玻璃漏斗等。 3.其他物品:药匙、称量纸、ph试纸、记号笔、棉花等。 四、操作步骤 (一)玻璃器皿的洗涤和包装 1.玻璃器皿的洗涤 玻璃器皿在使用前必须洗刷干净。将三角瓶、试管、培养皿、量筒等浸入含有洗涤剂的水中.用毛 刷刷洗,然后用自来水及蒸馏水冲净。移液管先用含有洗涤剂的水浸泡,再用自来水及蒸馏水冲洗。洗刷干净的玻璃器皿置于烘箱中烘干后备用。 2.灭菌前玻璃器皿的包装 (1)培养皿的包扎:培养皿由一盖一底组成一套,可用报纸将几套培养皿包

实验一基本门电路的逻辑功能测试

实验一基本门电路得逻辑功能测试 一、实验目得 1、测试与门、或门、非门、与非门、或非门与异或门得逻辑功能。 2、了解测试得方法与测试得原理。 二、实验原理 实验中用到得基本门电路得符号为: 在要测试芯片得输入端用逻辑电平输出单元输入高低电平,然后使用逻辑电平显示单元显示其逻辑功能。 三、实验设备与器件 1、数字逻辑电路用PROTEUS 2、显示可用发光二极管。 3、相应74LS系列、CC4000系列或74HC系列芯片若干. 四、实验内容 1.测试TTL门电路得逻辑功能: a)测试74LS08得逻辑功能.(与门)000 010100111 b)测试74LS32得逻辑功能.(或门)000 011 101 111 c)测试74LS04得逻辑功能.(非门)0110 d)测试74LS00得逻辑功能。(两个都弄得时候不亮,其她都亮)(与非门)(如果只接一个得话,就就是非门)001011 101 110 e)测试74LS02(或非门)得逻辑功能。(两个都不弄得时候亮,其她不亮)001010100 110 f)测试74LS86(异或门)得逻辑功能。 2.测试CMOS门电路得逻辑功能:在CMOS 4000分类中查询 a)测试CC4081(74HC08)得逻辑功能。(与门) b)测试CC4071(74HC32)得逻辑功能。(或门) c)测试CC4069(74HC04)得逻辑功能。(非门) d)测试CC4011(74HC00)得逻辑功能。(与非门)(如果只接一个得话,就就是非门) e)测试CC4001(74HC02)(或非门)得逻辑功能。 f) 测试CC4030(74HC86)(异或门)得逻辑功能。

实验三、基本门电路设计

实验设计部分: 由于1在预习时已经做过设计,故在此省略该步骤。 2、用与非门实现Y=A’B’+CD+ABC+BD. 由于Y=A’B’+CD+ABC+BDY =((A’B’)’(CD)’(ABC)’(BD)’)’ 由此连接电路得: 测试结果为: 3、设计一个奇偶校验器,使得三输入中“1”的个数为奇数时发出报警信号。 由题意得输出为1是报警,0是不报警,逻辑真值表为: 即: Y=A’B’C+A’BC’+AB’C’+ABC =C(A⊕B)’+C’(A⊕B) =C⊕B⊕A 所以逻辑电路图为: