BCD七段显示译码器

BCD七段显示译码器

1.什么是BCD码?

2.理解二进制?十进制?十六进制?

BCD码(Binary-Coded Decimal?)也称二进码十进数或二-十进制代码。用4位二进制数来表示1位十进制数中的0~9这10个数码。是一种二进制的数字编码形式,用二进制编码的十进制代码。BCD码这种编码形式利用了四个位元来储存一个十进制的数码,使二进制和十进制之间的转换得以快捷的进行。这种编码技巧最常用于会计系统的设计里,因为会计制度经常需要对很长的数字串作准确的计算。相对于一般的浮点式记数法,采用BCD码,既可保存数值的精确度,又可免却使电脑作浮点运算时所耗费的时间。此外,对于其他需要高精确度的计算,BCD编码亦很常用。

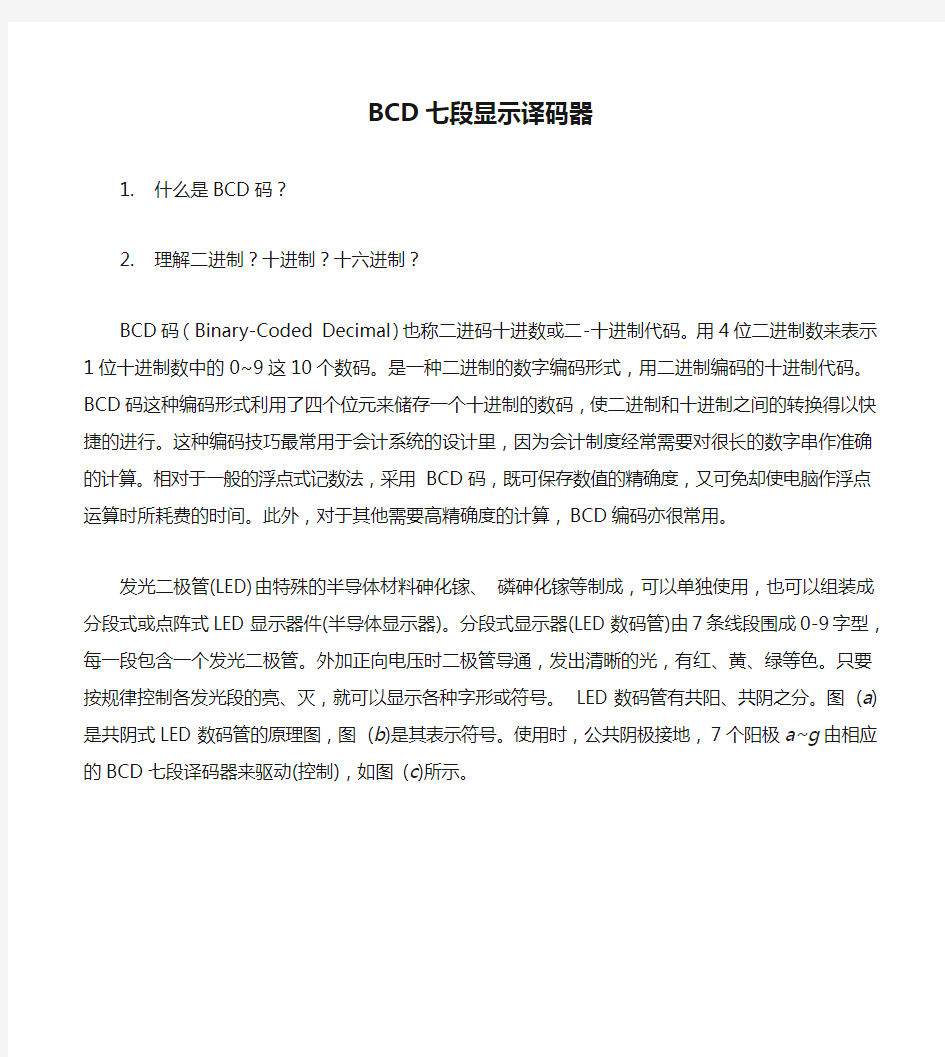

发光二极管(LED)由特殊的半导体材料砷化镓、磷砷化镓等制成,可以单独使用,也可以组装成分段式或点阵式LED显示器件(半导体显示器)。分段式显示器(LED数码管)由7条线段围成0-9字型,每一段包含一个发光二极管。外加正向电压时二极管导通,发出清晰的光,有红、黄、绿等色。只要按规律控制各发光段的亮、灭,就可以显示各种字形或符号。 LED数码管有共阳、共阴之分。图 (a)是共阴式LED数码管的原理图,图 (b)是其表示符号。使用时,公共阴极接地,7个阳极a~g由相应的BCD七段译码器来驱动(控制),如图 (c)所示。

数字显示译码器

BCD七段译码器的输入是一位BCD码(以D、C、B、A表示),输出是数码管各段的驱动信号(以Fa~Fg表示),也称4—7译码器。若用它驱动共阴LED数码管,则输出应为高有效,即输出为高(1)时,相应显示段发光。例如,当输入8421码DCBA=0100时,应显示,即要求同时点亮b、c、f、g段,熄灭a、d、e 段,故译码器的输出应为Fa~Fg=0110011,这也是一组代码,常称为段码。同理,根据组成0~9这10个字形的要求可以列出8421BCD七段译码器的真值表,见表4 - 12(未用码组省略)。

BCD七段译码器就是根据上述原理组成的,只是为了使用方便,增加了一些辅助控制电路。这类集成译码器产品很多,类型各异,它们的输出结构也各不相同,因而使用时要予以注意。图(c)是BCD七段译码器驱动LED数码管(共阴)的接法。

图中,电阻是上拉电阻,也称限流电阻,当译码器内部带有上拉电阻时,则可省去。数字显示译码器的种类很多,现已有将计数器、锁存器、译码驱动电路集于一体的集成器件,还有连同数码显示器也集成在一起的电路可供选用。

七段译码器显示电路

数字显示译码器 在数字系统中,常需要将数字、文字或符号等直观地显示出来。能够显示数字、文字或符号的器件称为显示器。数字电路中的数字量都是以一定的代码形式出现的,所以这些数字量要先经过译码,才能送到显示器去显示。这种能把数字量翻译成数字显示器所能识别的信号的译码器为数字显示译码器。 数字显示器有多种类型。按显示方式分,有字型重叠式、点阵式、分段式等。按发光物质分,有半导体显示器,又称发光二极管(LED)显示器、荧光显示器、液晶显示器、气体放电管显示器等。目前应用较广泛的是由发光二极管构成的七段数字显示器。 ①七段数字显示器 图6-53为发光二极管构成的七段数字显示器。它是将七个发光二极管(小数点也是一个发光二极管,共八个)按一定的方式排列起来,七段a、b、c、d、e、f、g(小数点DP)各对应一个发光二极管,利用不同发光段的组合,显示不同的阿拉伯数字。 (a)(b) 图6-53 七段数字显示器 (a)数字显示器(b)显示的数字 根据七个发光二极管的连接形式不同,七段数字显示器分为共阴极和共阳极接法两种。 (a)(b) 图6-54 七段数字显示器的内部接法 (a)共阳极(b)共阴极 图6-54(a)是共阳极接法,它是将七个发光二极管的阳极连在一起作公共端,使用时要接高电平。发光二极管的阴极经过限流电阻接到输出低电平有效的七段译码器相应的输出端。 图6-54(b)所示是共阴极接法,它是将七个发光二极管的阴极连在一起作公共端,使用时要接低电平。发光二极管的阳极经过限流电阻接到输出高电平有效的七段译码器相应的输出端。 改变限流电阻的阻值,可改变发光二极管电流的大小,从而控制显示器的发

用七段数码管显示简单字符

用七段数码管显示简单字符——译码器及其应 用 一、实验目的 1、了解显示译码器的结构和理解其工作原理。 2、学习7段数码显示译码器设计。 3、学习用基逻辑门、3-8译码器、4-1选择器控制显示器的显示。 二、实验内容 1、了解逻辑门、3-8译码器、4-1选择器的工作原理,设计基本电路,实现以下功能: C2C1C0是译码器的3个输入,用C2C1C0的不同取值来选择在七段数码管上输出不同字符。七段数码管是共阳极的。 图1 七段译码器 C2C1C0的不同取值对应显示的字母如下: 图2 字符编码

三、实验仪器及设备: 一、PC 机 二、 Quartus Ⅱ 9.0 三、 DE2-70 四、显示器 四、实验步骤 1、列出真值表,计算要实现以上功能时数码管的0-7段对应的逻辑函数式。 真值表如下: 函数表达式如下: “0”=' 02C C + “1”=“2”=0'1'012C C C C C ++ “3”=(2C +1C +'0C )(2C +0C +'1C )(2C +' 1C +'0C ) “4”=“5”=2C “6”=2C +1C +02C C 2、新建一个 quartusII 工程,用以在DE2_70平台上实现所要求的电路。 建立一个BDF 文件,基于SSI ,实现七段译码器电路,用SW3_SW1作为输入C2C1C0, DE2_70平台上的的数码管分别为HEX0~HEX7,输出接HEX1。 参照de2_70_pin_assignments.csv 中的引脚分配表配置引脚。 新建仿真文件,给出输入信号,观察输出信号是否符合要求。 编译工程,完成后下载到FPGA 中。 拨动波段开关并观察七段数码管HEX0的显示,以验证设计的功能是否正确。 基于3-8译码器和4-1选择器重复上述2.、中的步骤完成设计。

BCD-七段译码器设计

###课程设计 摘要 人类社会已进入到高度发达的信息化社会,信息社会的发展离不开电子产品的进步。现代电子产品在性能提高、复杂度增大的同时,价格却一直呈下降趋势,而且产品更新换代的步伐也越来越快,实现这种进步的主要原因就是生产制造技术和电子设计技术的发展。前者以微细加工技术为代表,目前已进展到深亚微米阶段,可以在几平方厘米的芯片上集成数千万个晶体管;后者的核心就是EDA技术。EDA是指以计算机为工作平台,融合了应用电子技术、计算机技术、智能化技术最新成果而研制成的电子CAD通用软件包,主要能辅助进行三方面的设计工作:IC设计,电子电路设计以及PCB设计。没有EDA技术的支持,想要完成上述超大规模集成电路的设计制造是不可想象的,反过来,生产制造技术的不断进步又必将对EDA技术提出新的要求。此设计是设计一个BCD-七段译码器,通过4个输入7个输出来显示0~9这10个数字。应用MAX+PLUSII软件,应用VHDL语言编程,实现上述功能。 关键字:EDA技术,电子设计自动化, MAX+PLUSII, VHDL语言

BCD-七段译码器 Abstract The human society entered to the highly developed informationization society, information society's development cannot leave the electronic products the progress. The modern electronic products while the performance enhances which, the order of complexity increases, the price has actually assumed the declining trend, moreover the product renewal's step is also getting quicker and quicker, realizes this kind of progressive primary cause is the manufacturing technology and the electron design technique development. The former take the tiny process technology as representative, at present progressed to the deep submicron stage, may integrate the many transistors on several square centimeters chips; The latter's core is EDA the technology. EDA is refers to take the computer as the working platform, fused the electronic CAD general software package which using the electronic technology, the computer technology, the intellectualized technology newest achievement develops, mainly can assist carries on three aspects the project works: IC design, electronic circuit design as well as PCB design. Does not have the EDA technology support, the wish to complete the above ultra large scale integrated circuit's design manufacture is cannot imagine, in turn, the manufacturing technology will progress unceasingly will certainly to set the new request to the EDA technology. This design is designs BCD- the decoder, inputs 7 through 4 to lose demonstrates 0~9 these 10 digit. Using the MAX+PLUSII software, applies the VHDL language programming, realizes the above function. key words: EDA technology,Electronic design automation, MAX+PLUSII, VHDL language

七段数码显示译码器电路的设计

WHEN "1001" => LED7s <="1101111"; WHEN "1010" => LED7s <="1110111"; WHEN "1011" => LED7s <="1111100"; WHEN "1100" => LED7s <="0111001"; WHEN "1101" => LED7s <="1011110"; WHEN "1110" => LED7s <="1111001"; WHEN "1111" => LED7s <="1110001"; WHEN OTHERS => NULL; END CASE; END PROCESS; END; 在完成源程序的编辑后,执行”Processing”菜单下的“Start Compilation”命令,对DECL7s.vhd进行编译。在完成对源文件的编译后,执行“File”菜单的“New”命令,或者直接按主窗口上的“创建新的文本文件”按钮,在弹出的新文件类型选择对话框中,选择“Vector Waveform File”生成仿真文件。 对引脚进行锁定。执行”Assignments”菜单下的“Pins”命令,根据下图进行引脚设置。 用电缆连接电脑与设备箱,执行”Tools”菜单下的“Programmer”命令,在弹出的对话框中,单击“Hardware Setup”并在新弹出的对话框中选择驱动,然后退出至上一层对话框,单击“Start”进行下载烧录。 【实验数据整理与归纳】

DECL7s11.vhd 实际效果图 DECL7s11.vwf 【实验结果与分析】 计数译码系统电路的仿真波形如图DECL7s.vwf所示,键值为"0000"时,数码管显示数值应为"0";键值为"0001"时,数码管显示数值应为"1",依此类推。仿真结果验证了设计的正确性。而实际情况与仿真结果相吻合。 【实验中遇到的问题及解决方案】 1.驱动安装失败。 解决方案:根据老师发的教程,更换别的方法进行安装。 2.虽然数码管显示数值正确,但对应按键与想象的有出入。 解决方案:经排查发现是管脚分配时颠倒了顺序导致的,按键时亦随之颠倒顺序即可。

实验一 七段数码显示译码器

实验一七段数码显示译码器 一、实验目的 1.学会的破解quartusII方法并破解机房电脑。 2.掌握七段数码管显示的工作原理并能够用verilog语言编程。 3.初步了解quartusII建立程序编译、仿真及下载的操作流程并学会七段数码显示译码器的 Verilog硬件设计。 二、实验原理 7段数码管是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能做十进制BCD译码,然而数字系统中的处理和运算都是二进制,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。本实验中的7段译码管输出信号LED7S的7位分别接数码管的7个段,高位在左,低位在右 三、实验内容 1、实现BCD/七段显示译码器的“ Verilog ”语言设计。 说明:7段显示译码器的输入为:IN0…IN3共4根, 7段译码器的逻辑表,同学自行设计,要求实现功能为:输入“ 0…15 ”(二进制)输出“ 0…9…F ”(显示数码),输出结果应在数码管(共阴)上显示出来。 2、使用工具为译码器建立一个元件符号 3、设计仿真文件,进行验证。 4、编程下载并在实验箱上进行验证。 四、实验步骤 第一步破解quartusII 1.在安装目录找到本机中关于quartusII的证书文件 2.运行未破解的quartusII,在【tools】>【license setup】路径下的倒数第三行中找到本机 网卡号并复制; 3.以记事本方式打开证书文件,在编辑替换中将证书文件中host id后面的号码替换为上一 步复制的内容,保存退出; 4.在quartusII中打开【tools】>【license setup】中找到证书所在路径并打开单击ok即完成 破解。 证书所在目录license setup选项

七段显示译码器7448

七段显示译码器7448功能,引脚图及应用电路 数字显示译码器是驱动显示器的核心部件,它可以将输入代码转换成相应的数字显示代码,并在数码管上显示出来。图8-51所示为七段显示译码器7448的引脚图,输入A3 、A2 、A1和A0接收四位二进制码,输出a~g为高电平有效,可直接驱动共阴极显示器,三个辅助控制端、、,以增强器件的功能,扩大器件应用。7448的真 值表如表8-20所示。 从功能表可以看出,对输入代码0000,译码条件是:灯测试输入和动态灭零输入同时等于1,而对其他输入代码则仅要求=1,这时候,译码器各段a~g输出的电平是由输入代码决定的,并且满 足显示字形的要求。 图8-51 7448引脚图

表8-20 7448功能表 灯测试输入低电平有效。当= 0时,无论其他输入端是什么状态,所有输出a~g均为1,显示字形8。该输入端常用于检查7448 本身及显示器的好坏。 动态灭零输入低电平有效。当=1,,且输入代码时,输出a ~g均为低电平,即与0000码相应的字形0不显示,故称“灭零”。 利用=1与= 0,可以实现某一位数码的“消隐”。 灭灯输入/动态灭零输出是特殊控制端,既可作输入,又可作输出。当作输入使用,且= 0时,无论其他输入端是什么电平,所有输出a~g均为0,字形熄灭。作为输出使用时,受和控制,只

有当,,且输入代码时,,其他情况下。该端主要用于显示多 位数字时多个译码器之间的连接。 【例8-13】七段显示器构成两位数字译码显示电路如图8-52所示。当输入8421BCD码时,试分析两个显示器分别显示的数码范围。 图8-52 两位数字译码显示电路解:图8-52所示的电路中,两片7448的均接高电平。由于7448(1)的,所以,当它的输入代码为0000时,满足灭零条件,显示器(1)无字形显示。7448(2)的,所以,当它的输入代码为0000时,仍能正常显示,显示器(2)显示0。而对其他输入代码,由于,译码器都可 以输出相应的电平驱动显示器。 根据上述分析可知,当输入8421BCD码时,显示器(1)显示的数码范围为1~9,显示器(2)显示的数码范围为0~9。 工作电压:5V

7段数码管显示电路

4.4 显示模块 4.4.1 7段数码管的结构与工作原理 7段数码管一般由8个发光二极管组成,其中由7个细长的发光二极管组成 数字显示,另外一个圆形的发光二极管显示小数点。 当发光二极管导通时,相应的一个点或一个笔画发光。控制相应的二极管导通,就能显示出各种字符,尽管显示的字符形状有些失真,能显示的数符数量也有限,但其控制简单,使有也方便。发光二极管的阳极连在一起的称为共阳极数码管,阴极连在一起的称为共阴极数码管,如图4.9所示。 4.4.2 7段数码管驱动方法 发光二极管(LED 是一种由磷化镓(GaP )等半导体材料制成的,能直接将电能转变成光能的发光显示器件。当其内部有一一电流通过时,它就会发光。 7段数码管每段的驱动电流和其他单个LED 发光二极管一样,一般为5~10mA ;正向电压随发光材料不同表现为1.8~2.5V 不等。 7段数码管的显示方法可分为静态显示与动态显示,下面分别介绍。 (1) 静太显示 所谓静态显示,就是当显示某一字符时,相应段的发光二极管恒定地寻能可截止。这种显示方法为每一们都需要有一个8位输出口控制。对于51单片机,可以在并行口上扩展多片锁存74LS573作为静态显示器接口。 静态显示器的优点是显示稳定,在发光二极管导通电注一定的情况下显示器的亮度高,控制系统在运行过程中,仅仅在需要更新显示内容时,CPU 才执行一次显示更新子程序,这样大大节省了CPU 的时间,提高了CPU 的工作效率;缺点是位数较多时,所需I/O 口太多,硬件开销太大,因此常采用另外一种显示方式——动态显示。

(2)动态显示 所谓动态显示就是一位一位地轮流点亮各位显示器(扫描),对于显示器的每一位而言,每隔一段时间点亮一次。虽然在同一时刻只有一位显示器在工作(点亮),但利用人眼的视觉暂留效应和发光二极管熄 灭时的余辉效应,看到的却是多个字符“同时”显示。显示器亮度既与点亮时的导通电流有关,也与点亮时间和间隔时间的比例有关。调整电流和时间参烽,可实现亮度较高较稳定的显示。若显示器的位数不大于8位,则控制显示器公共极电位只需一个8位I/O 口(称为扫描口或字位口),控制各位LED 显示器所显示的字形也需要一个8位口(称为数据口或字形口)。 动态显示器的优点是节省硬件资源,成本较低,但在控制系统运行过程中,要保证显示器正常显示,CPU 必须每隔一段时间执行一次显示子程序,这占用了CPU 的大量时间,降低了CPU 工作效率,同时显示亮度较静态显示器低。 综合以上考虑,由于温度显示为精确到小数点后两位,故只需4个数码管,又考虑到CPU 工作效率与电源效率,本毕业设计采用静态显示。为共阳极显示。 4.4.3 硬件编码 动74LS47是一款BCD 码转揣为7段输出的集成电路芯片,利用它可以直接驱动共阳 极的7段数码管。它的引脚分部和真值表分别下图。

BCD七段显示译码器的设计报告

实验二、BCD七段显示译码器的设计 一、实验目的 学习利用VHDL语言设计BCD七段显示译码器的方法,掌握BCD七段显示译码器的设计思路:掌握软件工具的使用方法。 二、实验原理 三、实验内容 1.用VHDL语言设计BCD七段显示译码器,进行编译、波形仿真及器件编程。(代码一详见附录)产生仿真波形如下:

BCD七段显示译码器仿真1 分析: 问:给定的代码驱动的是共阴极还是共阳极的七段数码管显示器? 由BCD七段显示译码器真值表可知是共阴极七段数码管显示器。 2.用VHDL语言设计3-8译码器,进行编译、波形仿真及器件编程。(代码二详 见附录)产生仿真波形如下:

3-8译码器仿真1 四、实验心得 在实验中,通过BCD七段显示译码器真值表真值表得到BCD七段显示译码器case 代码。同理通过8-3译码器真值表修改BCD七段显示译码器case代码得到8-3译码器case代码。 附录 代码一(BCD七段显示译码器代码): library ieee; use ieee.std_logic_1164.all; entity bcdym is port (a:in std_logic_vector(3 downto 0); y:out std_logic_vector(6 downto 0)); end bcdym; architecture zhang of bcdym is begin process(a) begin case a is when"0000"=>y<="0111111"; when"0001"=>y<="0000110";

when"0010"=>y<="1011011"; when"0011"=>y<="1001111"; when"0100"=>y<="1100110"; when"0101"=>y<="1101101"; when"0110"=>y<="1111101"; when"0111"=>y<="0100111"; when"1000"=>y<="1111111"; when"1001"=>y<="1101111"; when"1010"=>y<="1110111"; when"1011"=>y<="1111100"; when"1100"=>y<="0111001"; when"1101"=>y<="1011110"; when"1110"=>y<="1111001"; when others=>y<="1110001"; end case; end process; end zhang; 代码二(8-3译码器代码):library ieee; use ieee.std_logic_1164.all; entity bm3_8 is port(a:in std_logic_vector(0 to 2); b:out std_logic_vector(0 to 7)); end bm3_8; architecture zhang of bm3_8 is begin process(a) begin case a is when"000"=>b<="00000001"; when"001"=>b<="00000010"; when"010"=>b<="00000100"; when"011"=>b<="00001000"; when"100"=>b<="00010000"; when"101"=>b<="00100000"; when"110"=>b<="01000000"; when others =>b<="10000000"; end case; end process; end zhang;

十六进制七段数码显示译码器

十六进制七段数码显示译码器 一、实验目的:学习7段数码显示器的Verilog硬件设计。 二、实验原理:7段数码显示器是纯组合电路。通常的小规模专用IC,如74 或4000系列的器件只能做十进制BCD码译码器(其真值表如图(1)所示),然而数字系统中的数据处理和运算都是二进制的,所以输出表达式都是十六进制的,为了满足十六进制的译码显示,最方便的方法就是利用Verilog译码程序在FPGA/CPLD中来实现。所以首先要设计一段程序。设输入的4位码为A[3:0],输出控制7段共阴数码管(如图(2)所示)的7位数据为LED7S[6:0]。输出信号LED7S的7位接共阴数码管的7个段,高位在左,低位在右。例如当LED7S输出为“1101101”时,数码管7个段g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。 图(2)7段共阴数码管 三、实验任务:将设计好的Verilog译码器程序在Quartus II上进行编辑、 编译、综合、适配、仿真,给出其所有信号的时序仿真波形图(注意仿真波形输入激励信号的设置)。提示:设定仿真激励信号是用输入总线的方式给出输入信

号的仿真数据。 四、实验步骤: (一)、建立工作库文件和编辑设计文文件 任何一项设计都是一项Project(工程),而把一个工程下的所有文件放在一个文件夹内是一个非常好的习惯,以便于我们整理,利用和提取不同工程下的文件,而此文件夹将被EDA软件默认为Work Library(工作库),所以第一步先根据自己的习惯,建立个新的文件夹。 (1)新建文件夹:我的习惯在D盘建立并保存工程,我将文件夹取名Test, (2)输入源程序:打开Quartus II,选择菜单File-->New-->Design Files-->VerilogHDL File-->OK(如图1所示) 代码如下: module DECL7S(A,LED7S); input[3:0] A; output[6:0] LED7S; reg[6:0] LED7S; always@(A ) case(A) 4'b0000 :LED7S<=7'b0111111; 4'b0001 :LED7S<=7'b0000110; 4'b0010 :LED7S<=7'b1011011; 4'b0011 :LED7S<=7'b1001111; 4'b0100 :LED7S<=7'b1100110; 4'b0101 :LED7S<=7'b1101101; 4'b0110 :LED7S<=7'b1111101; 4'b0111 :LED7S<=7'b0000111; 4'b1000 :LED7S<=7'b1111111; 4'b1001 :LED7S<=7'b1101111; 4'b1010 :LED7S<=7'b1110111;

七段数码显示译码器设计

七段数码显示译码器设计 实验目的: 学习7段数码显示译码器设计,学习VHD啲多层次设计方法。 二、实验原理: 七段数码管由8个(a,b,c,d,e,f,g,dp )按照一定位置排列的发光二极管构成, 通常采取共阴极或者共阳极的设计,将8个二极管的同一极接在一起,通过分别控制另外的8个电极的电平,使二极管导通(发光)或截止(不发光)。 七段数码显示译码器的功能就是根据需要显示的字符,输出能够控制七段数 码管显示出该字符的编码。 三、实验内容: 1)用VHDL设计7段数码管显示译码电路,并在VHDL苗述的测试平台下对译码器进行功能仿真,给出仿真的波形。 CNT46 DECL7S A[.iu . 0] LED??[4B . ay rstG ObiitCl 程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY SMG IS PORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0); LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END; ARCHITECTURE ONE OF SMG IS BEGIN PROCESS(A) BEGIN

CASE A IS WHEN"0000"=>LED7S<="0111111"; WHEN"0001"=>LED7S<="0000110"; WHEN"0010"=>LED7S<="1011011"; WHEN"0011"=>LED7S<="1001111"; WHEN"0100"=>LED7S<="1100110"; WHEN"0101"=>LED7S<="1101101"; WHEN"0110"=>LED7S<="1111101"; WHEN"0111"=>LED7S<="0000111"; WHEN"1000"=>LED7S<="1111111"; WHEN"1001"=>LED7S<="1101111"; WHEN"1010"=>LED7S<="1110111"; WHEN"1011"=>LED7S<="1111100"; WHEN"1100"=>LED7S<="0111001"; WHEN"1101"=>LED7S<="1011110"; WHEN"1110"=>LED7S<="1111001"; WHEN"1111"=>LED7S<="1110001"; WHEN OTHERS=>NULL; END CASE; 仿真波形:

BCD七段数码管显示译码器电路

BCD七段数码管显示译码器电路 7段数码管又分共阴和共阳两种显示方式。如果把7段数码管的每一段都等效成发光二极管的正负两个极,那共阴就是把abcdefg这7个发光二极管的负极连接在一起并接地;它们的7个正极接到7段译码驱动电路74LS48的相对应的驱动端上(也是abcdefg)!此时若显示数字1,那么译码驱动电路输出段bc为高电平,其他段扫描输出端为低电平,以此类推。如果7段数码管是共阳显示电路,那就需要选用74LS47译码驱动集成电路。共阳就是把abcdefg的7个发光二极管的正极连接在一起并接到5V电源上,其余的7个负极接到74LS47相应的abcdefg输出端上。无论共阴共阳7段显示电路,都需要加限流电阻,否则通电后就把7段译码管烧坏了!限流电阻的选取是:5V电源电压减去发光二极管的工作电压除上10ma到15ma得数即为限流电阻的值。发光二极管的工作电压一般在1.8V--2.2V,为计算方便,通常选2V即可!发光二极管的工作电流选取在10-20ma,电流选小了,7段数码管不太亮,选大了工作时间长了发光管易烧坏!对于大功率7段数码管可根据实际情况来选取限流电阻及电阻的瓦数! 发光二极管(LED)由特殊的半导体材料砷化镓、磷砷化镓等制成,可以单独使用,也可以组装成分段式或点阵式LED显示器件(半导体显示器)。分段式显示器(LED数码管)由7条线段围成8型,每一段包含一个发光二极管。外加正向电压时二极管导通,发出清晰的光,有红、黄、绿等色。只要按规律控制各发光段的亮、灭,就可以显示各种字形或符号。图4 - 17(a)是共阴式LED数码管的原理图,图4-17(b)是其表示符号。使用时,公共阴极接地,7个阳极a~g由相应的BCD七段译码器来驱动(控制),如图4 - 17(c)所示。 BCD七段译码器的输入是一位BCD码(以D、C、B、A表示),输出是数码管各段的驱动信号(以F a~F g表示),也称4—7译码器。若用它驱动共阴LED数码管,则输出应为高有效,即输出为高(1)时,相应显示段发光。例如,当输入8421码DCBA=0100时,应显示,即要求同时点亮b、c、f、g段,熄灭a、d、e段,故译码器的输出应为F a~F g=0110011,这也是一组代码,常称为段码。同理,根据组成0~9这10个字形的要求可以列出8421BCD七段译码器的真值表,见表4 - 12(未用码组省略)。

BCD七段显示译码器

BCD七段显示译码器 1.什么是BCD码? 2.理解二进制?十进制?十六进制? BCD码(Binary-Coded Decimal?)也称二进码十进数或二-十进制代码。用4位二进制数来表示1位十进制数中的0~9这10个数码。是一种二进制的数字编码形式,用二进制编码的十进制代码。BCD码这种编码形式利用了四个位元来储存一个十进制的数码,使二进制和十进制之间的转换得以快捷的进行。这种编码技巧最常用于会计系统的设计里,因为会计制度经常需要对很长的数字串作准确的计算。相对于一般的浮点式记数法,采用BCD码,既可保存数值的精确度,又可免却使电脑作浮点运算时所耗费的时间。此外,对于其他需要高精确度的计算,BCD编码亦很常用。 发光二极管(LED)由特殊的半导体材料砷化镓、磷砷化镓等制成,可以单独使用,也可以组装成分段式或点阵式LED显示器件(半导体显示器)。分段式显示器(LED数码管)由7条线段围成0-9字型,每一段包含一个发光二极管。外加正向电压时二极管导通,发出清晰的光,有红、黄、绿等色。只要按规律控制各发光段的亮、灭,就可以显示各种字形或符号。 LED数码管有共阳、共阴之分。图 (a)是共阴式LED数码管的原理图,图 (b)是其表示符号。使用时,公共阴极接地,7个阳极a~g由相应的BCD七段译码器来驱动(控制),如图 (c)所示。 数字显示译码器

BCD七段译码器的输入是一位BCD码(以D、C、B、A表示),输出是数码管各段的驱动信号(以Fa~Fg表示),也称4—7译码器。若用它驱动共阴LED数码管,则输出应为高有效,即输出为高(1)时,相应显示段发光。例如,当输入8421码DCBA=0100时,应显示,即要求同时点亮b、c、f、g段,熄灭a、d、e 段,故译码器的输出应为Fa~Fg=0110011,这也是一组代码,常称为段码。同理,根据组成0~9这10个字形的要求可以列出8421BCD七段译码器的真值表,见表4 - 12(未用码组省略)。 BCD七段译码器就是根据上述原理组成的,只是为了使用方便,增加了一些辅助控制电路。这类集成译码器产品很多,类型各异,它们的输出结构也各不相同,因而使用时要予以注意。图(c)是BCD七段译码器驱动LED数码管(共阴)的接法。

七段显示译码器电路设计

题目:七段显示译码器电路设计专业:生产过程自动化专业 班级:生产过程0901 姓名: 学号: 指导老师:杨旭

目录 第一节绪论…………………………………………………………………………….. 1.1本设计的任务和主要内容……………………………………………………………….. 1.2基本工作原理及原理框图………………………………………………………………...第二节硬件电路的设计………………………………………………………………… 2.1BCD译码器选择与设计……………………………………………………………………. 2.2LED显示器的设计…………………………………………………………………………… 2.3总的设计……………………………………………………………………………………第四节设计总结………………………………………………………………………… 第一节绪论 本课程设计的七段译码器主要以BCD译码器或LED显示器为主要部件,应用集成门电路组成的一个具有译码和显示的装置。其中BCD 译码器采用8421BCD译码器,即----七段显示译码器(74LS48)型。LED显示器是由发光二极管组成的,LED显示器分共阴极和共阳极两种型号,共阴极LED显示器的发光二级管阴极接地,共阳极LED显示器的发光二极管阳极并联。最后把BCD译码器或LED显示器组成了的

装置就具有了显示和译码的功能。此七段译码器也就成功了。 1.1设计的任务和本主要内容 1)运用LED显示器或BCD译码器实现一定的功能 2)写出详细的实验报告 1.2基本工作原理及原理框图 基本工作原理及原理框图如下: 第二节硬件的设计 BCD译码器选择与设计 发光二极管(LED)由特殊的半导体材料砷化镓、磷砷化镓等制成,可以单独使用,也可以组装成分段式或点阵式LED显示器件(半导体显示器)。分段式显示器(LED数码管)由7条线段围成字型,每一段包含一个发光二极管。外加正向电压时二极管导通,发出清晰的光,有红、黄、绿等色。只要按规律控制各发光段的亮、灭,就可以显示各种字形或符号。 LED数码管有共阳、共阴之分。图4 - 17(a)是共阴式LED数码管的原理图,图4-17(b)是其表示符号。使用时,公共阴极接地,7个阳极a~g由相应的BCD七段译码器来驱动(控

完整word版EDA7段数码显示译码器设计精

EDA 技术实验报告 实验项目名称:7段数码显示译码器设计 实验日期:2012.06.04 实验成绩: 实验评定标准: 1)实验程序是否正确A()B()C() 2)实验仿真、结果及分析是否合理A()B()C() 3)实验报告是否按照规定格式A()B()C() 一、实验目的 学习7段数码显示译码器设计,学习VHDL的CASE语句应用及多层次设计方法。 二、实验器材 QuartusII7.2软件 三、实验内容(实验过程) (一). 1、首先设计一个2选1的数据选择器 (1)打开软件,选择菜单file—>new,在弹出的new对话框中选择Device Design Files 的VHDL File项,按OK键后进入VHDL文本编辑方式。 根据7段数码显示译码器的功能编辑相应的源程序。如下: library ieee; use ieee.std_logic_1164.all; entity decl7s is port (a:in std_logic_vector(3 downto 0; led7s:out std_logic_vector(6 downto 0; end decl7s; architecture one of decl7s is

begin process(a begin case a is when when when0=>led7s<=A1011; when1=>led7s<=@1111; when0=>led7s<=H0110; when1=>led7s<=H1101; when0=>led7s<=I1101; when1=>led7s<= when@0=>led7s<=I1111; when@1=>led7s<=H1111; whenA0=>led7s<=I0111; whenA1=>led7s<=I1100; whenH0=>led7s<=1001; whenH1=>led7s<=A1110; whenI0=>led7s<=I1001; whenI1=>led7s<=I1001; when others =>null; end case; end process; end one; 2、对该VHDL语言进行编辑后,无误后进行仿真。点击相应的编辑按钮用来检查源程序的正确性。 3.、编译和仿真 仿真前要新建波形文件:filenewother filesvector waveform file 点击OK后在出现的新建波形文件左边空白栏点击鼠标右键,选择insertinsert node or bus.在出现的对话框中直接点击node finder。之后,在出现的对话框中选择list。当左边的nodes found栏中出现设计文件的输入输出端口后,点击》加入到右边的selected node 中,点击OK。 在完成7段数码显示译码器源程序的编辑后,执行Processingstart compilation命令,对decl7s.vhd进行编译。 下图是7段数码显示译码器对应的仿真波形:

七段LED数码管显示电路设计(精)

实验七七段LED数码管显示电路设计 一、实验目的 1.学习EDA软件的基本操作 2.学习使用原理图进行设计输入 3.初步掌握软件输入、编译、仿真和编程的过程 4.学习实验开发系统的使用方法 二、实验说明 本实验通过七段LED数码管显示电路的设计,初步掌握EDA 设计方法中的设计输入、编译、综合、仿真和编程的基本过程。七段LED数码管显示电路有四个数据输入端(D0-D3),七个数据输出端(A-G。 三、实验要求 1、完成七段LED数码管显示电路的原理图输入并进行编译 2、对设计的电路经行仿真验证 3、编程下载并在实验开发系统上验证设计结果 四、实验步骤 1、新建工程 2、新建Verilog HDL文件 3、在文本输入窗口键入代码 4、保存HDL文件

5、编译文件直至没有错误 6、新建波形文件 7、添加观察信号 8、添加输入激励,保存波形文件 9、功能仿真 七段LED数码管显示电路真值表: 输入D3D2D1D0G F E D C B A 000000111111 100010000110 200101011011 300111001111 401001100110 501011101101 601101111101 701110001111 810001111111

910011101111 A10101110111 B10111111100 C11001111001 D110111011110 E11101111001 F11111110001五、电路原理图 啊Verilog代码描述: module qiduan(data_in,data_out; input [3:0]data_in; output [6:0]data_out; reg [6:0]data_out; always @(data_in begin casex(data_in 4'b0000:data_out<=7'b0111111;

十六进制七段数码显示译码器

十六进制七段数码显示译码器

十六进制七段数码显示译码器 一、实验目的:学习7段数码显示器的Verilog硬件设计。 二、实验原理:7段数码显示器是纯组合电路。通常的小规模专用IC,如74 或4000系列的器件只能做十进制BCD码译码器(其真值表如图(1)所示),然而数字系统中的数据处理和运算都是二进制的,所以输出表达式都是十六进制的,为了满足十六进制的译码显示,最方便的方法就是利用Verilog译码程序在FPGA/CPLD中来实现。所以首先要设计一段程序。设输入的4位码为A[3:0],输出控制7段共阴数码管(如图(2)所示)的7位数据为LED7S[6:0]。输出信号LED7S的7位接共阴数码管的7个段,高位在左,低位在右。例如当LED7S 输出为“1101101”时,数码管7个段g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。 图(1) 7段译码器真值表 输入码输入码代表 数据输入码输入 码 代表 数据 0000 0111111 0 1000 1111111 8 0001 0000110 1 1001 1101111 9 0010 1011011 2 1010 1110111 A 0011 1001111 3 1011 1111100 B 0100 1100110 4 1100 0111001 C 0101 1101101 5 1101 1011110 D 0110 1111101 6 1110 1111001 E 0111 0000111 7 1111 1110001 F 图(2)7段共阴数码管

实验译码显示电路

实验四译码显示电路 一、实验目的: 1、掌握中规模集成译码器的逻辑功能和使用方法 2、熟悉数码管的使用 二、实验仪器及器件: 1、数字电路实验箱、数字万用表、示波器。 2、器件:74LS48X1, 74LS194X1, 74LS73X1, 74LS00X2 三、实验预习: 1、复习有关译码显示原理。 2、根据实验任务,画出所需的实验线路及记录表格。 四、实验原理: 1、数码显示译码器: (1)七段发光二极管(LED)数码管 LED数码管是目前最常用的数字显示器,图(一)(a)、(b)为共阴管和共阳管的电路,(C)为两种不同出线形式的引出脚功能图。 一个LED数码管可用来显示一位0--9十进制数和一个小数点。小型数码管(0.5寸和0.36寸)每段发光二极管的正向压降,随显示光(通常为红、绿、黄、橙色)的颜色不同略有差别,通常约为2~2.5V,每个发光二极管的点亮电流在5~10mA。LED数码管要显示BCD 码所表示的十进制数字就需要有一个专门的译码器,该译码器不但要完成译码功能,还要有相当的驱动能力。

(2)BCD码七段译码驱动器 此类译码器型号有74LS47(共阳),74LS48(共阴),CC4511 (共阴)等,本实验系采用'74LS48 BCD码锁存/七段译码/驱 动器。驱动共阴极LED数码管。 图(二)为74LS48引脚排列。其中A、B、C、D - BCD码 输入端,a、b、c、d、e、f、g——译码输出端,输出“1" 有效,用来驱动共阴极LED数码管。 - 灯测试输入端,=“0”时,译码输出全为“1” - 灭零输入端,=“0”时,不显示多余的零。 /-作为输入使用时,灭灯输入控制端; 作为输出端使用时,灭零输出端。 2、扫描式显示 对多位数字显示采用扫描式显示可以节电,这一点在某些场合很重要。对于某些系统输出的的数据,应用扫描式译码显示,可使电路大为简化。有些系统,比如计算机,某些A/D 转换器,是以这样的形式输出数据的:由选通信号控制多路开关,先后送出(由高位到低位或由低位到高位)一位十进制的BCD码,如图(三)所示。图中的Ds称为选通信号,并假定系统按先高位后低位的顺序送出数据,当Ds1高电平送出千位数,Ds2高电平送出百位数,……一般Ds的高电平相邻之间有一定的间隔,选通信号可用节拍发生器产生。 如图(四)所示,为这种系统的译码扫描显示的原理图。图中各片LED(共阴)的发光段并连接至译码器的相应端,把数据输入的相应权端与系统输出端相连,把各位选通端反相后接相应LED的公共端。f(A)使数据输入是伪码(8421BCD中的1010-1111)时使f(A)=0,伪码灭灯。接译码器的灭灯I B端,使不显示伪码。 3、四节拍发生器 扫描显示要求数码管按先后顺序显示。这就要求如图(三)所示的选通信号。通常该类型的信号称为节拍信号。如果使用的数码管是共阴极型,则选通信号是图(三)的反相。如图(五)所示就是这种节拍信号发生器。