FPGA设计的四种常用思想与技巧乒乓操作

FPGA设计的四种常用思想与技巧

王诚 Lattice Semiconductor

本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。

FPGA/CPLD的设计思想与技巧是一个非常大的话题,由于篇幅所限,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口的同步方法。希望本文能引起工程师们的注意,如果能有意识地利用这些原则指导日后的设计工作,将

取得事半功倍的效果!

乒乓操作

“乒乓操作”是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如图1所示。

乒乓操作的处理流程为:输入数据流通过“输入数据选择单元”将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM(DPRAM)、

单口RAM(SPRAM)、FIFO等。在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”;在第2个缓冲周期,通过“输入数据选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,同时将“数据缓冲模块1”缓存的第1个周期数据通过“输入数据选择单元”的选择,送到“数据流运算处理模块”进行运算处理;在第3个缓冲周期通过“输入数据选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,同时将“数据缓冲模块2”缓存的第2个周期的数据通过“输入数据选择单元”切换,送到“数据流运算处理模块”进行运算处理。如此循环。

乒乓操作的最大特点是通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。所以乒乓操作常常应用于流水线式算法,完成数据的无缝缓冲与处理。

乒乓操作的第二个优点是可以节约缓冲区空间。比如在WCDMA基带应用中,1个帧是由15

个时隙组成的,有时需要将1整帧的数据延时一个时隙后处理,比较直接的办法是将这帧数据缓存起来,然后延时1个时隙进行处理。这时缓冲区的长度是1整帧数据长,假设数据速率是3.84Mbps,1帧长10ms,则此时需要缓冲区长度是38400位。如果采用乒乓操作,只

需定义两个能缓冲1个时隙数据的RAM(单口RAM即可)。当向一块RAM写数据的时候,从另

一块RAM读数据,然后送到处理单元处理,此时每块RAM的容量仅需2560位即可,

2块RAM加起来也只有5120位的容量。

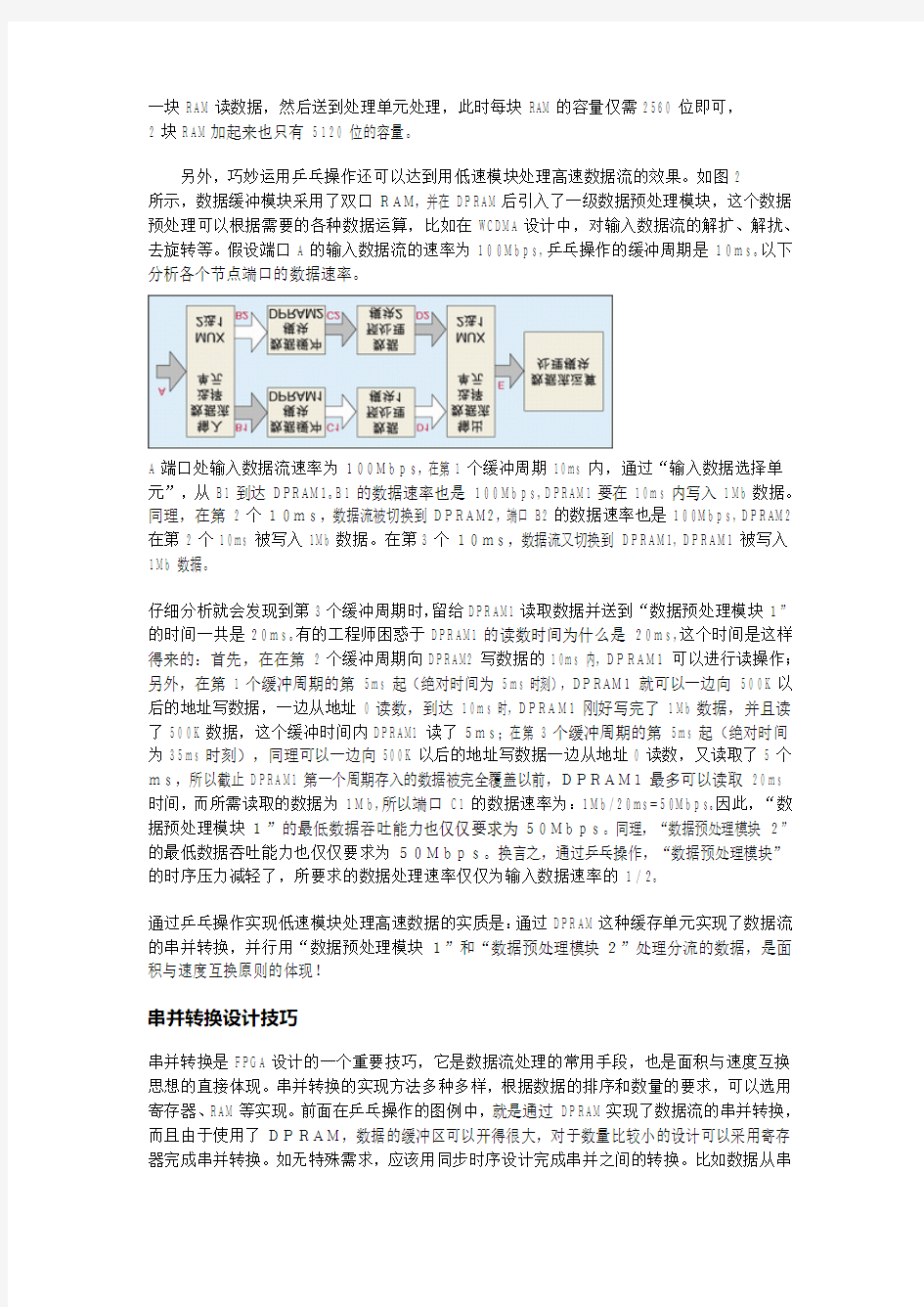

另外,巧妙运用乒乓操作还可以达到用低速模块处理高速数据流的效果。如图2

所示,数据缓冲模块采用了双口RAM,并在DPRAM后引入了一级数据预处理模块,这个数据预处理可以根据需要的各种数据运算,比如在WCDMA设计中,对输入数据流的解扩、解扰、去旋转等。假设端口A的输入数据流的速率为100Mbps,乒乓操作的缓冲周期是10ms。以下分析各个节点端口的数据速率。

A端口处输入数据流速率为100Mbps,在第1个缓冲周期10ms内,通过“输入数据选择单元”,从B1到达DPRAM1。B1的数据速率也是100Mbps,DPRAM1要在10ms内写入1Mb数据。同理,在第2个10ms,数据流被切换到DPRAM2,端口B2的数据速率也是100Mbps,DPRAM2在第2个10ms被写入1Mb数据。在第3个10ms,数据流又切换到DPRAM1,DPRAM1被写入1Mb数据。

仔细分析就会发现到第3个缓冲周期时,留给DPRAM1读取数据并送到“数据预处理模块1”的时间一共是20ms。有的工程师困惑于DPRAM1的读数时间为什么是20ms,这个时间是这样得来的:首先,在在第2个缓冲周期向DPRAM2写数据的10ms内,DPRAM1可以进行读操作;另外,在第1个缓冲周期的第5ms起(绝对时间为5ms时刻),DPRAM1就可以一边向500K以后的地址写数据,一边从地址0读数,到达10ms时,DPRAM1刚好写完了1Mb数据,并且读了500K数据,这个缓冲时间内DPRAM1读了5ms;在第3个缓冲周期的第5ms起(绝对时间为35ms时刻),同理可以一边向500K以后的地址写数据一边从地址0读数,又读取了5个ms,所以截止DPRAM1第一个周期存入的数据被完全覆盖以前,DPRAM1最多可以读取20ms时间,而所需读取的数据为1Mb,所以端口C1的数据速率为:1Mb/20ms=50Mbps。因此,“数据预处理模块1”的最低数据吞吐能力也仅仅要求为50Mbps。同理,“数据预处理模块2”的最低数据吞吐能力也仅仅要求为50Mbps。换言之,通过乒乓操作,“数据预处理模块”的时序压力减轻了,所要求的数据处理速率仅仅为输入数据速率的1/2。

通过乒乓操作实现低速模块处理高速数据的实质是:通过DPRAM这种缓存单元实现了数据流的串并转换,并行用“数据预处理模块1”和“数据预处理模块2”处理分流的数据,是面积与速度互换原则的体现!

串并转换设计技巧

串并转换是FPGA设计的一个重要技巧,它是数据流处理的常用手段,也是面积与速度互换思想的直接体现。串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用寄存器、RAM等实现。前面在乒乓操作的图例中,就是通过DPRAM实现了数据流的串并转换,而且由于使用了DPRAM,数据的缓冲区可以开得很大,对于数量比较小的设计可以采用寄存器完成串并转换。如无特殊需求,应该用同步时序设计完成串并之间的转换。比如数据从串

行到并行,数据排列顺序是高位在前,可以用下面的编码实现:

prl_temp<={prl_temp,srl_in};

其中,prl_temp是并行输出缓存寄存器,srl_in是串行数据输入。对于排列顺序有规定的串并转换,可以用case语句判断实现。对于复杂的串并转换,还可以用状态机实现。串并转换的方法比较简单,在此不必赘述。

流水线操作设计思想

首先需要声明的是,这里所讲述的流水线是指一种处理流程和顺序操作的设计思想,并非FPGA、ASIC设计中优化时序所用的“Pipelining”。

流水线处理是高速设计中的一个常用设计手段。如果某个设计的处理流程分为若干步骤,而且整个数据处理是“单流向”的,即没有反馈或者迭代运算,前一个步骤的输出是下一个步骤的输入,则可以考虑采用流水线设计方法来提高系统的工作频率。

流水线设计的结构示意图如图3所示。其基本结构为:将适当划分的n个操作步骤单流向串联起来。流水线操作的最大特点和要求是,数据流在各个步骤的处理从时间上看是连续的,如果将每个操作步骤简化假设为通过一个D触发器(就是用寄存器打一个节拍),那么流水线操作就类似一个移位寄存器组,数据流依次流经D触发器,完成每个步骤的操作。流水线设计时序如图4所示。

流水线设计的一个关键在于整个设计时序的合理安排,要求每个操作步骤的划分合理。如果前级操作时间恰好等于后级的操作时间,设计最为简单,前级的输出直接汇入后级的输入即可;如果前级操作时间大于后级的操作时间,则需要对前级的输出数据适当缓存才能汇入到后级输入端;如果前级操作时间恰好小于后级的操作时间,则必须通过复制逻辑,将数据流分流,或者在前级对数据采用存储、后处理方式,否则会造成后级数据溢出。

在WCDMA设计中经常使用到流水线处理的方法,如RAKE接收机、搜索器、前导捕获等。流水线处理方式之所以频率较高,是因为复制了处理模块,它是面积换取速度思想的又一种具体体现。

数据接口的同步方法

数据接口的同步是FPGA/CPLD设计的一个常见问题,也是一个重点和难点,很多设计不稳定都是源于数据接口的同步有问题。

在电路图设计阶段,一些工程师手工加入BUFT或者非门调整数据延迟,从而保证本级模块的时钟对上级模块数据的建立、保持时间要求。还有一些工程师为了有稳定的采样,生成了很多相差90度的时钟信号,时而用正沿打一下数据,时而用负沿打一下数据,用以调整数据的采样位置。这两种做法都十分不可取,因为一旦芯片更新换代或者移植到其它芯片组的芯片上,采样实现必须从新设计。而且,这两种做法造成电路实现的余量不够,一旦外界条件变换(比如温度升高),采样时序就有可能完全紊乱,造成电路瘫痪。

下面简单介绍几种不同情况下数据接口的同步方法:

1. 输入、输出的延时(芯片间、PCB布线、一些驱动接口元件的延时等)不可测,或者有可能变动的条件下,如何完成数据同步?

对于数据的延迟不可测或变动,就需要建立同步机制,可以用一个同步使能或同步

指示信号。另外,使数据通过RAM或者FIFO的存取,也可以达到数据同步目的。

把数据存放在RAM或FIFO的方法如下:将上级芯片提供的数据随路时钟作为写信号,

将数据写入RAM或者FIFO,然后使用本级的采样时钟(一般是数据处理的主时钟)将数据读出来即可。这种做法的关键是数据写入RAM或者FIFO要可靠,如果使用同步RAM或者FIFO,就要求应该有一个与数据相对延迟关系固定的随路指示信号,这个信号可以是数据的有效指示,也可以是上级模块将数据打出来的时钟。对于慢速数据,也可以采样异步RAM或者FIFO,但是不推荐这种做法。

数据是有固定格式安排的,很多重要信息在数据的起始位置,这种情况在通信系统中非常普遍。通讯系统中,很多数据是按照“帧”组织的。而由于整个系统对时钟要求很高,常常专门设计一块时钟板完成高精度时钟的产生与驱动。而数据又是有起始位置的,如何完成数据的同步,并发现数据的“头”呢?

数据的同步方法完全可以采用上面的方法,采用同步指示信号,或者使用RAM、FIFO缓存一下。找到数据头的方法有两种,第一种很简单,随路传输一个数据起始位置的指示信号即可,对于有些系统,特别是异步系统,则常常在数据中插入一段同步码(比如训练序列),接收端通过状态机检测到同步码后就能发现数据的“头”了,这种做法叫做“盲检测”。

上级数据和本级时钟是异步的,也就是说上级芯片或模块和本级芯片或模块的时钟是异步时钟域的。

前面在输入数据同步化中已经简单介绍了一个原则:如果输入数据的节拍和本级芯片的处理时钟同频,可以直接用本级芯片的主时钟对输入数据寄存器采样,完成输入数据的同步化;如果输入数据和本级芯片的处理时钟是异步的,特别是频率不匹配的时候,则只有用处理时钟对输入数据做两次寄存器采样,才能完成输入数据的同步化。需要说明的是,用寄存器对异步时钟域的数据进行两次采样,其作用是有效防止亚稳态(数据状态不稳定)的传播,使后级电路处理的数据都是有效电平。但是这种做法并不能保证两级寄存器采样后的数据是正确的电平,这种方式处理一般都会产生一定数量的错误电平数据。所以仅仅适用于对少量错误不敏感的功能单元。

为了避免异步时钟域产生错误的采样电平,一般使用RAM、FIFO缓存的方法完成异步时钟域的数据转换。最常用的缓存单元是DPRAM,在输入端口使用上级时钟写数据,在输出端口使用本级时钟读数据,这样就非常方便的完成了异步时钟域之间的数据交换。

2. 设计数据接口同步是否需要添加约束?

建议最好添加适当的约束,特别是对于高速设计,一定要对周期、建立、保持时间等添加相应的约束。

这里附加约束的作用有两点:

a. 提高设计的工作频率,满足接口数据同步要求。通过附加周期、建立时间、保持时间等约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率,满足接口数据同步要求。

b. 获得正确的时序分析报告。几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对设计的性能做出评估。静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。

Xilinx和数据接口相关的常用约束有Period、OFFSET_IN_BEFORE、OFFSET_IN_AFTER、OFFSET_OUT_BEFORE和OFFSET_OUT_AFTER等;Altera与数据接口相关的常用约束有Period、tsu、tH、tco等。

FPGA硬件实战设计经验

TR_Con_ZD板卡设计经验总结 针对TR板卡的PCB布线一根线未动想到的TR板卡bank分配方法介绍 与原来在华为工作的师兄(他做的TR板卡的PCB)聊了一下,他说TR板卡的FPGA线序一根都没改。Bank分配是我来做的,原则是方便PCB走线。分配时候是参考下面的资料来分配的。 TR板卡结构图 XC6VSX315T-FF1759的bank管脚分布图

的上方,因此将FPGA逆时针转90°,如下图所示,这样PCB布线就比较方便了。

分配bank的时候没有考虑Bank在FPGA内部的分布图,如下图所示:

想到的硬件设计流程的东西 师兄说:“动一根线的话,都需要FPGA程序重新跑一遍,这需要浪费很多时间。”FPGA 程序?TR板卡的程序还没有呢!的确值得思考了,到底这个设计应该是按照怎样的一个流程。 在华为,是按照这样的流程进行的。 1.硬件设计人员将IO需求,板卡供电等情况反馈给逻辑设计人员 2.逻辑人员对所需的FPGA资源做评估,最终确定FPGA型号(硬件设计人员也可以参与 一起选型) 3.逻辑设计人员对FPGA进行bank分配,需要以下资源: a)硬件设计人员提供硬件设计框图 b)最好对所用的IO先画一个自己根据原理图框图分配的bank的原理图草图,导入 PCB后进行一下预布局,这样信号流程就清晰了。 逻辑人员根据上述资源进行bank的分配,因为他们对FPGA内部的资源最清楚。逻辑人员要兼顾PCB布局布线的方便,有时候不可能照顾都到布局布线的方便。这时候,就需要在硬件设计人员和FPGA设计人员之间来回折腾,最终兼顾双方,得到一个bank 分配方案。 4.FPGA人员根据bank分配,写一个测试评估的程序,如果能够跑通,时序满足设计需求, 说明现在的bank分配可以使用,如果出现严重的时序错误,那么就需要考虑重新分配bank,通过不断地调整,最终确定板卡的bank分配。 5.根据最终的bank分配方案设计原理图。

乒乓ram介绍

乒乓ram简介 在现在的数据采集分析系统中,随着采集数据的速度剧增,每次都对这些庞大的数据量直接进行分析,这将会占用很多的CPU,使得CPU不能及时的去做其它的事情。我们可以在传输这些数据的时候提供适当的通道,建立一个缓冲电路,来实现数据流的无缝缓存和处理,提高系统的处理速度和性能。输入输出缓存电路一般有三种结构和形式: ①双口ram结构:双口RAM是在一个SRAM存储器上具有两套完全独立的数据线、地址线、读写控制线、并允许两个独立的系统同时对该存储器进行随机访问。 ②FIFO结构:FIFO(First In First Out)是一种先进先出的数据缓存器,可以进行双端操作,但是数据必须先进先出,不能进行随机性的访问。 从容量大小来看,双口RAM比FIFO要大一些,但总的来说,这两种缓冲结构的存储容量还是相对较小,对高速图像处理系统而言,还不是特别适合。 ③乒乓ram结构:这种结构是将输入数据流通过输入数据选择单元等时地将数据流分配到两个ram缓冲区。通过两个ram读和写的切换,来实现数据的流水式传输。 综上所述,乒乓缓存结构实际上相当于一个双口RAM,但它与普通的双口RAM又有所不同。普通双口RAM是单个存储体构成的IC,乒乓ram结构则由包含两个相互独立存储体的多片IC构成,从而使其在结构、速度、容量等方面具有更大的灵活性;若双口在访问同一地址时,普通双口SAM指向的必定是存储体内的同一存储单元,而乒乓ram结构则分别指向属于SRAM1和SRAM2的两个不同的存储单元,更易操作。乒乓缓存结构的上述特点决定了可以相对较便宜的高速大容量SRAM、外围逻辑器件构成比双口RAM以及高速FIFO更适合视频处理的系统所需要的缓冲存储器。 乒乓ram结构的上述特点决定了可以相对较便宜的高速大容量RAM、外围逻辑器件构成比双口RAM以及高速FIFO更适合大数据传输系统所需要的缓冲存储器。 乒乓ram控制原理 "乒乓操作"是一个常用的数据流控制处理技巧。典型的乒乓操作结构如图1所示。 图1 乒乓操作结果示意图 乒乓操作的处理流程为:输入数据流通过输入数据选择单元将数据流等时分配到两个数据缓冲区,数据缓冲模块一般为ram。在第一个缓冲周期,将输入的数据流缓存到数据缓冲模块ram A;在第2个缓冲周期,通过输入数据选择单元的切换,将输入的数据流缓存到数据缓冲模块ram B,同时将ram A缓存的第1个周期数据传给输出数据选择单元。在第3个缓冲周期通过输入数据选择单元的再次切换,将输入的数据流缓存到ram A同时将ram B缓存的第2个周期的数据传给输出数据选择单元。如此循环。 乒乓操作的最大特点是通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连

FPGACPLD数字电路设计经验

FPGA/CPLD数字电路设计经验分享 摘要:在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。 关键词:FPGA数字电路时序时延路径建立时间保持时间 1 数字电路设计中的几个基本概念: 1.1 建立时间和保持时间: 建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间 注:在考虑建立保持时间时,应该考虑时钟树向后偏斜的情况,在考虑建立时间时应该考虑时钟树向前偏斜的情况。在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间。 建立时间的约束和时钟周期有关,当系统在高频时钟下无法工作时,降低时钟频率就可以使系统完成工作。保持时间是一个和时钟周期无关的参数,如果设计不合理,使得布局布线工具无法布出高质量的时钟树,那么无论如何调整时钟频率也无法达到要求,只有对所设计系统作较大改动才有可能正常工作,导致设计效率大大降低。因此合理的设计系统的时序是提高设计质量的关键。在可编程器件中,时钟树的偏斜几乎可以不考虑,因此保持时间通常都是满足的。

基于FPGA双RAM乒乓操作的数据存储系统的研究_图文(精)

科技信息。机械与电子o2010年第2l期基于FPGA双RAM乒乓操作的 数据存储系统的研究 钱黄生1夏忠珍z 11。中国电子科技集团公司第四十一研究所山东青岛266555;2.南京立汉化学有限公.-3江苏南京211102l 【搐要】本文阐速了在对实时性要求较高,而对数据存储深度要求不高的数据采集系统中,用FPGA构建双RAM来乒乓存储数据的方法,重点介绍了乒乓操作的控制方法。本方法在XILINX9.1软件中通过时序仿真。并且通过XC2VP20验证了本方法完全能够满足设计的要求。 【关键词】FPGA;KAM;乒乓操作 0引言 经过70年的不断发展,FPGA已由当初的1200门发展成为今天 的百万门级。通过不断更新优化产品架构和生产工艺,实现了更多的 逻辑单元、更高的性能、更低的单位成本和功耗【11。 本文用到的FPGA是xilinx公司Virtex-Il Pro家族的xc2vp20芯 片,它包含2个POWER PC处理器.20880个cell.多达290KB的分布 式RAM以及88个18KB的Block RAM嘲。由于本系统的存储深度不 大,所以采用FPGA片内资源来构建RAM。这样效率更高.且使用方 便,而且还可以避免板级信号干扰。既节省了印制板空间又节约了成 本。

1乒乓操作原理 乒乓操作口棚是种经常应用于数据流控制的处理方法。图l是它的典型操作示意图。 乒乓操作的处理流程为:输人数据流通过“输入数据选择单元”将 数据流等时分配到两个数据缓冲区.数据缓冲模块选择双口RAM (DPRAM或单r】RAM,FIFO等。在第一个周期,将输入的数据流缓存到。数据暂存单元1”:在第2个周期,通过“输人数据选择单元”的切换,将输入的数据流缓存到“数据暂存单元2”,同时将“数据暂存单元1”缓存的第1个周期数据通过“输出数据选择单元”的选择。输送到“数据处理单元”即上位机凄走进行处理;在第3个缓冲周期通过“输 人数据选择单元”的再次切换,将输入的数据流缓存到“数据暂存单元1”,同时将“数据暂存单元2”缓存的第2个周期的数据通过“输出数 据选择单元”切换,输送到“数据处理单元”进行运算处理。如此循环。输入输出数 数据据 数据刊l(D骱PRA甑M1} 选择选择处 单元单元理 堕

典型的FPGA设计开发流程

典型的FPGA 设计开发流程 (2011-10-02 16:08:17) 标签: 杂谈 分类: 专业总结 FPGA 的设计流程就是利用EDA 开发软件和编程工具对FPGA 芯片进行开发的过程。FPGA 的开发流程一般如图1所示,包括电路设计、设计输入、功能仿真、综合优化、综合后仿真、实现、布线后仿真、板级仿真以及芯片编程与调试等主要步骤。 图1 FPGA 开发的一般流程 1. 电路功能设计 在系统设计之前,首先要进行的是方案论证、系统设计和FPGA 芯片选择等准备工作。系统工程师根

据任务要求,如系统的指标和复杂度,对工作速度和芯片本身的各种资源、成本等方面进行权衡,选择合理的设计方案和合适的器件类型。一般都采用自顶向下的设计方法,把系统分成若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接使用EDA元件库为止。 2.设计输入 设计输入是将所设计的系统或电路以开发软件要求的某种形式表示出来,并输入给EDA工具的过程。常用的方法有硬件描述语言(HDL)和原理图输入方法等。原理图输入方式是一种最直接的描述方式,在可编程芯片发展的早期应用比较广泛,它将所需的器件从元件库中调出来,画出原理图。这种方法虽然直观并易于仿真,但效率很低,且不易维护,不利于模块构造和重用。更主要的缺点是可移植性差,当芯片升级后,所有的原理图都需要作一定的改动。目前,在实际开发中应用最广的就是HDL语言输入法,利用文本描述设计,可以分为普通HDL和行为HDL。普通HDL有ABEL、CUR 等,支持逻辑方程、真值表和状态机等表达方式,主要用于简单的小型设计。而在中大型工程中,主要使用行为HDL,其主流语言是Verilog HDL和VHDL。这两种语言都是美国电气与电子工程师协会(IEEE)的标准,其共同的突出特点有:语言与芯片工艺无关,利于自顶向下设计,便于模块的划分与移植,可移植性好,具有很强的逻辑描述和仿真功能,而且输入效率很高。 3.功能仿真 功能仿真,也称为前仿真,是在编译之前对用户所设计的电路进行逻辑功能验证,此时的仿真没有延迟信息,仅对初步的功能进行检测。仿真前,要先利用波形编辑器和HDL等建立波形文件和测试向量(即将所关心的输入信号组合成序列),仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化。如果发现错误,则返回设计修改逻辑设计。常用的工具有Model Tech公司的ModelSim、Sysnopsys公司的VCS和Cadence公司的NC-Verilog以及NC-VHDL等软件。虽然功能仿真不是FPGA开发过程中的必需步骤,但却是系统设计中最关键的一步。

FPGA学习心得

回想起自己学FPGA,已经有一段时间了,从开始的茫然,到后来的疯狂看书,设计开发板,调电路,练习各种FPGA实例,到最后能独立完成项目,一路走来,感受颇多,拿出来和大家分享,顺便介绍下自己的一点经验所得,希望对初学者有所帮助。 废话不说了,下面进入正题,学习FPGA我主要经历了这么几个阶段: ①、Verilog语言的学习,熟悉Verilog语言的各种语法。 ②、FPGA的学习,熟悉QuartusII软件的各种功能,各种逻辑算法设计,接口模块(RS232,LCD,VGA,SPI,I2c等)的设计,时序分析,硬件优化等,自己开始设计简单的FPGA 板子。 ③、NiosII的学习,熟悉NiosII的开发流程,熟悉开发软件(SOPC,NiosII IDE),了解NiosII 的基本结构,设计NiosII开发板,编写NiosII C语言程序,调试板子各模块功能。先来说说第一个阶段,现在主要的硬件描述语言有VHDL,Verilog两种,在本科时老师一般教VHDL,不过现在 Verilog用的人越来越多,其更容易上手(与C语言语法比较类似),也更灵活,现在的IC设计基本都用Verilog。像systemC,systemVerilog之类的应该还在萌芽阶段,以后可能会有较大发展。鉴于以上原因我选择了Verilog作为我学习的硬件描述语言。 其实有C语言的基础,学起Verilog的语言很简单,关键要有并行的概念,所有的module,assign,always都是并行的,这一点与软件语言有明显不同。这里推荐几本评价比较好的学习Verilog的书籍: ①、《verilog 数字系统设计教程》,这本书对于入门是一本很好的书,通俗易懂,让人很快上手,它里面的例子也不错。但本书对于资源优化方面的编程没有多少涉及到。 ②、《设计与验证Verilog HDL》,这本书虽然比较薄,但是相当精辟,讲解的也很深入,很多概念看了这本书有种豁然开朗的感觉,呵呵。 学习Verilog其实不用看很多书,基本的语法部分大家都一样,关键是要自己会灵活应用,多做练习。 Verilog语言学了一段时间,感觉自己可以编点东西,希望自己编的程序在板子上运行看看结果,下面就介绍我学习的第二个阶段。 刚开始我拿了实验室一块CPLD的开发板做练习,熟悉QuartusII的各种功能,比如IP的调用,各种约束设置,时序分析,Logiclock设计方法等,不过做到后面发现CPLD 的资源不太够(没有内嵌的RAM、不能用SignalTapII,LE太少等),而实验室没有FPGA开发板,所以就萌生了自己做FPGA开发板的意图,刚好Cadence我也学的差不多了,就花了几天时间主要研究了FPGA配置电路的设计,在板子上做了Jtag和AS下载口,在做了几个用户按键和LED,其他的口全部引出作为IO口,电路比较简单,板子焊好后一调就通了(心里那个爽啊...)。我选的FPGA是cycloneII系列的EP2C5,资源比以前的FPGA多了好几倍,还有PLL,内嵌的RAM,可以试试SignalTapII,用内嵌的逻辑分析仪测试引脚波形,对于FPGA的调试,逻辑分析仪是至关重要的。利用这块板子我完成了项目中的几个主要功能:RS232通信,指令译码,配置DDS,AD数据高速缓存,电子开关状态设置等,在实践中学习起来真的比平时快很多,用到什么学什么动力更大。这个时候我主要看的数据有这几本感觉比较好: ①、《Altera FPGA/CPLD 设计(基础篇)》:讲解一些基本的FPGA设计技术,以及QuartusII中各个工具的用法(IP,RTL,SignalProbe,SignalTapII,Timing Closure Floorplan,chip Editor等),对于入门非常好。 ②、《Altera FPGA/CPLD 设计(高级篇)》:讲解了一些高级工具的应用,LogicLock,时序约束很分析,设计优化,也讲述了一些硬件编程的思想,作为提高用。

一个合格的FPGA工程师需要掌握哪些知识

一个合格的FPGA工程师需要掌握哪些知识?这里根据自己的一些心得总结一下,其他朋友可以补充啊。 1.Verilog语言及其于硬件电路之间的关系。 2.器件结构(最好熟练掌握Spartan3,Vertix4系列的器件结构,及其资源于Verilog行为描述方法的关系。)。 3.开发工具(熟练掌握Synplify,Quartus,ISE,Modelsim)。 4.数字电路(组合电路,触发器,特别是D触发器构成分频器,奇数倍分频占空比为50%,时序电路,并且能用Verilog语言描叙。)。 5.熟悉FPGA设计流程(仿真,综合,布局布线,时序分析)。 6.熟练掌握资源估算(特别是slice,lut,ram等资源的估算)。 7.同步设计原理。 8.熟练掌握基本概念(如建立时间,保持时间,流量(即所做FPGA设计的波特率)计算,延迟时间计算(所做FPGA设计),竞争冒险,消除毛刺的方法等等)。 9.具备具体设计经验(对应届生而言如毕业设计)。 10.良好的设计思路(流水线设计即熟称打拍子,在速率资源功耗之间的折中考虑)。 一个合格的FPGA工程师至少在以下三个方面的一个非常熟悉: 1.嵌入式应用 2.DSP应用 3.高速收发器应用 将自己的走过的弯路和总结的经验与大家分享一下,希望对您有一点点

的参考价值。 首先从先从如何成为一个合格的设计者说起吧!初学者觉得一切都是挑战,一切都新鲜,不知从何处下手。我总结了学习EDA逻辑设计的4个步骤,请拍砖! 1。首先,应该好好学习一下FPGA/CPLD的设计设计流程。 不要简单的以为就是设计输入-》仿真-》综合-》实现那么一回事,要抠细,要学精,要多问每个步骤的注意事项,区分相关步骤的联系和区别。比如要搞清楚功能仿真、综合后仿真、Translate后仿真、Map 后的仿真、布局布线后仿真的作用都是什么,什么时候应该做,什么时候可以不做这些仿真!学习清楚了设计流程最大的好处就是有利于培养良好的EDA设计习惯,日后会受益非浅! 2。关于设计输入和Coding Style。 设计输入最好学习HDL语言,Verilog、VHDL都可以,可以把状态机输入和原理图输入作为补充内容,但不是重点。我在前面的帖子已经反复强调了Coding Style的重要性。因为它是逻辑设计人员的一个基本业务素质。而且Coding Style不是看几篇文章,学几条原则就能够成为高手的,他需要您在工作中不断的体会和积累,在学习的最初,有Coding Style的意识,设计者就会有意的积累,对日后发展很有好处。反之则后患无穷。 3。培养硬件的意识,培养系统的观念。 我也在交流和授课的时候很强调硬件意识,如果从形式上看,逻辑设计随着智能化和优化手段的不断发展最后会越来越灵活,越来越简单。比

嵌入式USB主从设备控制器SL811中文翻译

Sl811HS嵌入式USB主/从设备控制器 目录 1.0 规定 2.0 定义 3.0 参考 4.0 介绍 4.1 块图表 4.2 sl811hs 主从模式选择 4.3 特性 4.4 数据口微处理器接口 4.5 中断控制器 4.6 缓冲器 4.7 PLL时钟发生器 4.8 USB传输器 5.0 SL811HS寄存器 5.1 开机和复位的寄存器值 5.2 USB控制寄存器 5.3 SL811HS控制寄存器 6.0 SL811HS和SL811HST—AC物理关系 6.1 SL811HS 物理连接 6.2 SL811HST-AC物理连接 7.0 电的规格 7.1 完全最大的等级 7.2 推荐操作条件 7.3 外部时钟输入特征 7.4 DC特征 7.5 USB主机传输器特征 ============================================================= 1.0 规定 没有注释的1,2,3,4都是十进制数 十六进制数的后面都有“h” 二进制数的后面都有“b” 斜体字用来表示USB规格或某一规格 2.0 定义 USB:通用串行总线 SL811HS: sl811hs是cypress公司的USB主/从设备控制器,提供多种功能。这里,我们提供28针PLCC封装(sl811hs)和48针TQFP封装 (sl811hst-ac)。这个文档中,除非说明,sl811hs包括两种封装 注释:这个芯片不含CPU SL11 sl11是cypress公司USB外围设备的控制器,提供多种功能,这里,我们提供28针PLCC封装(sl11)和48针TQFP封装(sl11t-ac)。 这个文档中,除非说明,sl11包括两种封装

从汇编、C语言到十年的FPGA开发设计,告诉你成长的经验

从汇编、C语言到十年的FPGA开发设计,告诉你成长的经验大学时代第一次接触FPGA至今已有10多年的时间,至今记得当初第一次在EDA实验平台上完成数字秒表、抢答器、密码锁等实验时那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。 后来读研究生,工作陆陆续续也用过Quartus II、FoundaTIon、ISE、Libero,并且学习了verilogHDL语言,学习的过程中也慢慢体会到verilog的妙用,原来一小段语言就能完成复杂的原理图设计,而且语言的移植性可操作性比原理图设计强很多。 在学习一门技术之前我们往往从它的编程语言入手,比如学习单片机时,我们往往从汇编或者C语言入门。所以不少开始接触FPGA的开发人员,往往是从VHDL或者Verilog开始入手学习的。但我个人认为,若能先结合《数字电路基础》系统学习各种74系列逻辑电路,深刻理解逻辑功能,对于学习HDL语言大有裨益,往往会起到事半功倍的效果。当然,任何编程语言的学习都不是一朝一夕的事,经验技巧的积累都是在点滴中完成,FPGA设计也无例外。下面就以我的切身体会,谈谈FPGA设计的经验技巧。 我们先谈一下FPGA基本知识: 1.硬件设计基本原则 FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD 等可编程器件的基础上进一步发展的产物。它是作为专用集成电路领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。速度与面积平衡和互换原则: 一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约; 反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用“乒乓操作”和“串并转换”的思想进

FPGA乒乓操作及串并转换设计篇

FPGA/CPLD重要设计思想及工程应用 乒乓操作及串并转换设计篇 概述 “乒乓操作”是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如下图所示。 乒乓操作的处理流程 输入数据流通过“输入数据选择单元”将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM(DPRAM) 、单口RAM(SPRAM) 、FIFO等。 在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”。在第2 个缓冲周期,通过“输入数据选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,同时将“数据缓冲模块1”缓存的第1 个周期数据通过“输出数据选择单元”的选择,送到“数据流运算处理模块”进行运算处理。 在第3 个缓冲周期通过“输入数据选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,同时将“数据缓冲模块2”缓存的第2 个周期的数据通过“输出数据选择单元”切换,送到“数据流运算处理模块”进行运算处理。如此循环。 利用乒乓操作完成数据的无缝缓冲与处理 乒乓操作可以通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。

把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。所以乒乓操作常常应用于流水线设计中,完成数据的无缝缓冲与处理。 串并转换 串并转换是FPGA 设计的一个重要技巧,它是高速数据流处理的常用手段,串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用寄存器、双口RAM(DPRAM) 、单口RAM(SPRAM) 、FIFO 等实现。 若想数据的缓冲区开得很大,可以通过DPRAM 实现了数据流的串并转换,对于数量比较小的设计可以采用寄存器完成串并转换。如无特殊需求,系统中应该用同步时序设计完成串并之间的转换。 那么在工程应用中,程序里怎么才能体现出串并转换设计的思想呢?怎么才能提高系统的处理速度呢?我们可以先来做一个串并转换的框架型设计。 这个章节老师没有给留下什么固定题目,所以自己构思起来也有点麻烦。想来想去就做个串入并出的设计吧。 设计的思想是这样的,有一组数据以50MHZ的速率从FPGA的一个I/O口传入,要实现在FPGA的另一端8个I/O口以50/8MHZ的速率把传入的速率吐出。也就是说每隔8个主时钟周期要从8个输出口输出从输入口输入的8个数据。 功能仿真的波形如下: 如图,从rst完成复位(拉低)并且输入使能信号en置位(拉高)后输入的数据(头8个时钟周期)为10101010,在第9个时钟周期,输出使能信号en_out 拉高了,说明此时可以从8位并行数据输出口取数了,data_out的输出16进制aa正好就是输入的10101010,所以第一个数据的串并转换正确无误。往后输入11110000,输出是16进制f0也没错…… 该程序实现了串并转换的要求,这样原来50MH速率传送的数据经过FPGA串并转换后只要用1/8的时钟频率就能完成数据流的传输,也可以说这是一个面积换速度的典型。 程序:

(完整版)FPGA资深FAE的经验独白

骏龙科技Andrew —— FPGA资深FAE的经验独白 时间:2014-08-25 来源:elecfans 作者: 关键字:FPGA FAE骏龙科技 看似简单的几个问题,Andrew却回答的井井有条,小编已经没有办法有什么其他词语去形容了。本文Andrew不仅仅对FPGA入门学习流程做了详细的分享,更是对FPGA开发工作的要求分成大公司和小公司两个层面来分析。你能想象曾经从一个疏忽学业的人成为一名资深FAE的嘛? 1. 您认为想学FPGA的话,先学好什么才最重要? Andrew:我们玩FPGA的通常就是跟数字电路打交道,要想玩得转,必须先学习并掌握最最基础的数字电路和HDL硬件描述语言,当然这只是入门必备,实际上远远不够。个人拙见,要入行除了至少掌握一种FPGA的仿真及开发调试流程之外;起码还要了解一些模拟电路知识,掌握诸如电源纹波、时钟抖动、信号质量等经常需要测量的硬件参数的测试方法;起码还要掌握一种原理图和Layout设计软件,能够查看分析调试电路板上的电路模块,如电源、时钟、存储器、配置、I/O和高速收发器等模块;起码还要掌握一种单片机的开发流程,项目中难免有一些需要配置控制的需求,使用外置单片机或者内置ARM硬核或者其他软CPU来实现,简单又方便;由于本人水平有限,其他方面这里就不再赘述。 那么,针对FPGA入门学习的一般流程,简单总结一下,供朋友们参考,有经验的大牛可以绕道: 1.首先要有开发平台,把该准备的都准备好,磨刀不误砍柴工: 比如ALTERA的Quartus II软件、开发板和配置调试工具USB Blaster,以及仿真软件Modelsim SE。软件可以从网上下载,入门功能的许可的和谐方法一大堆;开发板和USB Blaster可以借,可以买,动手能力强的朋友,自己画一块也行。对于初学者,建议找一块有详细配套教程的开发板。 2. 对于新手来讲,按部就班地学习往往就是最快的学习方法: 照猫画虎尽管囫囵吞枣一知半解,但起码能把开发流程摸熟,能跑起来。刚拿到开发板,肯定是丈二和尚摸不着头脑。这个时候,建议先根据开发板的配套教程,把原理图上的各项模块功能厘清,把FPGA周围的电源、时钟、复位、配置、GPIO和连接器等的电路原理理一理分析分析。再按照配套教程中介绍的流程,把配套的测试工程跑通,在这个阶段,

个人总结FPGA设计中Verilog编程的27条经验

个人总结Verilog编程27条经验 1.强烈建议用同步设计; 2.在设计时总是记住时序问题; 3.在一个设计开始就要考虑到地电平或高电平复位、同步或异步复位、上升沿 或下降沿触发等问题,在所有模块中都要遵守它; 4.在不同的情况下用if和case,最好少用if的多层嵌套(1层或2层比较合 适,当在3层以上时,最好修改写法,因为这样不仅可以reduce area,而且可以获得好的timing); 5.在锁存一个信号或总线时要小心,对于整个design,尽量避免使用latch, 因为在DFT时很难test; 6.确信所有的信号被复位,在DFT时,所有的FlipFlop都是controllable; 7.永远不要再写入之前读取任何内部存储器(如SRAM); 8.从一个时钟到另一个不同的时钟传输数据时用数据缓冲,他工作像一个双时 钟FIFO(是异步的),可以用Async SRAM搭建Async FIFO; 9.在VHDL中二维数组可以使用,它是非常有用的。在VERILOG中他仅仅可以使 用在测试模块中,不能被综合; 10.遵守register-in register-out规则; 11.像synopsys的DC的综合工具是非常稳定的,任何bugs都不会从综合工具中 产生 12.确保FPGA版本与ASIC的版本尽可能的相似,特别是SRAM类型,若版本一致 是最理想的,但是在工作中FPGA版本一般用FPGA自带的SRAM,ASIC版本一般用厂商提供的SRAM; 13.在嵌入式存储器中使用BIST; 14.虚单元和一些修正电路是必需的; 15.一些简单的测试电路也是需要的,经常在一个芯片中有许多测试模块; 16.除非低功耗不要用门控时钟,强烈建议不要在design中使用gate clock; 17.不要依靠脚本来保证设计。但是在脚本中的一些好的约束能够起到更好的性 能(例如前向加法器); 18.如果时间充裕,通过时钟做一个多锁存器来取代用MUX; 19.不要用内部tri-state, ASIC需要总线保持器来处理内部tri-state,如IO cell; 20.在top level中作pad insertion; 21.选择pad时要小心(如上拉能力,施密特触发器,5伏耐压等),选择合适的 IO cell; 22.小心由时钟偏差引起的问题; 23.不要试着产生半周期信号; 24.如果有很多函数要修正,请一个一个地作,修正一个函数检查一个函数; 25.在一个计算等式中排列每个信号的位数是一个好习惯,即使综合工具能做; 26.不要使用HDL提供的除法器; 27.削减不必要的时钟。它会在设计和布局中引起很多麻烦,大多数FPGA有1- 4个专门的时钟通道;

乒乓操作

唉。写好testbench后一定要将顶层模块写进,不然怎么会有结果呢!!其实乒乓操作用面积换速度。具体如何应用于实际中,不知道,只是知道怎么回事。比如串并转换中,必须先对串入数据进行处理,然后将其送出。这在通讯中应该会用到吧。如果处理发现错误则丢弃数据,那么在处理数据的时候就不能够允许数据更改,这样就限制了速度。(当然也可以用寄存器将结果先寄存处理)。不过写这个对Verilog又有了进一步的了解: 1.模块化!写程序前要想清楚如何划分模块,模块之间的接口。这样方便仿真出错时候查错误,而且会使模块内部逻辑关系变简单。 2.非阻塞赋值是beginend执行完后就改变数据,因此,对于某些信号我们可以根据触发条件进行选择。如模块2选一输入中的oden 1和oden2的选择 module sp_top(clk,nrst,serial_in,data_out,serial_en1,serial_en2,oden1,oden2); input clk,nrst,serial_in; output[3:0] data_out; output serial_en1,serial_en2; output oden1,oden2; wire oden1,oden2; wire serial_en1,serial_en2; wire[3:0] parallel_out1,parallel_out2; sp_imux21 Ssp_imux21(nrst,oden1,oden2,serial_en1,serial_en2); sp_buf Ssp_buf1(serial_en1,clk,nrst,serial_in,oden1,parallel_out1); sp_buf Ssp_buf2(serial_en2,clk,nrst,serial_in,oden2,parallel_out2); sp_omux21 Ssp_omux21(clk,oden1,oden2,nrst,parallel_out1,parallel_out2,data_out); endmodule //sp_mux41:serial to parallel data_buf choose module sp_imux21(nrst,oden1,oden2,serial_en1,serial_en2); input nrst; input oden1,oden2; output serial_en1,serial_en2; reg serial_en1,serial_en2; always@(posedge oden1 or posedge oden2 or negedgenrst) if(!nrst) begin serial_en1=1'b1;serial_en2=1'b0;end else if(oden1) begin serial_en1<=1'b0;serial_en2<=1'b1;end else if(oden2) begin serial_en1<=1'b1;serial_en2<=1'b0;end // else serial_en<=serial_en; endmodule //sp_buf:serial to parallel data input buffer module sp_buf(iden,clk,nrst,serial_in,oden,parallel_out); input iden;//data input enable input clk,nrst; input serial_in; output oden;//output enable

FPGA 乒乓操作 zhuan

FPGA 乒乓操作 乒乓操作的处理流程为:输入数据通过“输入数据选择单元"将数据等时分配到两个数据缓冲模块中,在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1"中,在第二个缓冲周期,通过“输入数据单元”切换,将输入的数据缓存到“数据缓冲模块2’’,同时将“数据缓冲模块1”缓存的第一个周期数据通过“数据选择单元”的选择,送到“数据流运算处理模块’’进行处理,在第三个缓冲周期通过“输入数据选择单元"的再次切换,将输入的数据流缓存到“数据缓冲模块1”中,同时将“数据缓冲模块2”缓存的第二个周期的数据通过“输出数据选择单元”的切换,送到“数据流运算处理模块”进行运算处理。如此循环。 乒乓操作的最大特点是通过“输入数据选择单元”和“输出数据选择单元’’按节拍的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算处理。把乒乓操作当作一个整体,站在这个模块的两端看数据,输入数据和输出数据都是连续不断的,因此非常适合对数据流进行流水线式处理,完成数据的无缝缓冲与处理。在本系统的存储模块设计中,正是采用了乒乓操作原理。 比较常用的存储单元为双口RAM(DPRAM)、单口RAM(SPRAM)、FIFO等。 乒乓操作的第二个优点是可以节约缓冲区空间。比如在WCDMA基带应用中,1个帧是由15个时隙组成的,有时需要将1整帧的数据延时一个时隙后处理,比较直接的办法是将这帧数据缓存起来,然后延时1个时隙进行处理。这时缓冲区的长度是1整帧数据长,假设数据速率是3.84Mbps,1帧长10ms,则此时需要缓冲区长度是38400位。如果采用乒乓操作,只需定义两个能缓冲1个时隙数据的RAM(单口RAM即可)。当向一块RAM写数据的时候,从另一块RAM

FPGA研发牛人心得总结

FPGA研发之道 FPGA是个什么玩意? FPGA是个什么玩意? 首先来说: FPGA是一种器件。其英文名feild programable gate arry 。很长,但不通俗。通俗来说,是一种功能强大似乎无所不能的器件。通常用于通信、网络、图像处理、工业控制等不同领域的器件。就像ARM、DSP等嵌入式器件一样,成为无数码农码工们情感倾泻而出的代码真正获得生命的地方。只不过,一样的编程,却是不一样的思想。嵌入式软件人员看到的是C。而FPGA工程师看到是硬件描述语言,verilog或VHDL。软件看到是函数、对象、重构。FPGA工程师则是模块、流水、复用。从现象上看,都是代码到下载程序再到硬件上运行。不能只看现象而忽略本质。FPGA 开发本质上是设计一颗IC,“**的身子,丫鬟的命”不是所有verilog/VHDL代码,都能获得青睐去流片成为真正的芯片,而更多的则成为运行在FPGA器件上,成为完成相同功能的替代品。其实现的功能却一点也不逊色于百万身价流片的近亲。从而成为独树一帜的行业。 FPGA开发的流程,是通过verilog/VHDL等硬件描述语言通过EDA工具编译、综合、布局布线成为下载文件,最终加载到FPGA器件中去,完成所实现的功能。那硬件描述语言描述的是什么?这里描述的就是组合逻辑电路和时序逻辑电路。组合逻辑电路就是大家所熟知的与门、或门、非门。时序逻辑电路则是触发器。数字芯片上绝大部分逻辑都是这两种逻辑实现的。也就是基本上每个电子行业的人所学过的数字电路。顺便说一下,感谢香农大师,在其硕士毕业论文<继电器与开关电路的符号分析>就奠定了数字电路的的根基。只

第8章FPGA设计技巧与设计经验介绍

第1节基本设计技巧 乒乓操作 1 操作过程 2 从外部看,数据流没有停顿的进出 3 用低速模块处理高速数据流 4 实际上,用两个缓冲模块实现了串并转换,两个预处理模块并行,面积换速度;串并转换 串并转换 1 FPGA设计的一个重要技巧 2 数据流处理的常用手段 3 面积与速度互换思想的直接体现 串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用: 1 寄存器:小设计 2 RAM:数据量比较大的情况 3 状态机:复杂的串并转换 流水线操作 1 流水线处理是高速设计中的一个常用设计手段 2 如果某个设计的处理流程分为若干步骤,而且整个数据处理是“单流向”的,即没有反馈或

者迭代运算,前一个步骤的输出是下一个步骤的输入,则可以考虑采用流水线设计方法提高系统的工作频率。 3 将适当划分的n个操作步骤单向串连起来 4 数据流在流水线各个部分的处理,从时间上看是连续的 5 数据流依次流经n个模块,完成每个步骤的操作 6 流水线设计时,时序要进行合理安排,每个操作步骤的划分要合理,仔细考虑各个步骤间的数据流量 7 如果前级操作时间恰好等于后级的操作时间,设计最为简单,前级直接输出到后级的输入即可 8 如果前级操作时间大于后级的操作时间,则后级会经常空闲。可以对前级的输出数据适当缓存,再输出到后级的输入端如果前级操作时间小于后级的操作时间,则必须通过复制逻辑,将数据流分流和并行预处理,或者在前级对数据采用存储、后处理方式,否则会造成后级数据溢出 数据接口的同步 1 两种易出问题的设计习惯 --手工加入非门调整数据延迟,从而保证本级时钟对上级数据的建立、保持时间的要求 --为了有稳定的采样,时而用正沿打一下数据,时而用负沿打一下数据,以调整数据的采样位置 2 问题 --一旦芯片更新换代,或者移植到其它器件系列的芯片上,采样实现必须重新设计 --这两种做法造成电路实现的时序余量不够,一旦外界条件变换(比如温度升高),采样时序就有可能紊乱,造成电路不能完成预定的功能 3 如果输入数据的节拍和本系统处理时钟同频,可以直接用本系统的主时钟对输入数据寄存器采样,完成输入数据的同步化如果输入数据的节拍和本系统处理时钟同频,可以直接用本系统的主时钟对输入数据寄存器采样,完成输入数据的同步化 4 为了避免异步时钟域产生错误的采样数据,一般使用RAM、FIFO缓存的方法完成异步时钟域的数据转换。在输入端口使用上级时钟写数据,在输出端口使用本级时钟读数据,就非 第2节FPGA设计思考 硬件描述语言的层次含义

10年FPGA开发经验的工程师肺腑之言

10年FPGA开发经验的工程师肺腑之言 从大学时代第一次接触FPGA至今已有10多年的时间。至今记得当初第一次在EDA实验平台上完成数字秒表,抢答器,密码锁等实验时,那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。后来读研究生,工作陆陆续续也用过Quartus II,Foundation,ISE,Libero,并且学习了verilogHDL语言,学习的过程中也慢慢体会到verilog的妙用,原来一小段语言就能完成复杂的原理图设计,而且语言的移植性可操作性比原理图设计强很多。 在学习一门技术之前我们往往从它的编程语言入手,比如学习单片机时,我们往往从汇编或者C语言入门。所以不少开始接触FPGA的开发人员,往往是从VHDL或者Verilog开始入手学习的。但我个人认为,若能先结合《数字电路基础》系统学习各种74系列逻辑电路,深刻理解逻辑功能,对于学习HDL 语言大有裨益,往往会起到事半功倍的效果。 当然,任何编程语言的学习都不是一朝一夕的事,经验技巧的积累都是在点滴中完成,FPGA设计也无例外。下面就以我的切身体会,谈谈FPGA设计的经验技巧。 1)看代码,建模型 只有在脑海中建立了一个个逻辑模型,理解FPGA内部逻辑结构实现的基础,才能明白为什么写Verilog和写C整体思路是不一样的,才能理解顺序执行语言和并行执行语言的设计方法上的差异。在看到一段简单程序的时候应该想到是什么样的功能电路。 例如: 上面这段代码实现的功能就是一个带使能端的2选1数据选择器,如下图所示。

再例如: 上面这段always实现的是带同步清零端的串并转换移位寄存器,位宽为width,下图为8位电路模型 当你具备了一定的识代码能力之后,你会发现原来Verilog不是那么的枯燥,只不过是一个个电路模型的拼搭而已。 2)组合逻辑中的if...else...与case 对于多输入端的组合逻辑来说,如果不需要考虑优先级应该尽量采用case语句来描述,这样综合出来的电路并行度要大一些,如果采用if...else...结构,综合出来的电路都是串行的,增大了信号时延路径。降低寄存器间组合路径的延迟是提高系统工作频率的主要手段,因此在完成相同功能的前提下应该尽量使用并行结构逻辑。

FPGA设计的四种常用思想与技巧乒乓操作

FPGA设计的四种常用思想与技巧 王诚 Lattice Semiconductor 本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。 FPGA/CPLD的设计思想与技巧是一个非常大的话题,由于篇幅所限,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口的同步方法。希望本文能引起工程师们的注意,如果能有意识地利用这些原则指导日后的设计工作,将 取得事半功倍的效果! 乒乓操作 “乒乓操作”是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如图1所示。 乒乓操作的处理流程为:输入数据流通过“输入数据选择单元”将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM(DPRAM)、 单口RAM(SPRAM)、FIFO等。在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”;在第2个缓冲周期,通过“输入数据选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,同时将“数据缓冲模块1”缓存的第1个周期数据通过“输入数据选择单元”的选择,送到“数据流运算处理模块”进行运算处理;在第3个缓冲周期通过“输入数据选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,同时将“数据缓冲模块2”缓存的第2个周期的数据通过“输入数据选择单元”切换,送到“数据流运算处理模块”进行运算处理。如此循环。 乒乓操作的最大特点是通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。所以乒乓操作常常应用于流水线式算法,完成数据的无缝缓冲与处理。 乒乓操作的第二个优点是可以节约缓冲区空间。比如在WCDMA基带应用中,1个帧是由15 个时隙组成的,有时需要将1整帧的数据延时一个时隙后处理,比较直接的办法是将这帧数据缓存起来,然后延时1个时隙进行处理。这时缓冲区的长度是1整帧数据长,假设数据速率是3.84Mbps,1帧长10ms,则此时需要缓冲区长度是38400位。如果采用乒乓操作,只 需定义两个能缓冲1个时隙数据的RAM(单口RAM即可)。当向一块RAM写数据的时候,从另