A 7-GHz 1.8-dB NF CMOS Low-Noise Amplifier

852IEEE JOURNAL OF SOLID-STATE CIRCUITS,VOL.37,NO.7,JULY 2002

A 7-GHz 1.8-d

B NF CMOS Low-Noise Amplifier

Ryuichi Fujimoto ,Member,IEEE ,Kenji Kojima,and Shoji Otaka

Abstract—A 7-GHz low-noise amplifier (LNA)was designed and fabricated using

0.25-m CMOS technology.A cascode configuration with a dual-gate MOSFET and shielded pads were adopted to improve the gain and the noise performance.The effects of the dual-gate MOSFET and the shielded pads are discussed quantitatively.An associated gain of 8.9dB,a minimum noise figure of 1.8dB,and an input-referred third-order intercept point of +8.4dBm were obtained at 7GHz.The LNA consumes 6.9mA from a 2.0-V supply voltage.These measured results indi-cate the feasibility of a CMOS LNA employing these techniques for low-noise and high-linearity applications at over 5GHz.Index Terms—Dual-gate MOSFET,intercept point,low-noise amplifier,noise figure,shielded pad,Si substitute.

I.I NTRODUCTION

R

ECENTLY ,wireless communication systems with a car-rier frequency of over 5GHz,such as intelligent trans-port system (ITS)and wireless LAN specified by IEEE 802.11a,have attracted considerable attention.Furthermore,a carrier fre-quency of up to 10GHz is expected to be used for fourth-gen-eration (4G)wireless systems.

Thanks to recent advances in CMOS technology,a transition

frequency

is competitive with that of silicon bipolar junc-tion transistor (Si-BJT)technology.The main noise sources of MOSFETs at high frequency are the thermal noise of channel and gate resistance.The gate resistance is reduced using low-re-sistance salicided gate material and a multifinger gate structure to obtain low noise performance [1],[2],and so the dominant noise source of MOSFETs is the thermal noise of a channel.On the other hand,the main noise sources of Si-BJTs are thermal noise of base resistance and shot noise of the collector current.To reduce base resistance,a large geometry device is needed,but this requires more collector current to keep the same

high value,which causes more shot noise.To reduce shot noise,a small collector current is needed,but this requires a small geom-etry device to keep the same

high

value,which causes a large base resistor.So,reducing the thermal noise of the base resis-tance causes large shot noise,and vice versa.Hence,the noise performance of MOSFETs is superior to that of Si-BJTs.CMOS technology is also advantageous for low cost and large-scale in-tegration.

Owing to these merits of the CMOS technology,many low-noise amplifiers (LNAs)using CMOS technology have been reported [3]–[7].Considering the demand for systems

Manuscript received November 5,2001;revised January 28,2002.

R.Fujimoto and S.Otaka are with the Corporate Research and Development Center,Toshiba Corporation,Kawasaki 212-8582,Japan (e-mail:ryuichi.fuji-moto@toshiba.co.jp).

K.Kojima is with the SoC Research and Development Center,Toshiba Cor-poration,Semiconductor Company,Yokohama 235-8522,Japan.Publisher Item Identifier S

0018-9200(02)05857-2.

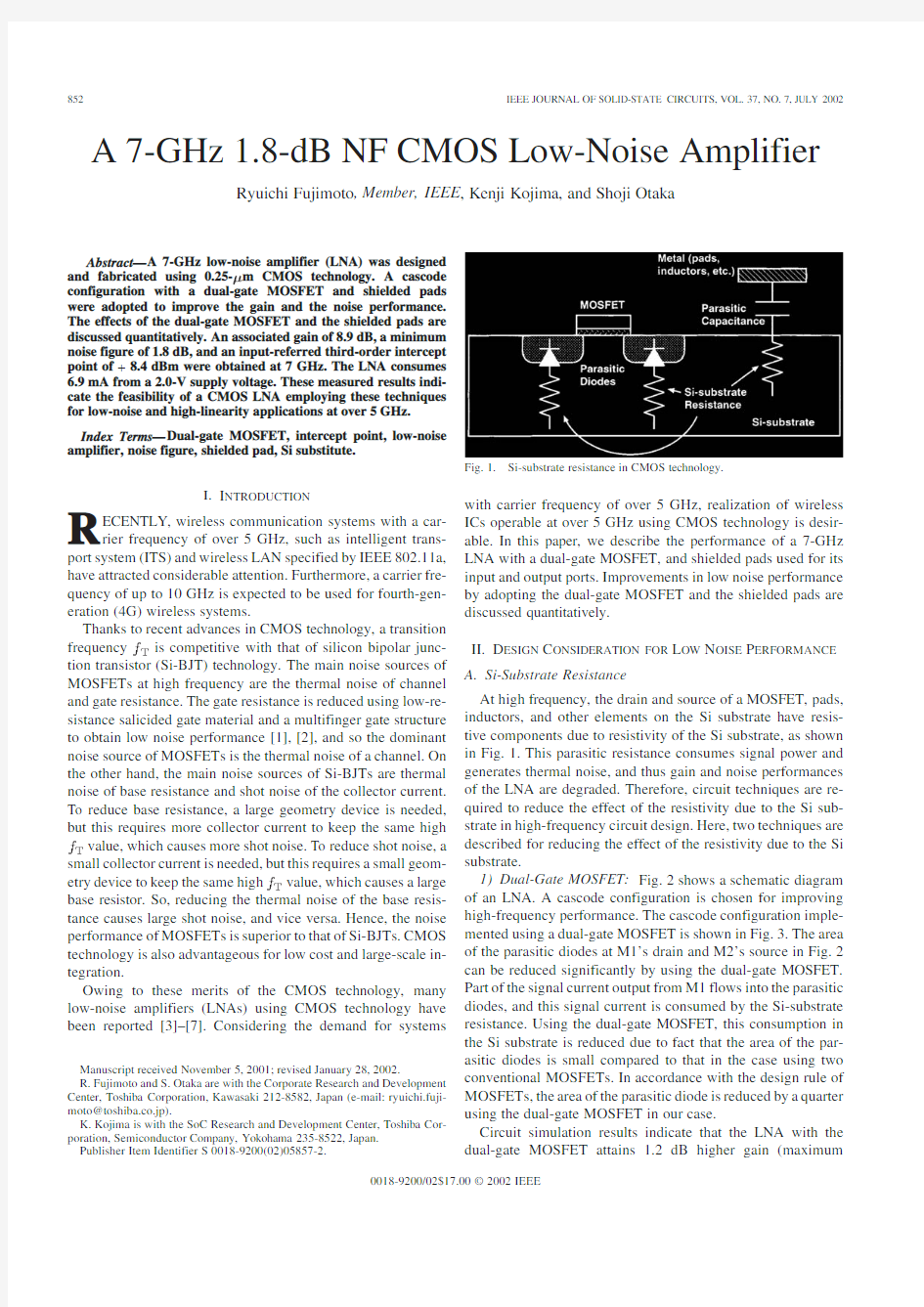

Fig.1.Si-substrate resistance in CMOS technology.

with carrier frequency of over 5GHz,realization of wireless ICs operable at over 5GHz using CMOS technology is desir-able.In this paper,we describe the performance of a 7-GHz LNA with a dual-gate MOSFET,and shielded pads used for its input and output ports.Improvements in low noise performance by adopting the dual-gate MOSFET and the shielded pads are discussed quantitatively.

II.D ESIGN C ONSIDERATION FOR L OW N OISE P ERFORMANCE A.Si-Substrate Resistance

At high frequency,the drain and source of a MOSFET,pads,inductors,and other elements on the Si substrate have resis-tive components due to resistivity of the Si substrate,as shown in Fig.1.This parasitic resistance consumes signal power and generates thermal noise,and thus gain and noise performances of the LNA are degraded.Therefore,circuit techniques are re-quired to reduce the effect of the resistivity due to the Si sub-strate in high-frequency circuit design.Here,two techniques are described for reducing the effect of the resistivity due to the Si substrate.

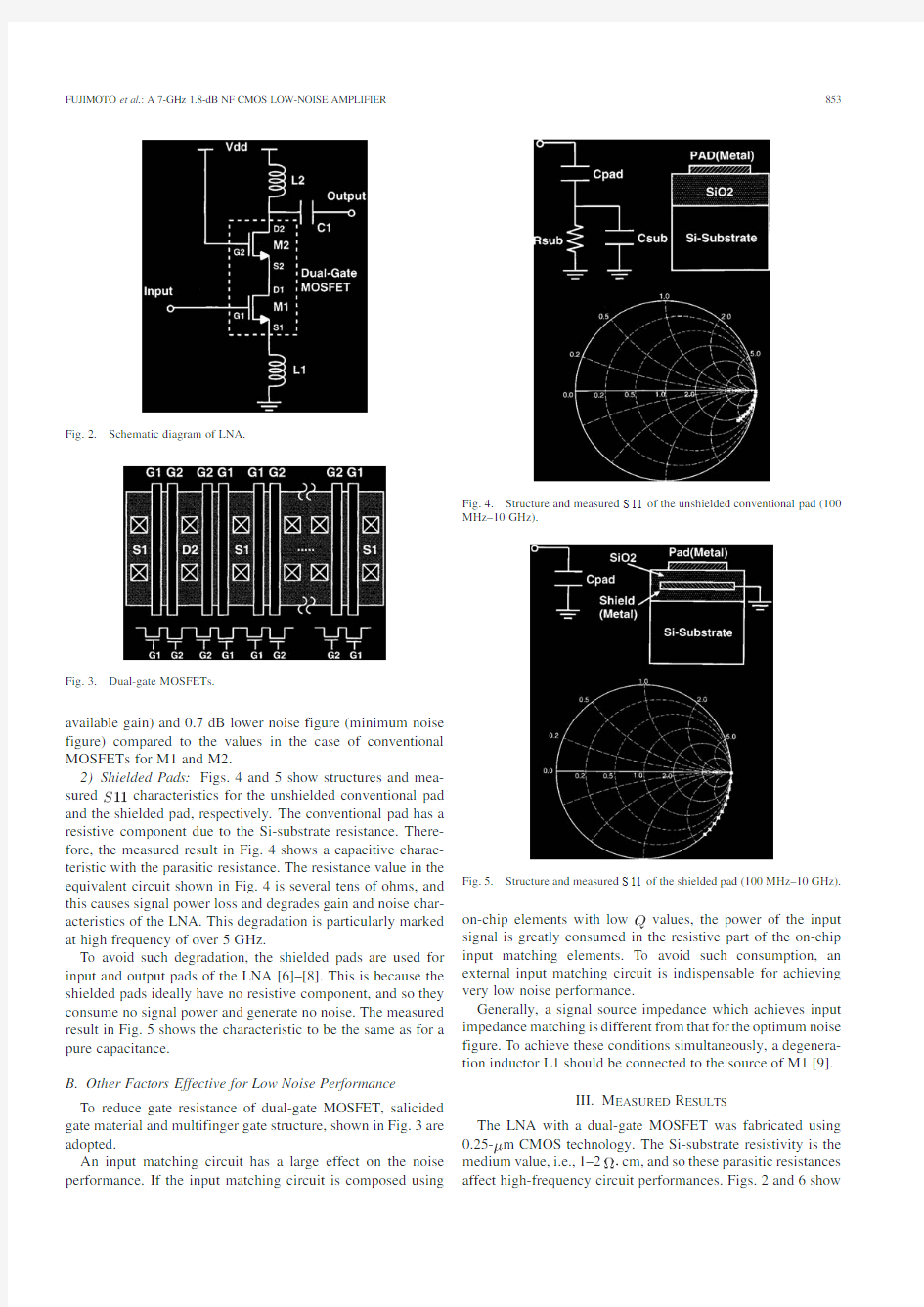

1)Dual-Gate MOSFET:Fig.2shows a schematic diagram of an LNA.A cascode configuration is chosen for improving high-frequency performance.The cascode configuration imple-mented using a dual-gate MOSFET is shown in Fig.3.The area of the parasitic diodes at M1’s drain and M2’s source in Fig.2can be reduced significantly by using the dual-gate MOSFET.Part of the signal current output from M1flows into the parasitic diodes,and this signal current is consumed by the Si-substrate https://www.360docs.net/doc/503593892.html,ing the dual-gate MOSFET,this consumption in the Si substrate is reduced due to fact that the area of the par-asitic diodes is small compared to that in the case using two conventional MOSFETs.In accordance with the design rule of MOSFETs,the area of the parasitic diode is reduced by a quarter using the dual-gate MOSFET in our case.

Circuit simulation results indicate that the LNA with the dual-gate MOSFET attains 1.2dB higher gain (maximum

0018-9200/02$17.00?2002IEEE

FUJIMOTO et al.:A 7-GHz 1.8-dB NF CMOS LOW-NOISE AMPLIFIER

853

Fig.2.Schematic diagram of

LNA.

Fig.3.Dual-gate MOSFETs.

available gain)and 0.7dB lower noise figure (minimum noise figure)compared to the values in the case of conventional MOSFETs for M1and M2.

2)Shielded Pads:Figs.4and 5show structures and mea-

sured

characteristics for the unshielded conventional pad and the shielded pad,respectively.The conventional pad has a resistive component due to the Si-substrate resistance.There-fore,the measured result in Fig.4shows a capacitive charac-teristic with the parasitic resistance.The resistance value in the equivalent circuit shown in Fig.4is several tens of ohms,and this causes signal power loss and degrades gain and noise char-acteristics of the LNA.This degradation is particularly marked at high frequency of over 5GHz.

To avoid such degradation,the shielded pads are used for input and output pads of the LNA [6]–[8].This is because the shielded pads ideally have no resistive component,and so they consume no signal power and generate no noise.The measured result in Fig.5shows the characteristic to be the same as for a pure capacitance.

B.Other Factors Effective for Low Noise Performance To reduce gate resistance of dual-gate MOSFET,salicided gate material and multifinger gate structure,shown in Fig.3are adopted.

An input matching circuit has a large effect on the noise performance.If the input matching circuit is composed

using

Fig.4.Structure and measured S 11of the unshielded conventional pad (100MHz–10

GHz).

Fig.5.Structure and measured S 11of the shielded pad (100MHz–10GHz).

on-chip elements with

low values,the power of the input signal is greatly consumed in the resistive part of the on-chip input matching elements.To avoid such consumption,an external input matching circuit is indispensable for achieving very low noise performance.

Generally,a signal source impedance which achieves input impedance matching is different from that for the optimum noise figure.To achieve these conditions simultaneously,a degenera-tion inductor L1should be connected to the source of M1[9].

III.M EASURED R ESULTS

The LNA with a dual-gate MOSFET was fabricated using

0.25-m CMOS technology.The Si-substrate resistivity is the medium value,i.e.,

1–2cm,and so these parasitic resistances affect high-frequency circuit performances.Figs.2and 6show

854IEEE JOURNAL OF SOLID-STATE CIRCUITS,VOL.37,NO.7,JULY

2002

Fig.6.Die photograph of

LNA.

Fig.7.Gains and noise figures of the LNA.

a circuit diagram and a die photograph of the LNA,respec-tively.The chip size including the area of the pads is

860

m

610m.The degeneration inductor L1,and the output matching elements L2and C1are integrated on the chip.

Measured results are obtained by using on-wafer probing technique.The power supply voltage is 2V and the current consumption of the LNA is 6.9mA.

Fig.7shows the frequency response of gain

(

,Ga,MAG)and noise figure (NFmin,NF50)for the

LNA.

,Ga,and MAG are the magnitude

of

,associated gain,and maximum available gain,respectively.NFmin is the minimum noise figure and NF50is the noise figure when a signal source with

50-impedance is connected directly to the LNA.NFmin of 1.8dB and Ga of 8.9dB are obtained at 7GHz.

Fig.8

shows

,from 5to 9GHz,and noise circles at 7

GHz.

is the signal impedance which realize NFmin at 7GHz,

and

is the optimum signal impedance for impedance

matching.

and are close at 7GHz,as shown in Fig.8,owing to the degeneration inductor L1.This result indicates that both good impedance matching and low noise characteristic are realized simultaneously.For good impedance matching,the voltage standing-wave ratio (VSWR)

should be less than 2;the input

VSWR

and

NF dB can be satisfied by adding an appropriate matching

circuit.

Fig.8.S 11and noise circle of the LNA (S 11,S 11:5–9

GHz).

Fig.9.S 22of the LNA (5–9GHz).

Fig.9

shows of the LNA from 5to 9

GHz.is close to

50at 7GHz owing to the on-chip output matching circuit,and the output VSWR is 1.3.

Fig.10shows intermodulation characteristics for the LNA

with two-tone signal inputs

(

GHz

and GHz).A very high input-referred third-order intercept point (IIP3)

of 8.4dBm is obtained without the input matching circuit.A 2.7dB gain enhancement is achieved by adopting the input matching circuit which realizes NFmin at 7GHz.In this case,the IIP3is expected to

be 5.7dBm,and the LNA still attains high-linearity characteristic.Such a high IIP3value is achieved due to the approximately square-low property of MOSFETs and appropriate valued degeneration inductor L1of 0.3nH.Table I summarizes the measured results of the LNA.

IV .D ISCUSSION

Generally,

the value of a capacitive component is higher than that of inductors up to several GHz.At 7GHz,the induc-tors used in the LNA

have values of over 10owing to low-re-

简单电路设计设计大全

装饰材料购销合同 简单电路设计设计大全 1.保密室有两道门,只有当两道门都关上时(关上一道门相当于闭合一个开关),值班室内的指示灯才会发光,表明门都关上了.下图中符合要求的电路是 2.小轿车上大都装有一个指示灯,用它来提醒司机或乘客车门是否关好。四个车门中只要有一个车门没关好(相当于一个开关断开),该指示灯就会发光。下图为小明同学设计的模拟电路图,你认为最符合要求的是 3.中考试卷库大门控制电路的两把钥匙分别有两名工作人员保管,单把钥匙无法打开,如图所示电路中符合要求的是 ”表示)击中乙方的导电服时,电路导通,4.击剑比赛中,当甲方运动员的剑(图中用“S 甲 乙方指示灯亮。下面能反映这种原理的电路是 5.家用电吹风由电动机和电热丝等组成,为了保证电吹风的安全使用,要求:电动机不工作时,电热丝不能发热;电热丝发热和不发热时,电动机都能正常工作。如图所示电路中符合要求的是( )

6.一辆卡车驾驶室内的灯泡,由左右两道门上的开关S l、S2和车内司机右上方的开关S3共同控制。S1和S2分别由左右两道门的开、关来控制:门打开后,S1和S2闭合,门关上后,S l和S2断开。S3是一个单刀三掷开关,根据需要可将其置于三个不同位置。在一个电路中,要求在三个开关的共同控制下,分别具有如下三个功能:(1)无论门开还是关,灯都不亮; (2)打开两道门中的任意一道或两道都打开时,灯就亮,两道门都关上时,灯不亮;(3)无论门开还是关,灯都亮。如图所示的四幅图中,符合上述要求的电路是 A.图甲 B.图乙 C.图丙 D.图丁 7.教室里投影仪的光源是强光灯泡,发光时必须用风扇给予降温。为了保证灯泡不被烧坏,要求:带动风扇的电动机启动后,灯泡才能发光;风扇不转,灯泡不能发光。则在如图3所示的四个电路图中符合要求的是 ( ) 8.一般家用电吹风机都有冷热两挡,带扇叶的电动机产生风,电阻R产生热。冷热风能方便转换,下面图3中能正确反应电吹风机特点的电路图是 ( ) 9.飞机黑匣子的电路等效为两部分。一部分为信号发射电路,可用等效电阻R1表示,用开关S1控制,30天后自动断开,R1停止工作。另一部分为信息存储电路,可用等效电阻R2表示,用开关S2控制,

光接收机的结构及原理

第三部分光接收机的结构及原理 在有线电视HFC网络中,光接收机通常位于光纤接点和有线电视的前端位置,它的主要功能是把光信号转变为RF信号,前面已经详细讲述了光探测器、光接收组件的原理及应用。光探测器是实现光/电转换的关键部件,其质量的优劣决定了光接收机的性能指标与档次,光接收组件是光探测器与前置放大器的组合,在光接收机中,无论是分离组件还是一体组件,该部分的成本比重都比较大,与光发射机的激光器一样,不仅决定了光接收机的性能指标,还将决定光接收机的价格。光接收的整机组成主要由光接收组件、功率放大模块及其附属功能电路组成,除光接收组件外,功率放大模块是光接收机的第二大核心元件。即使是采用相同的组件,由于采用不同档次、不同价位的放大模块组合,整机也会有显著不同。有线电视技术发展到今天,光接收机采用分离元件制作放大模块已不多见,基本上全采用集成一体化组件结构。该结构模块大多属于厚膜集成电路,它是用丝网印刷和烧结等工艺在同一陶瓷基片上制作无源网源,并在其上组装分立的半导体芯片或单片集成电路、放大三极管管芯等,另外再外加塑料密封,防止潮气、杂质的进入。 一、光接收机常用的放大模块介绍 能用于光接收机的模块有众多型号,排除品牌命名的差异,根据放大模块的增益划分有14dB、18dB、20dB、22dB、27dB等,用于单模块放大器的34dB的放大模块在光接收机中少有应用,当然也不排除低档光接收机应用的可能。根据放大模块具体放大电路结构的

不同划分:有推挽放大模块、功率倍增放大模块两种,而根据放大元件工艺的不同,放大模块又分为硅放大工艺、砷化镓工艺两种,在光接收机中采用的模块的命名,一般以推挽和功率倍增为主要区分,同时附加增益的差异与器件工艺,如果不说是砷化镓工艺模块则所说的放大模块一般都是指硅工艺。 1.推挽放大模块的原理及结构。在实用的放大电路中,三极管的集电极并非总有电流流过,根据集中极电流导通时间的长短,通常把放大器分成甲类、乙类、丙类等。在输入信号的整个周期中都有电流流过集电极的放大器称为甲类放大器;只有在输入信号的半个周期内有集中极电流的放大器称为乙类放大器;在小于输入信号半个周期内有集中极电流的放大器称为丙类放大器。在许多实用的放大电路中,为了提高放大效率通常都需要把工作点移到截止区,即采用半周导通的乙类工作状态,这时若仍采用一个晶体管,输出信号中将只出现一半波形,将发生严重的截止失真。为了解决这个问题,可采用两只特性完全相同的晶体管,使其中一只晶体管在正半周导通,另一晶体管在负半周导通,最后在负载上合成完整波形,这就是推挽放大电路。下图是推挽放大电路的结构示意图: 输入信号经过高频传输变压器B1,反相加在晶体管VT1和V T2上,被放大后各自在半个周期内产生半个波,在变压器B2上反相叠加,重新合成完整波形输出,由于输出信号反相叠加,其中的直流分量和非线性失真中的偶次谐波互相抵消。降低了直流工作点,使变压器中流过电流减少,从而体积可以做得较小,进一步提高了放大器

简易门铃电路设计

《电子线路CAD》课程论文题目:简易门铃电路的设计

1 电路功能和性能指标 简易门铃是一种简单的门铃电路,它由分立元件和中规模集成芯片的构成,主要采用NE555定时器电路和扬声器组成门铃,利用多谐振荡电路来制作一简易单音门铃电路。它主要由一个NE555、一个47uf的电容、一个0.047uf电容、一个0.01uf电容、一个36kΩ的电阻、一个30kΩ的电阻、两个22k电阻、一个喇叭、两个IN4148高速开关二极管、一个9013三极管、一个开关和一个6v电源组成。NE555作为多谐振荡器,发出脉冲波。与传统的门铃相比,其可靠性、抗干扰性都较好,应用领域也相对较广泛。 2 原理图设计 2.1原理图元器件制作 方法和步骤: ①右键点击项目文件,选择追加新文件到项目中,在二级菜单下选择Schematic Library。 ②在放置菜单中,选择放置矩形。 ③在放置菜单中选择放置引脚。 ④在放置引脚时,按Tab键,选择引脚属性。 图1 注:在放置引脚的过程中,引脚有一端会附带着一个×形灰色的标记,该标记表示引脚端是用来连接外围电路的,所以该端方向一定要朝外,而不能向着矩形的方向。若需要调整引脚的方向,可按键盘撒花上的空格键,每按一次,可将引脚逆时针旋转90°。

2.2 原理图设计 步骤: ①创建PCB工程项目,执行File→New→Project→PCB Project,在弹出对话框中选择Protle Pcb类型并点击OK。将新建默认名为“PCB Project1.PrjPCB”的项目保存,命名为“简易门铃”。 ②创建原理图,在该项目文件名上点击右键,选择追加新文件到项目中,在二级菜单下选择Schematic。 ③保存项目目录下默认名为“Sheet1.SchDOC”的原理图文件。并命名为“简易门铃”。 ⑤绘图环境其他参数采用默认设置。 图2 编译原理图步骤: ①在原理图编辑页面,执行“Project→Compile PCB Project 简易门铃.PRJPCB” 菜单命令。 ②在Messages工作面板中,出现提醒为“Warning”的检查结果可以忽略。 图3

基于光纤通信系统的光接收机前端电路的设计毕业设计

本科毕业设计(论文)

南通大学毕业设计(论文) 原创性声明 本人声明:所呈交的论文是本人在导师指导下进行的研究成果。除了文中特别加以标注和致谢的地方外,论文中不包含其他人已发表或撰写过的研究成果。参与同一工作的其他同志对本研究所做的任何贡献均已在论文中作了明确的说明并表示了谢意。 签名:日期: 本论文使用授权说明 本人完全了解南通大学有关保留、使用学位论文的规定,即:学校有权保留论文及送交论文复印件,允许论文被查阅和借阅;学校可以公布论文的全部或部分内容。 (保密的论文在解密后应遵守此规定) 学生签名:指导教师签名:日期: 2

摘要 随着通信技术产业的迅速发展,光纤通信由于其频带宽、容量大、损耗低、抗辐射等诸多优点成为高速通信系统研究热点。光接收机在整个光纤通信系统中占有重要地位,而前置放大器和限幅放大器是构成光接收机的两个关键电路,所以它们的性能在很大程度上决定了光接收机甚至是光纤通信系统的性能。 为了设计一个满足性能要求、结构简单的光接收机,我们对前置放大器和限幅放大器进行了详细的分析设计,利用电路仿真软件Pspice对跨阻型前置放大器进行了直流分析、交流分析和温度分析等。也对限幅放大器进行了单元电路的设计与仿真。通过对两种电路的分析设计,实现了高增益大带宽的放大目标,可以最大地消除寄生参量的影响,减小混合电路的组装环节,使集成电路的速度性能和可靠性得到显著的提高。 关键词:光接收机,前端放大电路,前置放大器,限幅放大器

ABSTRACT With the rapid development of communication technology industry, optical fiber communication have become the high-speed communications systems research focus because of its frequency bandwidth, large capacity, low loss, anti-radiation, and many other advantages.Optical receiver plays an important role in the optical communication systems, and the preamplifier and limiting amplifier is the two key circuits which constitute the optical receiver, so their performance largely determines the performance of the optical receiver and even the optical fiber communication systems. In order to design an optical receiver which meets the performance requirements and has a simple structure, we analyze and design the preamplifier and limiting amplifier in detail, and we use the circuit simulation software Pspice for transimpedance type preamplifier’s DC analysis, AC analysis and temperature analysis. We also design and simulate unit circuit of limiting amplifier.Through the analysis of the two circuit design, we achieve the amplified target of high gain and large bandwidth, it can eliminate the effects of parasitic parameters largely and reduce the assembly of hybrid circuits,so the speed performance and reliability of integrated circuits can be improved significantly. Keywords:Optical Receiver, Front-end Amplifier, Preamplifier, Limiting Amplifier

光接收机的结构和原理

光接收机的结构和原理 2009-08-31 20:20:03| 分类:电子通信时代| 标签:|字号大中小订阅 在有线电视HFC网络中,光接收机通常位于光纤接点和有线电视的前端位置,它的主要功能是把光信号转变为RF信号,前面已经详细讲述了光探测器、光接收组件的原理及应用。光探测器是实现光/电转换的关键部件,其质量的优劣决定了光接收机的性能指标与档次,光接收组件是光探测器与前置放大器的组合,在光接收机中,无论是分离组件还是一体组件,该部分的成本比重都比较大,与光发射机的激光器一样,不仅决定了光接收机的性能指标,还将决定光接收机的价格。光接收的整机组成主要由光接收组件、功率放大模块及其附属功能电路组成,除光接收组件外,功率放大模块是光接收机的第二大核心元件。即使是采用相同的组件,由于采用不同档次、不同价位的放大模块组合,整机也会有显著不同。有线电视技术发展到今天,光接收机采用分离元件制作放大模块已不多见,基本上全采用集成一体化组件结构。该结构模块大多属于厚膜集成电路,它是用丝网印刷和烧结等工艺在同一陶瓷基片上制作无源网源,并在其上组装分立的半导体芯片或单片集成电路、放大三极管管芯等,另外再外加塑料密封,防止潮气、杂质的进入。 一、光接收机常用的放大模块介绍 能用于光接收机的模块有众多型号,排除品牌命名的差异,根据放大模块的增益划分有14dB、18dB、20dB、22dB、27dB等,用于单模块放大器的34dB的放大模块在光接收机中少有应用,当然也不排除低档光接收机应用的可能。根据放大模块具体放大电路结构的不同划分:有推挽放大模块、功率倍增放大模块两种,而根据放大元件工艺的不同,放大模块又分为硅放大工艺、砷化镓工艺两种,在光接收机中采用的模块的命名,一般以推挽和功率倍增为主要区分,同时附加增益的差异与器件工艺,如果不说是砷化镓工艺模块 则所说的放大模块一般都是指硅工艺。 1.推挽放大模块的原理及结构。在实用的放大电路中,三极管的集电极并非总有电流流过,根据集中极电流导通时间的长短,通常把放大器分成甲类、乙类、丙类等。在输入信号的整个周期中都有电流流过集电极的放大器称为甲类放大器;只有在输入信号的半个周期内有集中极电流的放大器称为乙类放大器;在小于输入信号半个周期内有集中极电流的放大器称为丙类放大器。在许多实用的放大电路中,为了提高放大效率通常都需要把工作点移到截止区,即采用半周导通的乙类工作状态,这时若仍采用一个晶体管,输出信号中将只出现一半波形,将发生严重的截止失真。为了解决这个问题,可采用两只特性完全相同的晶体管,使其中一只晶体管在正半周导通,另一晶体管在负半周导通,最后在负载上合成完整波形,这就是推 挽放大电路。下图是推挽放大电路的结构示意图: 输入信号经过高频传输变压器B1,反相加在晶体管VT1和VT2上,被放大后各自在半个周期内产生半个波,在变压器B2上反相叠加,重新合成完整波形输出,由于输出信号反相叠加,其中的直流分量和非线性失真中的偶次谐波互相抵消。降低了直流工作点,使变压器中流过电流减少,从而体积可以做得较小,进一步提高了放大器的输出功率和效率;更为重要的是,偶次谐波的抵消,减少了放大器的非线性失真,对提高有线电视系统的非线性失真指标具有重要意义。在实际应用中,通常采用两组推挽电路并接的方法,构成桥式结构,则每级推挽电路在负载上的直流电压可抵消,从而简化电路结构。在推挽电路中,两个极性相同晶体管的特性应尽可能一致,两个极性相反晶体管的特性应尽可能互补,才能最大限度的抵消输出信号中的偶次谐波失真,若在电电路中引入负反馈,非线性失真还可进一步减小。 下图是商用化模块常采用的电路结构。 该模块用了共射——共基极放大推挽输出,4个NPN型晶体管两两接成共射—共基极组合放大电路,它们再通过输入、输出变压器接成推挽电路。共射—共基电路的特点是:简单高效,在选定最佳e极电流的情况下,此电路能有效的减小集电极非线性及e—b结非线性。此电路采用低射极电阻和高并联电阻取得高增益,又由于采用了低噪声晶体管使模块的噪声系数降到了尽可能低的程度。总之该电路集中了共射—共基

数字钟的设计与仿真

目录 摘要 (3) 前言 (4) 第一章理论分析 1.1 设计方案 (5) 1.2 设计目的 (5) 1.3 设计指标 (6) 1.4 工作原理及其组成框图 (6) 第二章系统设计 2.1 多谐振荡器 (8) 2.2 计数器 (10) 2.3 六十进制电路 (12) 2.4 译码与LED显示器 (13) 2.5 校时电路 (14) 2.6 电子时钟原理图 (15) 2.7 仿真与检测 (16) 2.8 部分元器件芯片结构图 (18) 2.9 误差分析 (19) 第三章小结 心得体会 (20) 致谢 (21) 参考文献 (22)

摘要 时钟,自从它发明的那天起,就成为人类的朋友,但随着时间的推移,科学技术的不断发展,人们对时间计量的精度要求越来越高,应用越来越广。怎样让时钟更好的为人民服务,怎样让我们的老朋友焕发青春呢?这就要求人们不断设计出新型时钟。在这次的毕业设计中,针对一系列问题,设计了如下电子钟。 本系统由555多谐振荡器,分频器,计数器,译码器,LED显示器和校时电路组成,采用了CMOS系列(双列直插式)中小规模集成芯片。总体方案手机由主题电路和扩展电路两大分组成。 其中主体电路完成数字钟的基本功能,扩展电路完成数字钟的扩展功能,进行了各单元设计,总体调试。 关键词:555多谐振荡器;分频器;计数器;译码器;LED显示器

前言 20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。数字钟已成为人们日常生活中:必不可少的必需品,广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。由于数字集成电路技术的发展和采用了先进的石英技术,使数字钟具有走时准确、性能稳定、集成电路有体积小、功耗小、功能多、携带方便等优点,因此在许多电子设备中被广泛使用。 电子钟是人们日常生活中常用的计时工具,而数字式电子钟又有其体积小、重量轻、走时准确、结构简单、耗电量少等优点而在生活中被广泛应用,因此本次设计就用数字集成电路和一些简单的逻辑门电路来设计一个数字式电子钟,使其完成时间及星期的显示功能。 本次设计以数字电子为主,分别对1S时钟信号源、秒计时显示、分计时显示、小时计时显示、整点报时及校时电路进行设计,然后将它们组合,来完成时、分、秒的显示并且有走时校准的功能。并通过本次设计加深对数字电子技术的理解以及更熟练使用计数器、触发器和各种逻辑门电路的能力。电路主要使用集成计数器,例如CD4060、CD4518,译码集成电路,例如CD4511,LED数码管及各种门电路和基本的触发器等,电路使用5号电池共电,很适合在日常生活中使用。

第5章 电路级设计与仿真

第5章 电路级设计与仿真 电路设计技术是EDA 技术的核心和基础。电路设计可以分为数字电路、模拟电路、常规电路和集成电路。现代EDA 与传统的电路CAD 相比其主要区别是比较多地依赖于电路描述语言,常用的电路描述语言有描述模拟电路的SPICE (Simulation Program with Integrated Circuit Emphasis )语言,描述数字电路的硬件描述语言。弄清电路结构形式与语言的关系以及各种语言的基本功能是学习EDA 技术非常重要的环节,这也是本章的主要目的所在。 本章将从最基本的数学和物理模型出发,引入程序化模型,介绍模拟电路与仿真、数字电路与仿真。从一般的设计原理上讲,常规电路与集成电路并没有本质的区别,本章采用的例子主要以常规电路为主,其基本设计原理也同样适合于相应的集成电路,关于集成电路设计将在后续章节中详细介绍。 5.1模拟电路模型与SPICE 程序 5.1.1 模拟电路模型 电路的物理模型是指利用电路元件(如:电阻、电容、电感等无源元件,三极管、集成电路等有源元件)按照一定的电路连接方式进行连接的图形描述方法。其中电路元件是器件的物理模型,器件模型的建立以及器件的连接是按照电学参数和基本电路功能的描述为依据的。这种电路的物理模型也叫做等效电路模型,也就是我们常说的电路。 电路的物理模型是一种简化了的直观的电路图,可以十分方便地反映电路的连接关系和基本功能,但是这个模型并不能进行直接分析,如果要对电路进行分析,还需要建立电路的数学模型。电路数学模型是根据电路的物理模型和电路分析原理得到的电路行为特性及各参数之间的数学关系。 我们在《电路分析原理》中已经建立起这样的概念,这个概念是基于一些基本的电路定律和基本定理,例如基尔霍夫定律、叠加定理、代文宁定理、欧姆定律等。 基尔霍夫定律:; 0i n 1k k =∑=0v n 1k k =∑=欧姆定律:V=IR 对于特定的电路,这些定律和定理构成了电路中物理参数之间的特定关系,这种特定关系是约束电路的基本数学模型。不同的元件具有不同的参数运算或转换关系,这种关系如表5-1所示,这是一些最基本和最简单的元件及其数学模型,复杂元件的数学模型也是由这些简单的元件按照功能需求组成的。因此,描述模拟电路的数学模型是微分方程或代数方程。 《电路分析基础》课程就是在建立了这些电路模型的基础上对电路进行分析,不论是建立电路模型或者是分析运算,电路分析是在基于电压、电流的等效模型进行的。 表5-1 电路元件及其数学描述 电路元件 符号 物理模型 数学模型(VI 关系) R v = R·i C i = C·dv/dt v = L t ·di/d v = v s , i 电阻电容电感 L 电压源 Vs 103

电子电路设计与仿真工具

电子电路设计与仿真工具 我们大家可能都用过试验板或者其他的东西制作过一些电子制做来进行实践。但是有的时候,我们会发现做出来的东西有很多的问题,事先并没有想到,这样一来就浪费了我们的很多时间和物资。而且增加了产品的开发周期和延续了产品的上市时间从而使产品失去市场竞争优势。有没有能够不动用电烙铁试验板就能知道结果的方法呢?结论是有,这就是电路设计与仿真技术。 说到电子电路设计与仿真工具这项技术,就不能不提到美国,不能不提到他们的飞机设计为什么有很高的效率。以前我国定型一个中型飞机的设计,从草案到详细设计到风洞试验再到最后出图到实际投产,整个周期大概要10年。而美国是1年。为什么会有这样大的差距呢?因为美国在设计时大部分采用的是虚拟仿真技术,把多年积累的各项风洞实验参数都输入电脑,然后通过电脑编程编写出一个虚拟环境的软件,并且使它能够自动套用相关公式和调用长期积累后输入电脑的相关经验参数。这样一来,只要把飞机的外形计数据放入这个虚拟的风洞软件中进行试验,哪里不合理有问题就改动那里,直至最佳效果,效率自然高了,最后只要再在实际环境中测试几次找找不足就可以定型了,从他们的波音747到 F16都是采用的这种方法。空气动力学方面的数据由资深专家提供,软件开发商是IBM,飞行器设计工程师只需利用仿真软件在计算机平台上进行各种仿真调试工作即可。同样,他们其他的很多东西都是采用了这样类似的方法,从大到小,从复杂到简单,甚至包括设计家具和作曲,只是具体软件内容不同。其实,他们发明第一代计算机时就是这个目的(当初是为了高效率设计大炮和相关炮弹以及其他计算量大的设计)。 电子电路设计与仿真工具包括SPICE/PSPICE;multiSIM7;Matlab;SystemView;MMICAD LiveWire、Edison、Tina Pro Bright Spark等。下面简单介绍前三个软件。 ①SPICE(Simulation Program with Integrated Circuit Emphasis):是由美国加州大学推出的电路分析仿真软件,是20世纪80年代世界上应用最广的电路设计软件,

简单逻辑电路设计与仿真

VHDL与集成电路CAD 实验四十二简单逻辑电路设计与仿真 验项目名称:简单逻辑电路设计与仿真 实验项目性质:普通实验 所属课程名称:VHDL与集成电路CAD 实验计划学时:2学时 一.实验目的 1.学习并掌握MAX+PLUSⅡ的基本操作; 2.学习在MAX+PLUSⅡ下设计简单逻辑电路与功能仿真的方法。 二.实验要求 1.MAX+PLUSⅡ使用的相关内容; 2.阅读并熟悉本次实验的内容; 3.用图形输入方式完成电路设计; 4.分析器件的延时特性。 三.实验主要仪器设备和材料 1.PC机。 2.MAX+PLUSⅡ软件。 四.实验内容及参考实验步骤 1.用D触发器设计一个4进制加法计数器并进行功能仿真。 (1)开机,进入MAX+PLUSⅡ系统。 (2)点击File菜单Project子菜单之Name项,出现Project Name 对话框。为当 前的实验选择恰当的路径并创建项目名称(注意MAX+PLUSⅡ不识别中文 路径)。 (3)点击File菜单之New项,出现对话框,选择Graphic Editor File输入方式。 出现图形编辑窗口(注意界面发生了一定变化)。 (4)双击空白编辑区,出现Enter Symbol 对话框(或点击Symbol 菜单Enter Symbol项)从Symbol Libraries项中选择mf子目录(双击),然后在 Symbol File 中选择7474元件(双D触发器);在prim子目录中选择电源 vcc、输入脚input 和输出引脚output。(或直接在Symbol Name 中输入所 需元件的名称回车亦可)。 (5)在图形编辑窗口中的左侧点击连线按钮(draws a horizontal or vertical line), 并完成对电路的连线。各元件布置在合适的位置上(参考电路如图1)。 (6)在引脚的PIN_NAME处左键双击使之变黑,键入引脚名称。 (7)点击File菜单Project子菜单之set project to current file,也可点击工具栏中

光接收机的结构及原理(精)

第三部分光接收机的结构及原理 在有线电视 HFC 网络中, 光接收机通常位于光纤接点和有线电视的前端位置,它的主要功能是把光信号转变为 RF 信号,前面已经详细讲述了光探测器、光接收组件的原理及应用。光探测器是实现光 /电转换的关键部件,其质量的优劣决定了光接收机的性能指标与档次,光接收组件是光探测器与前置放大器的组合,在光接收机中, 无论是分离组件还是一体组件, 该部分的成本比重都比较大, 与光发射机的激光器一样, 不仅决定了光接收机的性能指标, 还将决定光接收机的价格。光接收的整机组成主要由光接收组件、功率放大模块及其附属功能电路组成, 除光接收组件外, 功率放大模块是光接收机的第二大核心元件。即使是采用相同的组件,由于采用不同档次、不同价位的放大模块组合, 整机也会有显著不同。有线电视技术发展到今天, 光接收机采用分离元件制作放大模块已不多见, 基本上全采用集成一体化组件结构。该结构模块大多属于厚膜集成电路, 它是用丝网印刷和烧结等工艺在同一陶瓷基片上制作无源网源, 并在其上组装分立的半导体芯片或单片集成电路、放大三极管管芯等, 另外再外加塑料密封,防止潮气、杂质的进入。 一、光接收机常用的放大模块介绍 能用于光接收机的模块有众多型号,排除品牌命名的差异,根据放大模块的增益划分有 14dB 、 18dB 、 20dB 、 22dB 、 27dB 等,用于单模块放大器的 34dB 的放大模块在光接收机中少有应用,当然也不排除低档光接收机应用的可能。根据放大模块具体放大电路结构的 不同划分:有推挽放大模块、功率倍增放大模块两种,而根据放大元件工艺的不同,放大模块又分为硅放大工艺、砷化镓工艺两种,在光接收机中采用的模块的命名, 一般以推挽和功率倍增为主要区分, 同时附加增益的差异与器件工艺, 如果不说是砷化镓工艺模块则所说的放大模块一般都是指硅工艺。 1.推挽放大模块的原理及结构。在实用的放大电路中,三极管的集电极并非总有电流流过, 根据集中极电流导通时间的长短, 通常把放大器分成甲类、乙类、丙类等。在输入信号的整个周期中都有电流流过集电极的放大器称为甲类放大器; 只

模电课程设计简易门铃

科技学院 《模拟电子技术》课程设计 题目简易门铃 学生梦蔚 专业班级11级电科一班 学号201131002 院(系)电气工程学院 指导教师月英 完成时间 2013年5月16日

目录 1 课程设计的目的 (1) 2 课程设计的任务与要求 (1) 3 实验设计方案及论证 (1) 3.1方案一 (1) 3.2方案二 (2) 3.3两种方案的比较 (3) 4 设计原理及功能说明 (4) 5硬件的制作与调试 (6) 6 总结 (12) 参考文献 (13) 附录1:总体电路原理图 (14) 附录2:元器件清单 (15)

1 课程设计的目的 ?通过该项目的学习,学生应当能够读懂项目任务书,看懂任务书中的电路原理图,分析电路工作原理,根据项目实训评价明确制考核要求和评分标准。 ?能熟练运用万用表检测各元器件的质量。 ?能熟练使用各焊接工具按照电路原理较长和工艺要求完成电路的连接。 ?熟练运用电子测量工具完成电路的调试和故障的排除。 ?具备一定的团队合作开发能力。 2 课程设计的任务与要求 ?设计一个门铃电路,两端接6v的电压,设置一个按钮开关,当按下开关时发出门铃在任听觉围的“铃”声,松开开关,则声音消失。 ?其中先设计出电路图,再通过电路图演示软件演示出其可用性,最后进行实际操作进行电路元件的选择与焊接。 ?要求用部中断实现,当按下门铃时,门铃发出响声,直到释放。 3 实验设计方案及论证 3.1 方案一

图3-1 原理图 电路原理: 由VT1、VT2及相关元件组成多谐振荡器,用以控制两种音调转换,由VT3、VT4等组成音频振荡器,当VT2导通时,相当于R1与R2并联,这时产生一种音调,当VT2截止时,只有R1参与音频振荡器工作,因此产生的是另外一种声音,电路中的R1、R2和C5的值决定了音调的高低当按下门铃开关后,门铃便会交替产生二种不同音调的声音。 3.2 方案二

电路四输入与非门设计 - 副本

四输入与非门课程设计任务书 学生姓名:专业班级: 指导教师:工作单位: 题目: CMOS四输入与非门电路设计 初始条件: 计算机、ORCAD软件、L-EDIT软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD软件、L-EDIT软件。 (2)设计一个CMOS四输入与非门电路。 (3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对CMOS四输入与非门电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

摘要........................................................................ I Abstract ................................................................... II 1 绪论 (1) 2 设计内容及要求 (2) 2.1 设计的目的及主要任务 (2) 2.2 设计思想 (2) 3软件介绍 (3) 3.1 OrCAD简介 (3) 3.2 L-Edit简介 (4) 4 COMS四输入与非门电路介绍 (5) 4.1 COMS四输入与非门电路组成 (5) 4.2 四输入与非门电路真值表 (6) 5 Cadence中四输入与非门电路的设计 (7) 5.1 四输入与非门电路原理图的绘制 (7) 5.2 四输入与非门电路的仿真 (8) 6 L-EDIT中四输入与非门电路版图的设计 (10) 6.1 版图设计的基本知识 (10) 6.2 基本MOS单元的绘制 (11) 6.3 COMS四输入与非门的版图设计 (13) 7课程设计总结 (14) 参考文献 (15)

1.2基本门电路设计-版图绘制

集成电路设计实习Integrated Circuits Design Labs I t t d Ci it D i L b 单元实验一(第二次课) 基本门电路设计--版图设计 2006-2007 Institute of Microelectronics Peking University

实验目的及时间安排 z内容一: z掌握基本门电路的版图设计 z熟悉Cadence版图设计、版图验证工具的使用 z内容二: z完成2与非门的设计,包括原理图输入、电路仿真、版图设计、版图 验证 Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page2

1. 版图图层 z本课程中使用CSMC双硅三铝混合信号工艺,主要的设计层包括 z TB:tub,n阱,作为pmos器件衬底 z TO:Thin Oxide,有源区,作为mos的源漏区 Thin Oxide z GT:gate,多晶硅1,作为mos栅极 z SP:P+注入区 z SN:N+注入区 z W1:接触孔,金属1到多晶硅和有源区的接触孔 z A1:铝1,第一层金属 z W2:通孔1,金属1和金属2的接触孔 z A2:铝2,第二层金属 z W3:通孔2,金属2和金属3的接触孔 z CP:bond pad,pad开孔 z IM:第二层多晶硅电阻阻挡层 z PC:poly Cap,用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅 l C z PT:p tub,p阱,作为nmos器件衬底 z详细的工艺信息请参考设计规则(在CSMC05MS/docs目录下) Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page3

模电课程设计 简易门铃

郑州科技学院 《模拟电子技术》课程设计 题目简易门铃 学生姓名孙梦蔚 专业班级11级电科一班 学号201131002 院(系)电气工程学院 指导教师李月英 完成时间 2013年5月16日

目录 1 课程设计的目的 (1) 2 课程设计的任务与要求 (1) 3 实验设计方案及论证 (1) 3.1方案一 (1) 3.2方案二 (2) 3.3两种方案的比较 (3) 4 设计原理及功能说明 (4) 5硬件的制作与调试 (6) 6 总结 (12) 参考文献 (13) 附录1:总体电路原理图 (14) 附录2:元器件清单 (15)

1 课程设计的目的 ?通过该项目的学习,学生应当能够读懂项目任务书,看懂任务书中的电路原理图,分析电路工作原理,根据项目实训评价明确制考核要求和评分标准。 ?能熟练运用万用表检测各元器件的质量。 ?能熟练使用各焊接工具按照电路原理较长和工艺要求完成电路的连接。 ?熟练运用电子测量工具完成电路的调试和故障的排除。 ?具备一定的团队合作开发能力。 2 课程设计的任务与要求 ?设计一个门铃电路,两端接6v的电压,设置一个按钮开关,当按下开关时发出门铃在任听觉范围内的“铃”声,松开开关,则声音消失。 ?其中先设计出电路图,再通过电路图演示软件演示出其可用性,最后进行实际操作进行电路元件的选择与焊接。 ?要求用内部中断实现,当按下门铃时,门铃发出响声,直到释放。 3 实验设计方案及论证 3.1 方案一

图3-1 原理图 电路原理: 由VT1、VT2及相关元件组成多谐振荡器,用以控制两种音调转换,由VT3、VT4等组成音频振荡器,当VT2导通时,相当于R1与R2并联,这时产生一种音调,当VT2截止时,只有R1参与音频振荡器工作,因此产生的是另外一种声音,电路中的R1、R2和C5的值决定了音调的高低当按下门铃开关后,门铃便会交替产生二种不同音调的声音。 3.2 方案二

简单电路设计设计大全

简单电路设计设计大全 1.保密室有两道门,只有当两道门都关上时(关上一道门相当于闭合一个开关),值班室内的指示灯才会发光,表明门都关上了.下图中符合要求的电路是 .小轿车上大都装有一个指示灯,用它来提醒司机或乘客车门是否关好。四个车门中只要2,该指示灯就会发光。下图为小明同学设计有一个车门没关好(相当于一个开关断开)的模拟电路图,你认为最符合要求的是 .中考试卷库大门控制电路的两把钥匙分别有两名工作人员保管,单把钥匙无法打开,如3 图所示电路中符合要求的是

”表示)击中乙方的导电服时,电路导通,4.击剑比赛中,当甲方运动员的剑(图中用“S甲 乙方指示灯亮。下面能反映这种原理的电路是 .家用电吹风由电动机和电热丝等组成,为了保证电吹风的安全使用,要求:电动机不工5作时,电热丝不能发热;电热丝发热和不发热时,电动机都能正常工作。如图所示电路中符( ) 合要求的是 S和车内司机右上方的开关、S6.一辆卡车驾驶室内的灯泡,由左右两道门上的开关S3l2闭合,门关上后,和SS共同控制。和S分别由左右两道门的开、关来控制:门打开后,S2211是一个单刀三掷开关,根据需要可将其置于三个不同位置。在一个电路中,S断开。S和S3l2无论门开还是关,灯都不亮;(1)要求在三个开关的共同控制下,分别具有如下三个功能:无论(3)(2)打开两道门中的任意一道或两道都打开时,灯就亮,两道门都关上时,灯不亮;门开还是关,灯都亮。如图所示的四幅图中,符合上述要求的电路是 图丁 C.图丙 D. B. A.图甲图乙,为了保证灯泡不被烧坏,发光时必须用风扇给予降温。.7教室里投影仪的光源是强光灯泡所示的灯泡不能发光。则在如图3带动风扇的电动机启动后要求:,灯泡才能发光;风扇不转, ( )

2_5Gb_sGaAsPIN_PHEMT单片集成光接收机前端_焦世龙

#光电子信息技术# 2.5Gb/s GaAs PIN/PHEMT单片集成光接收机前端** 焦世龙1,2**,叶玉堂1,陈堂胜2,杨先明1,李拂晓3,邵凯3,吴云峰1 (1.电子科技大学光电信息学院,四川成都610054; 2.单片集成电路与模块国家级重点实验室,江苏南京 210016;3.南京电子器件研究所,江苏南京210016) 摘要:采用0.5L m GaAs PHEMT工艺,研制了一种PIN光探测器和分布放大器单片集成850nm光接收机前 端。探测器光敏面直径为30L m,电容为0.25pF,10V反向偏压下的暗电流小于20nA。分布放大器-3dB带 宽接近20GHz,跨阻增益约46dB8;在50MHz~16GH z范围内,输入、输出电压驻波比均小于2;噪声系数在 3.03~6.50dB之间。单片集成光接收机前端在1.0和2.5Gb/s非归零(NRZ)伪随机二进制序列(PRBS)调制 的光信号下得到较为清晰的输出眼图。 关键词:PIN光探测器;分布放大器;光接收机;眼图 中图分类号:TN929.11文献标识码:A文章编号:1005-0086(2008)02-0191-05 2.5G b/s G aAs PIN/PHE MT m on olithic integ rated optical receiver front end JIAO Sh-i long1,2**,YE Yu-tang1,CHEN Tang-sheng2,YANG Xian-ming1,LI Fu-xiao3, SHAO Kai3,WU Yun-feng1 (1.School of Optoelectronic Information,U niversity of Electronic Science and Technology of China,Cheng du 610054,China; 2.N ational Key Laboratory of Monolithic Integrated Circuits and Modules,Nanjing210016,China; 3.Nanjing Electronic Devices Institute,Nanjing210016,China) A bs tra ct:T he front end of an850nm monolithic integrated opti cal receiver has been d evelop ed with0.5L m GaAs PHEMT process,whi ch comprises a PIN photodetector and a distri buted amplifi er.T he photodetector has a diameter and capacitance of30L m and0.25pF,respectively,as well as a dark current of less than20nA under the reverse bias of10V.T he distrib- uted amplifi er has a-3d B bandwi dth close to20GHz,with a transimpedance gain of46dB8;In the range of50MHz~ 16GHz,both the i nput and output voltage standi ng wave ratios are less than2;The noise figure varies from3.03to6.5d B wi thin the bandwidth.T he monolithic integrated optical receiver front end output eye di agrams for1Gb/s and2.5Gb/s NRZ pseudorandom binary seq uence(PRBS)are clear and satisfying. Key words:PIN photodetector;distri buted amplifier;opti cal receiver;eye diagram 1引言 放大器组成的光接收机前端在很大程度上决定了整个光接收机的性能。其中,光探测器主要有APD、PI N和MSM3种形式,前置放大器则包括基于MESFET、CMOS、PHEMT、MH EM T和HBT等器件的低阻抗、高阻抗、跨阻抗和分布参数放大器。针对光纤通信的3个窗口,光接收机前端又有Si、GaAs和InP系材料的区别[1~7]。如何将光探测器和前置放大器进行有效组合一直是研究的重点,并形成了以金丝互连和/倒扣焊0(flip-c hip)为代表的混合集成[2,7](hybrid integration)以及以空气桥或介质桥互连为代表的单片集成[3,4](monolithic integra tion)2种组合方式。 一般认为,光探测器和前置放大器2个分立芯片的混合集成有利于各自性能的最优化,工艺实现相对简单;单片集成将二者制作在同一衬底上,最大程度地减小了互连寄生参数的影响,使接收机前端超高速应用(几10甚至上102Gb/s)成为可能,并且互连一致性得到有效保证,有利于提高可靠性、减小体积和降低成本,尤其在强调品质因子的面阵列应用中显示出独特的优势。 单片集成对材料生长、结构设计和工艺实现等提出了较高要求,国内仅有少数单位开展这方面的研究[8,9]。基于南京电子器件研究所0.5L m GaAs PH EMT工艺,本文成功研制出集PIN光探测器与分布式前置放大器于一体的850nm单片集成 光电子#激光 第19卷第2期2008年2月Journal of Optoelectronics#Laser V o l.19N o.2F eb.2008 *收稿日期:2007-01-25修订日期:2007-07-01 *基金项目:国家自然科学基金资助项目(60277008);单片集成电路与模块国家重点实验室基金资助项目(51491050105DZ0201) **E-m ail:j-shi long@https://www.360docs.net/doc/503593892.html,