引脚,连线,PIN脚

添加引脚步骤:

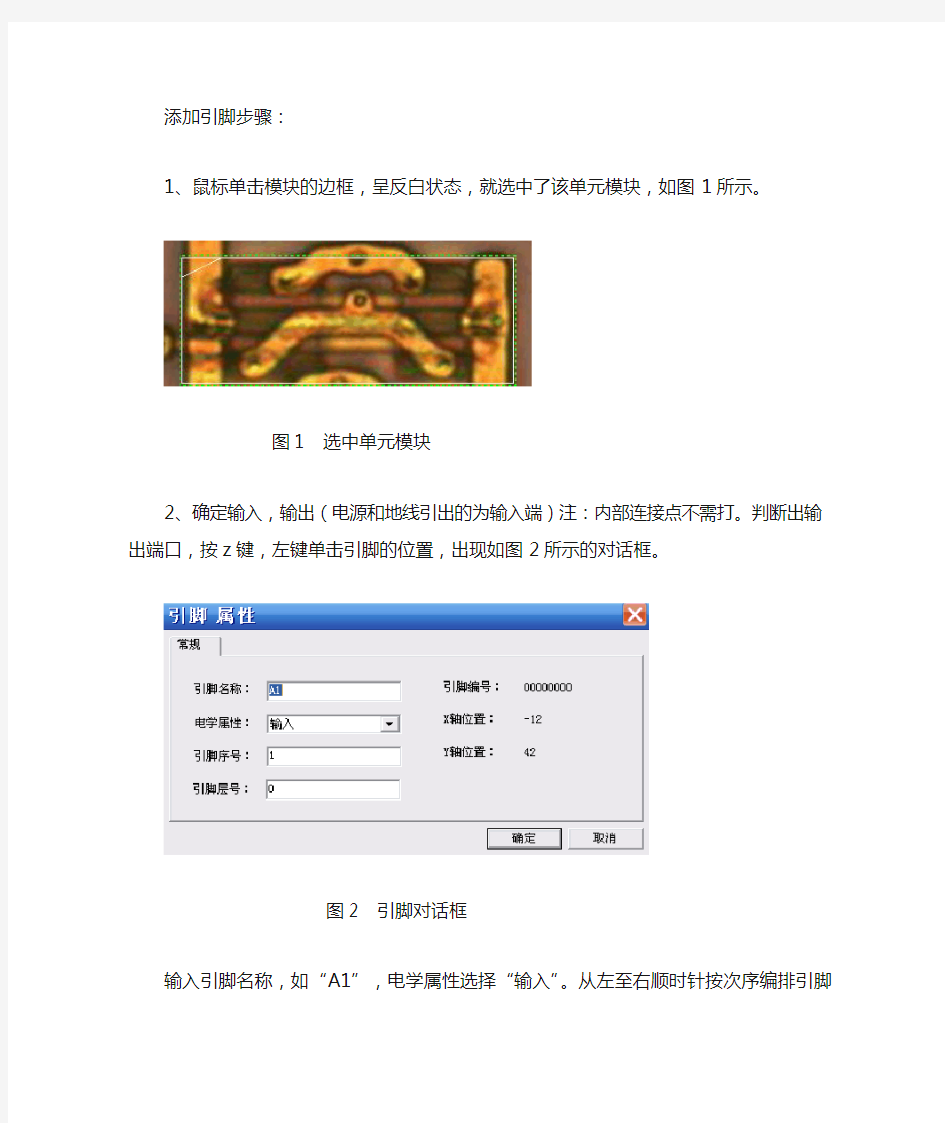

1、鼠标单击模块的边框,呈反白状态,就选中了该单元模块,如图1所示。

图1 选中单元模块

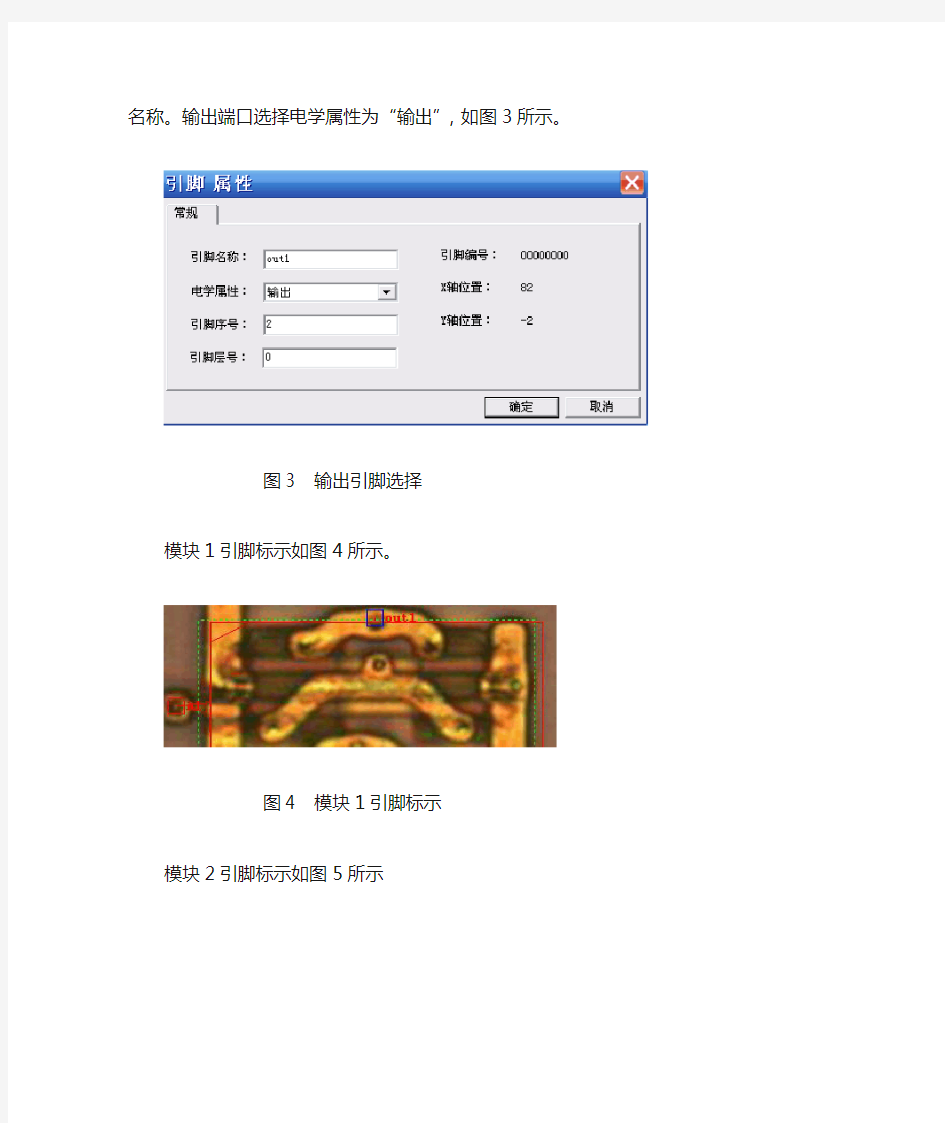

2、确定输入,输出(电源和地线引出的为输入端)注:内部连接点不需打。判断出输出端口,按z键,左键单击引脚的位置,出现如图2所示的对话框。

图2 引脚对话框

输入引脚名称,如“A1”,电学属性选择“输入”。从左至右顺时针按次序编排引脚名称。输出端口选择电学属性为“输出”,如图3所示。

图3 输出引脚选择模块1引脚标示如图4所示。

图4 模块1引脚标示

模块2引脚标示如图5所示

图5 模块2引脚标示

也就是说只要弄清楚该模块的逻辑功能,确定输入输出后标示引脚就很简单了。

连线步骤:

1.切换至铝2层,按按钮,锁住屏幕。

2.双击图6所示的颜色框可改变该层布线的颜色。

图6 显示视图

图中所示为引线可见,右键单击v,可将引线隐藏。

3.N键进行连线(横线),单击右键可进行端与端之间的连线或单击

引线”的对话框,其中可以选择引线类型,如“直线”“45度斜线”

和“斜线”,依不同的情况选择不同的类型。如图7所示。

图7 改变连线的角度连接完后如图8所示。

图8 铝1层连线

4.在铝2层布置连线(竖线),选取跟铝1层不同的颜色。连线如图

9所示。

图9 铝2层连线

打PIN脚步骤:

1.在铝1,铝2层中切换,观察引线,若不同层的引线连接同一点需

打pin脚,如图10,11所示两种不同打孔法。

图10 交叉法1 图11 交叉法2

2.对图10所示的引线可按insert键,然后按上、下、左、右键将孔

移至需打孔的位置。按Q键进行图10这种交叉法的打孔。打孔后如图12所示。按tab键可切换至下一位置选择是否打孔。

图12 打孔后的视图1

3.对图11所示的引线可按insert键,然后按上、下、左、右键将孔

移至需打孔的位置。按caps lock将空心孔变成实心孔,修改调整位置、线长,确保相连接,再按caps lock键进行打孔。如图13所示。

图13 打孔后视图2

整图打孔后如图14所示。

图14 打孔后的画面

一、线网同引脚的连接

在做完标PIN脚和线网提取工作之后,下面一步是要将这两个部分连接起来。具体步骤如下:

1、连接顺序:在工作区比较大或者是在对整个芯片分析的时候,

为了顺利连接线网和引脚,不至于有所遗漏,按左侧单元中显示的模块列表从上而下的顺序来进行连接比较好。在“显示”

中,右击所要连接的模块名称,选择“枚举所有实例”,然后就会在最下方的输出窗口中列举出这个单元模块的所有实例。如图(15)所示

图15 枚举所有实例

2、连接方法:双击第一个实例就会在工作区中出现该实例,然后就

可以将该模块和周围的线网连接起来。按工具条工具箱图标,在其子菜单内选择“连接引脚”(快捷键为“V”), 先点下PIN脚,再点下引线,就成功生成一个连接器(Connector)

。用鼠标先后单击两个引脚,可以在这两

个引脚之间产生一根引线。连完该实例后可以利用“F4”或者“]”来连接下一个实例,当需要修改时,按“[”可以返回到上一个实例。注意:1、线网同PIN脚连接时,因为当初画线网时有很多线并不确定最终位置,所以经常会出现要将引线加长或则截短。加长可直接在需要加长的那一层,画线网即可;截短操作为Shift+D,单击可剪断鼠标领域内的所有引线。

2、连接时要让连接器跨度有一定的长度,这样才算是好的连接方式,所以要结合加长和截短来完成。如图(16)所示

图16 两种连接方式的比较左侧为不好的连接方式,右侧为好的连接方式

检查线网和节点

在画完线网、融合和连接引脚后,需要对整个部分进行检查,方法如下:

选择“查看”下的“枚举”,如图(17)所示

图17 枚举元素

一般情况下,需要对以下四个进行检查:多叉头,悬空线头,拐点和邻层孔。

1、多叉头。一般选择“LAYER1”和“LAYER2”,如

图(18)所示

图18 枚举多叉头

2、悬空线头。分别选择“引线1”“引线2”进行检

查,如图(19)所示

图19 枚举悬空线头

3拐点。分别选择“引线1”“引线2”进行检查,如图(20)所示。

图20 枚举拐点

3、邻层孔。分别选择“引线1”“引线2”进行检查,

如图(21)所示。

图21 枚举邻层孔

注:每次检查都会有很多元素符合要求,当然有很多是不需要修改的,我们可以利用“[”和“]”来选择上一个或者下一个来检查,发现确有错误的地方要作出修改。一般“引线孔”比较多一点,在检查时要废点时间。因当时画线网或者打孔时有疏忽,一般经常有以下几种错误:

这种错误需要将工作区放大后才能看清楚,需要将多出的部分剪断,可使用Shift+D,然后鼠标单击就行,当然之后可能还需要修整一下。

这种错误可能在线网需要拐弯的时候出现,发现后只要按“N”,把缺的部分补上就行,当这两端不在一条水平线上时,可能需要按“N”+“F3”,然后出现如图(22)所示对话框。

图22 创建引线

在这里,我们可以选择“直线”“45度斜线”或者“斜线”,这样就可以去补上不在同一水平的断线。

实验电路结构图及芯片引脚对应表

实验电路结构图及芯片引脚对应表 NO.0 实验电路结构图 HEX PIO2PIO3PIO4PIO5PIO7PIO6D1 D2 D3 D4 D5 D6 D7 D8 D16 D15 D14 D13 D12 D11 数码1 数码2 数码3 数码4 数码5 数码6 数码7 数码8 S P E A K E R 扬声器 译码器译码器译码器译码器译码器译码器译码器译码器 FPGA/CPLD PIO15-PIO12 PIO11-PIO8PIO7--PIO2HEX 键1 键2 键3键4键5键6键7键8PIO47-PIO44 PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16目标芯片 附图2-2 实验电路结构图NO.0

附图2-3 实验电路结构图NO.1 附图2-4 实验电路结构图NO.2

êμ?éμ??·?á11í? NO.3 ò????÷ ò????÷ò????÷ò????÷ò????÷ò????÷ò????÷ò????÷D9 D16D15D14D13D12D11D10 D8D7D6D5D4D3D2D1PIO8 PIO9 PIO10 PIO11 PIO12 PIO13 PIO14 PIO15 S P E A K E R ??éù?÷ 1 2 3 4 5 6 7 8 ??±êD???FPGA/CPLD PIO0 PIO1PIO2PIO3PIO4PIO5PIO6PIO7?ü1 ?ü2?ü3?ü4?ü5?ü6?ü7?ü8PIO15-PIO8PIO47-PIO44 PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16 附图2-5 实验电路结构图NO.3 附图2-6 实验电路结构图NO.4

常见SPDT继电器的原理图元件和封装设计

常见SPDT继电器的原理图元件和封装设计

常见SPDT继电器的原理图和封装设计 1、5引脚SPDT继电器的原理图和封装设计 DXP系统提供的5引脚SPDT继电器原理图符号见图1,图中1号引脚为COM公共端,2号引脚为NC(Normal Close常闭),3号引脚为NO(Normal Open)常开,4、5号引脚为无极性线圈。默认的封装是DIP-P5/X1.65,该封装长35.5mm*宽21.6mm,尺寸比较大,在教育机器人驱动控制时一般使用小功率如HHC66A(T73) 继电器,但是一般生产厂家给出的器件说明书中的电气示意图和封装参数都没有标示引脚编号,如果设计时没有实际器件,在使用时从网络上难以找到完整信息,需要综合比较才能得到正确的设计。 图1 DXP2004系统给出的5引脚SPDT继 电器原理图符号和封装 在进行电路设计时,必须要有实物才能设计正确的元件封装。下面比较两个不同厂家生产的

5引脚SPDT继电器,进行原理图元件和元件封装的设计。 图2 5引脚SPDT继电器的封装设计比较 比较两个厂家相同尺寸封装的5引脚SPDT 继电器,从元件实物图片看,汇港继电器是左边三个引脚(图a),底面标示了各引脚的电气属性,没有引脚编号,给引脚按图示进行编号,得到电气特性和元件封装(见图c),松乐继电器是右边三个引脚(图b),给出了电气连接示意图和1、3号引脚编号,按此编号对所有引脚统一编号,得到电气特性和元件封装(见图d),比较(c)(d)发现两种继电器的电气特性是一致的,封装是中心对称的,常开引脚是左上角或右

下角的那个引脚,说明两种不同厂家生产出来的继电器可以通用,并使用统一的原理图元件和封装(设计封装时的尺寸位置根据元件说明书提供的参数确定)。 (a)原理图库元件RELAY-SPDT 5PIN (b)元件库封装5PIN-RELAY—SPDT 图3 自建库的5引脚SPDT继电器原理图 符号和封装 图4 HHC66A(T73)继电器封装参数及电

常用芯片引脚图

.v .. .. 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

.v .. .. 74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试 灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

松乐继电器使用手册

用单片机控制继电器 首先看看继电器的驱动 这是典型的继电器驱动电路图,这样的图在网络上随处可以搜到,并且标准教科书上一般也是这样的电路图. 单片机是一个弱电器件,一般情况下它们大都工作在5V甚至更低.驱动电流在m A级以下.而要把它用于一些大功率场合,比如控制电动机,显然是不行的.所以,就要有一个环节来衔接,这个环节就是所谓的"功率驱动".继电器驱动就是一个典型的、简单的功率驱动环节.在这里,继电器驱动含有两个意思:一是对继电器进行驱动,因为继电器本身对于单片机来说就是一个功率器件;还有就是继电器去驱动其他负载,比如继电器可以驱动中间继电器,可以直接驱动接触器,所以,继电器驱动就是单片机与其他大功率负载接口.这个很重要,因为,一直让我们的电气工程师(我指的是那些没有学习过相应的电子技术的)感到迷惑不解的是:一个小小的芯片,怎么会有如此强大的威力来控制像电动机这样强大的东西? 怎么样理解这个电路图? 要理解这个电路,其实也比较容易.那么请您按照我的思路来,应该没有问题:

首先的,里面的三极管很重要.三极管是电子电路里很重要的一个元件.怎么样理解三极管呢? 简单的来说三极管有两个作用一个是放大作用,一个是开关作用.(严格来讲开关作用是放大作用的极限情况,不过没关系,把两者分开,更便于理解它的工作原理).在这里,我们只了解它跟本电路有关的开关作用. 首先把三极管想成一个水龙头. 上面的V c c就是水池,继电器是一个水轮机,下面的G N D是比水池低的任何一点.刚才说过,三极管就是水龙头,它的把手就是那个带有电阻的引脚. 现在,单片机的某一个需要控制这个继电器电路的输出引脚就是一只"手",当单片机的这个引脚输出低电平的时候,就像"手"在打开三极管"水龙头",水就从上往下流,继电器"水轮机"就开始转起来了.反之,如果是输出高电平,"手"就开始关"水龙头",继电器"水轮机"因为没有水流下来,就会停止. 这就是三极管的开关作用. 简单的理解和记忆就是:三极管是一个开关器件,其实你真的可以将它看成是一个开关,只不过它不是用手来控制,而是用电压(电流)来控制的,因此,三极管有些时候也被称做电子开关(与机械开关相区别). 图上还有一个东西,是保护二极管,如果不需要深入理解的话,你大可不必追就为什么有它存在,但是一定得记住,只要是用三极管驱动继电器的场合,一般都有它的存在.需要特别注意的是它的接法:并联在继电器两端阴极一定是接V c c

芯片引脚图及引脚描述

555芯片引脚图及引脚描述 555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。 1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。 当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平; 2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。 4脚是复位端,当4脚电位小于0.4V时,不管2、6脚状态如何,输出端3脚都输出低电平。 5脚是控制端。 7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。 555集成电路管脚,工作原理,特点及典型应用电路介绍. 1 555集成电路的框图及工作原理 555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。 2. 555芯片管脚介绍 555集成电路是8脚封装,双列直插型,如图2(A)所示,按输入输出的排列可看成如图2(B)所示。其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。 图2 555集成电路封装图 我们也可以把555电路等效成一个带放电开关的R-S触发器,如图3(A)所示,这个特殊的触发器有两个输入端:阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:Q=1时DIS端接地,Q=0时DIS 端悬空。另外还有复位端MR,控制电压端Vc,电源端VDD和 地端GND。这个特殊的触发器有两个特点: (1)两个输入端的触发电平要求一高一低,置零端R即阈值端(TH)要求高电平,而置位端s 即触发端(TR)则要求低电乎; (2)两个输入端的触发电平使输出发生翻转的阈值电压值也不同,当V c端不接控制电压时,对TH(R)端来讲,>2/3VDD是高电平1,<2/3VDD是低电平0:而对TR(S)端来讲,>1/3VDD是

继电器控制电路

三极管驱动继电器电路图分析 利用三极管饱和导通和截止的的特性,本身就可以实现接通和断开的功能,但由于它的带载功率有限,所以需配继电器扩流,并且可以扩充触点的数量,该电路是PNP三极管,所以采用集电极接低电平方式输出,P37为上拉电阻,当基极没有输入脉冲或电压时,基极为高电平,因为这是反极性三极管,所以平时是截止的,只有基极输入低电平,降低基极电压,这时三极管导通,继电器线圈得电吸合,原常闭触点断开,常开触点吸合,完成设备的接通与断开功能。图中二极管反向接在线圈两端,是保护线圈不受反峰电压的冲击,对继电器起到保护作用。 三极管驱动继电器电路 我用的是S9013,请问这个电路该怎样画,S9013是不是一个NPN型三极管,还有我用的是STC89C52芯片。 常用的小型继电器工作电压有5V和12V两种,你使用的时候最好有一个9V或者12V的电压(如果你选12V的继电器,那么电压要再高一些). 单片机IO口输出控制信号,最好采用低电平控制导通的方式,也就是IO口输出0控制导通,1截止,因为IO口的灌电流较大而拉电流能力不足.这时候三极管应该选择PNP的,比如9012,8550之类的. 你选择的9013理论上可行,但实际使用中一般不这么做. 下面是接法:(以PNP三极管为例) 单片机IO口输出控制信号接三极管基极,继电器的线圈正极接三极管的C 极,线圈负极接一个小电阻比如75欧之后接电源负极(也就是继电器一定要在集

电极通路上),三极管的E极接电源正极,然后在线圈的正负极之间并联一个二极管比如1N4007. 三极管驱动继电器 2009-09-23 21:49:47| 分类:Electronic&&Elec | 标签:|字号大中小订阅 继电器线圈需要流过较大的电流(约50mA)才能使继电器吸合,一般的集成电路不能提供这样大的电流,因此必须进行扩流,即驱动。 图1.21所示为用NPN型三极管驱动继电器的电路图,图中阴影部分为继电器电路,继电器线圈作为集电极负载而接到集电极和正电源之间。当输入为0V时,三极管截止,继电器线圈无电流流过,则继电器释放(OFF);相反,当输入为+VCC时,三极管饱和,继电器线圈有相当的电流流过,则继电器吸合(ON)。 图1.21 用NPN三极管驱动继电器电路图 当输入电压由变+VCC为0V时,三极管由饱和变为截止,这样继电器电感线圈中的电流突然失去了流通通路,若无续流二极管D将在线圈两端产生较大的反向电动势,极性为下正上负,电压值可达一百多伏,这个电压加上电源电压作用在三极管的集电极上足以损坏三极管。故续流二极管D的作用是将这个反向电动势通过图中箭头所指方向放电,使三极管集电极对地的电压最高不超过+VCC +0.7V。 图1.21中电阻R1和R2的取值必须使当输入为+VCC时的三极管可靠地饱和,即有。 例如,在图1.21中假设Vcc = 5V,,,则有。 而 则

数字逻辑实验内容及芯片引脚图

数字逻辑实验计划及要求(附录:实验所用芯片引脚图及功能说明) 实验一逻辑门功能验证及应用电路实验 1.实验目的: (1)了解并掌握基本逻辑门电路的逻辑功能; (2)熟悉基本逻辑门电路的应用; (3)熟悉三态门和OC门电路的应用; (4)学习实验台的使用方法。 2.实验所用器件: 四二输入端与非门组件2片,型号为:74LS00 四二输入端与非门(OC)组件1片,型号为:74LS01 四二输入端或非门组件1片,型号为:74LS02 二与或非门组件1片,型号为:74LS51 四异或门组件1片,型号为:74LS86 四三态门组件1片,型号为:74LS125 排电阻(上拉电阻) 3.预习要求: (1)查出实验用器件引脚功能,画出实验电路图; (2)复习TTL各逻辑门电路的工作原理; (3)按实验内容要求设计电路。 4.实验内容 (1)测试实验所用器件的逻辑功能,填写真值表。 (2)用一片74LS00实现一2输入端异或门的功能。 (3)用一片74LS01及排电阻实现芯片74LS51的功能,做(AB+CD)’一组。 (4)用三态门组成两路总线传输电路。 5.实验要求 记录各实验观察结果并与理论所得各真值表进行比较。 6.思考 任何一逻辑电路均可分别用与非门,或非门,与或非门实现,为什么? 实验二组合电路功能验证及应用电路实验 1.实验目的: (1)熟悉常用组合逻辑芯片的功能; (2)掌握组合逻辑电路的设计方法。 2.实验所用器件 3-8线译码器一片,型号为:74LS138 8路数据选择器一片,型号为:74LS151 4位数码比较器一片,型号为:74LS85 四输入端与非门一片,型号为:74LS20 3.实验内容 (1)74LS85,74LS151的功能。 (2)用一片74LS85及一片74LS00组成5位二进制数值比较器。

74LS系列主要芯片引脚及参数

<74LS00引脚图> 74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。 Vcc 4B 4A 4Y 3B 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ __ │14 13 12 11 10 9 8│ Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1B 1Y 2A 2B 2Y GND 74LS00真值表: A=1 B=1 Y=0 A=0 B=1 Y=1 A=1 B=0 Y=1 A=0 B=0 Y=1

74HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下: 当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。 74LS138的作用: 利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器 用与非门组成的3线-8线译码器74LS138

图74ls138译码器内部电路 3线-8线译码器74LS138的功能表 备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。<74ls138功能表> 74LS138逻辑图

无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。 当附加控制门的输出为高电平(S=1)时,可由逻辑图写出 74ls138逻辑图 由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。 71LS138有三个附加的控制端、和。当、时,输出为高电平(S=1),译码器处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。 带控制输入端的译码器又是一个完整的数据分配器。在图3.3.8电路中如果把作为“数据”输入端(在同一个时间),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。这就不难理解为什么把叫做地址输入了。例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。 例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。试画出八个输出管脚的波形。

WRG旺荣 通用电子继电器 竞品型号对照表 20180629

TYCO AXICOM OEG P & B SCHRACK 1RA1HF105F-1G8P JTN/JTV ORU T9A/T90T9A 832HAT901AZ2250/2251CT 5905 490/590 W90 2RA2HF2160JT T9A/T90852 HAT902AZ2160 CT 3RB HF115F G2RL JW1/JW2/DJ RT RT/42900/RT1/RT2FTR-H1/K1 M2541 series 881/888SPR AZ743/761/762/763 TH K172B 4RC HF46F/HF46F-G G5NB LD PCJ FTR3 202/202H CU 5RD HF3FA/HF3FF/HF3FD G5LC/G5LE JS PCE/ORWH T72T7N VTA/H 36.11833H KLT AZ943/AZ943H/9431270496W178RE 6RE HF7520 G5CA JV/JVN PCD PCD 201 MHR AZ9481CQ 7RF HF102F/HF160F/HF161F G4A LF PCFN AZ769 502 8RJ HF32F/HF32FV/HF32F-G/HF32FV-G OJ/OJE OJ 835/835NL AZ765/AZ767CS 9RJE HF33F G5SB/G5Q JQ/PQ PCH RE/REL JY JF 892HPR AZ94010RL HF18FF MY2/3/4HC/HJ PCL KHA ZT 55 series SCLB/SCLD UJJ AZ164-168KMH C281K102/104/112/114 280/290 1310/1315/5310/5315156W7811RLH HF13F LY1/2HL DRET/RET K10TM FRL26056 series SCLA/SCL UJ2AZ164-168KML C281 1390/1395 258W7812RMI/RMIH HF14FW G2R JR1AF OMI-H/OZ RKA/RKS FBR610 MZPA-001 40.61793P PR AZ755 K2861655 498 W76 13RMIE HF157F G2RS HN 46 series 14RMIF HF62F G5J JR1AF-TMP OMIF VR 302AZ75615 RY HF41F G2RV PE/PF V23092(SNR) FTR-LY 34.51 882 AZ699 CW 序号 旺荣Aromat Cornell Dublier GOODSKY CIT IDEC Relpol HANDOUK Million Spot SUN HOLD SANYOU FORWARD ASIAON TIANBO WANJIA TYH/HG 松乐浙江欣大台湾欣大无锡明达 汇港 16RA1JT CDR8/CDR80/CDR88 GU J115F1RA RT1SLA NT90 (塑封)JQX-15F(T90)HJQ-15F WJ115HG4115/HG4234 SLA HHC67E(T90)953G CMP717RA2GU J115F2 RT3 SLI NT90T (T91)矮壳身 JQX-21FS(T93) HJQ-15-2WJ117SLI 953B CMP8 18RB EM/EZ ERM84/85HL2TNC NT75-1/NT75-2 JQX-115F TRA1/TRA2/TRA3 WJ121/WJ122/WJ123/WJ124 HG4509 Y02 HCP1/HCP2/HCP3 19RC BC4 SRB/SRC 20RD JS/JSM CDR70RW J107F RM50HA1RAS SRD NT73 4098TRKF WJ107HG4231SRB/SRD HHC66A(T73)943 MR72HRS4 21RE SF-SFG J111HC2SJV SPA NT76 1A WJ111 945 22RF JM J120 HM3SG4SFK/SFK-P/DI1U-P JQX-102F TRAF HG4239SLK 948CMP623RJ GJ/GQ HE1 SOJ SJ JZC-32F JZC-32F TRG1 WJ105HG4183SRSB HHC69E HRS324RJE JQ J105E HF SJE JZC-33F JZC-33F WJ105E HG4503SRSC HRS3T 25RL HC2/HC4CDR10RET J152RM2/RY4ER2/ER3/ER4GA RHS SMET JZX-18FF HH5P HJQ-22F WJ152HG4104SMB HHC68B 952/Y07HH52/HH53/HH54 26RLH HL2CDR40/50RET J151 RH2ERY2 GB RHL(1C2C) SME JQX-13F.1c2c JQX-13F HJQ-13F-1C/2C WJ151HG4104L SMBH HHC68A 951(1C、2C)/Y06HH61/HH6227RMI/RMIH JR1A CDR67 GSZ RG RM63/ERMB631/632 HL1 JQX-14FF WJ114 HG4124L 942-T 28RMIE RJ 29RMIF ALE J121 HM1JQX-62F HG4515SMIH-Plug in HRMF 30 RY RM699BV Struthers Dunn GRUNER Deltrol Guardian Midtex Magnecraft FEME FINDER SONGCHUAN HASCO ZETTLER NEC WRG旺荣继电器型号对照表-通用功率继电器 序号 TYCO GROUP 注释:因各品牌产品线更新频繁,此表仅做参考。 旺荣HONGFA OMRON Panasonic FUJITSU

常用芯片引脚图[1]

您的数字ID 是:463099 您的密码是:1.8667 附录三 常用芯片引脚图 一、单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。 ALE/PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 XTAL1、XTAL2:内部振荡器反相器输 P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS

常见SPDT继电器的原理图元件和封装设计

常见SPDT继电器的原理图和封装设计 1、5引脚SPDT继电器的原理图和封装设计 DXP系统提供的5引脚SPDT继电器原理图符号见图1,图中1号引脚为COM公共端,2号引脚为NC(Normal Close常闭),3号引脚为NO(Normal Open)常开,4、5号引脚为无极性线圈。默认的封装是DIP-P5/X1.65,该封装长35.5mm*宽21.6mm,尺寸比较大,在教育机器人驱动控制时一般使用小功率如HHC66A(T73) 继电器,但是一般生产厂家给出的器件说明书中的电气示意图和封装参数都没有标示引脚编号,如果设计时没有实际器件,在使用时从网络上难以找到完整信息,需要综合比较才能得到正确的设计。 图1 DXP2004系统给出的5引脚SPDT继电器原理图符号和封装在进行电路设计时,必须要有实物才能设计正确的元件封装。下面比较两个不同厂家生产的5引脚SPDT继电器,进行原理图元件和元件封装的设计。 图2 5引脚SPDT继电器的封装设计比较 比较两个厂家相同尺寸封装的5引脚SPDT继电器,从元件实物图片看,汇港继电器是左边三个引脚(图a),底面标示了各引脚的电气属性,没有引脚编号,给引脚按图示进行编号,得到电气特性和元件封装(见图c),松乐继电器是右边三个引脚(图b),给出了电气连接示意图和1、3号引脚编号,按此编号对所有引脚统一编号,得到电气特性和元件封装(见图d),比较(c)(d)发现两种继电器的电气特性是一致的,封装是中心对称的,常开

引脚是左上角或右下角的那个引脚,说明两种不同厂家生产出来的继电器可以通用,并使用统一的原理图元件和封装(设计封装时的尺寸位置根据元件说明书提供的参数确定)。 (a)原理图库元件RELAY-SPDT 5PIN (b)元件库封装5PIN-RELAY—SPDT 图3 自建库的5引脚SPDT继电器原理图符号和封装 图4 HHC66A(T73)继电器封装参数及电气连接图 2、6引脚SPDT继电器的原理图和封装设计 汇港继电器HRS1H-S-DC12V 汇科继电器HK4100F-DC5V-SH 超小型6引脚SPDT继电器,安装尺寸(单位mm):长15.5*10.5*11.8,引脚长度3.5。器件说明书给出封装参数和电气图。

常用芯片引脚图

. . 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

. . 74LS30 数据手册 74LS32数据手册 74LS33 数据手册 74LS37 数据手册 74LS38数据手册 74LS40 数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试灯 输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

常用芯片引脚图

附录三 常用芯片引脚图 一、 单片机类 1、MCS-51 芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。 MCS-51系列单片机共有40条引脚,包括32 条I/O 接口引脚、4条控制引脚、2条电源引 脚、2条时钟引脚。 引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时 的地址/数据复用口。 P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。 P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。 P3.0~P3.7:P3口8位口线,第一功能作为 通用I/O 接口,第二功能作为为单片机的控 制信号。 ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号) PSEN :片外程序存储器开发信号引脚(输出信号) EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚 RST/VPD :复位/备用电源引脚 2、MCS-96 芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单 片机系列。它含有比较丰富的软、硬件 资源,适用于要求较高的实时控制场合。 它分为48引脚和68引脚两种,以48引 脚居多。 引脚说明: RXD/P2.1 TXD/P2.0:串行数据传出分发 送和接受引脚,同时也作为P2口的两条 口线 HS1.0~HS1.3:高速输入器的输入端 HS0.0~HS0.5:高速输出器的输出端(有 两个和HS1共用) Vcc :主电源引脚(+5V ) Vss :数字电路地引脚(0V ) Vpd :内部RAM 备用电源引脚(+5V ) V REF :A/D 转换器基准电源引脚(+5V ) AGND :A/D 转换器参考地引脚 12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1 P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7 EA/V PP ALE/PROG PSEN P2.7/A 15P2.6/A 14P2.5/A 13 P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751

常用芯片引脚图

. . .. .v .. .. 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

. . .. .v .. .. 74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI)必须开路或保持高电平,如果不 要灭十进制数零,则动态灭灯输入(RBI)必须开路或为高电平。 [2].将一低电平直接输入BI端,则不管其他输入为何电平,所有的输 出端均输出为低电平。 [3].当动态灭灯输入(RBI)和A,B,C,D输入为低电平而试灯输入为高 电平时,所有输出端都为低电平并且动态灭灯输入(RBO)处于第电 平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO)开朗路或保持高电平而试 灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO是线与逻辑,作灭灯输入(BI)或 动态灭灯(RBO)之用,或者兼为二者之用。

2020年芯片封装大全(图文对照)

芯片封装大全(图文对照)

封装有两大类;一类是通孔插入式封装(through-holepackage);另—类为表面安装式封装(surfacemountedPackage)。每一类中又有多种形式。表l和表2是它们的图例,英文缩写、英文全称和中文译名。图6示出了封装技术在小尺寸和多引脚数这两个方向发展的情况。 DIP是20世纪70年代出现的封装形式。它能适应当时多数集成电路工作频率的要求,制造成本较低,较易实现封装自动化印测试自动化,因而在相当一段时间内在集成电路封装中占有主导地位。 但DIP的引脚节距较大(为2.54mm),并占用PCB板较多的空间,为此出现了SHDIP和SKDIP等改进形式,它们在减小引脚节 距和缩小体积方面作了不少改进,但DIP最大引脚数难以提高(最大引脚数为64条)且采用通孔插入方式,因而使它的应用受到 很大限制。 为突破引脚数的限制,20世纪80年代开发了PGA封装,虽然它的引脚节距仍维持在2.54mm或1.77mm,但由于采用底面引 出方式,因而引脚数可高达500条~600条。 随着表面安装技术(surfacemounted technology,SMT)的出现,DIP封装的数量逐渐下降,表面安装技术可节省空间,提高性能,且可放置在印刷电路板的上下两面上。SOP应运而生,它的引脚从两边引出,且为扁平封装,引脚可直接焊接在PCB板上,也不再需要插座。它的引脚节距也从DIP的2.54mm减小到1.77mm。后来有SSOP和TSOP改进型的出现,但引脚数仍受到限制。 QFP也是扁平封装,但它们的引脚是从四边引出,且为水平直线,其电感较小,可工作在较高频率。引脚节距进一步降低到1.00mm,以至0.65mm和0.5mm,引脚数可达500条,因而这种封装形式受到广泛欢迎。但在管脚数要求不高的情况下,SOP 以及它的变形SOJ(J型引脚)仍是优先选用的封装形式,也是目前生产最多的一种封装形式。 方形扁平封装-QFP(QuadFlatPackage) [特点]引脚间距较小及细,常用于大规模或超大规模集成电路封装。必须采用SMT(表面安装技术)进行焊接。操作方便,可靠性 高。芯片面积与封装面积的比值较大。 小型外框封装-SOP(SmallOutlinePackage) [特点]适用于SMT安装布线,寄生参数减小,高频应用,可靠性较高。引脚离芯片较远,成品率增加且成本较低。芯片面积与封装面积比值约为1:8 小尺寸J型引脚封装-SOJ(SmalOutlineJ-lead) 有引线芯片载体-LCC(LeadedChipCarrier) 据1998年统计,DIP在封装总量中所占份额为15%,SOP在封装总量中所占57%,QFP则占12%。预计今后DIP的份额会进一步下降,SOP也会有所下降,而QFP会维持原有份额,三者的总和仍占总封装量的80%。 以上三种封装形式又有塑料包封和陶瓷包封之分。塑料包封是在引线键合后用环氧树脂铸塑而成,环氧树脂的耐湿性好,成本也低,所以在上述封装中占有主导地位。陶瓷封装具有气密性高的特点,但成本较高,在对散热性能、电特性有较高要求时,或者用于国防军事需求时,常采用陶瓷包封。 PLCC是一种塑料有引脚(实际为J形引脚)的片式载体封装(也称四边扁平J形引脚封装QFJ(quadflatJ-leadpackage)),所以

松乐继电器

SONGLE RELAY

RELAY ISO9002

SLA

1. MAIN FEATURES

? Up to 30A switching in SPST and 20A switching in spot arrangements. ? Available as an open-frame relay, with a snap-on dust cover or with an immersion cleanable, plastic sealed case.

2. APPLICATIONS

? Used for power switching, Electrical Heater, ventilator, Air conditioning, Refrigerating, Automobile and House-hold Appliance.

3. ORDERING INFORMATION

SLA Model of relay SLA XX VDC Nominal coil voltage 05 06 09 12 18 24 48 110VDC S Structure S:Sealed type Coil L sensitivity C Contact form A:1 form A B:1 form B C:1 form C

L:0.93W D:Special

F:Flux free type

4. RATING

20A/28VDC 250VAC 30A/30VDC 250VAC CCC FILE NUMBER:CQC03001003728 UL/CUL FILE NUMBER: E179944 TUV FILE NUMBER: R50056114 30A/250VDC NO:20A/240VAC 28VDC NC:10A/240VAC 28VDC NO:30A/250VAC 30VDC NC:20A/250VAC 30VDC

5. DIMENSION(unit:mm)

DRILLING(unit:mm)

WIRING DIAGRAM

1

各种芯片特性对比

先简单的将各种无线收发芯片做个对比,然后从中选出一个较为合适的芯片在详细与CC2540蓝牙芯片作对比。 表1 各种无线收发芯片对比 根据上表各种芯片的性能对比,结合一些实际因素,在这些芯片中我们初步认为nRF2401无线收发一体芯片比较适合。因为其与蓝牙芯片一样都是工作在2.4GHz自由频段。为此我们在下面将进一步将其与CC2540蓝牙芯片做进一步的对比,然后从两者中选出一个更为合适的芯片。

下面我们将对比nRF24l01芯片与CC2540蓝牙芯片的优缺点表2 CC2540与nRF24L01芯片对比

CC2540芯片简介: 图1 CC2540引脚图 从上图可知,CC2540芯片共有40个引脚,全部引脚可分为I/O端口线引脚、电源线引脚和控制线引脚三类。 I/O端口线引脚: CC2540有19个可编程的I/O引脚,p0、p1口是完全的8位口,p2口只有3个可以使用的位。 I/O端口的关键特性: (1)可设置为通常的I/O口,也可设置为外围I/O口使用; (2)在输入时有上拉和下拉能力; (3)19个数字I/O口引脚都具有响应外部的中断能力。如果需要外部中断,可对I/O 口引脚产生中断,同时外部的中断事件也可能被用来唤醒休眠模式。 (4)12~19脚(即P0_0~P0_7):具有4mA输出驱动能力; 9/11脚(即P1_0~P1_1):具有20mA输出驱动能力; 5~8脚(P1_2~P1_5)、34~36脚(P2_0~P2_2)、37~38脚(P1_6~P1_7):具有4mA 输出驱动能力。

表4 控制线引脚功能 用CC2540芯片设计的蓝牙模块系统框图如图2所示 图2 蓝牙模块系统框图 从图2可以看出外围电路设计的设计主要围绕主控芯片CC2540核心芯片进行设计。外围电路主要包括两个时钟、电源电路、阻抗匹配电路、通信接口电路、天线等。 片内供压方式:1.8V的稳压器外加去耦电容;现实中可以用40号管脚外加1μf的电容来