EDA序列信号发生器与检测器

实验报告

学生姓名:EDA小王子学号:国家机密专业班级:国家机密

实验类型:□验证□综合√设计□创新实验日期:国家机密实验成绩:很高实验三序列信号发生器与检测器设计

一、实验目的

1.学习一般有限状态机的设计;

2.实现串行序列的设计。

二、设计要求

要求用状态机设计实现串行序列检测器的设计,先设计(可用原理图输入法)序列信号发生器,产生序列:0111010011011010;再设计检测器,若检测到串行序列11010则输出为“1”,否则输出为“0”,并对其进行仿真和硬件测试。

三、实验设备

PC机,Quartu eⅱ软件,实验箱

四、实验原理

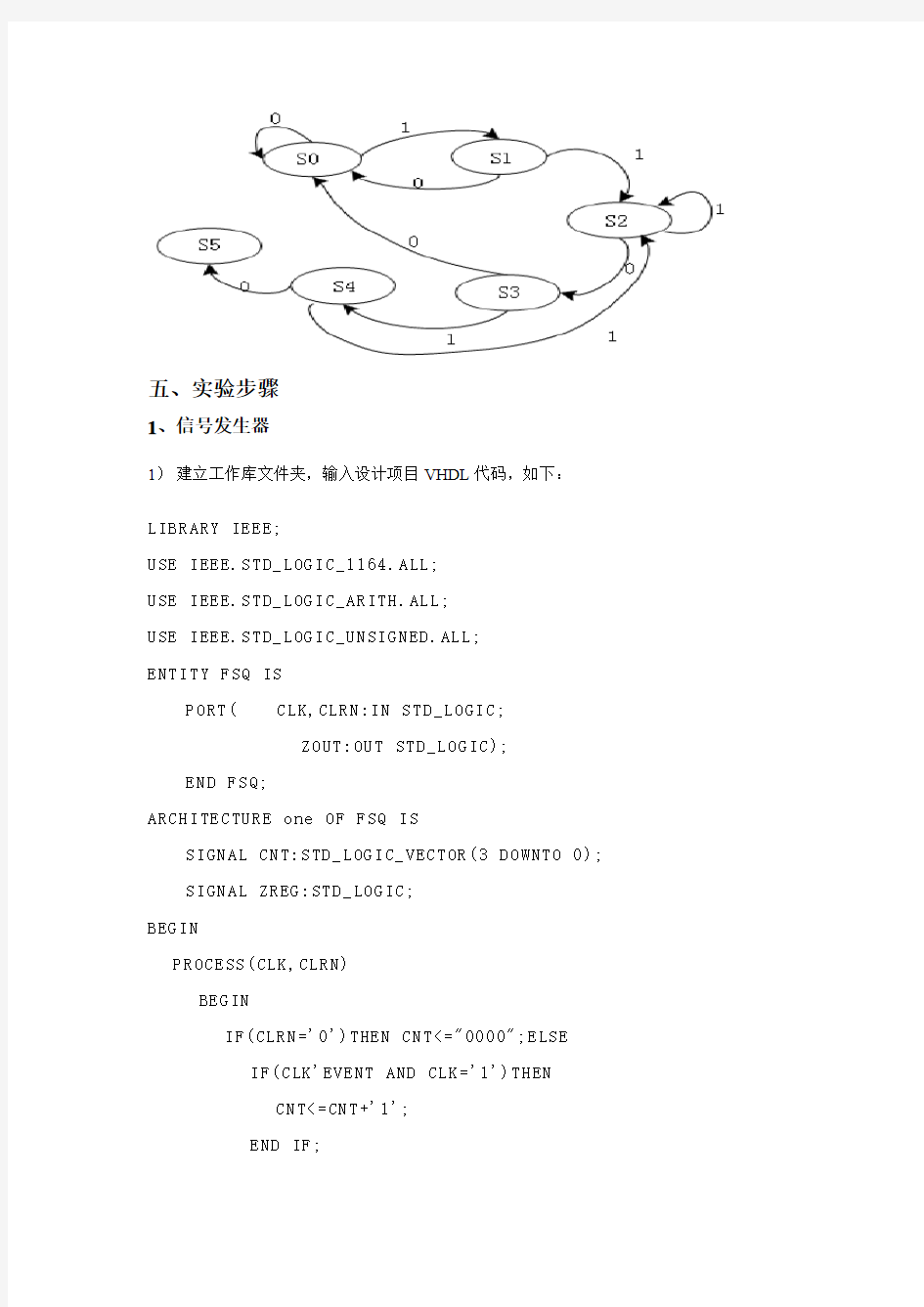

1、序列信号发生器

复位信号CLRN。当CLRN=0时,使CNT=0000,当CLRN=1时,不影响程序运行,每来一个CLK脉冲CNT加一。

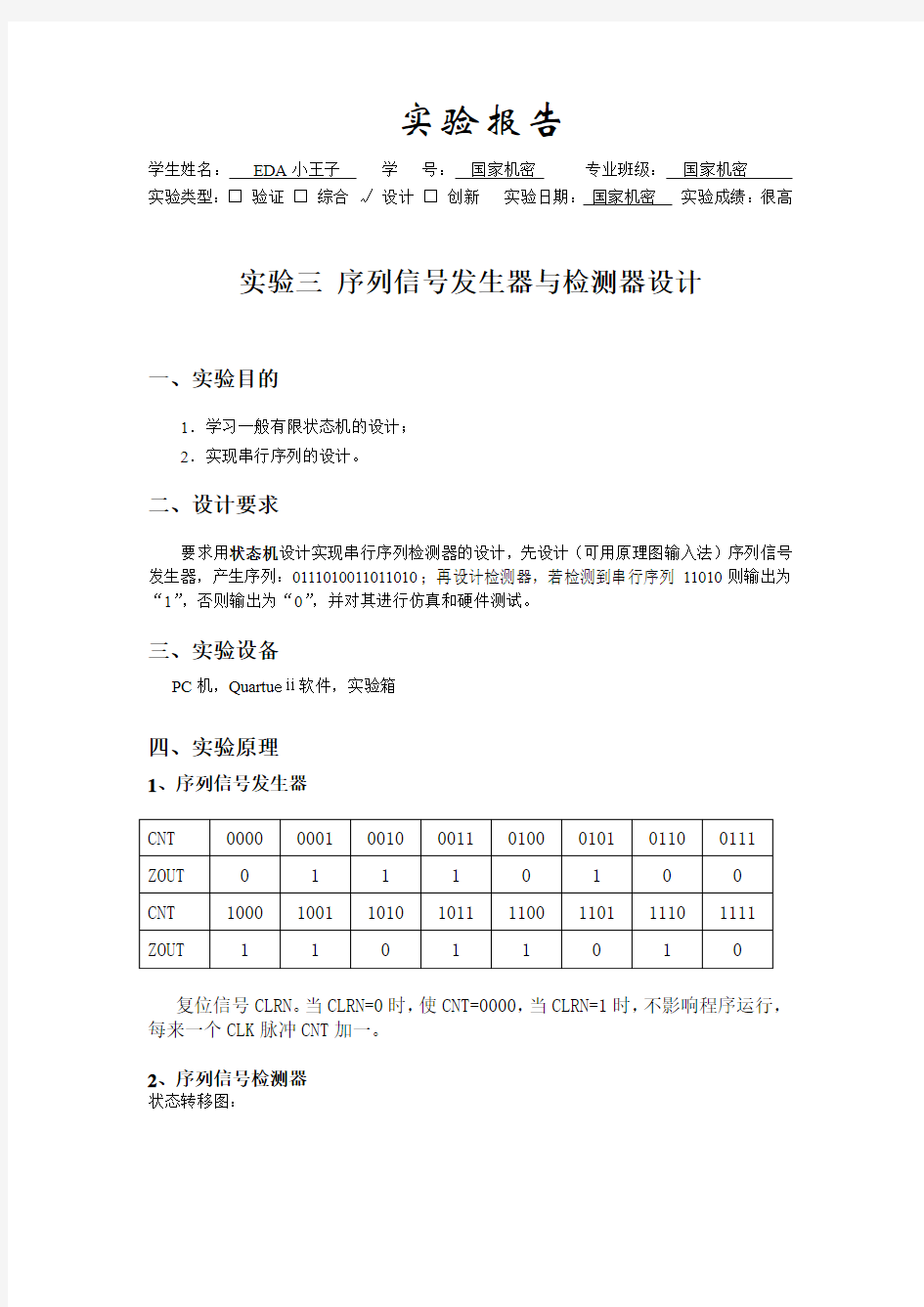

2、序列信号检测器

状态转移图:

五、实验步骤

1、信号发生器

1)建立工作库文件夹,输入设计项目VHDL代码,如下:

L I B R A R Y I E E E;

U S E I E E E.S T D_L O G I C_1164.A L L;

U S E I E E E.S T D_L O G I C_A R I T H.A L L;

U S E I E E E.S T D_L O G I C_U N S I G N E D.A L L;

E N T I T Y

F S Q I S

P O R T(C L K,C L R N:I N S T D_L O G I C;

Z O U T:O U T S T D_L O G I C);

E N D

F S Q;

A R C H I T E C T U R E o n e O F F S Q I S

S I G N A L C N T:S T D_L O G I C_V E C T O R(3D O W N T O0);

S I G N A L Z R E G:S T D_L O G I C;

B E G I N

P R O C E S S(C L K,C L R N)

B E G I N

I F(C L R N='0')T H E N C N T<="0000";E L S E

I F(C L K'E V E N T A N D C L K='1')T H E N

C N T<=C N T+'1';

E N D I F;

E N D I F;

E N D P R O C E S S;

P R O C E S S(C N T)

B E G I N

C A S E C N T I S

W H E N"0000"=>Z R E G<='0';

W H E N"0001"=>Z R E G<='1';

W H E N"0010"=>Z R E G<='1';

W H E N"0011"=>Z R E G<='1';

W H E N"0100"=>Z R E G<='0';

W H E N"0101"=>Z R E G<='1';

W H E N"0110"=>Z R E G<='0';

W H E N"0111"=>Z R E G<='0';

W H E N"1000"=>Z R E G<='1';

W H E N"1001"=>Z R E G<='1';

W H E N"1010"=>Z R E G<='0';

W H E N"1011"=>Z R E G<='1';

W H E N"1100"=>Z R E G<='1';

W H E N"1101"=>Z R E G<='0';

W H E N"1110"=>Z R E G<='1';

W H E N"1111"=>Z R E G<='0';

W H E N O T H E R S=>Z R E G<='0';

E N D C A S E;

E N D P R O C E S S;

Z O U T<=Z R E G;

E N D o n e;

2)对其进行波形仿真,如下图:

3)将其转换成可调用元件如图:

2、信号检测器

1)建立工作库文件夹,输入设计项目VHDL代码,如下:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY JCQ IS

PORT(DIN, CLK, CLR : IN STD_LOGIC;

ss : OUT std_logic_vector(0 downto 0));

END JCQ;

ARCHITECTURE behav OF JCQ IS

type states is (S0,S1,S2,S3,S4,S5);

SIGNAL Q : states ;

SIGNAL D : STD_LOGIC_VECTOR(4 DOWNTO 0);

BEGIN

D <= "11010" ;

PROCESS( CLK, CLR )

BEGIN

IF CLR = '1' THEN Q <= S0 ;

ELSIF CLK'EVENT AND CLK='1' THEN

CASE Q IS

WHEN S0=> IF DIN = D(4) THEN Q <= S1 ; ELSE Q <= S0 ; END IF ; WHEN S1=> IF DIN = D(3) THEN Q <= S2 ; ELSE Q <= S0 ; END IF ; WHEN S2=> IF DIN = D(2) THEN Q <= S3 ; ELSE Q <= S2 ; END IF ; WHEN S3=> IF DIN = D(1) THEN Q <= S4 ; ELSE Q <= S0 ; END IF ; WHEN S4=> IF DIN = D(0) THEN Q <= S5 ; ELSE Q <= S2 ; END IF ;

WHEN OTHERS => Q <= S0 ;

END CASE ;

END IF ;

END PROCESS ;

PROCESS( Q )

BEGIN

IF Q = S5 THEN ss <="1";

ELSE ss <= "0";

END IF ;

END PROCESS ;

END behav ;

状态机如图:

3)将其转换成可调用元件如图:

3.序列信号检测器顶层文件

1)调用序列信号发生器和序列信号检测器元件,建立工作库文件夹,输入设计项目原理图如下图:

2)对总体进行波形仿真,如下图:

4.管脚邦定

六、实验现象及验证

当PIN53灭,PIN54亮时:

七、实验心得

1.首先用VHDL语言设计序列信号发生器和序列信号检测器模块。

2.了使设计简化,顶层文件采用原理图法,直接将两个模块连接起来。

3.测器时要先画出其状态转移图,否则很容易出错。

4.通过本次实验,加深了我序列信号检测器状态转移的理解。

使用D触发器设计一个11001序列检测器介绍

讨论使用D触发器设计一个11001序列检测器,讨论序列可交迭(Overlap)检测和不可交迭检测在设计上的区别,讨论分别采用Mealy机设计和采用Moore机设计的区别,讨论未用状态的处理问题。 【要求】给出电路原理图或HDL代码,要求进行仿真,并给出仿真结果。 1.原件介绍 D触发器(74LS74)、“与”门(74LS08)、“或”门(74LS32)、“非”门(74LS04),集成电路引脚

2.设计思路 根据要求,设计的序列检测器有一个外部输入x和一个外部输出Z。输入和输出的逻辑关系为:当外部输入x第一个为"1",外部输出Z为"0";当外部输入x 第二个为"1",外部输出Z为"0";当外部输入第三个x为"0",外部输出Z为"0",当外部输入第四个x为“0”,外部输出Z为0,当外部输入第五个x为“1”,外部输出Z为“1”。假定有一个外部输入x序列以及外部输出Z为: 输入X 0 1 1 1 0 0 1 0 1 输出Y 0 0 0 0 0 0 1 0 0 要判别序列检测器是否连续接收了"11001",电路必须用不同的状态记载外部输入x的值。假设电路的初始状态为A,x 输入第一个"1",检测器状态由A装换到B,用状态B记载检测器接受了"11001"序列的第一个"1",这时外部输出Z=0;x输入第二个"1",检测器状态由B装换到C,用状态C 记载检测器接了“11001”序列的第二个"1",外部输出Z=0;x输入第三个"0",检测器状态由C装换到D,外部输出Z=0;x输入第四个为“0”,检测器状态由D装换到E,外部输出Z=0;x输入第五个为“1”,检测器状态由E装换到F,外部输出Z=1。然后再根据外部输入及其他情况时的状态转移,写出相应的输出。以上分析了序列检测器工作,由此可画出原始状态图。根据原始状态图可列出原始状态表。 状态转换表 A B D C E F 1\0 1\0 0\0 0\0 1\1 0\0 0\0 1\0 1\0 0\0 0\0

实验五 用状态机实现序列检测器的设计

实验五用状态机实现序列检测器的设计 一、实验目的 1.熟悉QuartusⅡ软件应用环境,了解实验流程。 2.编写简单的Verilog代码,并在QuartusⅡ中进行调试和验证,并在EDA6000中下载代 码和验证。 3.掌握用状态机(State Machine)实现序列检测器的设计。 二、实验原理 假设检测器预先已经设定一个8位序列d,那么当由din端口串行输入的一个8位序列,与d完全相同时,检测器输出代码1010,即在试验箱上的LED上显示一个“A”;否则,检测器输出1110,即在试验箱上的LED上显示一个“E”。同时,当清零信号clr有效时,输出为1110。由清零信号clr和输入信号din共同控制状态机的状态变化。 三、实验内容 1、检测一组二进制序列信号,当连续的脉冲信号和预先设定的序列d相同时,显示字符“A”,否则显示“E”。 2、使用工具为译码器建立一个元件符号 3、设计仿真文件,进行验证。 4、编程下载并在实验箱上进行验证。 四、实验步骤 1.新建Verilog工程项目,编写代码并保存至与模块名对应的项目文件夹。 2.编译程序,编译无误后,在【tools】>【netlist viewers】里面选择RTL Viewer,观察电 路结构;在【tools】>【netlist viewers】里面选择State Machine Viewer,查看状态机转换图。 3.新建波形文件进行仿真。保存时要和源程序存放在同一目录下。设置好输入波形参数后, 开始仿真。在仿真后输入输出波形中观察逻辑关系是否正确。 4.将实验箱和PC合理连接起来。打开EDA6000软件,设置好芯片类型为ACEX1K (EP1K30TC144-3),载入模式12。 5.根据EDA6000界面内管脚对应芯片的实际管脚在QUARTUSⅡ里面设定管脚号并检查 无误。 6.将程序下载至FPGA内,并在EDA6000软件界面内进行验证测试。 程序代码 module SCHK(clk,din,clr,d,err); input clk,din,clr; input [7:0]d; output [3:0]err; parameter s0=0,s1=1,s2=2,s3=3,s4=4,s5=5,s6=6,s7=7,s8=8; reg [8:0]cs,ns; reg [3:0]err; always @(posedge clk or posedge clr) begin if(clr) cs<=s0; else cs<=ns; case (cs) s0:if(din==d[0] ) ns<=s1; else ns<=s0;

EDA课程设计——函数信号发生器

EDA课程设计——函数信号发生器 实验报告 学院(系) 专业、班级 学生姓名 学号 小组其他队员: 指导教师

(1)实验要求 (2)总体设计思路 (3)程序仿真 (4)实验结果 (5)心得体会 一.实验要求 (1)利用VHDL语言设计一个多功能信号发生器,可以产生正弦波,三角波,锯齿波和方波的数字信号。

(2)焊接一个D/A转换器,对输出的数字信号转换成模拟信号并在示波器上产生波形。 (3)在电路板上可以对波形进行选择输出。 (4)在电路板上可以对波形的频率与幅度进行调节。 二.总体设计思路 信号发生器主要由分频,波形数据的产生,四选一多路选择,调幅和D/A转换五个部分组成。 总体框架图如下: (1)分频 分频器是数字电路中最常用的电路之一,在FPGA的设计中也是使用效率非常高的基本设计。实现的分频电路一般有两种方法:一是使用FPGA芯片内部提供的锁相环电路,如ALTERA提供的PLL(Phase Locked Loop),Xilinx提供的DLL(Delay Locked Loop);二是使用硬件描述语言,如

VHDL、Verilog HDL等。本次我们使用VHDL进行分频器设计,将奇数分频,和偶数分频结合起来,可以实现50%占空比任意正整数的分频。 分频器原理图: 在我们本次试验中的实现即为当按下按键时,频率自动减半。如当输入为100MHZ,输出为50MHZ。 (2)信号的产生。 根据查找资料,我们最终确定了在QUARTUS中波形数据产生的方法,即利用地址信号发生器和LPM_ROM模块。ROM 的地址信号发生器,有七位计数器担任。LPM_ROM底层是FPGA 中的M4K等模块。然后在VHDL顶层程序设计中将两部分调用从而实现信号的发生。ROM中存放不同的初始化MIF文件(存放不同波形的数据)从而产生不同的波形。 信号产生模块:

设计一个1010的序列检测器

二、设计一个1010的序列检测器,检测到1010时输出为“1”否则为“0”,用D触发器实现。 第一步:根据要求进行逻辑抽象,得出电路的原始状态转换图和状态转换表。 取输入数据变量为X,检测的输出变量为Z, 该同步时序逻辑电路的功能是检测输入序列是否为1010,一旦输入序列出现一个1就记下来,因为这个1可能是1010序列的第一个1,;接着看输入是否为0,因为10是序列1010的前两位;其次再看输入是否为1,因为101是1010序列的前三位;最后再输入一个0,输出则为1,因为出现了一个1010序列,泽电路必须记住1,10,101,1010四种输入情况,每一种输入情况应与电路的一个状态相对应。 根据题意,设电路随机的输入和输出序列为: X:0 1 0 1 0 0 0 1 0 1 0 1 0…… Z: 0 0 0 0 1 0 0 0 0 0 1 0 0…… 该电路仅有一个输入端,每个现态有两个可能转移方向,设电路初态为S0,当X=0时,电路仍处在状态S0,当输入一个1以后的状态为S1,输入10以后的状态为S2,输入101以后的状态为S3,输入1010以后的状态为S4。以S n表示电路的现态,S n+1表示电路的次态。 由此得出原始状态转换图和原始状态转换表:

第二步:状态化简: 依据状态等效条件判断得出S0和S4在相同的输入条件下,它们转换到相同的次态去,且有相同的输出,故S0和S4等效,经分析比较,找出最大等效类:{S1},{S2},{S3},{S0,S4}。 由此得出化简的状态转换图和最简状态表: 第三步:状态编码: 最贱状态表共有四种状态,可用两位二进制代码来表示,设状态变量为Q1,Q2,依据状态编码原则,确定S0=00,S1=01,S2=11,S3=10四种状态,其编码后的状态转换图和状态转换表:

1011序列检测器

综合设计性实验报告 题目: 学生姓名: 学号: 班级: 指导教师: 学期:2010——2011第2学期

目录 一基本知识点 (1) 二实验器件 (1) 三设计思路 (1) 四设计过程 (2) (一)三位二进制减法计数器(无效状态000,001) (二)5 五引脚功能 (9) 六逻辑电路图: (11) 七实验结果波形图 (12) 八设计心得体会 (12)

一基本知识点 1、掌握时序电路的设计方法和步骤 2、掌握触发器的设计与应用 3、掌握移位寄存器的原理与应用 4 熟悉集成电路的引脚排列; 5 掌握芯片的逻辑功能及使用方法; 6 了解序列产生及检测器的组成及工作原理 7 会在EWB软件上进行仿真; 二实验器件 1、移位寄存器74LS194 1片 2、负边沿JK触发器74LS112 1片 3四输入与非门74LS20 1片 4、六输入非门74LS05 1片 5 电源一个 6 地线一个 7 与门,或门,非门若干个 8 时钟脉冲一个 三设计思路 1作原始状态表。根据给定的电路设计条件构成原始状态表和状

态转化图 2状态表的简化。原始状态表通常不是最小化状态表,它往往包括多余的状态,因此必须首先对它进行简化。 3状态分配。即对简化后的状态给以编码。这就要根据状态数确定触发器的数量并对每个状态指定一个二进制数构成的编码。 4根据给定的电路设计条件选择触发器根据 5 作激励函数和输出函数。根据选用的触发器激励表和电路的状态表,综合出电路中各触发器的激励函数和电路的输出函数。 ⑸6画逻辑图,并检查自启动功能 四设计过程 (一)101101001信号发生器的设计 设计一个信号序列发生器,在产生的信号序列中,含有“1011”信号码,要求用一片移位寄存器,生成信号序列“10110100”,其中含有1011码,其设计按以下步骤进行:、、 1本实验所用仪器为移位寄存器74LS194,确定移存器的位数n。因M=9,故n≥4,用74LS194 的四位。 2确定移存器的九个独立状态。将序列码101101001按照每四位一组,划分为九个状态,其迁移关系如下所示: 3作出状态转换表及状态转换图如下:

quartus设计状态机实现序列检测器

用状态机实现序列检测器的设计 一、原理 序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果与检测器预先设置的码相同,则输出为1,否则输出为0。 二、内容与步骤: 1、状态转换图 2、设计一个序列检测器,对1110010进行检测,编写实验程序。 3、对程序进行仿真测试并给出仿真波形。 4、仿真通过后进行引脚锁定,再进行一次全编译,并下载到实验箱上进行验证。 三、状态机源程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY STATEMACHINE IS PORT(DIN,CLK,RST:IN STD_LOGIC; SOUT:OUT STD_LOGIC); END STATEMACHINE; ARCHITECTURE BEHA V OF STATEMACHINE IS TYPE STATES IS (S0,S1,S2,S3,S4,S5,S6,S7); SIGNAL ST,NST:STATES:=S0; BEGIN COM:PROCESS(ST,DIN) BEGIN CASE ST IS WHEN S0=>IF DIN='1' THEN NST<=S1;ELSE NST<=S0;END IF; WHEN S1=>IF DIN='1' THEN NST<=S2;ELSE NST<=S0;END IF; WHEN S2=>IF DIN='1' THEN NST<=S3;ELSE NST<=S0;END IF; WHEN S3=>IF DIN='1' THEN NST<=S3;ELSE NST<=S4;END IF; WHEN S4=>IF DIN='1' THEN NST<=S1;ELSE NST<=S5;END IF; WHEN S5=>IF DIN='1' THEN NST<=S6;ELSE NST<=S0;END IF; WHEN S6=>IF DIN='1' THEN NST<=S2;ELSE NST<=S7;END IF; WHEN S7=>IF DIN='1' THEN NST<=S1;ELSE NST<=S0;END IF; WHEN OTHERS=>NST<=S0; END CASE;

序列检测器的一种简化实现算法

第8卷第6期石家庄学院学报Vol.8,No.62006年11月JournalofShijiazhuangUniversityNov.2006序列检测器的一种简化实现算法 李俊红,解建军 (河北师范大学数学与信息科学学院,石家庄050016) 摘要:分析了序列检测器的内部原理,给出它的一种新硬件实现.利用它无需对状态图进行状态化简,极大地简化了时序线路的设计.最后结合具体实例说明了该设计思想的详细步骤和具体实现方法. 关键词:子串;主串;序列检测器 中图分类号:TP16文献标识码:A文章编号:1673-1972(2006)06-0063-03 1序列检测器原理 序列检测是指将一个指定的序列从数字流中识别出来,或在主串中查询相应子串,一般可以通过软件方法或时序电路即硬件方法实现.有关软件实现方法的研究可参见文献[1],本文主要针对时序电路进行讨论.用硬件方法实现序列检测器时,检测器中存储模式串,主串可以通过输入端流入检测器[2,3].在主串的输入过程中,检测器可以动态检测子串.检测器利用时序线路记忆已检测出的有效序列,并与自身所含的模式串进行比对,若检测成功,输出端自动输出成功标记[4].设计一个“11100”序列检测器,当识别到一组序列时,输入一个高电平.由于采用时序线路,主串的内容应每给一个上升沿或下降沿输入一位,具体应视所选触发器类型而定. 我们提出一种新硬件实现方法,在该方法中对每一个状态都根据实际意义给予特殊的含义,具体含义在后面的实例中再加以说明,由于不存在重复状态,故最终的状态图不用化简. 序列检测器的初态是指被检序列的第一位出现前的特定状态,此状态后如果输入的代码对检测有效(即被测序列的第一位),则相应次态为新的状态(第2个状态,它记住了被测序列的第一位),否则相应次态仍为初态.第2个状态是指被检序列的第一位出现后的特定状态,此状态后如果输入的代码对检测有效,(即被测序列的第2位)则相应次态为新的状态(第2个状态,它记住了被测序列的前2位),否则判断最近输入的代码是否是被检序列的第一位,是则相应次态仍为第2个状态,否则相应次态为初态.以次类推,第i个状态记住了被检序列的前i-1位,相应次态确定方法如下: 假设序列长度为n,当i<n时,如果第i个状态后输入的一位代码是被检序列的第i位,则次态为新的状态(记住了被检序列的前i位),否则次态按如下规则选择:从初态开始输入的i位代码中如果其中的后i-j位为被检序列的前i-j位,则次态为第i-j+1个状态(j=1,2,...,i-1,找到次态即停止),否则次态为初态.此时所有的外输出均为‘0’. 当i=n时,第n个状态已经记住了被检序列的前n-1位,此状态后输入的一位代码如果是被检序列的第n位,则外输出为‘1’,否则外输出为‘0’,其次态按如下规则选择:从初态开始输入的n位代码中如果其中的后n-j位为被检序列的前n-j位,则次态为第i-j+1个状态(j=1,2,...,n-1,找到次态即停止),当j=n时,次态为初态. 按上述方法构造的原始状态转移图中恰好含n个状态,且每个状态都有确定的含义,避免了其设计过程中,构造原始状态转移图繁杂,化简原始状态转移图麻烦的弊端,设计时既逻辑清晰,又不用化简,从而极大地简化了该类线路的设计. 收稿日期:2005-12-09 基金项目:河北省石家庄市科学研究与发展计划项目(05213570);河北师范大学青年基金资助(L2005Q02) 作者简介:李俊红(1971-),女,山西运城人,河北师范大学数学与信息科学学院讲师,硕士,研究方向:并行逻辑模拟,计算机系统结构.

实验三_用状态机实现序列检测器的设计Verilog

实验三用状态机实现序列检测器的设计 一、实验目的: 用状态机实现序列检测器的设计,并对其进行仿真和硬件测试。 二、原理说明: 序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出a,否则输出b。由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。在检测过程中,任何一位不相等都将回到初始状态重新开始检测。例3-1描述的电路完成对序列数"11100101"的。当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“a”,否则仍然输出“b”。 【例3-1】 //顶层文件: module XULIEQI(clk,reset,din18,LED7S); input clk; input reset; input [17:0] din18; output [6:0] LED7S; wire [3:0] AB; wire [17:0] din18; xulie u1 (clk, din18, reset, din); schk u2 (din,clk,reset,AB); decl7s u3 (AB,LED7S); endmodule //串行检测: module schk(DIN,CLK,CLR,AB); input DIN,CLK,CLR; output[3:0] AB; reg [3:0] AB; reg [7:0] Q;

parameter idle = 8'b00000000, a = 8'b00000001, b = 8'b00000010, c = 8'b00000100, d = 8'b00001000, e = 8'b00010000, f = 8'b00100000, g = 8'b01000000, h = 8'b10000000; parameter data=8'b11100101; always @(posedge CLK or negedge CLR) if(!CLR) begin Q <= idle; end else begin case(Q) idle: begin if(DIN==data[7]) Q<=a; else Q<=idle; end a: begin if(DIN== data[6]) Q<=b; else Q<=idle; end b: begin if(DIN== data[5]) Q<=c; else Q<=idle; end c: begin if(DIN== data[4]) Q<=d; else Q<=c; end d: begin

EDA课程设计-正弦信号发生器的设计

《EDA技术》设计报告 设计题目正弦信号发生器的设计 院系:信息工程学院 专业:通信工程____ 学号: 姓名:__________

一.设计任务及要求 1.设计任务: 利用实验箱上的D/A 转换器和示波器设计正弦波发生器,可以在示波器上观察到正弦波 2.设计要求: (1) 用VHDL 编写正弦波扫描驱动电路 (2)设计可以产生正弦波信号的电路 (3)连接实验箱上的D/A 转换器和示波器,观察正弦波波形 二.设计方案 (1)设计能存储数据的ROM 模块,将正弦波的正弦信号数据存储在在ROM 中,通过地址发生器读取,将正弦波信号输入八位D/A 转化器,在示波器上观察波形 (2)用VHDL 编写正弦波信号数据,将正弦波信号输入八位D/A 转化器,在示波器上观察波形 三.设计框图 图 1 设计框图 信号发生器主要由以下几个部分构成:计数器用于对数据进行采样,ROM 用于存储待采样的波形幅度数值,TLV5620用于将采集的到正弦波数字量变为模拟量,最后通过示波器进行测量获得的波形。其中,ROM 设置为7根地址线,8个数据位,8位并行输出。TLV5260为串行输入的D/A 转换芯片,因此要把ROM 中并行输出的数据进行并转串。 四.实现步骤 1.定制ROM 计 数 器 7根地址线 8 位 R O M 并转串输出 CLK TLV5620D/A 转换 RST

ROM的数据位选择为8位,数据数选择128个。利用megawizard plug-in manager定制正弦信号数据ROM宏功能块,并将上面的波形数据加载于此ROM中。如图3所示。 图2 ROM存储的数据 图3 调入ROM初始化数据文件并选择在系统读写功能 2.设计顶层

110序列检测器的设计及仿真实现

题目:设计110序列检测器,当输入信号时输 出,否则 一、设计思路 我们采用Moore机完成这个功能。对于触发器的选择,为了简便我们选用D触发器以及基本的门电路完成基本设计。 二、时钟同步状态机 1根据题目要求我们得到下面的状态图 状态表示的意义Q X=0 X=1 输出Z 等待1的出现 A A B 0 出现1 B A C 0 出现11 C D C 0 出现110 D A B 1 * Q 2 转移输出表 01 Q Q输入X 输出Z X=0 X=1 00 00 01 0 01 00 11 0 11 10 11 0

10 00 01 1 01Q Q * * 3 状态图如图: 通过卡诺图化简可得 转移方程: 00111=Q Q Q Q X Q X * * += 输出方程:01 Z Q Q ? = 我们选择D 触发器作为记忆电路部分 由D 触发器的特征方程: Q D * = 得激励方程: 00111D =Q Q Q X D X += 三、V erilog 程序如下: module shiyan2 (clk,x,z); input clk,x; output z; wire[1:0] state;

wire[1:0] excite; nextlogic u1(x,state,excite); statememory u2(clk,excite,state); outputlogic u3(state,z); endmodule module statememory (clk,d,q); input clk; input[1:0] d; output[1:0] q; reg[1:0] q; always @ (posedge clk) begin q <= d; end endmodule module nextlogic (x,q,d); input x; input[1:0] q; output[1:0] d; assign d[0]=(q[1]&q[0])|(q[1]&x); assign d[1]=x; endmodule

eda课程设计 信号发生器

目录 1. 引言 (1) 2. VHDL语言及Quartus II软件介绍 (2) 2.1 VHDL语言 (2) 2.2 Quartus II软件 (2) 3.总体设计思想及流程 (3) 4. 具体程序实现模块 (4) 4.1倍频器模块 (4) 4.2主程序模块 (4) 4.3 波形显示模块 (5) 4.4频率显示模块 (5) 5. 软件仿真 (6) 6. 硬件显示 (7) 7. 总结与体会 (8) 参考文献 (9) 附录 (10) 附录1. 整体系统原理图 (10) 附录2. 主程序 (11)

1. 引言 信号发生器是一种能够产生多种波形,如三角波、方波、锯齿波、正弦波的仪器。信号发生器在电路实验和设备检测以及通信、雷达、导航、宇航等领域有广泛的应用。正因为其在生活中应用的重要性,人们它做了大量的研究,总结出了许多实现方式。可以基于FPGA 、VHDL、单片机、DOS技能、数字电路等多种方法实现。简易信号发生器是信号发生器的一种。可以实现信号发生器的一些基本功能。本次课程设计要求设计的是一种简易信号发生器。 在本设计中要求设计的简易信号发生器是采用VHDL来实现的简易多功能信号发生器。它能产生正弦波,三角波和方波。且对各种波形的要求如下:(1)设计任意信号发生器,使之能够生成正弦波、三角波和方波; (2)电路的外部频率为40MHz,要求信号发生器可产生0-1KHz、 1KHz~10KHz、10KHz~1MHz三档频率的信号; (3)要求具有波形选择和频率选择的功能; (4)在同一频率档内,可实现频率的加减; (5)要求显示波形的同时能够进行频率的调节; (6)要求能够显示波形:A——正弦波;B——三角波;C——方波; (7)要求能够显示频率值; (8)可用示波器进行波形的观测。

8位序列检测器的设计

八位序列检测器设计 摘要:序列检测器多用于通信系统中对禁用码的检测,或者是对所需信号的提取,即一旦检测到所需信号就输出高电平,这在数字通信领域有广泛的应运。本文介绍了一种采用单片PGA 芯片进行脉冲序列检测器的设计方法,主要阐述如何使用新兴的EDA 器件取代传统的电子设计方法,利用FPGA 的可编程性,简洁而又多变的设计方法,缩短了研发周期,同时使设计的电路体积更小功能更强大。本次课程设计设计出能够检测序列“”的序列检测器,并以此来描述序列检测器的设计过程和基于FPGA 的软件仿真。最后通过QuartusII 的波形输出对设计方案进行检测,在硬件调试经检测输出正确设计符合要求。 关键词: VHDL 序列检测QuartusⅡFPGA Abstract:Sequence detector system used for communication on the detection code disabled, or is the extraction of the desired signal, that is, once detected, the required high output signal, which in the broad field of digital communications to be transported. This paper presents a single FPGA chip with the detector pulse sequence design method, mainly on how to us e new device to replace the traditional EDA electronic design, the use of FPGA's programmability, concise and changing the design method shortens the development cycle, while allowing smaller circuit design and more powerful. The curriculum is designed to detect sequence "" sequence detectors, and detector in order to describe the sequence of the design process and FPGA- based software simulation. Finally, the output of the waveform QuartusII design testing, debugging the hardware design has been tested and meet the requirements of the correct output. Keywords:VHDL Sequence detection QuartusⅡFPGA

实验5 状态机序列检测器设计

实验五序列检测器设计 一、实验目的 1 掌握时序电路状态机设计一般方法; 2 学会用状态机方法实现序列检测器的设计。 二、实验原理: 序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出1,否则输出0。由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。在检测过程中,任何一位不相等都将回到初始状态重新开始检测。序列检测可由状态机完成,也可进行串行滑窗检测器。 线性反馈移位寄存器,用来产生伪随机序列,用做测试数据输入。 三、实验内容 1、完成“1101”检测器的设计,输入信号a和时钟clk,输出为out。 2、设计一个五位线性反馈移位寄存器,其输出数据以串行移位方式进入序列 检测器,其有置数端set,输入时钟clk,左移输出out; 3、连接五位线性反馈移位寄存器和序列检测器构成完整实验系统。 四、设计步骤 1、建立新工程, 2、完成五位线性反馈移位寄存器设计,序列检测器设计,顶层文件设计,并把各 个模块连接起来。 3、对顶层文件进行编译。 4、对顶层文件时序仿真。 五、实验报告:根据以上的实验内容写出实验报告,包括设计原理、程序设计、仿真分析等详细实验过程。 六、扩展部分: 1、采用文本输入方式构成顶层文件,重新构造本系统。

2、设计采用移动滑窗法进行序列检测。 参考程序:状态机序列检测器(1101)module fsm (clock, reset, datain, out); input clock,reset, datain; output out; reg out; reg [1:0] state; parameter Idle = 2'b00, Start = 2'b01, Step=2'b10, Stop = 2'b11; always @(posedge clock)// if (!reset) // begin state <= Idle; out<=0; end else case (state) Idle: if (datain==1) begin state <= Start; out<=0; end else begin state<=Idle; out<=0; end Start: if (datain==1) begin state <= Step; out<=0; end else state <=Idle; Step: if (datain==0) begin state <= Stop; out<=0; end else state<=Step; Stop: if (datain==1) begin state <= Idle; out<=1; end else begin state <=Idle; out<=0; end endcase endmodule

状态机设计仿真

状态机设计仿真 一、实验例题 设计一个序列检测器电路,检测出串行输入数据data中的二进制序列110,当检测到该序列时,电路输出1 out=;没有检测到该序列时,电路输出0,电路的状态图如1所示: 图1 电路状态转换图 二、实验原理分析 由电路的状态图分析,可列出对应的状态转换表,如图2所示: 图2 状态转换表 +相同,将图1,图2简化可得: 从状态转化表分析可得S3与S0对应的S n1

改进的状态转换表 三、实验任务:依据图1状态图2表,S 存在时,用VerilogHDL设计的参考程序如 3 下: module pulse_check(data,clk,rst,out); input data,clk,rst; output out; reg out; reg[1:0] CST,NST; parameter[1:0] s0=0,s1=1,s2=2,s3=3; always@(posedge clk or negedge rst) if (!rst) CST<=s0;//复位有效,进入下一个状态 else CST<=NST; always@(CST or data) begin case(CST) s0: if(data==1'b1) NST<=s1; else NST<=s0; s1: if(data==1'b1) NST<=s2; else NST<=s0; s2: if(data==1'b0) NST<=s3; else NST<=s2; s3: if(data==1'b0) NST<=s0; else NST<=s1;

default: NST<=s0; endcase end always@(CST or data) case(CST) s0:out=1'b0; s1:out=1'b0; s2: if(data==1'b0) out=1'b1; else out=1'b0; s3:out=1'b0; endcase endmodule rst复位信号(低电平有效),clk状态时钟。四:仿真图形

课程设计------序列检测器

电子课程设计 ------序列检测器 学院: 专业班级: 姓名: 学号: 指导老师: 2012年12月

目录 一、设计任务与要求 (1) 二、总体框图 (1) 三、选择器件 (1) 四、功能模块 (1) 1、脉冲发生器 (1) 2、序列检测器 (2) 3、分频器 (3) 五、总体设计电路图 (5) 1、总体电路原理图 (5) 2、Q UARATU SII的仿真结果图与分析 (5) 3、管脚分配 (6) 4、E DA实验箱验证 (6)

序列检测器 一、任务与要求 设计一个序列检测器,在上升沿的作用下,输入一组二进制码,与预先设置的吗“11100101”一致时,输出A,不同时则输出B,(在检测过程中,任何一位不相等都将回到初始状态重新开始检测。) 二、总体框图 脉冲发生器:为检测器提供脉冲。 检测器:具有存储功能。 数码显示器:显示输出A或B 方案:设计手动的脉冲发生器为检测器提供脉冲,使其正常工作,然后设计检测器存储的数字为“11100101”再用译码器使其显示在数码管上,这就要求检测器必须记住前一次的正确吗及正确序列,直到在连续的检测中所收到的每一位吗与预置数的对应码相同,否则重新开始检测。 三、选择器件 芯片:EDA实验箱中EP1C12核心板;七段数码管等。 外围电路:将IO_CLK用导线连接到IO3上,将IO9,IO10用导线连接到两个LED灯上,接上电源下载完成即可验证。 四、功能模块 1.脉冲发生器 VHDL程序: LIBRARY ieee; use ieee.std_logic_1164.all; entity pulse is port(pul,M: in std_logic; nq,q: out std_logic --VGA:out std_logic_vector(3 downto 0) ); end pulse; architecture a of pulse is signal temp: std_logic; begin --VGA <= "0001";' q<=temp; nq<=not temp; process(m)

EDA--调频信号发生器

湖南人文科技学院 课程设计报告 课程名称:VHDL语言与EDA课程设计 设计题目:调频信号发生器 系别:信息学院 专业:电子信息工程 班级:一班 学生姓名: 姚靖瑜何渡余建佳 学号: 13409112 13409115 13409120 起止日期: 2016年6月16日 指导教师:姚毅 教研室主任:

指导教师评语: 指导教师签名:年月日 成绩评定 项目权重 成绩 1、设计过程中出勤、学习态度等方面 2、课程设计质量与答辩 3、设计报告书写及图纸规范程度 总成绩 教研室审核意见: 教研室主任签字:年月日教学系审核意见: 主任签字:年月日

摘要 本文介绍一种利用EDA技术和VHDL语言,在QuartusⅡ环境下,设计的一种调频信号发生器。EDA 技术是以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关开发软件,自动完成用软件的方式设计的电子系统到硬件系统实现,最终形成集成电子系统或专用集成芯片的一门新技术。介绍一种基于DDS 原理,并采用FPGA 芯片和VHDL 开发语言设计的任意函数调频的任意波形信号发生器,给出了设计方案和在GW48 CK型EDA 集成电路开发系统上实现的实验结果。 关键词:调频;信号发生器;DDS;FPGA;VHDL;QuartusⅡ

目录 设计要求 (1) 1、方案论证与对比 (1) 1.1方案对比 (1) 1.2方案选择 (2) 2、工作原理及过程 (2) 2.1DDS的基本原理 (2) 2.2基本流程图 (3) 3、模块设计 (3) 3.1MATLAB设计 (3) 3.1.1 顶层原理图设计 (3) 3.1.2 Smulink模型仿真 (4) 3.1.3 Signalcompiler的使用 (4) 3.2Q UARTUS II设计 (6) 3.2.1 顶层原理图模块 (6) 3.2.2 高速A/D转换器TLC5510 (6) 3.2.3 调试与操作说明 (7) 3.2.4 顶层文件设计 (8) 4、问题分析 (9) 5、心得体会 (9) 6、元件清单 (10) 7、致谢 (10) 参考文献 .................................................................................................. 错误!未定义书签。附录一AD5510控制程序 .. (11) 附录二顶层文件程序 (12)

6实验六 状态机序列检测

实验六用状态机实现序列检测器的设计 1、实验目的 用状态机实现序列检测器的设计,并对其进行仿真和硬件测试。 2、实验原理 序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出1,否则输出0。由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。在检测过程中,任何一位不相等都将回到初始状态重新开始检测。例实验六描述的电路完成对序列数"11100101"的。当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“A”,否则仍然输出“B”。 【例实验六】 LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL; ENTITY SCHK IS PORT(DIN,CLK,CLR : IN STD_LOGIC ; --串行输入数据位/工作时钟/复位信号 AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); --检测结果输出 END SCHK; ARCHITECTURE behav OF SCHK IS SIGNAL Q : INTEGER RANGE 0 TO 8 ; SIGNAL D : STD_LOGIC_VECTOR(7 DOWNTO 0); --8位待检测预置数 BEGIN D <="11100101"; --8位待检测预置数 PROCESS( CLK, CLR ) BEGIN IF CLR = '1' THEN Q <= 0 ; ELSIF CLK'EVENT AND CLK='1' THEN --时钟到来时,判断并处理当前输入的位 CASE Q IS WHEN 0=> IF DIN = D(7) THEN Q <= 1 ; ELSE Q <= 0 ; END IF ; WHEN 1=> IF DIN = D(6) THEN Q <= 2 ; ELSE Q <= 0 ; END IF ; WHEN 2=> IF DIN = D(5) THEN Q <= 3 ; ELSE Q <= 0 ; END IF ; WHEN 3=> IF DIN = D(4) THEN Q <= 4 ; ELSE Q <= 0 ; END IF ; WHEN 4=> IF DIN = D(3) THEN Q <= 5 ; ELSE Q <= 0 ; END IF ; WHEN 5=> IF DIN = D(2) THEN Q <= 6 ; ELSE Q <= 0 ; END IF ; WHEN 6=> IF DIN = D(1) THEN Q <= 7 ; ELSE Q <= 0 ; END IF ; WHEN 7=> IF DIN = D(0) THEN Q <= 8 ; ELSE Q <= 0 ; END IF ; WHEN OTHERS => Q <= 0 ; END CASE ; END IF ; END PROCESS ; PROCESS( Q ) --检测结果判断输出 BEGIN

设计一个的序列检测器完整版

设计一个的序列检测器 HEN system office room 【HEN16H-HENS2AHENS8Q8-HENH1688】

二、设计一个1010的序列检测器,检测到1010时输出为“1”否则为“0”,用D触发器实现。 第一步:根据要求进行逻辑抽象,得出电路的原始状态转换图和状态转换表。 取输入数据变量为X,检测的输出变量为Z, 该同步时序逻辑电路的功能是检测输入序列是否为1010,一旦输入序列出现一个1就记下来,因为这个1可能是1010序列的第一个1,;接着看输入是否为0,因为10是序列1010的前两位;其次再看输入是否为1,因为101是1010序列的前三位;最后再输入一个0,输出则为1,因为出现了一个1010序列,泽电路必须记住1,10,101,1010四种输入情况,每一种输入情况应与电路的一个状态相对应。 根据题意,设电路随机的输入和输出序列为: X: 0 1 0 1 0 0 0 1 0 1 0 1 0…… Z: 0 0 0 0 1 0 0 0 0 0 1 0 0…… 该电路仅有一个输入端,每个现态有两个可能转移方向,设电路初态为 S 0,当X=0时,电路仍处在状态S ,当输入一个1以后的状态为S 1 ,输入10以后的状 态为S 2,输入101以后的状态为S 3 ,输入1010以后的状态为S 4 。以S n表示电路的现 态,S n+1表示电路的次态。 由此得出原始状态转换图和原始状态转换表:

依据状态等效条件判断得出S 0和S 4 在相同的输入条件下,它们转换到相同的 次态去,且有相同的输出,故S 0和S 4 等效,经分析比较,找出最大等效类:{S 1 }, {S 2},{S 3 },{S ,S 4 }。 由此得出化简的状态转换图和最简状态表: 最贱状态表共有四种状态,可用两位二进制代码来表示,设状态变量为Q 1 , Q 2,依据状态编码原则,确定S =00,S 1 =01,S 2 =11,S 3 =10四种状态,其编码后的状态 转换图和状态转换表: