28335_EPWM产生PWM

28335 ePWM模块中产生PWM的必要配置

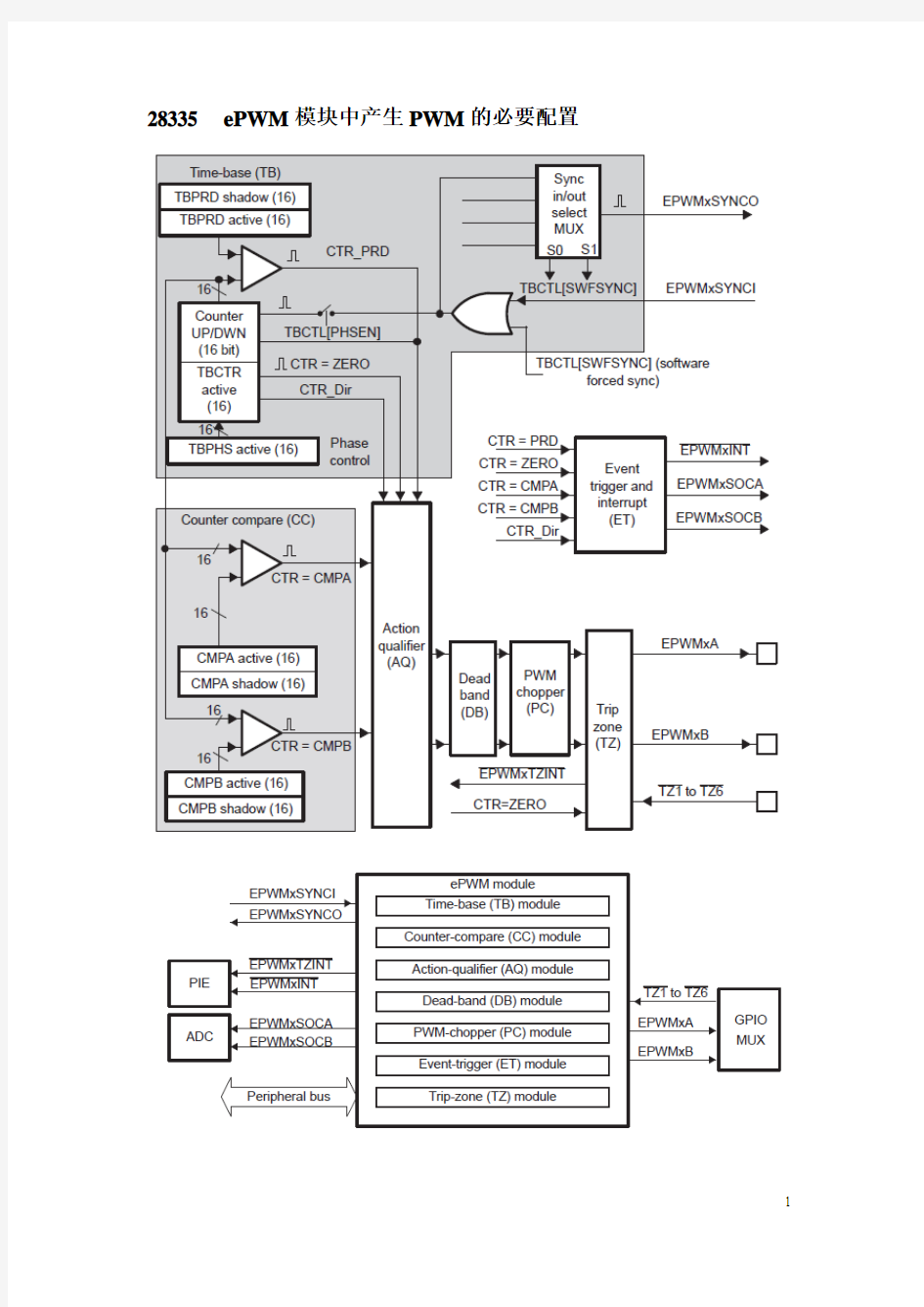

一个ePWM module包括Time-base (TB) module,Counter-compare (CC) module,Action-qualifier (AQ) module,Dead-band (DB) module,PWM-chopper (PC) module,Event-trigger (ET) module,Trip-zone (TZ) module等七个模块。正常的发出PWM波要配置TB(定时器模块)、CC(比较计数器模块)、AQ(比较方式预设模块)、DB(死区模块)、ET(事件触发模块)等五个模块。

Time-base (TB) module

Time-base (TB) module为定时器模块,有

TBCTL(控制寄存器)配置定时器的时钟、计数模式、同步模式

TBSTS(状态寄存器)

TBPHSHR(高速PWM用)

TBPHS(相位寄存器)计数器的起始计数位置,例如寄存器为0x0100则计数器从0x0100开始计数

TBCTR(计数器)

TBPRD(周期寄存器)设置计数器的计数周期。只有TBPRD(周期寄存器)有影子寄存器。

本程序的设置为count-up-and-down mode计数模式,相位为零,ePWM2 、ePWM3、ePWM4、ePWM5、ePWM6,通过ePWM1的计数器到零时进行同步,计数周期为0.5ms。

Counter-compare (CC) module

Counter-compare (CC) module为比较器模块有

CMPCTL (比较控制寄存器)设置CMPA、CMPB的重载模式CMPAHR(高速PWM用),

CMPA(比较值寄存器A)设置EPWMxA的比较值,有影子寄存器。CMPB(比较值寄存器B)设置EPWMxB的比较值,有影子寄存器。本程序只应用了CMPA,设置计数器到零时重载CMPA。

Action-qualifier (AQ) module

Action-qualifier (AQ) module比较方式预设模块

AQCTLA (输出A比较方式控制寄存器)设置EPWMA的比较方式有CBD、CBU、CAD、CAU、PRD、ZRO,无影子寄存器,立即装载

AQCTLB (输出B比较方式控制寄存器)设置EPWMB的比较方式有CBD、CBU、CAD、CAU、PRD、ZRO,无影子寄存器,立即装载

AQSFRC (软件强制控制寄存器)设置AQCSFRC重载方式(RLDCSF),通过(OTSFB、ACTSFB)设置EPWMB、(OTSFA、ACTSFA)设置EPWMA启动一次强制置位无效、置零、置高、反向,当OTSFB、OTSFA被写1时,动作一次,写0无效,无影子寄存器

AQCSFRC (软件连续强制控制寄存器)可以强制EPWMA、EPWMB的输出为low 或high或AQCSFRC不起作用,有影子寄存器,当寄存期被加载后的第二个时钟开始作用,如TBCLK=0时加载,TBCLK=1时开始起作用

说明:

CBD为TBCTR(计数器)与CMPB在down计数时相等使输出为low或high或反向或不动作

CBU为TBCTR(计数器)与CMPB在up计数时相等使输出为low或high或反向或

不动作

CAD为TBCTR(计数器)与CMPA在down计数时相等使输出为low或high或反向或不动作

CAU为TBCTR(计数器)与CMPA在up计数时相等使输出为low或high或反向或不动作

PRD为TBCTR(计数器)与TBPRD(周期寄存器)相等时使输出为low或high或反向或不动作

ZRO为TBCTR(计数器)计到零时使输出为low或high或反向或不动作

注意:以上均是相等时起作用,其它时间不管,只有AQCSFRC(软件连续强制控制寄存器)持续起作用

如同时出现比较则优先级如图

例:CMPA=100,CMPB=100,up计数,EPWMA初始为低,CAU设置高,CBU设置低,当TBCTR计到100时,CAU、CBU同时作用,根据优先级,EPWMA输出低。

当CMPA=100,CMPB=110,其它不变,当TBCTR计到100时,EPWMA输出高,计到110时EPWMA输出低。

本程序只应用了EPWMA输出通过Dead-band (DB) module产生互补的PWM波形。

Action-qualifier (AQ) module比较方式预设模块配置如下:AQCTLA (输出A比较方式控制寄存器)的CAU置高,CAD置低,其它无效。在初始化中配置。

AQCSFRC (软件连续强制控制寄存器)通过AQSFRC(软件强制控制寄存器)的RLDCSF配置为TBCTR(计数器)计到零时装载,根据需要每次中断配置CSFA置高、置低或软件连续强制无效。其优先级最高,强制时CAU置高,CAD置低不起作用,无效时CAU置高,CAD置低起作用。

AQSFRC(软件强制控制寄存器)的ACTSFA配置为置低,当本周期软件连续强制无效时,向OTSFA写1,保证有效高周期的起始是低状态,防止上一周期结束时为高。

Dead-band (DB) module

Dead-band (DB) module 死区模块

DBCTL(死区控制寄存器)设置S5,S4,S3,S2,S1,S0开关选择的

DBRED(死区上升沿延时)上升沿延时时间

DBFED(死区下降沿延时)下降沿延时时间

本程序的设置为S5=0,S4=0,S3=1,S2=0,S1=1,S0=1;延时时间为5us。EPWMxA= EPWMxA in,EPWMxB为EPWMxA in的反向。

Event-trigger (ET) module

Event-trigger (ET) module中断事件模块

ETSEL(中断选择寄存器)使能及事件源选择(SOCA触发ADC转换,SOCB触发ADC转换,中断)

ETPS(中断预设寄存器)xxxCNT记录时间发生次数,当与xxxPRD相等时,发出中断信号,xxxCNT停止计数,当标志为清除时xxxCNT置零重新计数

ETFLG(中断标志寄存器)状态标志位,中断时为1

ETCLR(中断标志清除寄存器)写1清除相应标志位

ETFRC(强制中断寄存器)写1强制相应中断发生

本程序选择SOCA触发ADC转换,TBCTR=0位中断事件源,xxxPRD为1。

TMS320F280X系列DSP的EPWM讨论

我们大家知道.2812,2407等系列的EVA.EVB模

块等能产生丰富的PWM波型.但是要作为一个

系列的话.我还是推荐大检查使用280X系列.

一个主要原因是它们的引脚可以完全共用.这

就为我们研发从低到高的产品提供了一个通用

平台.2809好象百元左右吧.2808是80RMB.小

袖珍的热门DSP28016可能也就超不过30RMB.

那可是32位60M主频的带全基本上的接口.我

觉的280X系列从价位和封装上为我们提供了

灵活的选择余地.

但是现在280X的资料好象很少.看了一下他们

的EPWM模块有些没弄明白.比如为使所有EPWM

在一个同步时基上工作.他们的EPWMXSYNCI和

EPWMXSYNCO是不是要级联起来.但是好象没看

见EPWM1-EPWM6有外接这么多同步时钟接口

啊.是不是在软件里Writing a 1 to the

TBCTL[SWFSYNC] control bit invokes a

software forced synchronization. This

pulse is ORed with the synchronization

input signal, and therefore has the same

effect as a pulse on

EPWMxSYNCI.就不用管外设的同步始终接口

EPWMSYNCI和EPWMSYNCO啊.其实多半做PWM控

制的都希望能用硬件产生有固定时基的时钟信

号啊.再就是有没有类似2407和2812等的影子

寄存器(同步缓存寄存器).在定时周期中断中

不用担心会在不恰当的时候改变了比较和周期

寄存器的内容.他们只会在当前执行了前一控

制内容后再执行改变的寄存器内容.避免了时

空错乱啊.280X有没有类似的设置啊?

TOP

61IC代码工厂*永久免费*所有代码都

通过官方审核,保证代码的完整性.

新手上路

?发短消息?加为好友

2#大中小发表于 2009-8-9

08:44 只看该作者

This feature enables the ePWM module to be automatically synchronized to the time

base of another

ePWM module. Lead or lag phase control can be added to the waveforms generated by

different ePWM

modules to synchronize them. In

up-down-count mode, the TBCTL[PSHDIR] bit

当前离线configures the direction of

the time-base counter immediately after a

synchronization event. The new direction

is independent of the

direction prior to the synchronization

event. The TBPHS bit is ignored in

count-up or count-down modes.

See Figure 2-7 through Figure 2-10 for

examples.

Clearing the TBCTL[PHSEN] bit configures

the ePWM to ignore the synchronization

input pulse. The

synchronization pulse can still be

allowed to flow-through to the EPWMxSYNCO

and be used to

synchronize other ePWM modules. In this

way, you can set up a master time-base (for

example, ePWM1)

and downstream modules (ePWM2 - ePWMx) may

elect to run in synchronization with the

master. See

the Application to Power Topologies

Chapter 3 for more details on

synchronization strategies.

以上是很关键的一段话.大概意思是如果你选

择EPWM1模块的时基,你就可以使能下游的其

余EPWMX模块和EPWM1有共同的时基.用这些

EPWM可以组成灵活的相位关系.但是万变不

离其踪.他们有一个共同的时基.所有的相位

和周期都是相对这个时基的增减关系啊.我们

也不用担心动态改变比较和周期寄存器的内

容会对占空比产生不确定的影响.TI的工程

师早为我们设计好了同步缓存寄存器的内容.

类似于2812和2407的影子寄存器.只有在下

一个比较周期里才可以改变占空比的.这个设计非常有用的.再就是刘和平老师翻译的影子寄存器我感觉有些怪异.还是叫同步缓存寄存

器好理解些啊.

TOP

新手上路

?发短消息

?加为好友

?当前离线

3#大中小发表于 2009-8-9 08:45 只看该作者

有啊,呵呵,感觉2812和28016不是一个应用场合的东西。2812主要是有地址和数据总线可以带一大堆东西,flash/ram,显示器,等等。只要加几个片选信号做一个地址扩展,跟访问内部地址差不多。28016就是做电机控制器用用了,顶多接片LCD,再I2C或spi加个eeprom,不会再有其他东西了。这种场合,不可能用2812这么贵的芯片了。不过感觉这种场合用28016还是有点没意思,100个脚,封装太大了。实际用的又不可能这么多。还有,其中AD有16个脚,一般项多用2,3个,电源加上地又有10多个脚,能做IO口的只有30多个。管脚利用率太低了。

要不是以前用的有点习惯了,宁可选freescale的dsp

TOP

新手上路

?发短消息

?加为好友

?当前离线

4#大中小发表于 2009-8-9 08:47 只看该作者

去ti里面找spru791D吧(如果没有记错的话),pwm同步是可以设置的,他们内部是级连的,只需要软件设置一下采用什么同步,比如zero,prd等..28016是60m的主频,带can通信,大量应用于低成本的数字电源,2801的16路ad 口,我觉得一点也不多,总而言之,资源的多少取决于你的期望的设计目标,需要达到什么性能.能用28016的绝对不用2801.

如何用ePWM模块实现0%~100%占空比控制

上网时间:2007年11月01日

所属类别: 电源管理I 电源管理I 技术方案I 技术方案I 技术方案

关键字:占空比ePWM PWM满量程在某些应用中让占空比控制达到满量程0%~100%是非常重要的。TMS320x280x系列处理器使用灵活、配置丰富,是在整个范围内实现满量程占空比控制的最佳选择。

增强型脉宽调制(ePWM)模块在保证系统开销最小的前提下可提供0%~100%占空比。这些模块有三种工作模式:加法计数模式、可逆计数模式和减法计数模式,本文重点讨论前两种工作模式。这里对TMS320x280xx/28xxx e PWM的基本使用不做详细介绍,并假设用户已熟悉TMS320x280xx/28xxx ePWM(SPRU791)的使用。

PWM模块配置

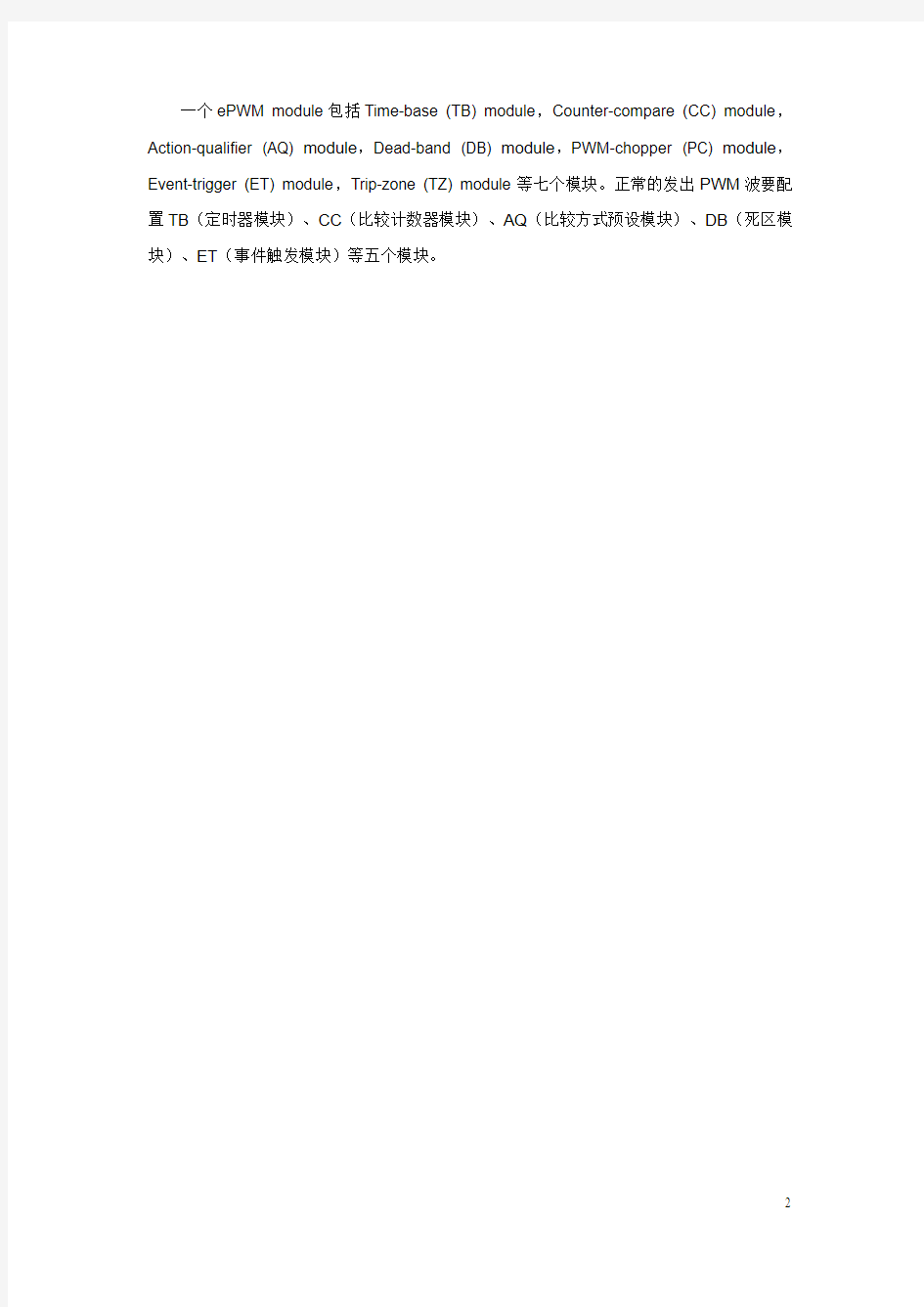

ePWM模块包括以下几个子模块:时基(TB)子模块、计数器-比较器(CC)子模块、动作限定(AQ)子模块、?死区(DB)发生器子模块、PWM斩波器(PC)子模块、故障断路器(Trip Zone)子模块、事件触发器(ET)子模块。图1为PWM模块结构框图。

图1:PWM模块结构框图。

配置ePWM模块时需要对上述子模块中的寄存器进行初始化。必须正确配置控制寄存器,以便ePWM模块能工作在上述三种模式的任意一种模式中。

在无需0%或100%的占空比的情况下,配置和使用ePWM模块比较简单,按照TMS320x 280xx/28xxx ePWM参考指南给出的程序就可实现ePWM模块的配置。但0%和/或100%占空比的应用则属于特殊情况,需要按照附加的程序配置ePWM模块。附加程序在本文的网络版本中给出。

占空比的满量程调节

通过执行附加的软件实现满量程的占空比调节,该软件可以跟踪当前占空比值和下一个占空比值,并充分利用动作限定子模块所具有的灵活的配置性能。该附加程序代码位于PWM中断服务例程(ISR)中,如果要改变下一个周期寄存器的数值,可以在当前ISR中进行设置。下文描述了在可逆计数模式及加法计数模式下,该软件的执行过程。

1. 可逆计数模式

当工作在可逆计数模式(PWM波形对称)时,若加法计数达到的值与CMPA值相匹配,置位ePWMxA输出;若减法计数达到的值与CMPA值相匹配,ePWMxA输出复位;如果CMP A值与计数器的值不匹配,则调用ISR并加载阴影寄存器。

在这种情况下,向CMPA寄存器加载0实现100%的ePWMxA占空比,向CMPA寄存器加载大于或等于周期的数值实现0%的ePWMxA占空比。代码的执行过程如下:

在当前周期的ISR中,计算下一个PWM周期的比较寄存器的值,这样通过当前ISR就可得知当前和下一个周期的占空比。获知下一个周期的占空比能更好的了解当前周期,详细描述如下:

a. 当CMPA值由非零变为零时:

(1) 改变动作确认控制寄存器的值,AQCTLA.bit.ZRO=AQ_SET。在下一个周期中立即使P WM引脚置位。

(2) 在下一个周期(实际上是第一个100%占空比)的ISR中,将动作确认寄存器的值变为初始值。

b. 当CMPA值由零变为非零时:

(1) 改变动作确认控制寄存器的值,AQCTLA.bit.ZRO=AQ_CLEAR,AQCTLA.bit.CAD=A Q_NO_ACTION。

(2) 改变LOADAMODE位的值,加载零或周期值。

需要注意的是,AQCTLA.bit.CAU=AQ_SET未发生变化,因此,对于最后一个'CMPA=0'周期之后的下一个周期,即使CMPA值等于1,当CMPA值与计数器值一致时,ePWM引脚也应置为高电平。

将动作确认寄存器和控制寄存器的值变回到SIR初始时的值,为下一个周期做准备。(实际上第一个非0%周期或者第一个非零CMPA周期都跟有一个零CMPA周期。)当CMPA值进入周期寄存器和返回时无需上述操作。EPwm1Regs.ETPS.bit.INTPRD应初始化为ET_1S T,即每一事件都产生中断。

2. 加法计数方式

当采用加法计数模式工作时,若计数器的值与ZRO值匹配,置位ePWMxA输出,若计数器的值与CMPA值匹配,则ePWMxA输出复位。CMPA值与计数器的值不匹配时调用IS R,并加载阴影寄存器。

在这种情况下,向CMPA寄存器加载大于周期的一个值即可实现100%的ePWMxA占空比;向CMPA寄存器加载0实现0%的ePWMxA占空比。代码的执行过程如下:

采用加法计数模式工作时,在当前周期的ISR中,计算下一个PWM周期的比较寄存器的值。因此,通过当前ISR就可得知当前和下一个周期的占空比。获知下一个周期的占空比能更好的了解当前周期,详细描述如下:

a. 当CMPA的值由非零变为零时:

(1) 改变动作确认控制寄存器的值,AQCTLA.bit.ZRO=AQ_CLEAR。在下一个周期中立即清除PWM引脚的状态。

(2) 在下一个周期(实际上是第一个100%占空比)的ISR中,将动作确认寄存器的值变为初始值。

b. 当CMPA值由零变为非零时:

(1) 改变动作确认控制寄存器的值AQCTLA.bit.ZRO=AQ_SET。

(2) 改变LOADAMODE位的值,加载零或周期值。

需要注意的是:AQCTLA.bit.CAU=AQ_CLEAR未发生变化。因此,在最后一个CMPA=0周期后的下一个周期,即使该周期的CMPA值等于1,在CMPA匹配时也应清除ePWM引脚的状态。

(3) 将动作确认寄存器和控制寄存器的值变回到ISR初始值,为下一个周期工作做准备。(实际上第一个非0%周期或者第一个非零CMPA周期都跟有一个零CMPA周期)。

当CMPA值进入周期寄存器和返回时无需上述操作。

EPwm1Regs.ETPS.bit.INTPRD应初始化为ET_1ST,即每一事件都产生中断。也应按此方法配置PWM时基子模块,这样可确保在可逆计数模式下,可在半个PWM周期内即可执行完ISR代码;而在加法计数模式下,可在一个PWM周期内执行完ISR代码。

软件流程

代码执行的软件流程图如图2所示。

图2:代码执行的软件流程图。

程序代码示例

下列ISR程序代码可用于实现加法计数模式下ePWM模块的0%-100%占空比调节。这些代码为ePWM1A和ePWM1B提供独立控制,并使ePWM1B对ePWM1A起到补充作用。