PCI总线的开发技术研究

基于PCI总线的开发技术研究

第1章 PCI总线简介

1.1 PCI总线的基本概念

PCI总线的英文全称为Peripheral Component Interconnect,即外设部件互连。PCI 总线的概念是由 Intel 公司联合Compaq、AST、Epson、HP、NEC 等多家公司提出的。发布的第一个技术规范 1.0 版本于 1992 年 6 月 22 日面世,2.0 版本于 1993 年 4 月发布,2.1 版本于 1995 年第一季度发布。制定PCI总线的目标是建立一个工业标准的、低成本的、允许灵活配置的、高性能局部总线结构。

PCI总线是局部总线,是来自处理器的延伸线路,与处理器同步操作。外部设备如果直接挂在局部总线上,就可与高速地CPU总线相匹配,从而打破了数据I/O地瓶颈,外设能以CPU的速度运行,使高性能CPU的功能得以充分发挥。由于局部总线有极高的数据传输率,因此在CPU与高速缓冲存储器(Cache)、CPU 与高速图形卡等需要高速传输信息的场合得到了广泛的应用。从1993年PCI局部总线标准推出到现在,PCI总线以其优异的性能逐步取代了ISA、EISA等总线,成为了当今总线发展的主流。

1.2 PCI总线的特点

PCI局部总线主要具有以下特点[:

1.高性能。采用 32 位或 64 位数据总线,以 33MHz 或 66MHz 的时钟频率操作,可支持多组外围部件及附加卡。在时钟频率为33MHz 的情况下,其数据传输速率高达132MB/s,远远高出标准ISA总线5MB/s的速率。

2.支持线性猝发传输。所谓猝发传输即若有一块地址连续的数据要传送时,只在开始时只有数据块第一个数据段的地址会出现,接下来的数据将不会跟有地址周期,外围设备一般会由内存某个地址顺序接受数据,这种线性顺序的寻址方式,意味着可以由某一个地址读写大量数据,然后每次只需要将地址自动加1,便可以接受数据流内下一个字节的数据如此就极大地提高了传送速度。线性突发传输能够更为有效地运用总线的带宽去传输数据,以减少无谓的地址操作。

3.极小的存取延误。支持PCI的设备存取延误小,能够大幅度减少外围设备取得总线控制所需的时间。

4.采用总线主控和同步操控。总线主控目的是让任何一个具有处理能力的外围设备暂时接管总线,以加速执行高吞吐量、高优先级的任务。PCI独特的同步操作功能可保证微处理器能够与这些总线主控同时操作,不必等待后者的完成。

5.不受处理器限制。PCI独立于处理器的结构,形成一种独特的中间缓冲器的设计方式,将中央处理器子系统与外围设备分开。有了缓冲器的设计方式,用户可以随意添外围设备,以扩展电脑系统而不必担心在不同时钟频率下会导致性能的下降。

6.兼容性强。由于PCI局部总线是要辅助现有的扩展总线的标准,因此它与ISA、EISA等总线完全兼容。

7.低成本、高效益。PCI的芯片将大量系统功能高度集成,节省了逻辑电路,占用较小的线路板空间,成本降低,PCI部件采用地址/数据复用,减少了PCI部件的引脚数。

第2章 PCI总线与DSP通讯电路设计

2.1 PCI-DSP通讯电路

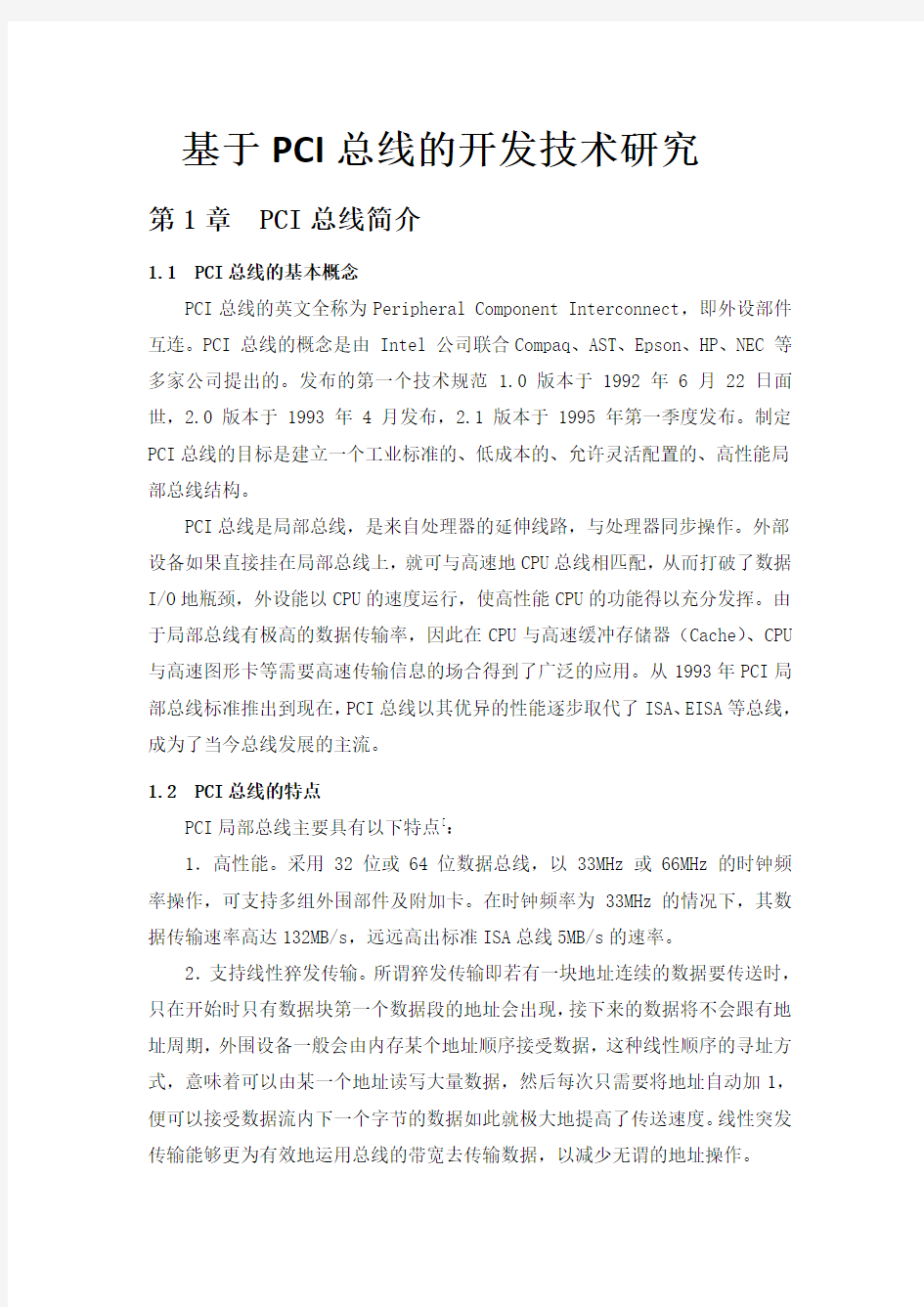

PC机通过PCI总线与DSP与的通讯电路如图2-1所示。

由于DSP与PC机之间需要高速地传送大量的数据,为了提高两者之间的通讯速度,在PCI 9052与DSP之间加入了双口RAM。双口 RAM作为一种特殊的RAM 芯片,在高速数据采集处理系统中得到广泛的应用。它具有两个独立的端口,各自均有一套独立的数据总线、地址总线和控制总线,允许两个端口独立地对存储器中的任何单元进行存取操作。当两个端口同时对存储器中的同一单元进行存取操作时,可由其内部仲裁逻辑决定优先权。

双口RAM芯片的型号为美国IDT公司生产的IDT7132 [35],它是2K×8bit高速静态双口RAM,存取速度35ns,在数字信号处理领域应用已经比较普遍。它的时序与DSP的时序相配合,特别适用于DSP与PC机之间的大量数据高速双向传送。该芯片均提供两个带有自身的控制、地址和I/O引脚的独立端口,它允许独

立地读写存储器中的任何单元。IDT7132带有片内硬件端口仲裁电路,可以允许双机同步地读或写存储器中的任何单元,同时保证数据的完整性。它的竞争原则是:左右两端口的地址信号同时到达,首先处理CE 片选信号先到的一端,慢的一方BUSY 线下拉,直到快的一方访问完毕;左右两端口的片选信号同时到达,首先处理访问地址信号先到的一端,慢的一方BUSY 线下拉,直到快的一方访问完毕。采用双口RAM 作为TMS320LF2407与PC 主机之间的通讯接口不但可以简化通讯接口电路的设计,而且提高了数据交换的速度,增强了控制卡的实时性。由于只用到了双口RAM 的16个地址,DSP 的地址线A[10: 4]与IS#信号进入CPLD 进行译码对双口RAM 片选。LRDYi 信号和两侧的BUSY#信号也进入双口CPLD 进行相应的逻辑判断。由于双口RAM 的数据信号电平为5V ,在与3.3V 的DSP 之间进行数据传输时需要74LVTH245进行电平转换。

2.2 PCI 总线接口电路实现方法

PCI 总线接口电路大体有两种实现方法:

1.用可编程逻辑器件CPLD 或FPGA 实现通用PCI 接口。这样做也有两种选AD[31: 0]

C/BE[3: 0]#

FRAME#

PAR

EESK ISAA[1: 0] CLK

IRDY#

TRDY#

STOP# DEVSEL#

PERR#

SERR#

RST#

INTA#

LOCK# PCI 9052 PCI 总线 IDT7132 DRAM TMS320LF2407 DSP IDSEL CPLD 芯片EPM7128 地址译码 R/W#L LA[10: 2] LAD[7: 0] CS1# IORD# IOWR# LRDYi OE#L CE#L I/O L [7: 0] A L [10: 2] A L [1: 0] CE#R OE#R R/W#R I/O R [7: 0] A R [10: 0] EEDO EECS EEDI 96LC46B E 2PROM

SK DO CS DI BUSY#L BUSY#R

A [10: 0] D [7: 0] 74LVTH 245 A [10:4] IS# RD# R/W# 图2-1 PCI-DSP 通讯电路图

择。一个是买IP宏,并根据应用的需要来裁剪IP宏并与相关应用电路烧入CPLD 或FPGA中。另一种是采用类似于QuickLogic公司的一次性可编程芯片来处理,每片可编程芯片内都内嵌PCI接口电路,也可根据应用的需要来裁剪烧写,但只能烧写一次。采用可编程逻辑器件的优点主要有:PCI接口可以根据插卡功能进行最优化的电路设计,而不必实现所有的PCI总线的功能,节约系统的逻辑资源;可以将PCI插卡上的其它用户逻辑与 PCI 接口逻辑集成在一块芯片上,实现紧凑的系统设计;当系统升级时,只需对可编程逻辑器件重新进行逻辑设计,而无须更改PCB板。但是,采用可编程逻辑器件由于要买IP宏,而一个IP宏少则几千美元多则更贵,并且一般的小规模的CPLD的免费开发软件不支持对IP宏的开发所以用户有可能还要花几万元买大规模的CPLD或FPGA设计软件,因此用户的开发前期投入很大;同时用户需具备一定可编程逻辑设计的功底以及扎实电路设计基础,要有一定深度的VHDL的开发能力,开发周期较长。

2.采用专用芯片实现PCI总线接口。专用芯片可以实现完整的PCI主控模块和目标模块的接口功能,将复杂 PCI 总线接口转换为相对简单的用户接口。厂商对 PCI 总线接口进行了严格的测试,用户只要设计转换后的总线接口即可。这样,用户可以集中精力于应用设计,而不是调试 PCI 总线接口,明显的缩短了开发周期。它的缺点是用户实际只用到了部分的 PCI 接口功能,这样造成一定的逻辑资源浪费,对于大批量生产的产品不易降低成本。

为了缩短开发周期,本运动控制器采用第二种实现方法,即选用专用PCI 总线接口芯片来设计PCI总线接口电路。

2.3 PCI总线接口芯片选择

目前市场上提供的专用芯片主要是AMCC、PLX和CYPRESS等公司的系

列产品。各个型号的PCI接口芯片的比较如表4-1所示。

表4-1各公司PCI接口芯片比较

生产公司主要特点驱动开发价格技术资料

AMCC 内置FIFO接口,适于

设计数据采集卡,使

用简单,性能好

有DOS下的驱动

程序范例

较

昂贵

较为全面,提供

评估板板图

CYPRESS 内置DRAM,可以替代

外部缓存,有效降低

性能成本

有VXD范例便宜

技术文档比较

全面

PLX 有较多型号可供选择提供SDK,降低工

作量

多种

选择

有价值的资料

在RDK中出售

从市场情况来看,PLX是PCI接口芯片的行业巨头,该公司提供多个系列的产品,例如主设备接口芯片9060、9080、9054等,从设备接口芯片9030、9050、9052等,分别支持“主控”和“从控”两种模式。所谓“主控”就是PCI接口芯片可以让用户电路控制PC机资源,即主动对目标设备发读写信号。“从控”就只能让PC机来控制用户电路工作,而用户电路只能被动接受,像ISA总线一样。支持该模式的芯片中,9030为嵌入式专门设计,支持CompactPCI;9050专门为ISA设备转PCI总线接口而设计;9052是9050的升级版本。这些芯片价格低廉,不支持DMA,适合于设计基于PCI总线的以中断、查询方式与主机交互的系统。

经过比较,PLX公司的9052技术成熟,价格适中,能够满足系统要求,所以决定采用该芯片作为PCI接口的运动控制卡的接口芯片。

2.4 PCI 9052的主要特点

PCI9052是PLX公司继PCI9050之后推出的低成本PCI总线目标接口芯片, 符合PCI 2.1规范,采用CMOS工艺,低功耗,PQFP 160 pins封装。其主要特点如下[33]:

1.包括一个64Byte的写FIFO存储器和一个32Byte的读FIFO存储器,可实现高性能的突发式数据传输;

2.ISA 模式下支持 PCI 总线到 ISA 总线的单周期存储器(8 位或 16位)读写和 I/O 访问,实现 ISA 总线到 PCI 总线的平滑过渡;

3.支持两个来自局部总线的中断,可生成一个PCI中断,利用软件写内部寄存器位也可以达到同样的目的;

4.PCI9052的局部总线与PCI总线的时钟相互独立运行,局部总线的时钟频率范围为0~40MHz,TTL电平,PCI的时钟频率范围为0~33MHz,两种总线的异步运行方便了高低速设备的兼容;

5.可编程的局部总线配置,支持复用或非复用模式的8、16或32位的局部

总线;

6.串行E2PROM提供PCI总线和局部总线的部分重要配置信息;

7.4个局部设备片选信号,各设备的基址和地址范围及其映射可由串行E2PROM或主机编程实现;

8.5个局部地址空间,基址和地址范围及其映射可由串行E2PROM或主机编程实现;

9.可对局部总线的预取计数器编程为0(非预取)、4、8、16或连续(预取计数器关闭)预取模式;

10.PCI锁定机制,PCI主控设备可以通过锁定信号独占对PCI9052的访问。

2.5 PCI 9052的工作原理

PCI9052 包含了四个接口部分:PCI 总线接口、串行 EEPROM 接口、局部总线接口和 ISA 总线接口。其中局部总线接口与 ISA 总线接口的引脚是复用的。PCI9052 就相当于一个桥,连接 PCI 控制的局部总线芯片到PCI 总线上,将PCI 指令(如读写某个寄存、内存、I/O)翻译到局部总线。PCI9052 内部提供了两种配置寄存器:PCI 配置寄存器(PCI Configuration Registers)和局部配置寄存器(Local Configuration Registers),为总线接口的实现提供了较大的灵活性。PCI 配置寄存器提供了 6 个基地址寄存器(BASE0-BASE5),这些基地址都是在系统中的物理地址,其中BASE1和BASE2都是用来访问局部配置寄存器的基地址,BASE1 是映射到内存的基地址,BASE2是映射到 I/O 的基地址,所以可以通过内存和 I/O 来访问局部配置寄存器。BASE2-BASE5 四个空间提供了访问局部端所接的 4 个芯片,它们将局部端的芯片通过局部端地址(在局部配置寄存器中设置)翻译成 PCI 总线的地址,也就是将本地的芯片影射到系统的内存或 I/O 口。这样使用程序操作这一段内存(或I/O)实际上就是对本地的芯片操作了。这些寄存器的内容必须在芯片复位时通过串行 E2PROM 进行加载,正确配置 E2PROM 的内容是使用 PCI9052 的关键。

上电时,PCI9052的内部寄存器由PCI总线的RST#信号复位,在局部总线上输出LRESET#信号。复位后,PCI9052尝试去读串行EEPROM来判断其是否存在。如果E2PROM的第一个字不是0FFFFH,则PCI9052假定设备非空并且继续读。PCI 总线上的主控设备也可以应用软件通过置CNTRL[30]=1,使PCI9052的寄存器复

位,但是主设备只能访问配置寄存器,而不能访问局部总线。当CNTRL[30]=0时,清除PCI9052的复位状态。

提供 PCI 总线到 ISA 总线之间的简单转换模式也是 PCI9052 的特色之一,只要设置相应的使能位并进行必要的配置即可,虽然只能用于单次数据传输,却为基于 ISA 总线的产品向 PCI 总线转移提供了极大的方便。ISA 模式的配置既可以通过编程器对串行 E2PROM 预先编程来实现,也可以通过 PCI 总线在线配置。

第3章 PCI总线接口卡的开发

PCI总线技术已经应用于形形色色的微机接口中。同在声卡、网卡甚至有些显示都是基于PCI总线技术的,一些高速数据传输系统中也需要用到PCI总线技术。PCI总线技术的出现是为了解决由于微机总线的低速度和微处理器的高速度而造成的数据传输瓶劲问题,PCI局部总线是在ISA总线和CPU总线之间增加的一级总线。由于独立于CPU的结构,该总线增加了一种独特的中间缓冲器的设计,从而与CPU及时钟频率无关,用户可以将一些高速外设直接挂到CPU总线上,使之与其相匹配。PCI局部总线使得PC系列微机结构也随之升级为现在的基于PC I总线的三级总线结构。PC机的三级总线结构如图1所示。

3.1 PCI总线接口卡的开发

PCI局部总线最显著的特征是速度快。ISA总线的传输速率为5MB/s,EISA 总线的传输速率为33MB/s,PCI1.0标准定义的总线传输速率为132MB/s,PCI2. 0标准定义的总线传输速率为264MB/s,PCI2.1和PCI2.2标准定义的总线传输速率为512MB/s。而新一代PCI-X技术则在原有PCI总线技术的基础上增加了许多新的技术特征,利用PCI-X技术可以为千兆以太网卡、基于Ultra SCSI320

的磁盘阵列控制器等高数据吞吐量的设备提供足够的宽带。1999年PCISIG(PC I特别兴趣小组发布的PCI-X1.0标准最高可提供1GB/s的传输速率,而2003年推出的PCI-X2.0标准则最高可提供4.3GB/s的传输速率。

目前,PCI总线接口电路的选择主要有两种方案。一种是选用可编辑逻辑器件(PLD)。使用PLD,用户可以灵活地开发出适合自己需要的具有特定功能的芯片,但PCI总线协议比较复杂,设计PCI控制接口难度较大,对于一般的工程项目来说,成本较大。现在有许多生产可编程逻辑器件的厂商都提供经过严格测试的PCI接口功能模块,用户只需进行组合即可。另一种是选用PCI专用芯片组(又称桥接电路),通过专用芯片来实现完整的PCI主控模块和目标模块的功能,将复杂的PCI总线接口转换为相对简单的用户接口,用户只需设计转换后的总线接口。本设计中选用PCI总线专用接口芯片来开发接口卡。

3.1.1 接口芯片介绍

PCI总线接口电路又分为主控设备和目标设备。主控设备可以控制总线,驱动地址、数据和控制信号;目标设备不能启动总线操作,只能依赖于主控设备从其中读取数据或向其传送数据。主控设备芯片价格比较高,目标设备芯片价格则比较便宜,而且目标设备芯片比较简单、易于操作。

目前两大PCI专用接口芯片生产商是AMCC公司和PLX公司。AMCC公司的PCI接口芯片有S5920、S5933、S5935等。S5920是目标设备芯片;S5933既可以设置为主控设备芯片,又可以设置为目标设备芯片;S5935是S5933的改进版,同样既可以设置为主控设备芯片,也可以设置为目标设备芯片。PLX公司在PCI接口芯片的设置生产中首屈一指,其目标设备芯片产品主要有PCI9030、PCI9052和

PCI9050,PCI9050和PCI9052可以运用于ISA卡转接PCI的设计中,PCI9030

是专门为嵌入式系统设计的;主控设备芯片产品主要有PCI9054、PCI9080和PC I9060,PCI9060是最早的32位主控设备芯片,PCI9080是PCI9060的后继产品,而PCI9054则是一种性价比很高的芯片,其性能比PCI9080、PCI9052更优越。由于主控设备芯片比较复杂,而且价格昂贵,所以对处理速度和传输速度要求不是特别高的场合应尽量选用目标设备芯片。本设计中选用PLX公司的PCI9052

目标设备芯片来设计PCI接口电路。

3.1.2 硬件设计

由于PCI9052属于目标设备芯片,只能依赖于主控设备从其中读取数据或向其传送数据,所以需要一个微处理器对通过PCI9052从PCI总线发送到局部总线的命令作出处理响应,或者把用户想要传送的数据以中断的方式通知PCI总线来读取。本设计中微处理器选用TI公司的C2000系列的16位DSP芯片TMS320LF2 407。

TMS320LF2407是TI公司推出的定点DSP处理器,是一款性价比较高的芯片。它采用高性能静态CMOS技术,供电电压为3.3V,指令周期可达25ns,片内有高达32K字的FLASH程序存储器、1.5K字的数据/程序 RAM、544字双口RAM(DAR AM)和2K字的单口RAM(SARAM),可以分别扩展64K字外部程序存储器、64K 字外部数据存储器和64K字I/O寻址空间;片内还集成了包括CAN控制器在内的多个外围模块及存储器,可以运用于电机及逆变电路的控制中;10位16通道的A/D转换器最小转换时间为500ns;内部自带看门狗定时器模块(WDT)和16位的串行外设接口模块(SPI)。另外,该芯片有高达40个可单独编程或复用的通用输入/输出引脚、一个串行通信接口(SCI)、一个并口和5个外部中断。目前投入市场试用的C2000系列的32位DSP芯片TMS320LF2812采用的是150MHz的时钟速率,其指令周期只为6.7ns,存储器可以扩展到1M,速度更快,功能更强大。

PCI接口卡硬件总体设计。DB代表数据总线,AB代表地址总线,CB代表控制总线。

PCI9052的PCI总线直接与金手指连接,局部总线与DSP之间的数据传输在双端口RAM中实现。双端口RAM采用两片CYPRESS公司的双端口RAM芯片CY7C1

31,组成16位存储转接电路PCI9052和CY7C131供电电压均为5V,而TMS320L F2407供电电压为3.3V,所以接口电平不匹配,需要加总线电平转换电路,这里选用16位总线传送接收器74FCT64245来实现。PCI9052的控制信号和TMS320L F2407的控制信号之间的逻辑转换用一片ALTERA公司的PFGA芯片EPM7032LC44来实现。

TMS320LF2407的外围电路可以根据需要扩展。由于TMS320LF2407内部自带32K字的FLASH程序存储器,程序调试完毕后可以烧写进去,但程序调试过程中需要频繁修改程序,所以可展一片存储器,调试程序时当作程序存储器用,程序调试完毕后再作为数据存储器用,这样既方便又实用。TMS320LF2407有一个串行通信接口和一个16位并行通信接口,串口可以做成RS485、RS232、RS422、S DI总线接口等,并行通信接口可以做成16位并行输入输出接口。

3.1.3 电路板制作

(1)在连线上只要将对应的引脚连在总线上就可以了。由于信号用的是反射波信号,所以驱动的信号只用了要求电压的一半,另一半靠反射来提升,所以对信号线的长度有要求:CLK信号线的长度为2500mil±100mil。如果长度不够可以画蛇行线,另外,CLK信号线要用地线屏蔽。

(2)PCI总线规范要求布四层线,也可以只布两层线。布两层线时,走线难度增大,要做好电源退耦。每个Vcc引脚必须有退耦电容,且容量的平均值至少为0. 01μF,从引脚根部到电容焊盘的走线长度不大于250mil,线宽至少为20mil,多个引脚可以并用一个电容,并且参与共用的引脚数不受限制,但必须满足以上条件。

(3)PCI总线信号PRSNT1#的PRSNT2#中必须有一个接地。如果都不接地,系统找不到开发板。它们接地有两个用途,其一,用来表明槽位上实际存在一块板;其二,提供该板对电源要求的有关信息。表1给出了PRSNT#引脚的设备情况。

表1 PRSNT#引脚的设置情况

PESNT1# PRSNT2# 扩展板配置

开路开路不存在扩展板

地开路有扩展板,最大功耗为25W

开路地有扩展板,最大功耗为15W

地地有扩展板,最大功耗为7.5W

(4)对于不实现JTAG边界扫描的板子,必须把引脚TDI和TDO连接起来,以使扫描链不至于断开。

(5)PCI连接器上的3.3V引脚(即使实际使用中未提供电流)在母板上必须连到一起,最好连到一个3.3V的电源平面上。而且,对3.3V引脚应提供一个交流回路,这时对地去耦应符合高频信号技术的要求。为此,应在3.3V平面上均匀排列12个高速电容,容易为0.01μF。

(6)为了稳定性,局部总线除了少数有特殊要求外,所有的信号线都应加上拉电阻(5kΩ~10 kΩ)或下拉电阻(一般选150kΩ)。

(7)为防止干扰,局部总线时钟也应对地屏蔽。

(8)串行EEPROM提供PCI总线和局部总线的部分重要配置信息,EEPROM一定要选支持串行传输方式的,如NM93CS46或者与之兼容的存储器。NM93C46不支持串行读写,所以不能选取。NM93CS46的CS、SK、SDI、SDO和PE端都要接10k Ω的上拉电阻,而PRE端要接150kΩ的下拉电阻。EEPROM的配置至关重要,EE PROM配置不正确可能导致操作系统无法运行。系统启动时自动检测EEPROM的开始48拉是否全为“1”,若全为“1”,则载入PCI9052的默认配置;否则则装载EEPROM中的内容,为板卡分配资源。串行EEPROM可以通过PCI总线直接写入,也可以用编程器直接烧写。

3.1.4 程序调试

FPGA程序的开发

可编程器件的设计软件种类很多,各大器件厂家及一些软件公司都开发了一些设计软件。软件的设计根据逻辑功能的描述方法可分为语言描述设计和原理图描述设计两个类。常见的如DATA I/O公司的ABEL语言、四通公司ASIC事业部开发的针对GAL器件的FM(Fast MAP)软件等属于语言描述类设计软件;而DA TA I/O公司的Synario软件、Orcad公司的PLD等软件属于电路图描述或电路图描述与语言描述相结合设计的软件。

本设计中FPGA的编程只涉及到信号逻辑转换,所以只需选用语言描述类设计软件,这里选用DATA I/O公司的ABEL语言描述设计软件。程序调试结束后用编程器写入FPGA芯片即可。

3.1.5 DSP程序开发

TI公司提供了DSP专用仿真器和仿真开发系统,C2000系列的开发系统最新版本为CCS2.2。对于不同的仿真器,只要安装驱动程序即可使用该开发系统进行仿真。仿真器选用最新款的带USB接口的ICETEK51000USBV2.0仿真器。由于该仿真器使用USB接口,所以不需外接供电电源,实用又方便。

由于硬件设计时扩展了可转换的存储器,进行仿真时把存储器接成程序存储器,程序可以直接转载到扩展的存储器中进行调试,免去了往FLASH中烧写的麻烦,程序调试完毕后再固化到FLASH中。

3.2 PCI总线接口卡的软件驱动开发

PCI卡的硬件调试需要结合软件程序的调试来完成。PCI卡的驱动程序开发有多种途径,驱动开发工具也有多种选择。

3.2.1 驱动开发工具的选取

(1)DDK(Driver Device Kit)

许多VMM服务都使用寄存器的调用方式,使用起来不是很方便,没有4深厚的汇编语言及硬件基础很难在短时间内开发出设备驱动程序。Micorosoft公司提供了设备驱动程序工具箱(DDK),它是基于汇编语言的编程方式的,DDK的优点是可以开发核心态的真正意义上的驱动程序,开发出来的驱动程序效率是最高的。

(2)DS(Driver Studio)

DS是一个驱动程序集成开发包,其中包括了DriverAgent、VtoolsD、DriverWo rks、SoftICE Driver Edition、BoundsChecker Driver Edition、DriverWork benc、FieldAgent for Drivers等。几中常见的DS驱动开发工具介绍如下:·Drivergent为Win32应用程序提供了访问硬件的接口。

·VtoolsD支持Windows95和Windows98的驱动程序开发(VxD)。VtoolsD包括代码生成器、实时接口库和可以作为开发一类驱动程序的例子程序。

·DriverWorks包括为Windows NT和Win32 Driver Model(WDM)开发驱动程序的完整的开发框架,同时也支持Windows98和Windows2000下驱动程序的开发。D riverWorks包含一个复杂的代码生成工具(Driver Wizard),其中含有支持C ++下编程的类库和例子程序。

(3) WinDriver

WinDriver是KRF-Tech公司的一套PCI驱动程序开发包。它改变了传统驱动程序开发的方法和思路,极大地简化了驱动程序的编制;同时又没有牺牲驱动程序的性能,是一套高效、快捷的PCI驱动程序开发软件包,特别适合专业硬件人员使用。

利用WinDriver开发驱动程序不需要熟悉操作系统的内核,整个驱动程序中的所有函数都是工作在用户态下的,通过与WinDriver的.Vxd或者.Sys文件交互可达到驱动硬件的目的。由于是一个用户态程序,效率的高低也就成了人们选择W inDriver时关心的问题。大量实践数据表明,WinDriver并没有通过牺牲系统性能来换取驱动程序的快速开发。本设计中选用WinDriver来开发驱动程序。3.2.2 WinDriver开发驱动程序

在WinDriver的体系结构中,WinDriver Kernet处于中心位置,它提供的用户态库函数(API)实际就是对WinDriver Kernel中实现的功能进行调用。几乎所有用户同硬件的交互都是通过WinDriverKernel来实现的,这样就极大地解放了开发人员。用户的主要任务就是利用WinDriver提供的用户动态函数库(API函数库)在用户态实现自己的驱动程序代码,完成硬件驱动的功能。

基于WinDriver的设备驱动程序主要分为驱动程序和应用程序两部分。利用Dri verWizard生成.inf驱动程序,安装该驱动程序后,系统就根据EEPROM中的配置信息给板卡分配资源,接下来就可以进行应用程序的开发了。利用DriverWiz ard生成应用程序框架后,用户把生成的框架整理到自己的程序中,再添加实际应用中需要的功能就完成了软件的开发。

PCI总线是计算机总线的枢纽,其速度是一般总线望尘莫及的,其应用也十分广泛。利用本文介绍的方法开发出的板卡可以运用于各种高速数据传输场合中,发雷达系统仿真控制、工业总线控制、高速数据采集、图像采集等。本设计在对芯片的选型时本着经济实用的原则,开发出的板卡性价比较高。