FPGA开发板说明

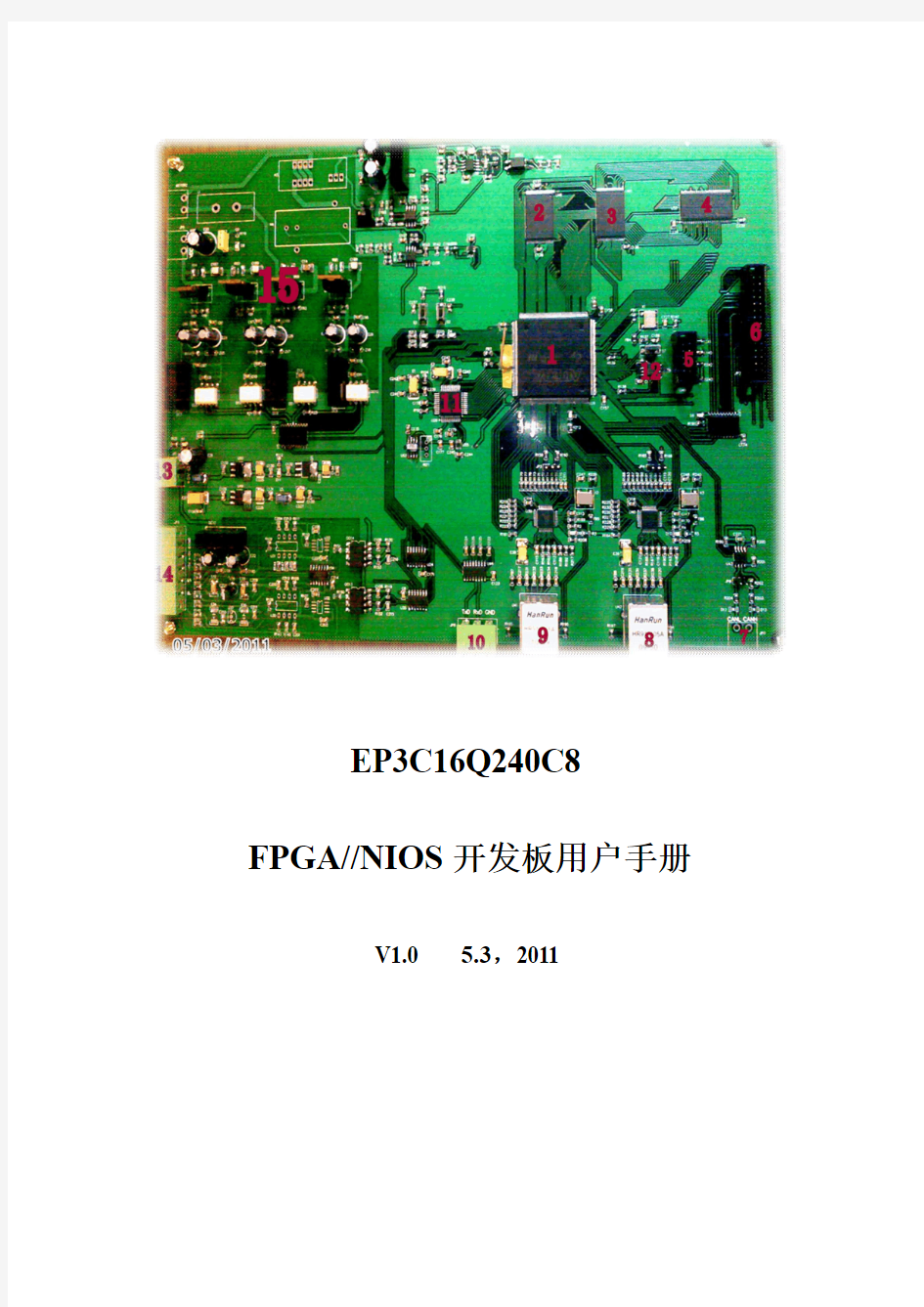

EP3C16Q240C8 FPGA//NIOS开发板用户手册

V1.0 5.3,2011

目录

一、简介 (3)

二、开发板照片及资源描述 (3)

2.1 EP3C16Q240C8芯片资源描述 (3)

2.2 照片及引脚分配 (4)

2.3 功能描述 (6)

2.4 硬件电路详解 (7)

1.EP3C16 FPGA各个bank (7)

2.存储器FLASH电路 (8)

3.存储器SDRAM电路 (9)

4.存储地SRAM电路 (10)

5.配置部分电路 (11)

6.时钟及复位部分电路 (11)

7.电源部分电路 (12)

8.AD采样部分电路 (13)

9.双极性电机驱动电路 (13)

10.以太网部分驱动电路 (14)

11.Can通讯部分驱动电路 (15)

12.串口通讯部分驱动电路 (15)

13.编码计数部分电路 (15)

14.其它部分电路 (16)

三、使用注意事项 (16)

3.1 电源 (16)

3.2 JTAG拔插方法 (16)

3.3 软件说明 (17)

3.4 引脚配置 (17)

四、开发板关键模块测试注意事项 (17)

4.1 JTAG测试 (17)

4.2 EPCS测试 (17)

4.3 存储器SDRAM测试 (17)

4.4 存储器SRAM测试 (18)

4.5 存储器FLASH测试 (18)

一、简介

EP3C16Q240C8-FPGA开发板采用Altera公司推出的CYCLONE3系列芯片EP3C16Q240C8芯片作为核心处理器进行设计,本开发板是目前市场上高端的FPGA/NIOS系列开发板,资源较多,用户可用IO数量也比较多,是3代的最新产品,比较适合做研究用。本开发板可以完成的功能主要包括双极性直流电机的控制、以太网通信、正交编码采集、CAN通信、超大数据存储(其中SDRAM-256Mbit、SRAM-16Mbit、FLASH-64Mbit、EPCS-16Mbit)、串口通信等等。

二、开发板照片及资源描述

2.1 EP3C16Q240C8芯片资源描述

Altera的最新芯片都采用逻辑单元作为衡量内部的资源,不同于以往的,多少万门的概念,请大家注意。换算的比例:

EP2C5等效23万门;EP2C8等效42万门;EP3C16等效90万门;可以访问Altera公司官方网址获得最新消,

https://www.360docs.net/doc/7c1865719.html,/products/devices/dev-index.jsp

表1三款芯片资源对比

2.2 照片及引脚分配

由于开发板主芯片EP3C16所有bank的引脚配置电压都为3.3V,所以VCCIO

都为3.3V,考虑到后面会详细介绍其他IO引脚的接法,这里仅仅列出VCC、GND引脚列表。

GND GND VCC_3.3 VCC_2.5 VCC_1.2

8 125 7 58 10

11 130 15 178 40

16 138 35 3 53

36 141 47 123 61

42 156 66 74

48 165 77 115

54 172 96 129

62 191 104 140

67 193 124 163

75 205 136 190

79 208 154 204

97 215 170 228

105 227 192 60

116 229 206 180

59 179 213 1

2 122 225 121

表2开发板引脚对应表

2.3 功能描述

图3EP3C16开发板正面功能图

1. 板载EP3C16Q240C8-FPGA核心芯片;

2. 板载SRAM-61WV102416BLL,容量16Mbit,其中地址线和数据线共用地址、

数据总线,可以用来运行程序和快速处理数据;

3. 板载FLASH-S29GLO64N90TF106或AM29LV641DH90REF,两款FLASH

兼容,容量64Mbit,其中地址线和数据线共用地址、数据总线,可以用来运行程序和掉电存储数据;

4. 板载SDRAM-H57V2562GTR,容量256Mbit,其中地址线和数据线共用地址、

数据总线,可以用来运行程序和处理大容量数据;

5. JTAG下载接口,对应下载的文件是SOF文件,速度很快,JTAG将程序直

接下载到FPGA中,但是掉电程序丢失,平时学习推荐使用JTAG方式,最后固化程序的时候通过JTAG将JIC文件烧写到EPCS配置芯片中即可;

6. 15X2双排直插2.54间距用户接口,用来外接扩展板进行进一步调试;

7. CAN通讯接口;

8. 以太网通讯口B;

9. 以太网通讯口A;

10. 3线制RS232串口通信接口;

11. AD采样芯片AD9240,用来采集模拟电压信号,传送到主芯片;

12. 配置芯片EPCS16,容量16Mbit,可以用来装载程序和数据存储;

13. 5V 电源输入接口,左正右负,开发板上标注有+5字样,接插件接反进不去;

14. 正交编码输入接口,包括电压输入和信号输入;

15. 双极性直流电机驱动模块,包括电流信号的采集,调理等;

16. 50MHz有源晶振,提供系统工作主时钟,通过匹配电阻或是磁珠连接CLK2、

CLK4、CLK7,均可以作为系统时钟使用;

2.4 硬件电路详解

1.EP3C16 FPGA各个bank

图4 EP3C16 Bank原理图

核心板对外接口如下所示,提供了2X15双排直插,2.54间距的标准接口,其中CLK端口只能用作输入端口,其中CLK2、CLK4、CLK7用作时钟输入引

脚,除了配置特殊引脚,其他的一些端口均可用作双向可用IO。

图5 EP3C16排针接口和时钟接口

2.存储器FLASH电路

这里选用的FLASH芯片是FLASH-S29GLO64N90TF106或者

AM29LV641DH90REF,两者管脚兼容,均为64Mbit容量,地址线为AB0-AB21,

数据线为DB0-DB15,FLASH的电源部分采用3.3V供电,电源部分加电容滤波,以提高稳定性,引脚可以和主芯片直接相连接,其中读写、片选信号独立分开,地址、数据线共用地址、数据总线。

图6 存储器FLASH电路

3.存储器SDRAM电路

这里选用的SDRAM芯片是SDRAM-H57V2562GTR,容量为256Mbit,地址为AB0-AB12,本款芯片为行列式存储,内部的为13行,9列。数据线为DB0-DB15。

图7 存储器SDRAM电路

4.存储地SRAM电路

为了满足数据的快速处理,本开发板提供了SRAM存储,以方便用户进行高速的数据缓冲。SRAM芯片采用的是SRAM-61WV102416BLL,容量为16Mbit。

其中地址线为AB0-AB19,数据线为DB0-DB15,读写、片选信号采用独立引脚。

图8 存储器SRAM电路

5.配置部分电路

这部分包括JTAG以及AS配置引脚,还有EPCS16配置芯片,同时设计了复位按键,可以不用断电直接重新配置FPGA。由于Bank1 IO口电压配置为3.3V,所以JTAG采用3.3V供电,锁相环采用2.5V电压供电,MSEL0-MSEL2分别置为GND、2.5V、GND为AS标准配置模式。

图9 配置部分电路

6.时钟及复位部分电路

该开发板采用50M有源贴片晶体为系统提供运行时钟,时钟部分电路电源经过电容和电感滤波,工作更加稳定可靠。EP3C16开发板为客户提供16个CLK 时钟使用,这些时钟可以用作普通的输入引脚,本系统中对这些引脚的处理如下:其中CLK2、CLK4、CLK7为系统工作时钟,直接接入50MHz晶体;其他的时钟引脚用作普通的输入IO口。

图10 时钟及复位部分电路

7.电源部分电路

电源部分主要分为两部分:FPGA供电部分和电机驱动供电这两部分。其中FPGA部分供电需要独立的3.3V、2.5V、1.2V这三种电压,外部输入5V电压,经过LD1117_3.3V稳压后输出3.3V,然后传送给LD1117_1.2V稳压,提供FPGA 的内核工作电压,EP3C16采用2.5V作为锁相环的工作电压,因此需要一个独立的LD1117_2.5V来输出2.5V电压。D7为5V电源工作指示灯,同时该部分的设计采用钽电容作为电源滤波处理,提高稳定性。

图11 FPGA供电部分电源电路

电机驱动和其他部分电源供电电路采用效率较高的电源转换芯片BS0512JS-1W和BS0515LS-1W转换出正负12V和15V电压,供给电路其他部分供电。

图12 电机驱动部分电源和其他部分电源电路

8.AD采样部分电路

AD采样部分主要包括电压调理电路和AD采样这两部分,电机的电流通过霍尔传感器将电流同等比例的减小,再经采样电阻转换为电压信号,经过调理电路之后,传送给AD采样芯片,进行采样。其中AD采样芯片采用AD9240,直接转换过来,只需要一个时钟信号就可以实现高速转换,其中转换速率可以达到3M左右。

图13 AD采样部分电路

9.双极性电机驱动电路

开发板的直流电机驱动采用独立的MOSFET管搭建双极性直流电机驱动,对电机进行控制。

图14 双极性电机驱动电路

该开发板带有A、B两个以太网口驱动,鉴于两个网口驱动一模一样,所以仅给出以太网口A的驱动电路,采用DP83848CVV作为驱动芯片,根据理论计算,可以轻松实现100M以太网需要。其中以太网驱动芯片时钟频率采用有源贴片晶振50MHz进行单独的输入。

图15 以太网驱动芯片电路

图16 以太网接口电路

CAN总线驱动芯片采用SN65HVD230,见开发板右下角。

图17 CAN通讯部分驱动电路

12.串口通讯部分驱动电路

串口通讯采用简单的三线通讯接口,其中串口驱动芯片采用MAX3232,可以直接接受3.3V电平信号,直接和EP3C16主芯片连接。

图18 串口通讯部分驱动电路

13.编码计数部分电路

编码计数模块的计数思路为,先对正交编码进行整形,差分光隔之后进行进

一步的整形滤波之后,传送给EP3C16。

图19 编码计数部分电路

14.其它部分电路

略

三、使用注意事项

3.1 电源

系统供电采用5V输入,左正右负,上边标有+5字样为正,切记不要插反了。

3.2 JTAG拔插方法

切记不要带点拔插USB Blaster JTAG下载线或者并口下载先,容易对FPGA 芯片的内部配置部分电路造成损坏,损坏即不可恢复。

正确操作流程:

连接---断电、连接JTAG下载线、上电

断开---断电、拔下JTAG下载线、上电

3.3 软件说明

Altera的软件版本不断的升级,所以客户自己的开发软件要根据自己的实际情况来选择,不一定最高版本就是好的,但是低版本的软件不能打开高版本的工程。注意安装软件时,Quartus 和NIOS IDE软件版本必须一致,安装在同一个目录下面,安装目录不要有中文和空格。同时在安装软件的时候一定要将该版本的软件补丁装上,不然调试的时候会出一些奇怪的错去,切记。

3.4 引脚配置

开发板上面的一些引脚是配置引脚,在当做普通IO口使用的时候,将特殊功能脚设置为IO口即可(Assigenment->Device->Device and Pin Options->Dual-Purpose Pins->Use as regular I/O)。同时将没用用到的引脚设置为三态输入(Assigenment->Device->Device and Pin Options->Unused Pins->As input tri-stated),将没有用到的电压设置为3.3V(Assigenment->Device->Device and Pin Options->V oltage->3.3V LVTTL)。

四、开发板关键模块测试注意事项

4.1 JTAG测试

按照正确的连接顺序,断电->连接JTAG->上电,建立一个工程,将SOF文件下载到FPGA中即可。切记操作中注意不要带点拔插JTAG线。

4.2 EPCS测试

EPCS的烧写也是通过JTAG进行的,首先需要将SOF文件转换为JIC文件,具体的转换方法和流程可以参照下面网址进行设置。

https://www.360docs.net/doc/7c1865719.html,/lyhdq315/blog/item/31c7e18f52dc8418b21bba1a.html

4.3 存储器SDRAM测试

单独进行SDRAM进行测试的时候,由于SDRAM、FLASH、SRAM共用数

据线、地址线,所以不用FLASH、SRAM的时候注意将片选信号拉高,以免出现不良状况,SDRAM的时钟输入相移给-72°比较合适一般。若和其它存储器件共用数据线时,由于SDRAM的地址线不需要右移一位,直接从AB0开始,而其他存储器件需要右移一位,从AB1开始,所以需要外接一个引脚切换模块。在实际的工程中可以看到。

4.4 存储器SRAM测试

单独进行SRAM测试的时候,同样需要将FLASH、SDRAM的片选信号拉高,由于SRAM驱动是自己编写的,所以进行调试的时候,注意设置时序关系。同时,若用到三态桥进行数据线共享时,注意将地址线右移一位,从AB1开始。

4.5 存储器FLASH测试

单独进行FLASH测试的时候,将SRAM、SDRAM的片选信号拉高,同时注意设置FLASH驱动时序的设置。地址线同样需要右移一位。

以上几个存储器进行测试的时候,可以在SOPC中加入onchip memory模块,可以设置为32k,进行NIOS编译的时候,注意将System Library库进行响应设置。其中程序运行空间可以根据自己的需求进行选择,默认是在onchip memory 中。

图20 System Library设置

FPGA开发板

FPGA开发板 FPGA开发板ALTERA FPGA是世界上十几家生产CPLD/FPGA的公司中最大的可编程逻辑器件供应商之一,生产的FPGA产品有:FLEX6000/8000/10K、APEX20K、ACEX1K、APEXⅡ、Mercury、Excalibur、Cyclone、Stratix、CycloneⅡ和StratixⅡ等系列。 Altera的FPGA器件采用钢铝布线的先进CMOS技术,具有非常低的功耗和相当高的速度,而且采用连续式互连结构,提供快速的、连续的信号延时。Altera器件密度从300门到400万门,能很容易地集成现有的各种逻辑器件,高集成度的FPGA提供更高的系统性能,更高的可靠性,更高的性能价格比。 Altera Cyclone系列FPGA是Altera公司2003年9月份推出的,基于1.5V,0.13μm 工艺,Cyclone 是一个性价比很高的FPGA系列。其中EP1C3T144是Cyclone系列中的一员,共有2910逻辑单元,59904RAM bits,1个PLLs,最多有104个用户I/O,可以说这款FPGA的资源非常丰富,足够满足大型设计的需要。 本公司因此特推出Cyclone EP1C3T144C8 FPGA开发板,该开发板功能强大,接口丰富,可做大型综合实验。 FPGA开发板硬件资源主要有:

1、Altera EP1C3T144C8 FPGA芯片 2、Altera 串行配置芯片EPCS1 3、DAC0832芯片 4、ADC0809芯片 5、液晶接口 6、TP3057PCM编解码芯片 7、八位高亮数码管 8、八位拨码开关 9、4×4阵列键盘 10、4个复位轻触按键 11、9个高亮发光二极管(红、绿、黄色各三灯) 12、双刀双掷继电器 13、异步通信串口(UART) 14、双有源晶振(24MHz和32.768MHz) 15、5V,3.3V,1.5V电源管理系统 FPGA开发板带以下DEMO程序: 1、FPGA实现流水灯实验 2、FPGA实现电子钟实验 3、FPGA实现串口发送实验 4、FPGA实现串口接收、点阵显示实验 5、FPGA实现矩阵键盘和点阵显示(实时扫描方式) 6、FPGA实现矩阵键盘和数码管显示(延时扫描方式) 7、FPGA实现AD转换、数码显示和拨码选择通道实验 8、FPGA实现DA转换,产生锯齿、三角、正弦波;拨码开关选择波形

ARM+FPGA开发板规格书

2014

Revision History

阅前须知 版权声明 本手册版权归属广州创龙电子科技有限公司所有,非经书面同意,任何单位及个人不得擅自摘录本手册部分或全部,违者我们将追究其法律责任。本文档一切解释权归广州创龙电子科技有限公司所有。 ?2014-2018Guangzhou TronlongElectronicTechnologyCo.,Ltd. All rights reserved. 公司简介 广州创龙电子科技有限公司(简称“广州创龙” ,英文简称"Tronlong"),是杰出的 嵌入式方案商,专业提供嵌入式开发平台工具及嵌入式软硬件定制设计及技术支持等服务,专注于DSP+ARM+FPGA 三核系统方案开发,和国内诸多著名企业、研究所和高校有密切的技术合作,如富士康、威胜集团、中国科学院、清华大学等国内龙头企业和院校。 TI 嵌入式处理业务拓展经理ZhengXiaolong 指出:“Tronlong 是国内研究OMAP-L138 最深入的企业之一,Tronlong 推出OMAP-L138+Spartan-6三核数据采集处理显示解决方案,我们深感振奋,它将加速客户新产品的上市进程,带来更高的投资回报率,使得新老客户大大受益。” 经过近几年的发展,创龙产品已占据相关市场主导地位,特别是在电力、通信、工控、 音视频处理等数据采集处理行业广泛应用。创龙致力于让客户的产品快速上市、缩短开发周期、降低研发成本。选择创龙,您将得到强大的技术支持和完美的服务体验。 产品保修 广州创龙所有产品保修期为一年,保修期内由于产品质量原因引起的,经鉴定系非 人为因素造成的产品损坏问题,由广州创龙免费维修或者更换。 更多帮助

金龙STM32F207开发板用户手册

1.概述 金龙STM32开发板用户手册芯片描述 -ARM32-bit Cortex-M3CPU -120MHz maximum frequency,150DMIPS/1.25DMIPS/MHz -Memory protection unit Memories -Up to1Mbyte of Flash memory -Up to128+4Kbytes of SRAM -Flexible static memory controller (supports Compact Flash,SRAM,PSRAM,NOR,NAND memories) -LCD parallel interface,8080/6800modes Clock,reset and supply management -1.8to3.6V application supply and I/Os -POR,PDR,PVD and BOR -4to25MHz crystal oscillator -Internal16MHz factory-trimmed RC -32kHz oscillator for RTC with calibration -Internal32kHz RC with calibration Low power -Sleep,Stop and Standby modes -VBAT supply for RTC, C32bit backup registers 20 optional4KB backup SRAM C12-bit,0.5us A/D converters 3 -up to24channels -up to6MSPS in triple interleaved mode C12-bit D/A converters 2 General-purpose DMA -16-stream DMA controller centralized FIFOs and burst support Up to17timers -Up to twelve16-bit and two32-bit timers Debug mode -Serial wire debug(SWD)&JTAG interfaces -Cortex-M3Embedded Trace Macrocell Up to140fast I/O ports with interrupt capability -51/82/114/140I/Os,all5V-tolerant Up to15communication interfaces C I2C interfaces(SMBus/PMBus) -Up to3 -Up to6USARTs(7.5Mbit/s,ISO7816interface,LIN,IrDA,modem control)

基于DE2-115开发板的FPGA入门设计实验

基于DE2-115开发板的FPGA入门设计实验 1、Lab1: 4位加法器、减法器的设计 1.1 摘要 在文件add_sub里面的工程文件operation_4.v为顶层文件,该顶层文件包含了三个子模块,分别为数码管显示模块,4位带进位的二进制加法器模块和4位带借位的二进制减法器模块,最后通过DE2-115开发板显示实验结果。 1.2 程序 1)add_4bits.v 加法器 module adder_4bits ( input clk, input rst_n, input [3:0] x, input [3:0] y, output reg [3:0] sum, output reg carry_out //溢出位 ); always@(posedge clk or negedge rst_n) begin if(!rst_n)

{carry_out, sum} <= 0; else {carry_out, sum} = x + y; end endmodule 2)substractor_4bits.v减法器module subtractor_4bits ( input clk, input rst_n, input [3:0] x, input [3:0] y, output r eg [3:0] sub, output r eg borrow_out ); always@(posedge clk or negedge rst_n) begin if(!rst_n) {borrow_out, sub} <= 0; else begin

if(x >= y) {borrow_out, sub} = {1'b0, x - y}; else {borrow_out, sub} = {1'b1, x - y}; end end endmodule 3)seg7_lut.v 数码管显示译码模块 module Seg7_lut ( input [3:0] iDIG, output r eg [6:0] oSEG ); always @(iDIG) begin case(iDIG) 4'h1: oSEG = 7'b1111001; // ---t---- 4'h2: oSEG = 7'b0100100; // | | 4'h3: oSEG = 7'b0110000; // lt rt 4'h4: oSEG = 7'b0011001; // | | 4'h5: oSEG = 7'b0010010; // ---m---- 4'h6: oSEG = 7'b0000010; // | |

路虎开发板用户手册

路虎NXP LPC1768开发板 用户手册

1、概述 路虎开发板采用 NXP公司 LPC1768 ARM是一款基于第二代 ARM Cortex-M3内核的微控制器,是为嵌入式系统应用而设计的高性能、低功耗的 32位微处理器,适用于仪器仪表、工业通讯、电机控制、灯光控制、报警系统等领域。路虎开发板板载 USB仿真器,支持 USB2.0 Device,具有双 CAN接口、RS-485接口等功能。路虎开发板配套丰富的例程和详尽的资料,方便用户快速进行项目开发。 功能特点: 强大的 MCU内核:Cortex-M3 ●处理速率高达 100MHz,并包含一个支持 8个区的存储器保护单元(MPU) ●内置嵌套向量中断控制器(NVIC) ● 512KB片上 Flash程序存储器,支持在系统编程(ISP)和在应用编程(IAP) ● 64KB SRAM可供高性能 CPU通过指令总线、系统总线、数据总线访问 ● AHB多层矩阵上具有 8通道的通用 DMA控制器(GPDMA) ●支持SSP、UART、AD/DA、定时器、GPIO等,并可用于存储器到存储器的传输 ●标准 JTAG测试/调试接口以及串行线调试和串行线跟踪端口选项 ●仿真跟踪模块支持实时跟踪 ● 4个低功率模式:睡眠、深度睡眠、掉电、深度掉电

●单个 3.3V电源(2.4V – 3.6V) ●工作温度:-40 °C - 85°C ●不可屏蔽中断(NMI)输入 ●片内集成上电复位电路 ●内置系统节拍定时器(SysTick),方便操作系统移植。 丰富的板载资源: 1、2路 RS232串行接口(使用直通串口线、其中一路串口支持 ISP下载程序) 2、2路 CAN总线通信接口(CAN收发器:SN65VHD230) 3、RS485通信接口(485收发器:SP3485) 4、RJ45-10/100M Ethernet网络接口(以太网 PHY:DP83848) 5、DA输出接口(可做 USB声卡实验、板载扬声器和扬声器输出驱动) 6、AD输入接口(可调电位器输入) 7、彩色液晶显示接口(可接 2.8寸或 3.2寸 TFT 320X240彩屏) 8、USB2.0接口,USB host及 USB Device接口。 9、SD/MMC卡(SPI)接口(提供带 FAT12、FAT16、FAT32文件系统)

RK3188开发板使用手册v1.0

RK3188开发板使用手册v1.0 一.安装RockUsb驱动 (2) 二.查看串口输出信息 (5) 三.烧写/下载固件 (8) 四.Kernel开发 (11) 五.Android开发 (12) 六.制作固件升级包update.img (13) 七.Recovery系统 (14) 八.Android系统USB操作 (17)

一.安装RockUsb驱动 Rockusb驱动放在RK3188\tools\RockusbDriver文件夹中 当你第一次使用RK3188SDK开发板时,接好USB线,按住“VOL+(RECOVERY)”按键上电,会要求安装驱动,按下面的图示步骤进行安装: 图1 选择“否,暂时不(T)”,点击“下一步”进入图2所示界面

图2 选择“从列表或指定位置安装(高级)”,点击下一步,进入图3界面 图3 选择你的驱动所存放的目录,点击“下一步”开始安装驱动,如图4所示

图4 完成以后可以在设备管理器看到设备已经安装成功 图5

二.查看串口输出信息 RK3188SDK开发板没有使用普通的串口,而是使用USB口来输出串口信息,你可以用一根特殊的USB调试线将开发板上的USB口连接到你的电脑中来查看串口信息。 1、在连接USB口之前,请先安装PL-2303USB转串口驱动 2、驱动安装完成后,再使用USB线将开发板上名为“UART0”的USB口连接到PC 中,然后你应该可以在设备管理器中看到一个新设备,如下所示: 3、使用串口工具查看开发板的输出信息。 在这边我以Windows自带的超级终端为例说明串口的配置: a、点击开始->所有程序->附件->通讯->超级终端 点击确定 b、选择正确的COM口:

STM32F429开发板用户手册

STM32F429开发板用户手册 介绍 STM32F429(32F429IDISCOVERY)开发板可以帮助你去学习高性能STM32F4系列,并去开发你自己的应用。它包含了一个STM32F429ZIT6和一个嵌入ST-LINK/V2调试接口,2.4吋TFTLCD,64MbitsSDRAM,ST微机电陀螺仪,按键和USB OTG接口。

1约定 下表提供了一些约定惯例,目前的文档可能会用到。

2快速入门 STM32F429开发板是一种廉价且易于上手的开发套件,可以让使用者快速评估和开始STM32F4的开发工作。 在安装和使用产品以前,请接收评估产品许可协议。 2.1启动 跟随以下顺序来设置STM32F429开发板并开始开发应用: 1、确认跳线JP3和CN4被设置为“on”(开发模式) 2、连接STM32F429Discovery开发板CN1到PC,使用USB电缆(type A/mini-B),开发板上电。 3、屏幕上以下应用可用: 时钟日历和游戏 视频播放器和图片浏览器(播放浏览USB大容量存储器上的视频和图片)性能显示器(观察CPU负载和图形测试) 系统信息 4、演示软件,也像其他软件例程,运行你用来开发STM32F4。 5、从例程开始开发你自己的应用吧。 2.2系统要求 ?Windows PC(XP,Vista,7) ?USB type A to mini-B cable 2.3支持STM32F429开发板的开发工具 ?Altium:TASKING?VX-Toolset ?Atollic:TrueSTUDIO ?IAR:EWARM ?Keil?:MDK-ARM 2.4订购码 要订购STM32F429Discovery kit,请使用STM32F429I-DISCO订购码。 3特性 STM32F429Discovery开发板提供一下特性: ?S TM32F429ZIT6具有2MB闪存,256KB的RAM,LQFP144封装。 ?板载ST-LINK/V2,带有选择模式跳线,可以作为独立的ST-LINK/V2使用。 ?板电源:通过USB总线或外部3V或5V电源。 ?L3GD20:ST微机电动作传感器,3轴数字输出陀螺仪 ?TFT LCD,2.4寸,262K色RGB,240*230分辨率 ?SDRAM64Mbits(1Mbit x16-bit x4-bank),包含自动刷新模式和节能模式 ?六个LED: LD1(红绿):USB通信 LD2(红):3.3V电源 两个用户LED LD3(绿),LD4红 两个USBOTG LED:LD5(绿)VBUS和LD6OC(过流) ?两个按键(user and reset)

FPGA开发板EP1C12用户手册(一版)

使用手册

目 录 第一章综述 (1) EP1C12核心板资源介绍 (1) FPGA开发板资源介绍 (2) 第二章 系统模块功能介绍 (5) EP1C12核心板模块说明 EP1C12F324C8芯片说明 (7) NOR FLASH模块说明 (8) SRAM模块说明 (9) FPGA接口I/O说明 (10) 调试接口JTAG、AS说明 (11) 其它功能模块 (12) EP1C12核心板使用注意事项 (15) FPGA开发平台模块说明 液晶显示模块 (17) RTC实时时钟模块 (19) USB接口模块 (19) 音频CODEC接口模块 (20) EEPROM存储模块 (21) 数字温度传感器模块 (22) 其它功能模块 (23) FPGA开发平台使用注意事项 (24) 附表一 核心板载资源与FPGAEP1C12I/O接口对照表 (25) 附表二 EP1C12与开发板硬件资源I/O接口对照表 (30)

第一章综述 FPGA开发来台是根据现代电子发展的方向,集EDA和SOPC系统开发为一体的综合性实验开发系统,除了满足高校专、本科生和研究生的SOPC教学实验开发之外,也是电子设计和电子项目开发的理想工具。整个开发系统由核心板EP1C12、SOPC开发平台和扩展板构成,根据用户不同的需求配置成不同的开发系统。 EP1C12核心板 EP1C12核心板为基于Altera Cyclone器件的嵌入式系统开发提供了一个很好的硬件平台,它可以为开发人员提供以下资源: 1主芯片采用Altera Cyclone器件EP1C12F324C8 2EPCS4I8配置芯片 34个用户自定义按键 44个用户自定义LED 51个七段码LED 6标准AS编程接口和JTAG调试接口 750MHz高精度时钟源 8三个高密度扩展接口 9系统上电复位电路 10支持+5V直接输入,板上电源管理模块 系统主芯片采用324引脚、BGA封装的E1C12 FPGA,它拥有12060个LE,52个M4K 片上RAM(共计239616bits),2个高性能PLL以及多达249个用户自定义IO。同时,系统还可以根据用户不同的设计需求来更换其它不同系列的核心板,如: EP1C6、EP2C20、EP3C25等。所以,不管从性能上而言,还是从系统灵活性上而言,无论您是初学者,还是资深硬件工程师,它都会成为您的好帮手。

Altium公司的FPGA开发板的原理图

1 12 23 34 45 56 67 78 8 D D C C B B A A 1 02 1/02/20101:34:44 PM NB3000_Top.SchDoc Project Title Size: Date:File:Revision:Sheet of Time:A2Sheet Title NB3000 Top Level Assy:81 NB3000AL - Altera D-820-0053 Altium Limited 3 Minna Close Belrose NSW 2085Australia PSU PSU.SchDoc SRAM SRA M1 SRAM_256Kx 16_TSOP44 STATUS_LED U SE R _STATUS_L E DS DB_LEDS_0603 SRAM1 SRAM2 MEM_COMMON DAU_RESET_SW BUZZER ONE_WIRE_DB_PB SW DIP USERIO EXT_A RS232 KEYBOARD MOUSE TFT_IO DB_PROGRAM STATUS_LED USER_LEDS RELAY I2C CODEC VGA ETH DBSD DBUSB PWM SPDIF DAC ADC RS485 MIDI DB_JTAG DB_CLOCKS DB_SPI ISP176X PROTOTYPE SPAREIO TFT_TSC FPGA _USE R FPGA.SCHDOC INT EXT V IDE O_OU T VGA_OUT.SCHDOC CON CON_VGA CON_VGA_DB15 HOST_JTAG LED1LED2 1WID DB_PROGRAM CLK_PLL FLASH_BOOT HOSTUSB SRAM RTC SD HOST_AUDIO DB_JTAG DB_CLOCKS FLASH_USER DB_SPI PB_A EXTSPI FLASH_GOLDEN DIAGCOMMS FPGA _HOST HOST_FPGA.SchDoc HOST_JTAG HOST_JTA G HOST_JTAG.SchDoc INT EXT R S232 RS232_HIN232 EXT INT KE Y BOA RD PC_PS2 RS232# KBD#MSE# RS232 KEYBOARD EXT INT MOUSE PC_PS2 DIPSW DB_RESET CON CON_DBU SB CON_MINI_USBB_RA_KME04-USBMU03A01-1 DBUSB DBUSB# CON CON_DBSD CON_SD_KSDC012551 DBSD EXT INT DBU SB_TX RX USB_CY7C68001-56LFC.SchDoc INT EXT E TH Ethernet_RTL8201CL.SchDoc ETH CLK_PLL CL K_PL L CLK_ICS307-02_PLL 1WID NB_ID 1WB_DS2502_ID CON CON_HOST_USB CON_MINI_USBB_RA_KME04-USBMU03A01-1 TFT_TSC TFT_TOUCH L CDTFT TSC_XPT2046.SchDoc TFT_TSC TFT_IO CON CON_MOU SE CON_PS2PORT_MINIDIN6F_BLACK INT CON PDA _SW ITCHE S SW_PB_SPNOx5_SMD INT TE ST_RE SE T SW_RESET_SPNO CON USERPOWER CON_IO CON_USER_20WBOXHDRRAMx 2 UIO BUZZER CODEC_AUD AUDIO SPK_L SPK_R HOST_AUDIO AIN AOUT_PBA A UDIO_A MP AUDIO_AMP_NB2C PB_AIN AUDIO SPK_L USER_LEDS CON U SE R _L E D LED_RGB_SMDx 8.SCHDOC USER_LEDS VGA# VGA SW SRAM SRA M2 SRAM_256Kx 16_TSOP44 RELAYS CON R E L AY RELAY_X4_IM03GR RELAY PWM CON PW M PWM_5.8A_30V_X4 PWM 1V21V82V53V35V0 PBPOW E R 1V21V82V53V35V0 I2C DIGITAL CODEC_AUD AIN A UDIO_CODE C Audio_Codec.SchDoc CODEC SPK_L SPK_R CON_SPE AKE R S CON_EXT_SPK SPK_R PB_AOUT PBIO LED1LED2 LED1_EXT LED2_EXT L E D_HOST LED_RGB_SMDx 2 SPDIF CON_SPDIF CON_SPDIF_INOUT_A SPDIF SPI CON DAC DAC_DAC084S085_SPI SPI CON A DC ADC_ADC084S021_SPI DAC ADC CON CON_E TH CON_ETHERNET_RJ45_LEDS ETH# TFT_IO TFT_TOUCH CON_L CDTFT CON_FFC40_LCDTFT.SCHDOC CON CON_RE L AY CON_RELAYx 4_KMRJIO3_5MM_12WAY CON CON_RS232 CON_RS232DCE_DB9_TH BOOT_FLASH MOUNTS Mounts.SchDoc INT EXT R S485 RS485_ISL8491 CON_PSU PWJACK+SWITCH.SchDoc HOST_USB HOSTUSB# EXT INT HOST_USB_TXR X USB_CY7C68001-56LFC.SchDoc VBATT CON_BA TT CON_BATT_COIN VBATT VBATT RTC R T CL OCK CLK_PCF2123_RTC HOST_RTC USERPOWER U SE R _POW E R USERPWR.SCHDOC CON CON_HOST_SD CON_SD_KSDC012551 RS485#CON CON_RS485 CON_RS485_RJ45 INT EXT MIDI INTE RFA CE MIDI_FULL CON CON_MIDI CON_MIDI_DIN5 MIDI# MIDI RS485HOST_AUDIO PBCTRL DB_PROGRAM HOST_JTAG HOST_ID HOST_CLK HOST_SRAM HOST_LED1 HOST_LED2 HOST_SD DB_SRAM1 DB_SRAM2 DB_MEM DB_STATUS ADC# RELAYS# PWM# DAC# UIO_PWR DB_JTAG DB_CLOCKS PB_SPI USER_FLASH DB_SPI EXT ONE_WIRE_DB_PB AIN I2C SPI AOUT CTRL PBPOWER CON_PE R IPHE R AL _BRD PBCON USER_LEDS SW_PDA SPARE_IO CON_L E DKBD CON_NB3000_LEDKB SERFLASH SYSBOOT FLASH_M25PX0_SPI_8Mbit GOLD_FLASH SERFLASH GOL DE N FLASH_M25PX0_SPI_8Mbit FLASH U SE R _FL A SH FLASHSPI_M25PX0 INT SW _DIP8_SM T SW_DIP8_SMT CON CON_KE YBOAR D CON_PS2PORT_MINIDIN6F_BLACK CON CON_USB1 CON_USBA_RA_UPRIGHT LEDS# ATE DIAGCOMMS A TE INTE R FACE CON_NB3000_ATE_INTF ISP176X PORT1 PORT2 PORT3 U SB_U SE RHOST USB_ISP1760 ATE VGA#SPDIF UIO ADC#DAC#AUDIO HOST_JTAG PWM RS232#RS485#KBD#MSE#MIDI# HOST_ID A TE INTE R FACE VGA#SPDIF UIO ADC# DAC# AUDIO HOST_JTAG PWM# RS232#RS485#KBD#MSE#MOUSE ISP176X PORT1 PORT2 PORT3 PROTOTYPE U SE R _PROTOTYPE _AR E A PROTOTYPE_A PROTOTYPE CON CON_AU DIO CON_AUDIO_AC99_NOMIC.SCHDOC DIAGCOMMS MIDI# HOST_ID SW# SPAREIO MEM COMM ON_ME M OR Y CommonMemory CON CON_ADC CON_ADCx 4_KMRJIO3_5MM_6WAY CON CON_DAC CON_DACx 4_KMRJIO3_5MM_6WAY CON CON_PW M CON_PWMx4_KMRJIO3_5MM_6WAY CON CON_USB2 CON_USBA_RA_UPRIGHT CON CON_USB3 CON_USBA_RA_UPRIGHT SRAM SRA M_HOST SRAM_256Kx 16_TSOP44 TFT_TOUCH INT U SB_CL K OSC_24MHZ.SchDoc HOST_USB.XTALIN HOST_USB.XTALOUT CMOSOUT XTALIN XTALOUT OSC DBUSB.XTALIN

STM32F0-DISCOVERY用户手册

1/30 文档ID 022910第1版2012年3 月 STM32F0DISCOVERY STM32F0探索套件 UM1525 前言 STM32F0DISCOVERY 是意法半导体STM32F0系列微控制器的探索套件,用于帮助你探索STM32F0 Cortex-M0微控制器的功能,轻松开发应用设计。STM32F0探索套件基于1颗STM32F051R8T6微控制器,组件包括ST-LINK/V2嵌入式调试工具、LED 指示灯、按键和1个原型板。 图1: STM32F0 探索套件 用户手册

2/30UM1525 文档ID 022910第1版 目录目录 1. 约定....................................................................................................................................52. 快速入门 (6) 2.1 开始使用........................................................................................................ 62.2 系统要求..........................................................................................................62.3 支持STM32F0探索套件的开发工具链 .......................................................62.4 订货代码. (6) 3. 特性....................................................................................................................................74. 硬件与原理图.. (8) 4.1 STM32F051R8T6 微控制器 ..........................................................................114.2 嵌入式ST-LINK/V2编程器/调试器 . (13) 4.2.1 使用ST-LINK/V2向板载STM32F0烧录和调试代码 ............................14 4.2.2 使用ST-LINK/V2向外部STM32应用板烧录和调试代码. (15) 4.3电源和电源选择............................................ 164.4 LED 指示灯 ...................................................................................................164.5 按键................................................................................................................164.6 JP2(Idd ) ﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍ 16 4.7 OSC 时钟 -----------------------------------------------------------------------------174.7.1 OSC 时钟电源 .............................................................................................174.7.2 OSC 32kHz 时钟电源 17 4.8 焊桥.................................................................................................................184.9 扩展连接器.. (19) 5. 尺寸图..............................................................................................................................266. 原理图..............................................................................................................................277. 修改历史记录 (30)

基于FPGA开发板的数字钟设计初探

基于FPGA开发板的数字钟设计初探 摘要:本文介绍了基于FPGA开发板的数字钟设计的基本构想,所提供的功能,基本的模块和控制逻 辑。 关键词: 模块,数字钟 1引言 VHDL结合FPGA可以方便地,可重复利用地实现各种设计,本文主要从原理上规划出设计一个数字钟需要的模块和功能逻辑,以便后期使用VHDL和FPGA实现。 2 设计原理 本文打算实现的数字钟向用户提供的功能包括:秒、分、时、日、月显示,闹钟设定,时间校准。鉴于所提供的功能,电路应当包括以下五大模块:控制模块,分频模块,闹钟模块,计时模块和显示模块。控制模块包括了输入部分,用户通过外部按钮选择数字钟工作模式和输入基准时间,闹钟时刻;分频模块主要是给需要的模块提供特定频率的时钟信号;闹钟模块的主要作用是接收并存储用户输入的闹钟时刻,比较当前时刻是否是用户所设定的闹钟时刻,进而决定是否启动闹钟提醒装置(蜂鸣器);计时模块包括了秒、分、时、日,月计数模块,并提供给显示模块显示输出;显示模块包括数码管及驱动部分,蜂鸣器。 3 电路设计 控制模块主要是一个译码电路,控制系统所处的模式:正常计时显示,时间校准,设定闹钟。 计时模块通过六十进制、二十四进制、三十或三十一进制和十二进制的计数器实现计时。计时模式下利用分频器提供的基准时钟信号实现计时;时间校准模式下,用户输入按钮的脉冲作时钟信号。 分频模块是一个分频器,将系统提供的时钟分频到需要的频率。 闹钟模块在计时模式下利用比较电路检测当前时间,如果是闹钟时刻,则启动蜂鸣器;闹钟模式下,用户通过输入按钮脉冲设定闹钟,闹钟模块记录并存储。 显示模块在计时模式和时间校准模式下由计时模块控制显示,设定闹钟时由闹钟模块控制显示,方便用户设定闹钟,蜂鸣器由闹钟模块控制。

AX301用户手册REV1.0

FPGA黑金开发平台 用户手册 AX301 REV 1.0 芯驿电子科技(上海)有限公司 黑金动力社区 https://www.360docs.net/doc/7c1865719.html,

目录 一、简介 (3) 二、电源 (6) 三、FPGA (7) 1)JTAG接口 (8) 2)配置芯片:M25P16 (8) 3)FPGA供电引脚 (9) 4)FPGA时钟输入引脚 (10) 四、50M有源晶振 (11) 五、SDRAM (11) 六、EEPROM 24LC04 (14) 七、PS/2接口 (15) 八、实时时钟DS1302 (16) 九、数码管 (17) 十、USB转串口 (19) 十一、VGA接口 (20) 十二、蜂鸣器 (23) 十三、SD卡槽 (24) 十四、扩展口 (25) 十五、LED (27) 十六、按键 (28) 十七、摄像头接口 (29) 十八、7寸TFT接口 (30)

FPGA黑金开发平台学生版2014款正式发布了,此款开发平台是在前两款学生版的基础上升级而来,型号为:AX301。虽然是一款入门级的FPGA开发平台,但是我们不管是在PCB设计上,还是在整个构造上都花费了很多的心思,真可谓“简约而不简单”。 一、简介 在这里,对这款FPGA开发平台进行简单的功能介绍。 此款开发板使用的是ALERA公司的CYCLONE IV系列FPGA,型号为EP4CE6F17C8,256个引脚的FBGA封装。根据ALTERA官方的数据,CYCLONE IV相对CYCLONE III来说,功耗减少25%,如下图所示 此款FPGA的资源如下图所示:

其中,主要的参数, 逻辑单元LE:6272; 乘法器LAB:392; RAM:276480bit; IO数量:179个; 内核电压:1.15V-1.25V(推荐1.2V); 工作温度:0-85℃ 图为整个系统的结构示意图:

单片机开发板操作手册.

单片机开发板操作手册 一、概述 1,多功能单片机开发板,板载资源非常丰富,仅是包括的功能(芯片)有:步进电机驱动芯片ULN2003、 八路并行AD转换芯片ADC0804、 八路并行DA转换芯片DAC0832、 光电耦合(转换)芯片MOC3063、 八路锁存器芯片74HC573、 实时时钟芯片DS1302及备用电池、 IIC总线芯片A T24C02、 串行下载芯片MAX232CPE, 双向可控硅BTA06-600B、 4*4矩阵键盘、 4位独立按键、 DC5V SONGLE继电器、 5V蜂鸣器、 八位八段共阴数码管 5V稳压集成块78M05 八路发光二极管显示 另还有功能接口(标准配置没有芯片但留有接口,可直接连接使用):单总线温度传感器DS18B2接口、 红外线遥控接收头SM003接口8、 蓝屏超亮字符型液晶1602接口、 蓝屏超亮点阵图形带中文字库液晶12864接口、 2(4)相五线制小功率步进电机接口、 外接交流(7V-15V)电源接口 USB直接取电接口 镀金MCU晶振座 40DIP锁紧座 外接电源和5V稳压电源的外接扩展接口及MCU所有IO口扩展2,可以完成的单片机实验: 1、LED显示实验(点亮某一个指示灯、流水灯), 2、八位八段数码管显示实验(你可以任意显示段字符和数字以及开发板所有功能芯 片的显示), 3、液晶显示(1602液晶显示、12864点阵中文图形液晶显示、可以显示出开发板所 有功能芯片的操作), 4、继电器的操作 5、蜂鸣器的操作(你可以编写程序让它发出美妙动听的歌声) 6、可控硅的操作(胆大的朋友就利用这一独有的功能吧,你见过实验室温度实验箱 没有,它的驱动就是这样的;聪明的朋友就可以自己写个程序把把加热温度温 度恒定在(X±0.5)度的范围内了 7、步进电机的操作(这个是迈向自动化控制的第一步,现在的数控机床、机器人呀

Altera Cyclone III系列FPGA开发板简介

ETL-002 Altera Cyclone III 系列FPGA开发板简介 概述 ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述 主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。开发板同时支持AS模式下载和JTAG模式下载。程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。 丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。这些接口主要包括: PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上 PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上 VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。开发板自带了动态彩条显示的功能 双串口接口:可以与任何的串口设备相接。开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。开发板自带的演示程序实时地显示分钟和秒钟的信息。 4位LED灯:用于指示状态。开发板自带了跑马灯实验。 4位按键开关:可用于复位等作用。 4位拨码开关:可用于电路的选择作用

FPGA开发板实验手册2017

FPGA开发板实验指导书(2017) 第一章注意事项 工程未使用到的IO请设置为三态 所有程序请一定将未定义的引脚设为三态输入(As input tri-stated),一定不能将未使用的引脚设置为输出(As outputs driving ground),否则可能会造成核心板主芯片及存储芯片冲突损坏!或是造成其它意想不到的损坏! 如何设置未使用的引脚为三态? 答:Quartus--菜单Assignments--Device---Device and Pin Options---Unused Pins---Reserve all unused pins==改为As input tri-stated 每个例程下载前都养成习惯,先查下设置对不对,不对的话,改好,要重新编译一下。 如果程序下载进去,数码管、LED灯都乱亮了,那肯定是没设置好,请严格遵照上面的修改好,重新编译。 1.1JTAG及AS的插拔安全 开发板带有JTAG和AS下载接口,严禁带电拔抽JTAG及AS下载线!带电操作容易对FPGA芯片的内部配置部分电路造成致命损坏,损坏后是无法修复的!请牢记一条:插拔下载线时必须断电!平时建议大家使用JTAG下载插口,如图1.1所示,红色框的为JTAG下载口。AS插口在必要时再使用。 图1.1 下载接口JTAG和AS 1.2外接电源 开发板套装里面附带标准5V/2A电源一条,5V输入,内正外负。建议使用我们标配电源,如果使用其它电源,请您一定确认输出电压是否为5V,以免由于电压不同造成开发板损坏! 核心板和接口板均设有5V电源插口,位置在PCB左上角。如图1.2所示:使用开发板时,只用随便接一个插口即可。不必要核心板和接口板都插电源。因为电源走线内部是相通的。 注意图1.2蓝白色那个按键就是全板电源总开关,按下后即可接通电源,这时底板与核心板左上角均有电源指示灯LED点亮。正常情况下:板载的流水灯程序就运行了。