02-ARM嵌入式处理器-2-讲义

ARM 嵌入式处理器

异常与中断

1

IRQ

北京交通大学

国家电工电子教学基地

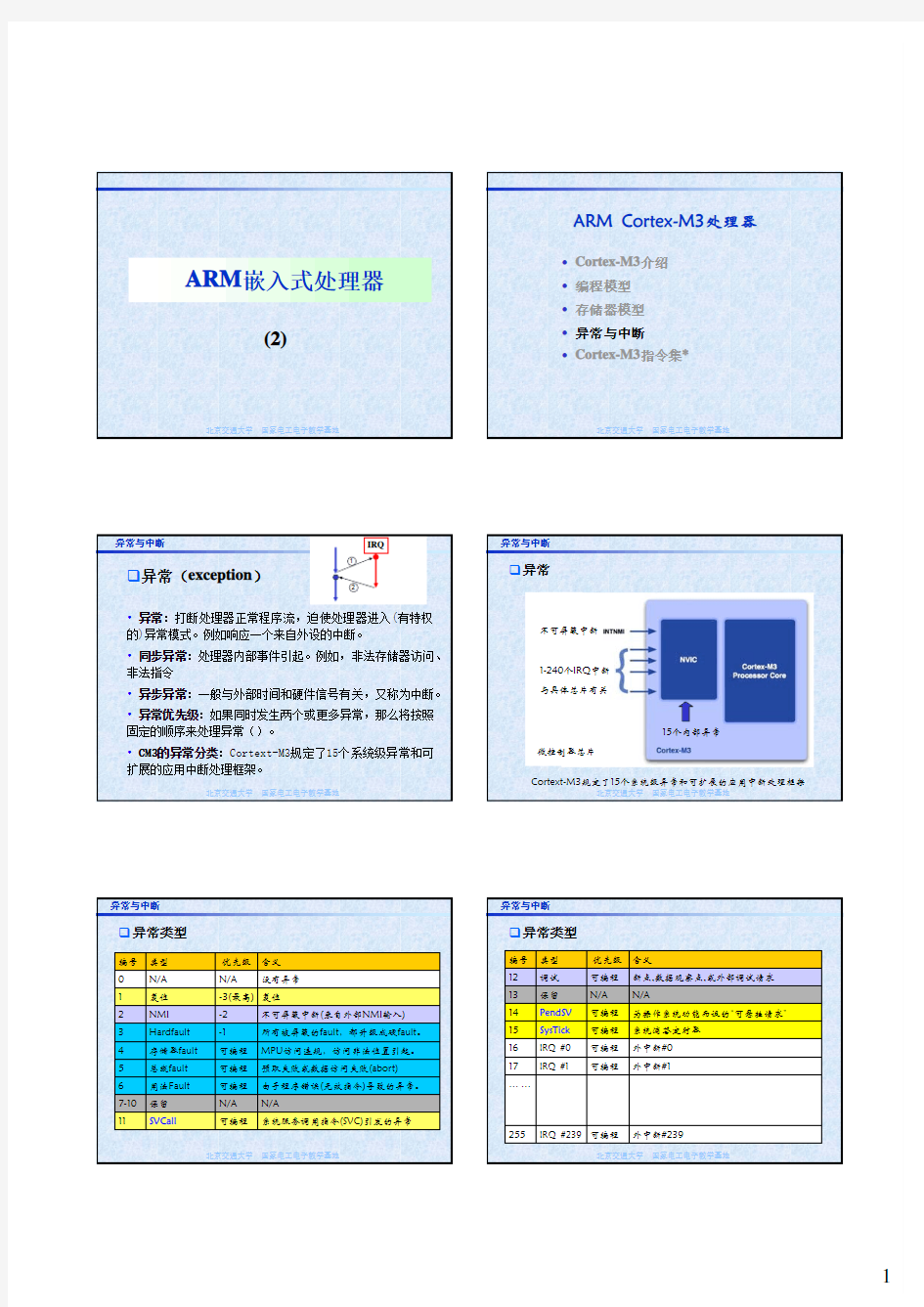

异常与中断

1-240个IRQ中断15个内部异常

微控制器芯片

不可屏蔽中断

与具体芯片有关

Cortext-M3规定了15个系统级异常和可扩展的应用中断处理框架

异常与中断异常与中断

北京交通大学

国家电工电子教学基地

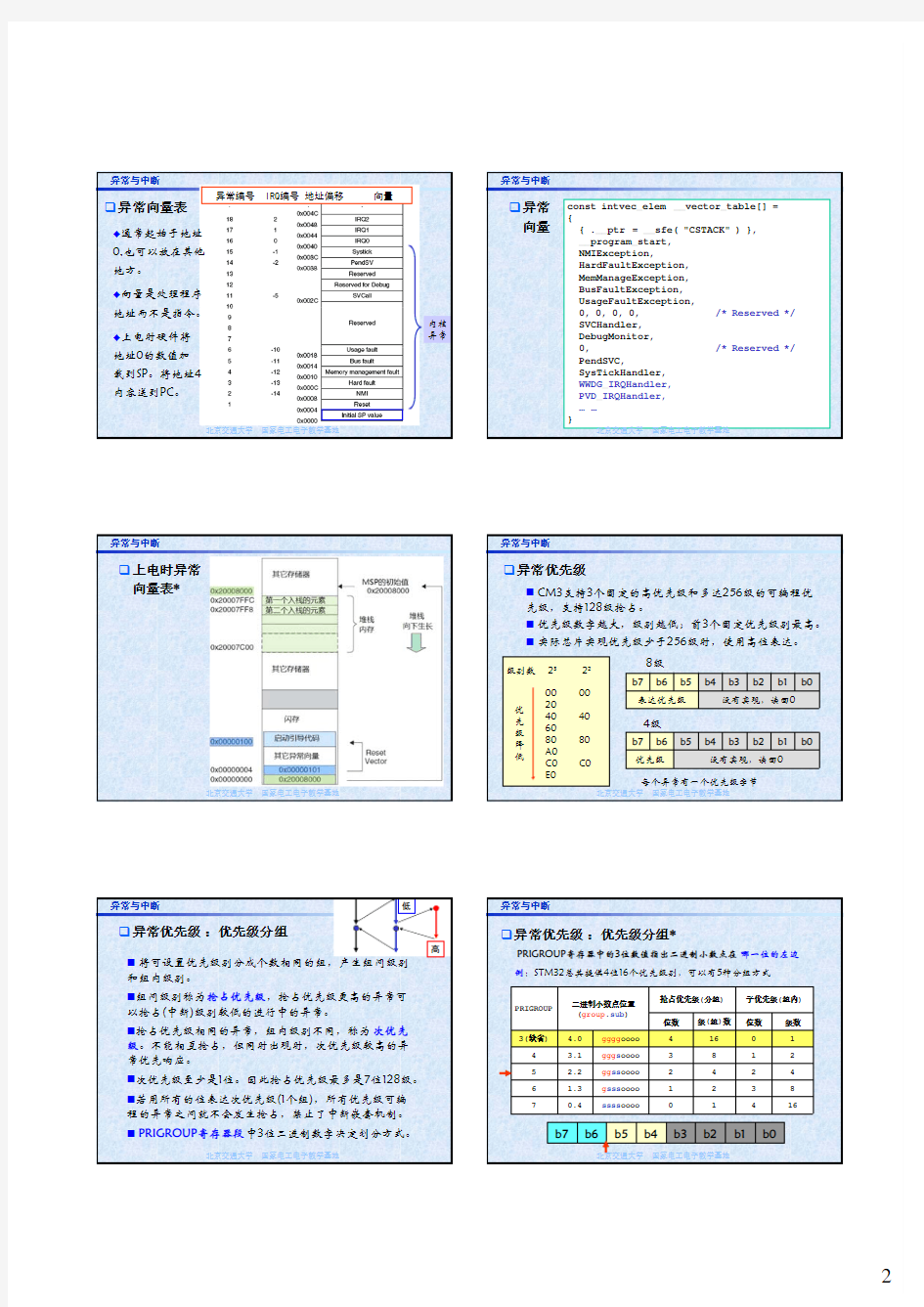

异常与中断通常起始于地址

0,也可以放在其他向量是处理程序

地址而不是指令。

载到SP。将地址4异常编号

IRQ编号地址偏移

向量

异常与中断

北京交通大学国家电工电子教学基地

异常与中断异常与中断

异常与中断低异常与中断

异常与中断

00H 10H 异常与中断

异常与中断硬件完成

异常堆栈帧

异常与中断

北京交通大学

国家电工电子教学基地

异常与中断?异常返回值*

在进入异常服务程序后,LR的值被自动更新为特殊的北京交通大学

国家电工电子教学基地

异常与中断

北京交通大学国家电工电子教学基地异常与中断?异常返回值*

在异常处理中可以修改PSP 使之指向不同的进程

北京交通大学国家电工电子教学基地

异常与中断

?嵌套向量中断控制器(NVIC)

国家电工电子教学基地

异常与中断(某中断发生了?)PRIMASK, FAULTMASK和BASEPRI )寄存器

软件通过访问这些寄存器来设定NVIC 的功能,了解当前中断状态。

北京交通大学

国家电工电子教学基地

异常与中断

?嵌套向量中断控制器(NVIC)

写中断允许寄存器

Clr 写中断关闭寄存器

写设定悬挂寄存器

写清除悬挂寄存器

去优先级

仲裁逻辑

优先级寄存器

中断n

每一个外部中断IRQ的控制逻辑

异常与中断CLRENA0

异常与中断

异常与中断异常与中断

没有地址,特权模式下访问异常与中断异常与中断

异常与中断异常与中断

如果在高优先级中断退出之前,低优先级中断挂起,则

在高优先级ISR1退出时不会弹出堆栈,而是直接取ISR2的

地址,更新寄存器等,只需要6个时钟周期。

异常与中断如果在较高优先级中断退出,堆栈弹出过程中低优先级中断挂起,未完成的弹出过程废止,SP恢复到原值,用额外的6个周期取指令,更新寄存器。

北京交通大学

国家电工电子教学基地

异常与中断

?ISR2按尾链方式进入。

北京交通大学国家电工电子教学基地异常与中断后直接进入休眠模式。成为完全中断驱动的低功耗应用程序。

北京交通大学国家电工电子教学基地

异常与中断

ARM Cortex-M3处理器时钟源选择,中段允许,计时启动,北京交通大学

国家电工电子教学基地

异常与中断

?Cortex-M3处理器框图

异常与中断

ARM Cortex-M3指令集ARM Cortex-M3指令集ARM Cortex-M3指令集ARM Cortex-M3指令集

ARM Cortex-M3处理器(CM3)