基于FPGA的ZBTSRAM接口控制器的设计

计算机应用

Computer Application

《自动化技术与应用》2004年第23卷第10期基于FPG A的Z BT SRAM接口控制器的设计

何永泰,黄文卿

(楚雄师范学院物理与电子信息科学系,云南 楚雄 675000)

摘要:Z ero Bus Turnaround(Z BT)SRAM是一种高速存储器,根据其操作接口的时序要求,本文介绍了一种基于Altera S tratix和S tratix

G X FPG A的Z BT SRAM接口控制器,在文中详细介绍了Z BT SRAM的接口时序和FPG A接口控制器的结构以及对Z BT SRAM

的读写操作过程。

关键词:Z BT SRAM;FPG A;控制器

中图分类号:TP33213 文献标识码:B 文章编号:100327241(2004)1020049203

FPGA-Bas e d ZB T S RAM Interf ace Co ntroller

HE Yong-tai,HUANG Wen-qing

(Department of Physics and E lectron In formation Science,Chuxiong N ormal University,Chuxiong675000,China)

Abstract:Z BT SRAM is a HS M(high speed mem ory).The inter face controller of Z BT SRAM based on Altera S tratix and S tratix FPG A is intrduced in the paper.The timing sequences of Z BTSRAM,the structure of FPG A inter face controller,and the reading and wirting operating process of Z BT SRAM are discussed in detail.

K ey w ords:Z BT SRAM;FPG A;controller

1 引言

随着计算机网络和通信系统的发展,对接口电路和外围器

件在通频带和执行速度上提出了更高的要求,要求接口电路的

带宽更宽,器件的执行速度更快。对于标准的静态存储器

SRAM,当频繁地对他进行读写操作时,在读写操作的转换期间,

他需要一定的等待时间,效率比较低,难于满足宽频带和高速度的需要。为此,I DI,M icron

和M otorla等公司已经设计出了Z ero Bus Turnaround(Z BT)SRAM存储器,解决标准SRAM中存在的问题。本文根据Z BT SRAM的接口时序要求,介绍一种基于FPG A 的Z BT SRAM的接口设计方法和设计的基本原理。

2 Z BT SRAM介绍

211 Z BT SRAM的概述

Z BT SRAM是具有一个简单接口的同步突发(SyncBurst) SRAM,他通过减少读写操作转换间的等待时间,允许设计者充

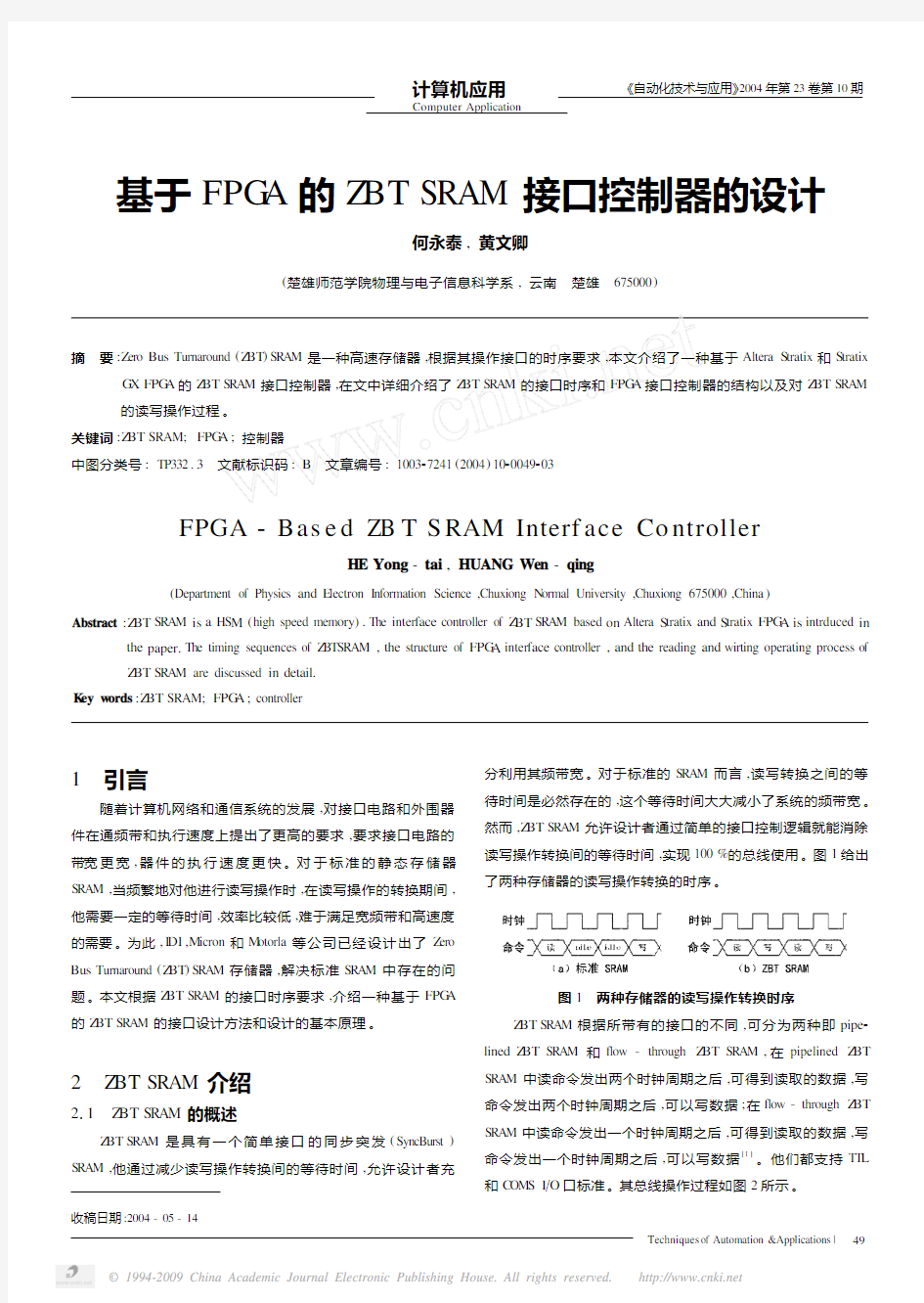

收稿日期:2004-05-14分利用其频带宽。对于标准的SRAM而言,读写转换之间的等待时间是必然存在的,这个等待时间大大减小了系统的频带宽。然而,Z BT SRAM允许设计者通过简单的接口控制逻辑就能消除读写操作转换间的等待时间,实现100%的总线使用。图1给出了两种存储器的读写操作转换的时序。

图1 两种存储器的读写操作转换时序

Z BT SRAM根据所带有的接口的不同,可分为两种即pipe2 lined Z BT SRAM和flow-through Z BT SRAM,在pipelined Z BT SRAM中读命令发出两个时钟周期之后,可得到读取的数据,写命令发出两个时钟周期之后,可以写数据;在flow-through Z BT SRAM中读命令发出一个时钟周期之后,可得到读取的数据,写命令发出一个时钟周期之后,可以写数据[1]。他们都支持TT L 和C OMS IΠO口标准。其总线操作过程如图2所示。

《自动化技术与应用》2004年第23卷第10期

计算机应用

Computer

Application

图2 Z BY SRAM 的总线操作

212 Z BT SRAM 的接口信号

Z BT SRAM 的接口信号主要由时钟信号、控制总线、地址总

线和数据总线等组成。其中,时钟信号是为Z BT SRAM 实现包括读、写操作在内的各种操作提供驱动信号;控制总线主要由三种信号组成。①RW N 是读写控制信号,RW N =1允许读操作,RW N =0允许写操作。②BW N 是同步字节写使能信号,每个字节都有自己有效的写使能低电平。③ADV LD N 是地址控制信号,ADV LD N =0时内部的寄存器加载新的地址,若在时钟的上升沿ADV LD N =1则内部地址计数器增加;地址总线S A[ASIZE -1—0]他为对Z BT SRAM 读写操作存储器单元提供存储地址寻址信号。其位数由Z BT SRAM 的存储容量决定;数据总线DQ[DSIZE -1—0]是Z BT SRAM 在读写操作时与外部进行数据交换的通道。

3 接口控制器的设计

根据Z BT SRAM 的接口信号和时序要求,利用Altera S tratix 和S tratix G X FPG A 产生简单的Z BT SRAM 接口信号

,实现对Z BT

SRAM 的各项操作。该设计在一片高速FPG A EP1S25F780C5上

实现,FPG A 和Z BT SRAM 的工作频率为200MHZ ,FPG A 接口控制器和Z BT SRAM 的连接框图如图3所示。

图3 FPG A 接口控制器的结构及功能

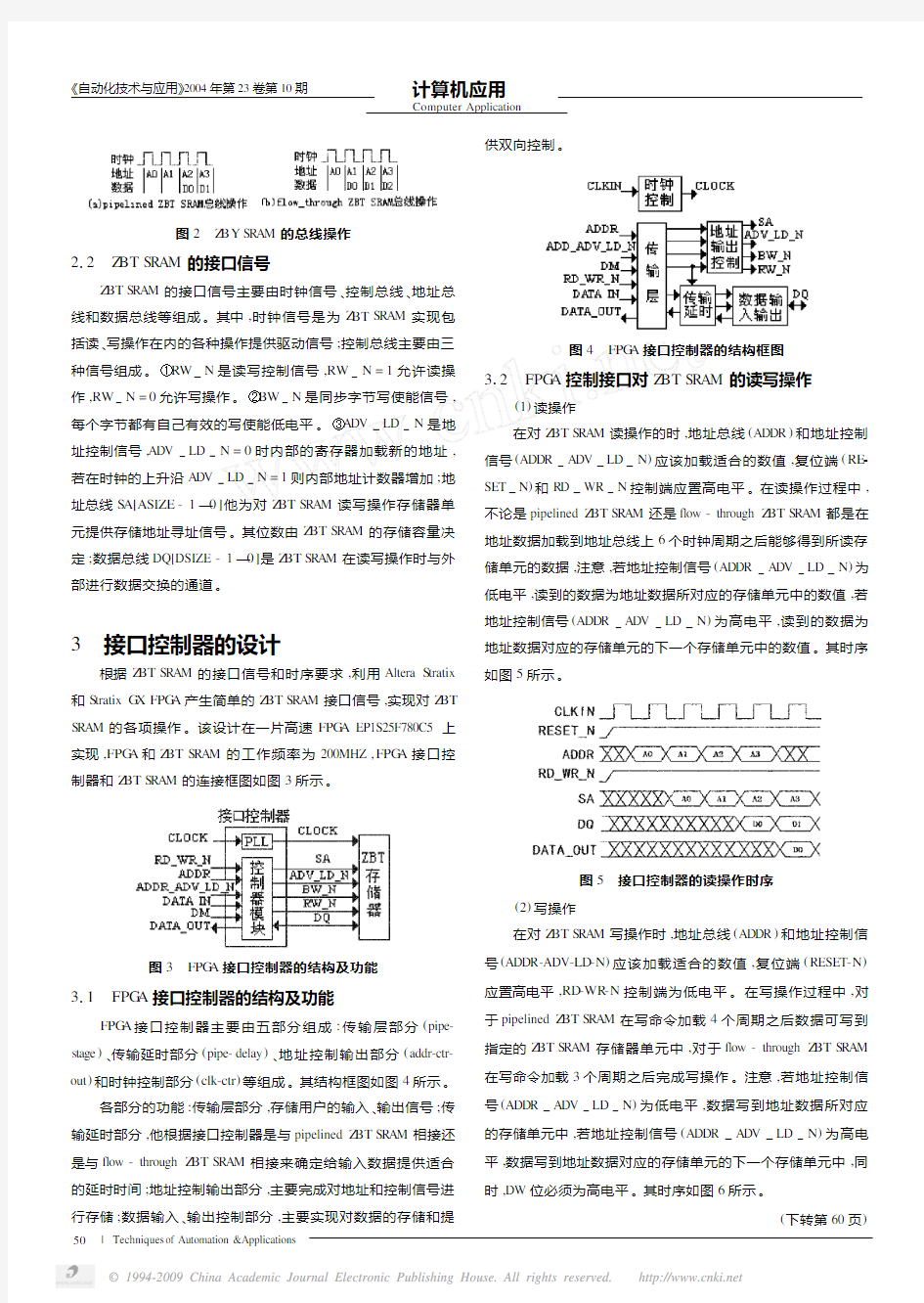

311 FPG A 接口控制器的结构及功能

FPG A 接口控制器主要由五部分组成:传输层部分(pipe-stage )、传输延时部分(pipe-delay )、地址控制输出部分(addr-ctr-out )和时钟控制部分(clk-ctr )等组成。其结构框图如图4所示。

各部分的功能:传输层部分,存储用户的输入、输出信号;

传输延时部分,他根据接口控制器是与pipelined Z BT SRAM 相接还是与flow -through Z BT SRAM 相接来确定给输入数据提供适合的延时时间;地址控制输出部分,主要完成对地址和控制信号进行存储;数据输入、输出控制部分,主要实现对数据的存储和提

供双向控制。

图4 FPG A 接口控制器的结构框图

312 FPG A 控制接口对Z BT SRAM 的读写操作

(1)读操作

在对Z BT SRAM 读操作的时,地址总线(ADDR )和地址控制信号(ADDR ADV LD N )应该加载适合的数值,复位端(RE 2

SET N )和RD WR N 控制端应置高电平。在读操作过程中,

不论是pipelined Z BT SRAM 还是flow -through Z BT SRAM 都是在地址数据加载到地址总线上6个时钟周期之后能够得到所读存储单元的数据,注意,若地址控制信号(ADDR

ADV LD N )为低电平,读到的数据为地址数据所对应的存储单元中的数值,若地址控制信号(ADDR ADV LD N )为高电平,读到的数据为

地址数据对应的存储单元的下一个存储单元中的数值。其时序如图5所示。

图5 接口控制器的读操作时序

(2)写操作

在对Z BT SRAM 写操作时,地址总线(ADDR )和地址控制信

号(ADDR -ADV -LD -N )应该加载适合的数值,复位端(RESET -N )应置高电平,RD -WR -N 控制端为低电平。在写操作过程中,对于pipelined Z BT SRAM 在写命令加载4个周期之后数据可写到指定的Z BT SRAM 存储器单元中,对于flow -through Z BT SRAM 在写命令加载3个周期之后完成写操作。注意,若地址控制信号(ADDR ADV LD N )为低电平,数据写到地址数据所对应的存储单元中,若地址控制信号(ADDR

ADV LD

N )为高电

平,数据写到地址数据对应的存储单元的下一个存储单元中,同时,DW 位必须为高电平。其时序如图6所示。

(下转第60页)

《自动化技术与应用》2004年第23卷第10期

仪器仪表与检测技术

Instrumentation and Mea surement

P R =

πD

N

=

12196×

π8000

=010051mm ≈5um

如果在控制方法上采取一些措施,例如单向矢量控制和在位移量末端采用单向逐次逼近的策略,达到要求的定位精度是可能的。

由于采用步进电机,和<12.96mm 的转动轴,那么变速器的变比需要多大?

通常,步进电机分为全步Π半步驱动两种方式,这两种驱动基本上保证了转角的精确度,如采用细分方法驱动,可以减少变速比,但是,定位精度低于全步Π半步驱动,而且要求的电机转矩较大。故在本方案设计中,采用半步驱动(0.9°Πstep ),转动也相对平稳,那么此时的变速比应该是:

019°n ?12196π

360°

×0.9°=0.0051mm n =20.3575为了提高精度,在模板位移的末端,采用单向逐步逼近的控制方法,变速比不能选n =20,如果采用三步逼近,变速比即为:

n =61.0725

变速比不能是小数;另一方面,考虑到我们是单台,尽量选用标准件。目前,市场上出售的变速箱Π变速器,是16、32、

64......故选用n =64。此时,步进电机走一步,驱动轴的线性

位移量为:

d =

12196π360?019

64

=0100159mm 三步逼近量为:

3d =0.00477mm

由此以来,我们就可以通过用半步驱动的步进电机、变速器、光码盘相结合的方法解决胶片位移精度的问题,这也是保证光栅印制质量的基本问题。

3.3 位移检测实验分析

通过实验对位移检测部分进行调试,检测胶片的实际位移是否满足精度要求,实验数据记录如表1所示,通过分析计算,该数据与理论数据接近,满足精度要求。

表1 胶片实际位移测试表

走胶片宽度

次数(10)

123456789101cm 07A007A307A207A007A307A207A107A207A207A12cm

0F50

0F52

0F51

0F50

0F52

0F51

0F51

0F52

0F52

0F52

4 小结

通过对上述方案进行整体试验调试,基本可以满足设计要求,当然,该方案的实施需要机械部件、电气特性、控制软件之间达到最佳协调。在后续研究中,我们将对相关细节问题和关键技术另立专题讨论。

5 参考文献:

[1] 张百海,柴森春,等.数据采集系统中光栅尺信号处理方法的

研究[J ],机床与液压,2003,(2):118-119

[2] 臧甲鹏

,王朝阳.高衍射效率全息光栅的制作与复制工艺研究[J ].M odern Scientific Instruments 1999,(5):46-48

[3] 裴文.全息印刷—21世纪的印刷术[J ].物理,1995,(3):160-165

作者简介:张光 (1979-),女,陕西西安人,硕士,研究方向:计算机图形图像处理技术。

(上接第50页)

图6 接口控制器的写操作时序

4 结束语

利用S tratix 和S tratix G X FPG A 作为Z BT SRAM 的接口控制器能较好地解决系统的竞争冒险问题。S tratix 和S tratix G X FP 2

G A 的开启时间和关断时间分别为 3.3ns 和 2.2ns ,I DT 71V3556P200-MHZ pipelined Z BT SRAM 的开启时间和关断时

间分别为3.2ns 和3.0ns [2]。若接口控制器执行一条写操作之后执行读操作,不会有竞争出现,因为Z BT SRAM 的关断时间比

FPG A 的开启时间快。相反,若接口控制器执行一条读操作之

后,执行写操作,同样也不会出现竞争冒险的问题,因为,FPG A 的关断时间比Z BT SRAM 的开启时间快。

5 参考文献:

[1] Synthesizable 200MHZ Z BT SRAM interface [E B/O L ].w w w.X https://www.360docs.net/doc/9e9288065.html, ,2003,3

[2] Z BT controller reference Design[E B/O L ].w w https://www.360docs.net/doc/9e9288065.html, ,2003,4

作者简介:何永泰(1970-),男,云南南华人,楚雄师范学院讲师,昆明理工大学硕士研究生,主要从事电子工程设计方向的研究。

基于FPGA的计数器的程序的设计方案

基于FPGA的计数器的程序设计方案 1.1 FPGA简介 FPGA(Field-Progrmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了 原有可编程器件门电路数有限的缺点。 自1985 年Xilinx 公司推出第一片中大规模现场可编程逻辑器件(FP2GA) 至 今,FPGA 已经历了十几年的历。在这十几年的过程中,可编程器件有了惊人的发展: 从最初的1200 个可利用门,到今天的25 万可利用门,规模增大了200 多倍; FPGA 供应商也从Xilinx 的一枝独秀,到今天近20 个厂商的分庭抗争;FPGA 从单一的基于SRAM结构到今天各种结构类型的出现,都充分体现了可编程器件这一巨大市场的吸引力。FPGA 不仅可以解决电子系统小型化、低功耗、高可靠性等问题,而且其开 发周期短、开发软件投入少、芯片价格 不断降低。由于目前电子产品生命周期相对缩短,相近功能产品的派生设计增多 等特点,促使FPGA 越来越多地取代了ASIC 的市场,特别是对国内众多的科研单位来说,小批量、多品种的产品需求,使得FPGA 成为首选。 1.2 硬件描述语言VHDL特点 功能强大、设计灵活。VHDL具有功能强大的语言结构,可以用简洁明确的源代码来描述复杂的逻辑控制。它具有多层次的设计描述功能,层层细化,最后可直接生成电路级描述。VHDL支持同步电路、异步电路和随机电路的设计,这是其他硬件描述语言所不能比拟的。VHDL还支持各种设计方法,既支持自底向上的设计,又支持自顶向下的设计;既支持模块化设计,又支持层次化设计。支持广泛、易于修改。由于VHDL已经成为IEEE标准所规范的硬件描述语言,目前大多数EDA工具几乎都支持VHDL,这为VHDL的进一步推广和广泛应用奠定了基础。在硬件电路设计过程中,主要的设计文件是用VHDL编写的源代码,因为VHDL易读和结构化,所以易于修改设计。强大的系统硬件描述能力。VHDL具有多层次的设计描述功能,既可以描

(完整版)基于FPGA的智能交通灯的设计毕业设计

目录 摘要 ............................................................. I 1 前言 (1) 2 交通红绿灯控制电路的发展与技术现状 (2) 2.1 交通控制系统以及交通红绿灯控制电路的发展现状 (2) 2.2 智能交通红绿灯控制电路技术的现状 (3) 3 VHDL、FPGA、Quartus ii简介 (5) 3.1 VHDL简介 (5) 3.1.1 VHDL简介 (5) 3.1.2 VHDL语言的特点 (6) 3.2 FPGA简介 (8) 3.2.1 PLD器件的设计特点 (8) 3.2.2 FPGA的基本结构 (10) 3.2.3 采用FPGA设计逻辑电路的优点 (11) 3.3 Quartus II 的简介 (12) 4 具体方案论证与设计 (13) 4.1 具体方案论证 (13) 4.2系统算法设计 (15) 4.3 具体电路原理图 (16) 4.4 电路仿真图 (16) 5 实验结果 (17) 总结 (18) 参考文献 ......................................... 错误!未定义书签。附录: .. (19)

基于FPGA的十字路口交通信号灯 摘要 本文主要介绍十字路口交通灯控制器的设计。首先,介绍交通控制系统以及交通红绿灯控制电路的发展现状;然后采用硬件描述语言进行的交通灯控制器设计。重点介绍了控制系统各部分的设计,以及各个模块之间的同步处理。为了克服交通信号灯控制系统传统设计方法的弊端,更加适应城镇交通现状,利用VHDL语言、采用层次化混合输入方式,设计了具有3种信号灯和倒计时显示器的交通信号灯控制系统,在 QuartusⅡ下进行仿真,并下载到FPGA中制作成实际的硬件电路进行了模拟运行.使用该方法设计的交通灯控制系统电路简单、运行可靠、易于实现,可实现对交通信号的控制和显示功能。 关键词 FPGA;QUARTUS ii;HDPLD;十字路口交通灯控制器; Based on FPGA intersection traffic lights Abstract This paper describes the design of intersection traffic signal controller.First, the introduction of traffic control systems and traffic light control circuit of the development status; then using language designed for the traffic light controller.Focus on various parts of the control system

基于FPGA的多功能数据选择器设计与实现

基于FPGA的多功能数据选择器设计与实现 章军海201022020671 [摘要]传统的数字系统设计采用搭积木式的方法来进行设计,缺乏设计的灵活性。随着可编程逻辑器件(PLD)的出现,传统设计的缺点得以弥补,基于PLD的数字系统设计具有很好的灵活性,便于电路系统的修改与调试。本文采用自顶向下的层次化设计思想,基于FPGA设计了一种多功能数据选择器,实现了逻辑单元可编程、I/O单元可编程和连线可编程功能,并给出了本设计各个层次的原理图和仿真时序图;本文还基于一定的假设,对本设计的速度和资源占用的性能进行了优化。 [关键词]层次化设计;EDA;自顶向下;最大时延 0引言: 在现代数字系统的设计中,EDA(电子设计自动化)技术已经成为一种普遍的工具。基于EDA技术的设计中,通常有两种设计思想,一种是自顶向下的设计思想,一种是自底向上的设计思想[1]。其中,自顶向下的设计采用层次化设计思想,更加符合人们的思维习惯,也容易使设计者对复杂系统进行合理的划分与不断的优化,因此是目前设计思想的主流。基于层次化设计思想,实现逻辑单元、I/O单元和连线可编程可以提高资源的利用效率,并且可以简化数字系统的调试过程,便于复杂数字系统的设计[2][3]。 1系统原理图构架设计 1.1系统整体设计原理 本设计用于实现数据选择器和数据分配器及其复用的I/O端口和连线的可编程却换,提高系统的资源利用效率。系统顶层原理框图如图1所示,系统拥有两个地址选择端口a0、a1,一个功能选择端口ctr,还有五路I/O复用端口。其中,地址选择端口用于决定数据选择器的数据输入端和数据分配器的数据输出端;功能选择端口用于切换数据选择器和数据分配器,以及相应的I/O端口和连线;I/O复用端口数据的输入和输出,其功能表如表一所示。 图1顶层模块原理图 表一顶层系统功能表

基于FPGA的电子抢答器的程序设计

基于FPGA的电子抢答器的程序设计 摘要 随着科学技术日新月异,文化生活日渐丰富,在各类竞赛、抢答场合电子抢答器已经作为一种工具得到了较为广泛的应用。顾名思义,电子抢答器是一种通过抢答者的指示灯显示、数码显示和警示显示等手段准确、公正、直观地判断出最先获得发言权选手的设备。 此次设计有4组抢答输入,每组设置一个抢答按钮供抢答者使用。电路具有第一抢答信号的鉴别和锁存功能。当第一抢答者按下抢答开关时,该组指示灯亮以示抢答成功。同时,电路也具备自锁功能,保证能够实现在一路成功抢答有效后,其他三路均不能抢答。本设计基于VHDL语言,采用FPGA为控制核心,并结合动手实践完成,具有电路简单、操作方便、灵敏可靠等优点。该四路抢答器使用VHDL硬件描述语言进行编程,分为七个模块:判断模块,锁存模块,转换模块,扫描模块,片选模块,定时报警模块和译码模块。编程完成后,使用QuartersII工具软件进行编译仿真验证。 关键词:VHDL,FPGA,四路抢答器,仿真

目录 1 概述 (1) 1.1 设计背景 (1) 1.2 抢答器现状 (1) 1.3 本论文主要完成的工作 (1) 1.4 设计心得 (2) 2 开发工具简介 (3) 2.1 VHDL语言简介 (3) 2.2 FPGA开发过程与应用 (4) 2.2.1 FPGA发展历程及现状 (4) 2.2.2 FPGA工作原理 (4) 2.2.3 FPGA开发流程 (5) 2.3 Quartus II软件 (6) 3系统设计 (8) 3.1 系统设计要求 (8) 3.2 系统设计方案 (8) 3.2.1 系统硬件设计方案 (8) 3.2.2 系统软件设计方案 (8) 3.3.3 系统原理详述 (10) 4 电路程序设计及仿真 (12) 4.1 抢答锁存模块设计 (12) 4.1.1 VHDL源程序 (12) 4.1.2 抢答锁存电路的模块 (13) 4.2 仿真 (14) 总结 (15) 致谢 (17) 参考文献 (18)

基于FPGA下的交通灯控制器设计

引言 随着城乡的经济发展,车辆的数量在迅速的增加,交通阻塞的问题已经严重影响了人们的出行。 现在的社会是一个数字化程度相当高的社会,很多的系统设计师都愿意把自己的设计设计成集成电路芯片,芯片可以在实际中方便使用。随着EDA技术的发展,嵌入式通用及标准FPGA器件的呼之欲出,片上系统(SOC)已经近在咫尺。FPGA/CPLD 以其不可替代的地位及伴随而来的极具知识经济特征的IP芯片产业的崛起,正越来越受到业内人士的密切关注。FPGA就是在这样的背景下诞生的,它在数字电路中的地位也越来越高,这样迅速的发展源于它的众多特点。交通等是保障交通道路畅通和安全的重要工具,而控制器是交通灯控制的主要部分,它可以通过很多种方式来实现。在这许许多多的方法之中,使用FPGA和VHDL语言设计的交通灯控制器,比起其他的方法显得更加灵活、易于改动,并且它的设计周期性更加短。 城市中的交通事故频繁发生,威胁着人们的生命健康和工作生活,交通阻塞问题在延迟出行时间的同时,还会造成更多的空气污染和噪声污染。在这种情况下,根据每个道路的实际情况来设置交通灯,使道路更加通畅,这对构建和谐畅通的城市交通有着十分重要的意义。

第一章软件介绍 1.1 QuartusⅡ介绍 本次毕业设计是基于FPGA下的设计,FPGA是现场可编程门阵列,FPGA开发工具种类很多、智能化高、功能非常的强大。可编程QuartusⅡ是一个为逻辑器件编程提供编程环境的软件,它能够支持VHDL、Verilog HDL语言的设计。在该软件环境下,设计者可以实现程序的编写、编译、仿真、图形设计、图形的仿真等许许多多的功能。在做交通灯控制器设计时选择的编程语言是VHDL语言。 在这里简单的介绍一下QuartusⅡ的基本部分。图1-1-1是一幅启动界面的图片。在设计前需要对软件进行初步的了解,在图中已经明显的标出了每一部分的名称。 图 1-1-1 启动界面 开始设计前我们需要新建一个工程,首先要在启动界面上的菜单栏中找到File,单击它选择它下拉菜单中的“New Project Wizard”时会出现图1-1-2所显示的对话框,把项目名称按照需要填好后单击Next,便会进入图 1-1-3 显示的界面。

基于FPGA的脉冲发生器的设计

【基础?应用】 基于FP GA 的脉冲发生器的设计 ① 张 涛 (北方交通大学电子信息工程学院,北京100044)【摘 要】 以脉冲发生器为研究对象,介绍了脉冲发生器的基本原理、硬件构成和实现方法,阐述了一种基于DSP -FP G A 数字系统的PWM 控制脉冲生成方法,并给出了仿真及实测实验结果。 【关键词】 脉宽调制;脉冲发生器;可编程门阵列 1 FP G A 简介 FP G A (Field Programmable G ate Array ,可编程门阵列)是美国Xinlinx 公司推出的一种采用单元型结构的新型PLD 器件。它采用CMOS 、SRAM 工艺制作,在结构上与阵列型PLD 不同,它的内部由许多独立的可编程逻辑单元构成,各逻辑单元之间可以灵活地相互连接,具有密度高、速度快、编程灵活和可重新配置等诸多优点。FP G A 已成为当前主流的PLD 器件之一。 1.1 PLD 的主要特点 (1)缩短研制周期。 (2)降低设计成本。用PLD 来设计和改造电子产品可以大幅度地减少印制板的面积和接插件,降低装配和调试费用。 (3)提高设计灵活性和可靠性。大量分立式元器件在向印制板上装配时,往往会发生由于虚焊或接触率近似于线性增加,且线性斜率较小;肝脏中大小不同的散射源对不同频率的声波存在有不同的散射效应。 由于肝脏组织结构的非均匀性、复杂性及其各部分散射相关长度分布的不一致性,其散射谱随深度增加而衰减变化,并非完全呈线性关系,而呈现较复杂的关系变化。 ⑵肝叶边缘部分及表层区域,其结构散射近似呈瑞利散射特征;肝叶表层以下与肝叶中心之间的中间区域,其结构散射呈随机散射特征;肝叶中心区域,其结构散射呈扩散漫射特征,也有较强的反射。 ⑶利用区域结构散射特征谱,不仅可对各特征区域组织微结构作出粗略估计,而且可通过区域散射谱特征的变化,对生物软组织的生理病理变化的判断提供依据。 综上所述,利用超声散射谱分析,可为B 超的形态学图像信息诊断提供一个组织特征的信息,在临床上是有应用前景的。 参考文献 [1]Luigi Landini et al.IEEE Trans on U FFC.1990,37(5):448-456 [2]陈启敏等.声学学报.1995,Vol.21,No.4:692-699 [3]E.J.Feleppa ,et al.IEEE Annual International Conference ,EMB ,1990;12(1):337 (责任编辑:常 平) 2003年4月第19卷第2期 武警工程学院学报JOURNAL OF EN GG COLL EGE OF ARMED POL ICE FORCE Apr.2003Vol.19No.2 ①收稿日期:2002-12-06作者简介:张涛(1968.07-),1994年毕业于西安交通大学工业电器自动化专业,现在北方交通大学电子信息工程学院电子与信息工程专业攻读硕士学位。

FPGA四路电子抢答器设计

课程设计报告 专业班级 课程 FPGA/CPLD原理及应用题目四路电子抢答器设计学号 姓名 同组人 成绩 2013年5月

一、设计目的 1.进一步掌握QUARTUSⅡ软件的使用方法; 2.会使用VHDL语言设计小型数字电路系统; 3.掌握应用QUARTUSⅡ软件设计电路的流程; 4.掌握电子抢答器的设计方法。 二、设计要求 1.系统总体设计 (1)设计一个可以容纳四组参赛队进行比赛的电子抢答器。 (2)具有第一抢答信号的鉴别和锁存功能。在主持人发出抢答指令后,若有参赛者按抢答器按钮,则该组指示灯亮,显示器显示出抢答者的组别。同时,电路处于自锁存状态,使其他组的抢答器按钮不起作用。 (3)具有计时功能。在初始状态时,主持人可以设置答题时间的初始值。在主持人对抢答组别进行确认,并给出倒计时记数开始信号以后,抢答者开始回答问题。此时,显示器从初始值开始倒计时,计到0时停止计数,同时扬声器发出超时警报信号。若参赛者在规定的时间内回答完问题,主持人可以给出计时停止信号,以免扬声器鸣叫。 (4)具有计分功能。在初始状态时,主持人可以给每组设置初始分值。每组抢答完毕后,由主持人打分,答对一次加1分,答错一次减1分。 (5)设置一个系统清除开关,该开关由主持人控制。 (6)具有犯规设置电路。超时抢答者,给予鸣喇叭警示,并显示规范组别。 2.设计方案 系统的输入信号有:各组的抢答按钮A、B、C、D,系统允许抢答信号STA,系统清零信号RST,计分时钟信号CLK,加分按钮端ADD、en,减分端SUB、sta,计时使能端en时钟信号clk,复位rst;系统的输出信号有:四个组抢答成功与否的指示灯控制信号输出口可用a1、b1、c1、d1表示,四个组抢答时的计时数码显示控制信号,抢答成功组别显示的控制信号,各组计分显示的控制信号。整个系统至少有三个主要模块:抢答鉴别模块;抢答计时模块;抢答计分模块,其他功能模块(输出显示模块)。 3.如图为流程图: 开始→抢答→抢答鉴别→回答→加减分数→显示↑↑ 倒计时倒计时 犯规抢答或抢答后答题时间超时鸣喇叭警告。

推荐-基于FPGA的计数器的程序设设计 精品

郑州轻工业学院 电子技术课程设计 题目 _基于FPGA的计数器设计___ _________________________ 学生姓名 _ XXX_________________ 专业班级 _电子信息工程10-01班____ 学号 _5401001030XXX__________ 院(系)电气信息工程学院___ ____ 指导教师 _杜海明耿鑫____________ 完成时间20XX年06月22日_______

郑州轻工业学院 课程设计任务书 题目基于FPGA的计数器的程序设设计_______________ 专业、班级电子信息工程学号姓名 _____ 主要内容、基本要求、主要参考资料等: 主要内容: 要求学生使用硬件描述语言(Verilog 或者VHDL)设计基于FPGA的计数器的 源程序。实现如下功能:显示1个0-9999的四位计数器;四位七段数码管的译码与 显示。理解数码管的译码原理,同时需要做一个分频器,理解时钟分频的原理及意 义。 基本要求: 1、学会quartusII的使用,掌握FPGA 的程序设计方法。 2、掌握硬件描述语言语法。 3、程序设计完成后要求在quartusII中实现功能仿真。 主要参考资料: 1、. [M]..20XX,4 2、陈怀琛.MATLAB及在电子信息课程中的应用[M].北京:电子工业出版 社.20XX,1 完成期限:20XX.6.21—20XX.6.25 指导教师签名: ________________ 课程负责人签名: ___________________ 20XX年6月18日

目录

基于FPGA的计数器的程序设设计 摘要 本文介绍了一种基于FPGA的,由顶层到底层设计的数字频率计。本文主要包括该频率计的设计基础和实现方法以及译码与显示等内容,描述了它的设计平台、工作原理和软硬件实现。本设计主要有分频器、四位计数器、16位锁存器以及数码管显示电路。计数器设计采用VHDL硬件描述语言编程,极大地减少了硬件资源的占用,仿真与分析结果表明,该数字频率计性能优异,软件设计语言灵活,硬件简单,速度快。 关键词FPGA 计数器 VHDL

通过Verilog实现交通灯设计实验报告

电子科技大学 实 验 报 告 一、实验室名称:虚拟仪器实验室 二、实验项目名称:交通灯设计实验 三、实验学时:4学时 四、实验原理

假设交通灯处于南北和东西两条大街的“十”字路口,如图1所示。用FPGA 开发板的LED 灯来模拟红、黄、绿3种颜色信号,并按一定顺序、时延来点亮LED ,如图2所示。图3给出了交通灯的状态转移图。设计使用频率为1Hz 的时钟来驱动电路(注1:仿真时采用1MHz 的时钟来驱动电路),则停留1个时钟可得到1S 的延时,类似停留3个时钟可得到3S 的延时,停留15个时钟可得到15S 的延时(注2:开发板工作时钟为50MHz )。 北 南 西东 图1. 六个彩色LED 可以表示一组交通信号灯 图2. 交通灯状态 南北 东西 红 黄 绿 红 黄 绿 S0 1 0 0 0 0 1 S1 1 0 0 0 1 0 S2 1 0 0 1 0 0 S3 0 0 1 1 0 0 S4 0 1 0 1 0 0 S5 1 0 0 1 0 0

图3. 交通灯的状态转移图 顶层模块 时钟分频模块状态机跳转模块 图4. 交通灯的原理框图 五、实验目的 本实验是有限状态机的典型综合实验,掌握如何使用状态转移图来定义Mealy状态机和Moore状态机,熟悉利用HDL代码输入方式进行电路的设计和仿真的流程,掌握Verilog语言的基本语法。并通过一个交通灯的设计掌握利用EDA软件(Xilinx ISE 13.2)进行HDL代码输入方式的电子线路设计与仿真的详细流程。。 六、实验内容 在Xilinx ISE 13.2上完成交通灯设计,输入设计文件,生成二进制码流文件下载到FPGA开发板上进行验证。 七、实验器材(设备、元器件)

基于FPGA的模拟IIC接口设计与实现

研究生课程论文 课程名称基于FPGA的模拟IIC接口设计与实现授课学期2012 学年至2013 学年第一学期学院电子工程学院 专业电子与通信工程 学号2012011603 姓名 任课教师 交稿日期2013.01.10 成绩 阅读教师签名 日期 广西师范大学研究生学院制

基于FPGA的模拟I2C接口设计与实现 摘要:本文论述了I2C总线的基本协议,以及基于FPGA 的模拟I2C 总线接口模块的设计,在QuartusII软件中用Verilog HDL语言编写了部分I2C总线接口功能的程序代码,生成原理图模块。并连接好各个模块,进行了时序仿真。最后,下载到FPGA的板运行测试。 关键词:I2C 接口FPGA Verilog 1课题研究意义、现状及应用分析 目前市场上主流的嵌入式设备主要是微处理器、DSP等,但FPGA 以其独有的高抗干扰性、高安全性正在逐步取得开发公司的青睐,在FPGA上开发I2C势在必行。并且利用EDA 工具设计芯片实现系统的功能,已经成为支撑电子设计的通用平台,并逐步向支持系统级的设计方向发展。模块化的设计思想在软件设计过程中越来越被重视。I2C总线是Philips 公司推出的双向两线串行通讯标准,具有接口线少、通讯效率高等特点。因此,基于FPGA的I2C总线设计有着广泛的应用前景。

2课题总体方案设计及功能模块介绍 本设计主要分三大模块,分别是I2C 总线接口模块、按键输入控制模块、数码管显示模块。I2C总线模块集成了I2C协议用于和总线相接EEPROM的通信;按键输入控制模块用于控制I2C模块的页读、页写、字节读、字节写功能;数码管显示模块用于显示通过I2C总线读取EEPROM中的数据。 3I2C接口设计原理 I2C总线最主要的优点是其简单性和有效性。由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。总线的长度可高达25英尺,并且能够以10 Kbps的最大传输速率支持40个组件。I2C总线的另一个优点是,它支持多主控(multimastering),其中任何能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率。 3.1总线的构成 I2C总线是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。在CPU与被控IC之间、IC与IC之间进行双向传送,最高传送速率100kbps。各种被控制电路均并联在这条总线上,但就像电话机一样只有拨通各自的号码才能工作,所以每个电路和模块都

8路抢答器基于fpga解析

基于FPGA的多路数字抢答器的设计 摘要:本文主要介绍了以FPGA为基础的八路数字抢答器的设计,首先对各模块的功能进行分配,此次设计主要有七个模块,依次为分频模块、抢答模块、加减分模块、倒计时模块、设置倒计时模块、蜂鸣器模块和数字显示模块。主持人按下开始键可以实现抢答开始,选手号的显示,加减分模块,积分的显示,积分的重置,并启动倒计时模块;若有选手犯规或者倒计时记到五秒,停止倒计时,开启蜂鸣器,并为进入加减分模块做准备。此次设计程序用Quartus II12.0为软件开发平台,用Verilog语言来编写,使用模块化编程思想,自上向下,通过寄存器变量来控制各个模块的运行。本次设计采用FPGA来增强时序的灵活性,由于FPGA的I/O端口资源丰富,可以在此基础上稍加修改可以增加很多其他功能的抢答器,因此后期可塑性很强,因为核心是FPGA芯片,外围电路比较简单,可靠性强、运算速度高,因此便于维护,并且维护费用低。 关键词:FPGA、抢答器、倒计时、犯规报警、加减分、显示 目录 第一章绪论................. . (2) 第二章 FPGA原理及相关开发工具软件的介绍 (3) 2.1 FPGA的简介..... . (3) 2.1.1 FPGA的发展与趋势......... .. (3) 2.1.2 FPGA的工作原理及基本特点 (4) 2.1.3 FPGA的开发流程 (5) 2.1.4 FPGA的配置... . (5) 2.2 软件介绍............... .. (6) 2.2.1 Verilog HDL的介绍........... .. (6)

2.2.2 Quartus II软件.................... .. (7) 第三章数字抢答器系统设计方案和主要模块 (8) 3.1 功能描述及设计架构...... .. (8) 3.2 抢答器程序流程图以及各模块代码分析 (10) 3.2.1 抢答器程序结构及主程序流程图 (10) 3.2.2 秒分频模块 (15) 3.2.3 倒计时以及倒计时剩5S时报警模块...... 错误!未定义书签。 3.2.4 倒计时显示及倒数计时设置显示模块 (20) 3.2.5 选手号显示及违规报警模块 (26) 3.2.6倒计时设置模块 (30) 3.2.7顶层模块 (35) 3.3 硬件电路 (37) 3.3.1 按键电路图 (38) 3.3.2 数码管显示电路图 (38) 3.3.2 蜂鸣器电路图 (39) 第四章管脚分配及功能 (40) 第五章总结 (41) 参考文献 (418) 第一章绪论 1.1 课题研究背景 随着社会的发展,各种竞赛比赛日益增多,抢答器以它的方便快捷、直观反映首先取得发言权的选手等优点,深受比赛各方的辛睐,市场前景一片大好。另一方面随着电子科技的发展,抢答器的功能以及实现方式也越来越多,产品的可靠性以及准确性也越来越强。能够实现多路抢答器功能的方式有很多种,主要包括前期的数字电路、模拟电路以及数字电路与模拟电路组合的方式,但是这种方

基于fpga的计数器的程序设计

基于FPGA的计数器的程序设计 摘要 本文介绍了一种基于FPGA的,由顶层到底层设计的数字计数器。本文主要包括该计数器的设计基础和实现方法以及译码与显示等内容,描述了它的设计平台、工作原理和软硬件实现。本设计主要有分频器、四位计数器、16位锁存器以及数码管显示电路四个模块组成。计数器各模块设计采用VHDL硬件描述语言编程,极大地减少了硬件资源的占用,仿真与分析结果表明,该数字计数器性能优异,软件设计语言灵活,硬件简单,速度快。 关键词FPGA计数器VHDL分频器

目录 基于FPGA的计数器的程序设计 (1) 摘要 (1) 1 绪论 (3) 1.1 FPGA简介 (3) 1.2硬件描述语言VHDL简介 (3) 1.3开发工具Quartus II简介 (4) 2整体设计方案 (4) 3各功能模块设计及仿真 (5) 3.1分频器的设计 (5) 3.1.1分频器设计原理 (5) 3.1.2源程序及波形仿真 (6) 3.1.3分频器RTL 电路图 (7) 3.2计数器的设计 (7) 3.2.1分频器设计原理 (7) 3.2.2源程序及波形仿真 (8) 3.2.3 RTL 电路图 (11) 3.3锁存器的设计 (11) 3.3.1锁存器设计原理 (11) 3.3.2锁存器源程序及波形仿真 (12) 3.3.3锁存器RTL电路图 (13) 3.4显示部分的设计 (13) 3.4.1七段数码管显示原理 (13) 3.4.2七段数码管显示源程序及波形仿真 (15) 3.4.3七段数码管显示RTL 电路图 (16) 4系统顶层设计 (17) 4.1.1自顶向下的设计方法 (17) 4.1.2 顶层设计源程序及其仿真波形 (17) 4.1.3系统顶层RTL 电路图 (20) 5总结 (21) 参考文献 (22)

基于FPGA的四路抢答器的Verilog-HDL代码

module qiangda4(clk,clr,inputEn,add,stu,inputL1,inputL2,inputL3,inputL4,Led1 ,Led2,Led3,Buzzer); // 开始声明各个端口 //输入口 input clk,clr,inputEn,add,stu,inputL1,inputL2,inputL3,inputL4; //输出口 output [0:7] Led1; //倒计时时使用的LED控制端 output [0:7] Led2; //数码管控制端 output [0:7] Led3; //分数显示数码管控制端 output Buzzer; //蜂鸣器 //各个寄存器变量声明 reg [0:7] Led1; reg [0:7] Led2; reg [0:7] Led3; reg cnt=32'b0; reg Buzzer; reg score=4’hf;//分数显示寄存器 //配置寄存器,EnFlat是表明开始抢答的标志位 reg EnFlat=1'b0; //BuClk是蜂鸣器的标志位 reg BuClk=1'b0; //BuL是做蜂鸣器的延时用 reg [0:7]BuL=8'd0; //抢答选手标志位 reg answer=3’d0; //各组分数标志位 reg score1=4’d5; reg score2=4’d5; reg score3=4’d5; reg score4=4’d5; //------------初始化模块--------------- always @ (posedge clk)//捕捉时钟 begin //初始化各按键并开始抢答 begin if(inputEn==1'b0) begin //初始化各个标志位和参数

基于FPGA的定时器计数器的设计与实现

基于FPGA的定时器/计数器的设计与实现 摘要 本课题旨在用EDA工具与硬件描述语言设计一个基于Altera公司的FPGA 16位计数器\定时器,可对连续和非连续脉冲进行计数,并且计数器在具有计数定时功能基础上,实现简单脉宽调制功能和捕获比较功能。本设计采用QuartusII编译开发工具使用VerilogHDL 设计语言进行设计,并采用了由上而下的设计方法对计数器进行设计,体现了VerilogHDL 在系统级设计上自上而下设计风格的优点。本设计中采用了三总线的设计方案,使设计更加简洁与规范。本设计所有模块与功能均在Quartus II 7.0_1.4G_Liwz版本下通过编译与仿真,实现了定时器/计数器的设计功能。 关键词:VerilogHDL硬件描述语言;QuartusII;FPGA;定时器/计数器

FPGA-based timer / counter design and implementation This topic aims to use EDA tools to design a 16 bit counter \ timer based on Altera's FPGA by hardware descripe language, which can count continuous and discontinuous pulset, and the counter with the function of capture and PWM. This design uses VerilogHDL language and top-down design method to design the counter on QuartusII compile tool, the design reflect the advantages of VerilogHDL top-down design in system-level design. The design uses a three-bus design, which make design much more specifications and concise. The design and function of all modules are compiled and simulationed on the Quartus II 7.0_1.4G_Liwz versions, and achieve the timer / counter’s features. Key words: VerilogHDL hardware description language; QuartusII; FPGA; timer / counter

基于fpga的eeprom设计

二线制I2C CMOS 串行EEPROM 的FPGA设计 姓名:钱大成 学号:080230114 院系:物理院电子系 2011年1月1日

一、课程设计摘要: (1)背景知识: A、基本介绍: 二线制I2C CMOS 串行EEPROM AT24C02/4/8/16 是一种采用CMOS 工艺制成的串行可用电擦除可编程只读存储器。 B、I2C (Inter Integrated Circuit)总线特征介绍: I2C 双向二线制串行总线协议定义如下: 只有在总线处于“非忙”状态时,数据传输才能被初始化。在数据传输期间,只要时钟线为高电平,数据线都必须保持稳定,否则数据线上的任何变化都被当作“启动”或“停止”信号。图1 是被定义的总线状态。· ①总线非忙状态(A 段) 数据线SDA 和时钟线 SCL 都保持高电平。 ②启动数据传输(B 段) 当时钟线(SCL)为高电平状态时,数据线(SDA)由高电平变为低电平的下降沿被认为是“启动”信号。只有出现“启动”信号后,其它的命令才有效。

③停止数据传输(C 段) 当时钟线(SCL)为高电平状态时,数据线(SDA)由低电平变为高电平的上升沿被认为是“停止”信号。随着“停在”信号出现,所有的外部操作都结束。 ④数据有效(D 段) 在出现“启动”信号以后,在时钟线(SCL)为高电平状态时数据线是稳定的,这时数据线的状态就要传送的数据。数据线(SDA)上的数据的改变必须在时钟线为低电平期间完成,每位数据占用一个时钟脉冲。每个数传输都是由“启动”信号开始,结束于“停止”信号。 ⑤应答信号 每个正在接收数据的EEPROM 在接到一个字节的数据后,通常需要发出一个应答信号。而每个正在发送数据的EEPROM 在发出一个字节的数据后,通常需要接收一个应答信号。EEPROM 读写控制器必须产生一个与这个应答位相联系的额外的时钟脉冲。在EEPROM 的读操作中,EEPROM 读写控制器对EEPROM 完成的最后一个字节不产生应答位,但是应该给EEPROM 一个结束信号。 C、3. 二线制I2C CMOS 串行EEPROM读写操作 ① EEPROM 的写操作(字节编程方式) 所谓EEPROM 的写操作(字节编程方式)就是通过读写控制器把一个字节数据发送到EEPROM 中指定地址的存储单元。其过程如下:EEPROM 读写控制器发出“启动”信号后,紧跟着送4 位I2C 总线器件特征编码1010 和3 位EEPROM 芯片地址/页地址XXX 以及写状态的R/W 位(=0),到总线上。这一字节表示在接收到被寻址的EEPROM 产生的一个应答位后,读写控制器将跟着发

简易四路抢答器

单片机课程设计 预习报告 班级:建电141 姓名:付鹏鑫 学号:1412032031 设计题目:四位竞赛抢答器系统设计设计时间:2016.01.03~01.07 评定成绩: 评定教师:

目录 摘要 -------------------------------------------------------------------- 错误!未定义书签。 一、任务分析: -------------------------------------------------------------------------------- 3 二、总体方案: -------------------------------------------------------------------------------- 4 2.1 可行方案--------------------------------------------------- 错误!未定义书签。 2.2 方案设计--------------------------------------------------- 错误!未定义书签。 三、硬件设计: -------------------------------------------------------------------------------- 8 3.1 电路原理图 --------------------------------------------------------------------------- 8 1.AT89C51简介 ------------------------------------------------------------------------ 10 2.PCF8591简介 --------------------------------------------------------------------------- 9 3.RESPACK8及RX8简介 (12) 3.2 器件选择--------------------------------------------------- 错误!未定义书签。 四、软件设计: ---------------------------------------------------- 错误!未定义书签。 4.1程序处理流程 --------------------------------------------- 错误!未定义书签。 4.2 程序流程图 ----------------------------------------------- 错误!未定义书签。 4.3 程序介绍--------------------------------------------------- 错误!未定义书签。 五、调试过程: ------------------------------------------------------------------------------ 22 5.1 调试步骤----------------------------------------------------------------------------- 22 六、参考文献: ---------------------------------------------------- 错误!未定义书签。 错误!未定义书签。 摘要:抢答器作为一种工具,已广泛应用于各自智力与知识竞赛场合。本设计是基于C52单片机系统的四路抢答器。考虑到其限时回答功能,

基于FPGA的交通灯课程设计报告

总体设计要求和技术要点 1.任务及要求 (1)设计一个交通信号灯控制器,由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外。 (2)红、绿、黄发光二极管作信号灯,用传感器或逻辑开关作检测车辆是否到来的信号。 (3)主干道处于常允许通行的状态,支干道有车来时才允许通行。主干道亮绿灯时,支干道亮红灯;支干道亮绿灯时,主干道亮红灯。 (4)主、支干道均有车时,两者交替允许通行,主干道每次放行45秒,支干道每次放行25秒,设立45秒、25秒计时、显示电路。 (5)在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,使行驶中的车辆有时间停到禁行线外,设立5秒计时、显示电路。 (6)按《湖南涉外经济学院课程设计管理办法》要求提交课程设计报告。 工作内容及时间进度安排 第17周:周1---周2 :立题、论证方案设计 周3---周5 :程序设计与调试 第18周:周1---周3 :硬件调试与测试、撰写课程设计报告 周4---周5 :验收答辩 课程设计成果 1.与设计内容对应的软件程序 2.课程设计总结报告

摘要 本实验为自主选题设计实验,实验选择具有倒计时显示功能的红黄绿三色交通设计,实验中采用VHDL 作为设计功能描述语言,选用Altera公司的EP1K30144-PIN TQFP最为主控芯片,实验报告中简要介绍了FPGA器件,并给出了设计原理图,详细的介绍了交通灯的设计流程,实验报告中还附有实验代码实验结果照片图。 Abstract This experiment designed for independent choice experiment, experiment choice which has the function of the countdown display red yellow green traffic design, description language (VHDL as design function is applied in the experiments, the most main control chip select MAX II EPM240T100C5 Altera company, experiment report, this paper briefly introduces the MAX II device series, and gives the design diagram, detailed introduces the traffic lights of the design process, the experiment report with the code results photo graph.

基于FPGA芯片的最小系统设计

黑龙江大学本科生 毕业论文(设计)档案编码: 学院:电子工程学院 专业:电子信息工程 年级:2007 学生姓名:王国凯 毕业论文题目:基于FPGA 的电梯自动控制 系统设计

摘要 本文在介绍了在当前国内外信息技术高速发展的今天,电子系统数字化已成为有目共睹的趋势。从传统的应用中小规模芯片构成电路系统到广泛地应用单片机,直至今天FPGA 在系统设计中的应用,电子设计技术已迈人了一个全新的阶段。FPGA 利用它的现场可编程特性,将原来的电路板级产品集成为芯片级产品,缩小体积,缩短系统研制周期,方便系统升级,具有容量大、逻辑功能强,提高系统的稳定性,而且兼有高速、高可靠性。越来越多的电子设计人员使用芯片进行电子系统的设计,通过基于FPGA 电梯系统开发设计,说明了FAPG 芯片研究的动机和研究意义。 关键词 FPGA;电梯系统;FLEX10K;JTAG;模块设计

Ab s t ract This paper introduces the rapid development of information technology around the world today. Digitalized electronic systems have become the trend. From the traditional application of small and medium-chip circuitry to Microcontroller and FPGA application in system design, electronic design technology is stepping into a new field. By using its field programmable features, FPGA changes the original circuit board-level products to the chip-level integration products. Now FPGA has advantages of reduced the size, shorten development cycle, facilitated in system upgrades, highly capacity, strong logic functions, stable system and high speed. More and more electronic designers use FPGA to design electronic systems. This paper shows the motivation and significance of designing by FPGA through the elevator FPGA system design. Ke ywo r d FPGA; Mini-System; FLEX10K; JTAG;Module design