一种快速位同步时钟提取方案及实现

一种快速位同步时钟提取方案及实现

[作者:靖文李斌屈薇宋开鑫转贴自:电子设计应用点击数: 120 更新时间:2007-12-20

【字体: A 】

摘要:本文比较了两种常用位同步提取电路的优缺点,在此基础上提出了一种基于CPLD/FPGA、用于数字通信系统的新型快速位同步方案。此方案借助Altera的设计工具设计了位同步提取电路,并利用FPGA予以实现,同时给出了该电路的仿真试验波形图。

关键词:CPLD/FPGA;位同步;VHDL;通信系统

引言

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时钟信号不仅用于监测输入码元信号,确保收发同步,而且在获取祯同步、群同步及对接收的数字码元进行各种处理的过程中,也为系统提供了一个基准的同步时钟。

随着可编程器件容量的增加,设计师倾向于把位同步电路设计在CPLD/FPGA芯片内部。因此,本文采用Quartus II软件设计了一种新型的位同步提取电路,对电路进行了仿真试验,并使用Altera 的Cyclone II系列FPGA芯片EP2C5予以实现。

在CPLD/FPGA上实现位同步,最简单直接的办法就是利用FPGA的片上锁相环。但这种锁相环要求的输入时钟范围是10MHz~100MHz,它对于低速数据显得无能为力。而且,对于中低档FPGA来说,锁相环是稀缺资源,很多时候被用作系统时钟锁相。CPLD片上则没有锁相环,大部分应用都需要设计师自己设计位同步电路。

两种位同步提取电路性能分析

目前在CPLD/FPGA上常用的位同步方案可分为两类:一是采用锁相环的闭环相位调整电路,二是采用开环结构的位同步电路。下面用两个典型的设计电路来讨论这两种方案的优缺点。

基于超前滞后型锁相环的位同步提取电路

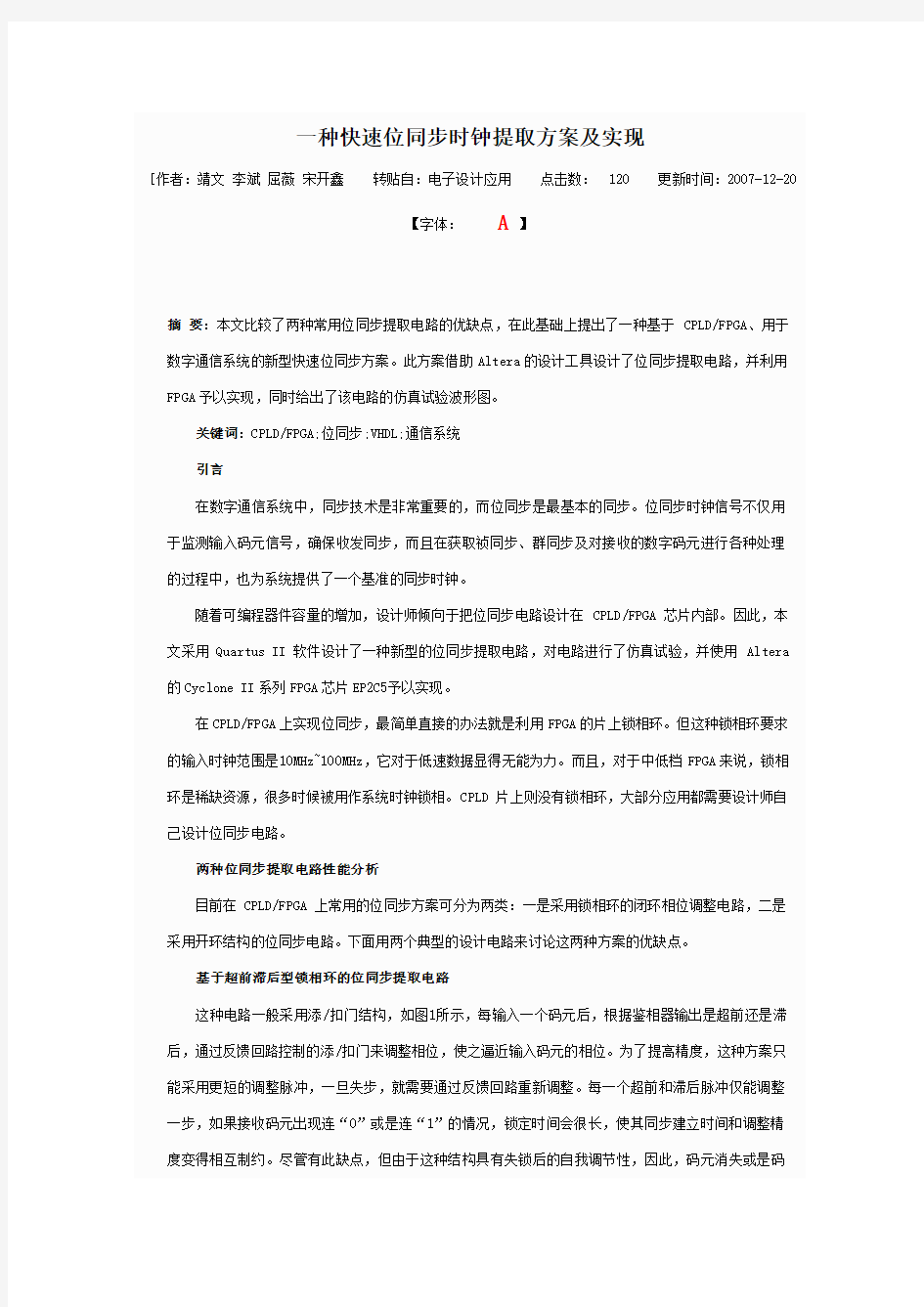

这种电路一般采用添/扣门结构,如图1所示,每输入一个码元后,根据鉴相器输出是超前还是滞后,通过反馈回路控制的添/扣门来调整相位,使之逼近输入码元的相位。为了提高精度,这种方案只能采用更短的调整脉冲,一旦失步,就需要通过反馈回路重新调整。每一个超前和滞后脉冲仅能调整一步,如果接收码元出现连“0”或是连“1”的情况,锁定时间会很长,使其同步建立时间和调整精度变得相互制约。尽管有此缺点,但由于这种结构具有失锁后的自我调节性,因此,码元消失或是码

元相位出现抖动时,同步脉冲不会出现较大变化,仍然可以输出稳定的同步脉冲。

图1 数字锁相环法位同步提取原理框图

采用开环结构的快速位同步电路

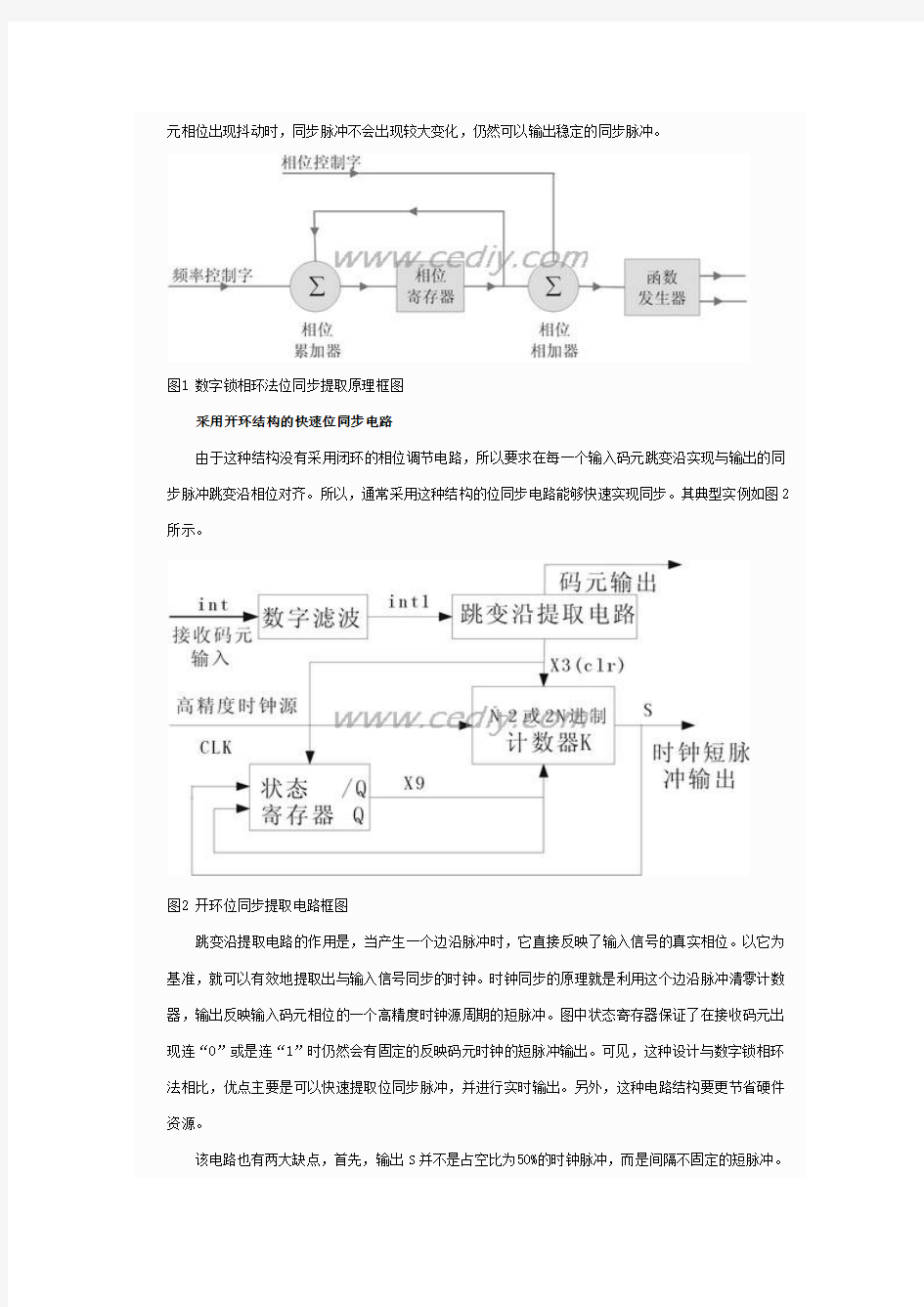

由于这种结构没有采用闭环的相位调节电路,所以要求在每一个输入码元跳变沿实现与输出的同步脉冲跳变沿相位对齐。所以,通常采用这种结构的位同步电路能够快速实现同步。其典型实例如图2所示。

图2 开环位同步提取电路框图

跳变沿提取电路的作用是,当产生一个边沿脉冲时,它直接反映了输入信号的真实相位。以它为基准,就可以有效地提取出与输入信号同步的时钟。时钟同步的原理就是利用这个边沿脉冲清零计数器,输出反映输入码元相位的一个高精度时钟源周期的短脉冲。图中状态寄存器保证了在接收码元出现连“0”或是连“1”时仍然会有固定的反映码元时钟的短脉冲输出。可见,这种设计与数字锁相环法相比,优点主要是可以快速提取位同步脉冲,并进行实时输出。另外,这种电路结构要更节省硬件资源。

该电路也有两大缺点,首先,输出S并不是占空比为50%的时钟脉冲,而是间隔不固定的短脉冲。

此缺点可以通过增加一个时钟整形电路来解决。第二个缺点是,由于跳变沿提取电路的输出X3(clr)具有对计数器清零的作用,如果跳变沿出现抖动的话,这种跳变沿会和计数器原先的输出产生冲突,造成输出时钟信号占空比大幅度变化,严重时会出现毛刺。这对后续电路功能的实现无疑会产生致命的影响,很可能导致设计失败。

新型快速位同步提取方案

综合以上两种设计的优缺点,本文提出了一种新型的设计方案,其原理框图如图3所示。该方案实现位同步的基本原理是利用输入码元的跳变沿脉冲作为计数器的清零输入信号,这里高精度时钟的频率为F,码元速率为f,取F=2Nf=2N/T(T为输入的不归零码元的宽度)。原理图中的计数器为N进制自动增加计数器。当输入清零信号后,计数器输出翻转。当输入码元出现连“0”或是连“1”时,一个码元的长度为2NT。由于计数器为N进制,计数器的计数值回到0时,计数器的输出仍然翻转,占空比为:NT/2NT=50%。这样就保证了一个输入码元的宽度对应了占空比为50%的时钟信号,即实现了输入码元与计数器输出CLKOUT时钟的同步。

图3中数字滤波器的作用是将输入码元中的窄脉冲干扰滤除掉,这部分电路较简单,在此不作介绍。跳变沿提取电路的作用仍然是提取码元的跳变沿,这部分作用和实现原理与图2介绍的方法相同。其中,跳变沿提取电路如图4所示。

图3 新型位同步提取电路框图

图4 码元跳变沿脉冲产生电路

固定延迟单元的作用是,将经过跳变沿提取电路之后的码元信号进行固定时钟周期的延迟,使之与计数器的输出同相,从而达到位同步。

本设计的关键点是带清零抖动判断的N进制计数器的设计。当计数器清零输入没有抖动,而严格按照t=n×2NT时间出现时(当出现连“1”或是连“0”时,式中n>1,否则n = 1),计数器计到“0”和清零脉冲同时生效,计数器输出翻转,这时的输出时钟是稳定的。计数器的清零输入信号是由码元的边沿脉冲提供的,所谓清零抖动实际上就是输入码元的边沿位置出现抖动,这是符合实际情况的,因为信号的传输路径上不可避免地会产生衰减,并受到干扰,发送方的数据发送时钟也有可能存在抖动。下面讨论这种抖动对N进制计数器输出产生的影响:

1.当输入的不归零码元的跳变沿出现的时间略小于2NT的整数倍时,称之为前向抖动。此时计数器的清零脉冲出现在计数器还没有计数到“0”的某个计数值的位置,比如当计数器计到N-1时,清零脉冲出现,于是计数器被清零脉冲清零,同时输出脉冲翻转。这种情况会使输出的时钟脉冲比估计的翻转时间提前aT=(0+N-(N-1)+1)T=2T,这对时钟输出不会产生不利影响。而且,时钟的翻转时间实时反映出码元的变化,有利于后续电路功能的实现。

2.当输入的不归零码元的跳变沿出现的时间略大于2NT的整数倍时,称之为后向抖动。此时计数器的清零脉冲出现在计数器计数到“0”之后的某个计数值的位置,比如当计数值为2时,清零脉冲出现。现在来看计数器的输出,首先当计数器计到“0”前,计数器输出一直维持在“0”;计数器计到“0”后,计数器输出自动翻转为“1”,然后继续计数;当计数值为2时,清零脉冲出现,于是计数器被清零脉冲清零,同时输出脉冲翻转为“0”,计数器输出就会出现持续时间为bT=(2-0)T=2T的窄脉冲。当接收电路的时钟里出现这种不可预测的窄脉冲时,接收电路位同步之后的后续电路的功能也就无法正常实现了,这也就是本文刚开始讨论的采用开环结构的快速位同步电路的缺点。

本文的设计方案中所采用的计数器是利用VHDL语言设计的、带清零抖动判断功能的计数器。具体来说,它可以判断清零抖动为前向抖动还是后向抖动。如果是后者,则忽略此次清零脉冲,同时将此之后的某个计数值减去b,这样做的目的是防止这种抖动带来的影响出现累加。依照以上分析及处理办法,可以设计出带有清零抖动判断功能的计数器。

a:process(clk,clr) begin

if clk'event and clk='1' then

if clr='1' and count>c then count<=0;

elsif clr='1' and count=0 then count<=1; zero<='1';

elsif clr='1' and count>0 and count<=c then temp<=count;

elsif count=N/2 then

if zero='1' then count<=N/2; zero<='0';

elsif temp=0 then count<=count+1;

else count<=N/2-temp+1; temp<=0;

end if;

else count<=count + 1;

end if;

end if;

end process a;

b:process(clk,clkout) begin

if clk'event and clk='1' then

if count=0 then clkout<= not clkout;

end if;

end if;

end process b;

程序中count为当前时刻的计数值,当清零信号有效时,首先进行0c。这样可以在码元跳边沿之间的计数值凑够N的整数倍,避免了这种抖动带来的影响出现累加。程序中对清零信号有效且n=0的情况作了特殊考虑。

本设计方案在Altera的Cyclone II系列FPGA芯片EP2C5上进行了实现,在Quartus II环境下,用VHDL硬件描述语言和电路图输入混合设计的方法,完成了整个时钟提取电路的设计,其仿真结果如图5所示。仿真中采用的CLK频率为10MHz,参数取值为N=32、c=4。仿真图中各输入输出标号与图3中标号对应。

图5 仿真波形

位同步时钟提取电路的性能

将广泛采用的锁相环路法(模拟锁相环和数字锁相环)和本文设计的开环位同步法相比较,本方案有如下优点:

1.本设计基于开环结构,具备了开环结构位同步提取电路的快速同步特点。如果输入不出现较大的相位抖动,输出时钟的相位可以实时地反映输入码元的相位。

2.由于具有判断输入码元脉冲边沿抖动的功能,因此也具有锁相环的自适应性。由以上分析可知,当输入码元出现抖动而使得输出时钟没有和码元对齐之后,下一个码元跳变沿就会重新对齐。这种自适应性比锁相环的自适应反应更迅速。

3.本设计可支持的系统时钟clk可以达到181MHz,支持的输入码元速率最大为(181/N)MHz,可以支持大部分的数字通信应用。

4.本设计结构简单,这种办法比锁相环法更节省LE资源。当N=32、c=4时,使用EP2C5Q208C8器件,位同步提取电路所消耗的LE数目仅为26个。

结语

实现位同步的方法很多,本文讨论的是一种提取位同步信号的新型设计方案。该设计在Quartus II 下调试通过并在实践中得到应用。实践证明这种方法可以用很少的FPGA资源实现位同步的目的,并具有很高的稳定性和可靠性。

参考文献:

1. 段吉海,黄志伟,王毓银. 基于CPLD/FPGA的数字通信系统建模与设计. 2004

2. 陈世伟. 锁相环路原理及应用. 兵器工业出版社, 1990

3. 王兰勋,荣民. 一种位同步时钟提取方案及实现. 工程应用, 2003

网络时钟系统方案

时钟系统 技术方案 烟台北极星高基时间同步技术有限公司 2012 年 3 月 第一部分:时钟系统技术方案 一、时钟系统概述 1. 1 概述 根据办公楼的实际情况,特制定如下施工设计方案: 时钟系统主要由GPS接收装置、中心母钟、二级母钟(中继器)、全功能数 字显示子钟、、传输通道和监测系统计算机组成。 系统中心母钟设在中心机房内,其他楼各设备间设置二级母钟,在各有关场所安装全功能数字显示子钟。 系统中心母钟接收来自GPS的标准时间信号,通过传输通道传给二级母钟,由 二级母钟按标准时间信号指挥子钟统一显示时间;系统中心母钟还通过传输系统将标准时间信号直接传给各个子钟,为楼宇工作人员提供统一的标准时间 二、时钟系统功能 根据本工程对时钟系统的要求,时钟系统的功能规格如下: 时钟系统由GPS校时接收装置(含防雷保护器)、中心母钟、扩容接口箱、二级 母钟、数字式子钟、监控终端(也称监测系统计算机)及传输通道构成。其主要功

能为: 。显示统一的标准时间信息。 。向其它需要统一时间的系统及通信各子系统网管终端提供标准时间信息。 2.1 中心母钟 系统中心母钟设置在控制中心设备室内,主要功能是作为基础主时钟,自动接 收GPS勺标准时间信号,将自身的精度校准,并分配精确时间信号给子钟,二级母钟和其它需要标准时间的设备,并且通过监控计算机对时钟系统的主要设备进行监控。 中心母钟主要由以下几部分组成: 。标准时间信号接收单元 。主备母钟(信号处理单元) 。分路输出接口箱 。电源 中心母钟外观示意图见(附图) 2.1.1 标准时间信号接收单元 标准时间信号接收单元是为了向时间系统提供高精度的时间基准而设置的,用以实现时间系统的无累积误差运行。 在正常情况下,标准时间信号接收单元接收来自GPS的卫星时标信号,经解码、 比对后,经由RS422接口传输给系统中心母钟,以实现对母钟精度的校准。

胸痛中心时钟统一方案

丹阳市人民医院胸痛中心的时间管理方案 一、时钟同步系统 时钟同步系统对于医院系统可以说是一个不可缺少的重要组成部分,其主要作用是为相关医医疗机构工作人员提供一个标准统一的时间信息,同时为各相关单位科室提供统一的标准时间系统同步,从而实现各相关单位及相关设备的时间标准统一。这对医院的服务质量起到了重要的作用。时钟同步系统工作原理是相关责任人手持移动终端接收3G基站时间信息来实现统一;所有相关设备均以此为标准校对,从而实现全系统统一的时间标准。并每周校对一次。 二、计时点及方法 1.发病时间:患者出现胸痛、胸闷、上腹不适等系列症状开始的时间 ·计时方法:主要是通过问诊方式获得 2.呼救时间:首次拨打120呼救或拨打医院急救电话求救 ·计时方法:120记录、本院胸痛中心记录或其他急救机构记录,已接听电话的时刻为准。 3.到达现场时间:院前急救人员、社区医生或其他医疗机构到达现场时间 计时方法:要求院前人员、网络医院、其他医疗机构准确计时 4.首份心电图时间:完成第一份12或18导联心电图的时间 计时方法:开始接触医疗人员到完成第一份心电图最后一个导联记录为准。在完成心电图操作后,应将准确时间记录在心电图上,包括年、月、日、时、分5.确诊STEMl时问:完成首份心电图后,由受过胸痛专科培训的医生或分诊护士确认为STEMI时间;或由我院医师使用胸痛中心微信群诊断为STEMI的时间。 6.抽血时间:首次抽血查Tnl、CKMB等的时间 计时方法:以抽血护士完成标本采集时刻为计时点。 7.开始转运时间:在确诊为ACS并离开现场/医院的时间。 . 计时方法:由转运医护人员在接到病人启动车辆时计时 8. 给药时间:在确定为ACS患者,排除各类用药禁忌症后,给予服用肠溶阿司

基于FPGA的新型位同步时钟提取方案的设计

一种基于FPGA的新型位同步时钟提取方案及实现 摘要: 关键词:位同步,锁相环,FPGA,异步串行码流 1 引言: 同步技术在数字通信系统中,是非常重要的技术。位同步是最基本的同步。位同步时钟信号不仅用于对输入码元信号的监测保证收发同步,而且在对获取祯同步,群同步及对接收的数字码元进行各种处理过程中也为系统提供了一个基准的同步时钟。 随着现代电子技术的发展,数字系统趋于模块化,小型化,芯片华,因此如何实现同步系统的模块化和芯片化是急需解决的问题。 在数字通信中,通常直接从接收到的数字信号中提取位同步信号,这种直接法按其提取同步信号的方式,大致可分为滤波法和锁相法。锁相法是指利用锁相环来提取位同步信号的方法,本设计方案就是基于锁相环的位同步提取方法,能够比较快速地提取位同步时钟,并且设计简单,方便修改参数。采用Quartus II 设计软件对系统进行了仿真试验,并用Altera的Cyclone II系列FPGA芯片Ep2c5予以实现。 2 位同步时钟提取方案的原理 本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两 种 情 况, 如图1和图2所示: 图1 码流滞后于本地时钟△T示意图图2 码流超前于本地时钟△T示意图 从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。用VHDL语言描述为: if (code_in’event and code_in=’1’) then if (code_in and clk)=’1’ then q<=’1’ else q<=’0’ end if end if 程序中输出信号q可作为控制电路的输入信号。 本设计方案的系统框图如图3所示:

时间同步系统在线监测可行性研究报告

附件4 甘肃电网智能调度技术支持系统 时间同步系统在线监测 技术改造(设备大修)项目 可行性研究报告模板项目名称: 项目单位: 编制: 审核: 批准: 编制单位: 设计、勘测证书号:

年月日

1.总论 时间同步系统在线监测功能,将时钟、被授时设备构成闭环,使对时状态可监测,且监测结果可上送,从而将时间同步系统纳入自动化监控系统管理。时间同步系统在线监测的数据来源分为两大类:设备状态自检数据和对时状态测量数据。设备状态自检主要是被监测设备自身基于可预见故障设置的策略,快速侦测自身的故障点。对时状态测量则是从被监测设备外部对其自身不可预见的故障产生的结果进行侦测,这两种方法较为完整的保证了时间同步系统监测的性能和可靠性。 1.1设计依据 2013年4月,国调中心专门下发了〔2013〕82号文《国调中心关于加强电力系统时间同步运行管理工作的通知》 1.2主要设计原则 通过在原系统上建立一套通讯技术及软件来实现系统级的时间同步状态在线监测功能。采用低建设成本、低管理成本、低技术风险的手段,解决当前自动化系统时间同步体系处于开环状态,缺乏反馈,无法获知工作状态紧迫现状,使时钟和被对时设备形成闭环监测,减少因对时错误引起的事件顺序记录无效,甚至导致设备死机等运行事故,并在此前提下尽可能的提高监测性能,减少复杂度。

1.3设计水平年 系统模块使用年限10年。 1.4设计范围及建设规模 智能调度技术支持系统(主站)针对时钟同步检测功能修改主要涉及前置应用,前置应用以104 或476 规约与变电站自动化系进行过乒乓原理对时,根据对时结果来检测各变电站时钟对时的准确性,从而保证全网时钟同步的准确性。同时,以告警直传方式接收变电站时间同步监测结果,包含设备状态自检数据和对时状态测量数据。 1.5主要技术经济指标 1.6经济分析 2.项目必要性 2.1工程概况 智能电网调度技术支持系统及各变电站都以天文时钟作为自己的时间源,正常情况下实现了全网时间的一致。 2.2存在主要问题 近期,电力系统时间同步装置在运行中发现的时钟异常跳变、时钟源切换策略不合理及电磁干扰环境下性能下降等问题,反映出电力系统时间同步在运行管理、技术性能、检验检测管理、在线监测手段及相关标准等方面仍需进一步完善和加强。

数字时钟设计原理

数字时钟设计——原理图一.实验目的 设计一个多功能数字中电路,基本功能为:①准确计时,以数字形式显示分、秒的时间;②分和秒的计时要求为60进位;③校正时间。 二.设计框图和工作原理 由振荡器产生高稳定的高频脉冲信号,作为数字钟的时间基准(系统时钟),再经分频器输出标准秒脉冲信号。秒计数器计满60后向分计数器进位,分计数器计满60后重新开始计时。计数器的输出经译码器送显示器。计时出现误差时可以用校时电路进行校分。 三.设计方案

1.振荡器的设计 振荡器是数字钟的核心。振荡器的稳定度及频率的精确度决定了数字钟计时的准确程度,通常选用石英晶体构成振荡器电路。一般来说,振荡器的频率越高,计时精度越高。 在这里我们选用由集成电路定时器555与RC组成的多谐振荡器。这里选用555构成的多谐振荡器,输出振荡频率v0=1KHz的脉冲,电路参数如下图所示。 2.分频器的设计 选用3片中规模集成电路计数器74LS90可以完成分频功能。因为每片为1/10分频,3片级联则可获得所需要的频率信号,即第1片的Q3端输出频率为100HZ,第2片的Q3端输出为10Hz,第3片的Q3端输出为1Hz。分频电路如下图所示:

3.分秒计数器的设计 分和秒计数器都是模M=60的计数器,其计数规律为:00-01-… -58-59-00…选74LS92作十位计数器,74LS90作个位计数器。再将它们级联组成模数M=60的计数器。分秒计数电路如下: 74LS90的原理图如下: 74LS92的原理图如下: 4.校时电路的设计 当数字钟接通电源或者计时出现误差时,需要校正时间(或称校时)。校时是数字钟应具备的基本功能。一般电子手表都具有时、分、秒等校时功能。为使

网络时钟系统方案

网络时钟系统方案

时钟系统 技术方案 烟台北极星高基时间同步技术有限公司 3月

第一部分:时钟系统技术方案 一、时钟系统概述 1.1概述 根据办公楼的实际情况,特制定如下施工设计方案: 时钟系统主要由GPS接收装置、中心母钟、二级母钟(中继器)、全功能数字显示子钟、、传输通道和监测系统计算机组成。 系统中心母钟设在中心机房内,其它楼各设备间设置二级母钟,在各有关场所安装全功能数字显示子钟。 系统中心母钟接收来自GPS的标准时间信号,经过传输通道传给二级母钟,由二级母钟按标准时间信号指挥子钟统一显示时间;系统中心母钟还经过传输系统将标准时间信号直接传给各个子钟,为楼宇工作人员提供统一的标准时间 二、时钟系统功能 根据本工程对时钟系统的要求,时钟系统的功能规格如下: 时钟系统由GPS校时接收装置(含防雷保护器)、中心母钟、扩容接口箱、二级母钟、数字式子钟、监控终端(也称监测系统计算机)及传输通道构成。其主要功能为: ☉显示统一的标准时间信息。 ☉向其它需要统一时间的系统及通信各子系统网管终端提供标准时间信息。

2.1 中心母钟 系统中心母钟设置在控制中心设备室内,主要功能是作为基础主时钟,自动接收GPS的标准时间信号,将自身的精度校准,并分配精确时间信号给子钟,二级母钟和其它需要标准时间的设备,而且经过监控计算机对时钟系统的主要设备进行监控。 中心母钟主要由以下几部分组成: ☉标准时间信号接收单元 ☉主备母钟(信号处理单元) ☉分路输出接口箱 ☉电源 中心母钟外观示意图见(附图) 2.1.1标准时间信号接收单元 标准时间信号接收单元是为了向时间系统提供高精度的时间基准而设置的,用以实现时间系统的无累积误差运行。 在正常情况下,标准时间信号接收单元接收来自GPS的卫星时标信号,经解码、比对后,经由RS422接口传输给系统中心母钟,以实现对母钟精度的校准。 系统经过信号接收单元不断接收GPS发送的时间码及其相关代码,并对接收到的数据进行分析,判断这些数据是否真实可靠。如果数据可靠即对母钟进行校对。如果数据不可靠便放弃,下次继续接收。 2.1.2主备母钟

GPS时钟同步系统在网络系统中的技术方案

前言 随着计算机和网络通信技术的飞速发展,火电厂热工自动化系统数字化、网络化的时代已经到来。这一方面为各控制和信息系统之间的数据交换、分析和应用提供了更好的平台、另一方面对各种实时和历史数据时间标签的准确性也提出了更高的要求。 使用价格并不昂贵的GPS时钟来统一全厂各种系统的时钟,已是目前火电厂设计中采用的标准做法。电厂内的机组分散控制系统(DCS)、辅助系统可编程控制器(PLC)、厂级监控信息系统(SIS)、电厂管理信息系统(MIS)等的主时钟通过合适的GPS时钟信号接口,得到标准的TOD(年月日时分秒)时间,然后按各自的时钟同步机制,将系统内的从时钟偏差限定在足够小的范围内,从而达到全厂的时钟同步。 一、GPS时钟及输出 1.1 GPS时钟 全球定位系统(Global Positioning System,GPS)由一组美国国防部在1978年开始陆续发射的卫星所组成,共有24颗卫星运行在6个地心轨道平面内,根据时间和地点,地球上可见的卫星数量一直在4颗至11颗之间变化。 GPS时钟是一种接受GPS卫星发射的低功率无线电信号,通过计算得出GPS时间的接受装置。为获得准确的GPS时间,GPS时钟必须先接受到至少4颗GPS 卫星的信号,计算出自己所在的三维位置。在已经得出具体位置后,GPS时钟只要接受到1颗GPS卫星信号就能保证时钟的走时准确性。 作为火电厂的标准时钟,我们对GPS时钟的基本要求是:至少能同时跟踪8颗

卫星,有尽可能短的冷、热启动时间,配有后备电池,有高精度、可灵活配置的时钟输出信号。 1.2 GPS时钟信号输出 目前,电厂用到的GPS时钟输出信号主要有以下三种类型: 1.2.1 1PPS/1PPM输出 此格式时间信号每秒或每分时输出一个脉冲。显然,时钟脉冲输出不含具体时间信息。 1.2.2 IRIG-B输出 IRIG(美国the Inter-Range Instrumentation Group)共有A、B、D、E、G、H几种编码标准(IRIG Standard 200-98)。其中在时钟同步应用中使用最多的是IRIG-B编码,有bc电平偏移(DC码)、1kHz正弦载波调幅(AC码)等格式。IRIG-B 信号每秒输出一帧(1fps),每帧长为一秒。一帧共有100个码元(100pps),每个码元宽10ms,由不同正脉冲宽度的码元来代表二进制0、1和位置标志位(P),见图1.2.2-1。 为便于理解,图1.2.2-2给出了某个IRIG-B时间帧的输出例子。其中的秒、分、时、天(自当年1月1日起天数)用BCD码表示,控制功能码(Control Functions,CF)和标准二进制当天秒数码(Straight Binary Seconds Time of Day,SBS)则以一串二进制“0”填充(CF和SBS可选用,本例未采用)。 1.2.3 RS-232/RS-422/RS-485输出 此时钟输出通过EIA标准串行接口发送一串以ASCII码表示的日期和时间报文,每秒输出一次。时间报文中可插入奇偶校验、时钟状态、诊断信息等。此输出目前无标准格式,下图为一个用17个字节发送标准时间的实例:

TI杯大学生电子设计竞赛题目

2016年T I杯大学生电子设计竞赛 A题:降压型直流开关稳压电源 1.任务 以TI公司的降压控制器LM5117芯片和CSD18532KCSMOS场效应管为核心器件,设计并制作一个降压型直流开关稳压电源。额定输入直流电压为时,额定输出直流电压为,输出电流最大值为。测试电路可参考图1。 图1电源测试连接图 2.要求 (1)额定输入电压下,输出电压偏差:;(10分) (2)额定输入电压下,最大输出电流:;(10分) (3)输出噪声纹波电压峰峰值:;(10分) (4)从满载变到轻载时,负载调整率: ;(10分) (5)变化到17.6V和13.6V,电压调整率: (10分)(6)效率;(15分) (7)具有过流保护功能,动作电流;(10分) (8)电源具有负载识别功能。增加1个2端子端口,端口可外接电阻R(1kΩ-10kΩ)作为负载识别端口,参考图1。电源根据通过测量端口识别电阻R的阻值,确定输出电压,;(10分) (9)尽量减轻电源重量,使电源不含负载的重量。(15分)

(10)设计报告(20分) 3.说明 (1)该开关稳压电源不得采用成品模块制作。 (2)稳压电源若含其它控制、测量电路都只能由端口供电,不得增加其他辅助电源。(3)要求电源输出电压精确稳定,或,作品不参与测试。 2016年TI杯大学生电子设计竞赛题 B题:物品分拣搬送装置 1.任务 在一个以木条(截面不大于3cm×4cm,木质本色)围成的100cm×150cm的A区域内,散落着边长均为4cm的正方体。设计一自动物体搬运系统,能够快速将这些正方体移至指定区域。A区域的颜色为白色,B区域为黑色,C区域为红色。 2.要求 (1)在A区域内任意放置了12只黑色正方体,以最快的速度将这些正方体移送到B区域,完成时间不得超过180秒;(24分) (2)将A区域的12只黑色正方体以最快的速度移送到红色C区域;完成时间不得超过180秒;(26分) (3)A区域12只正方体中有桔黄色与黑色两种颜色,以最快的速度将桔黄色正方

XP系统时间同步解决方案

XP系统时间同步不成功_Windows time服务无法启动解决 同步时间的服务器是:210.72.145.44 xp自带的时间同步服务器老是会连不上,而且时间还会差一秒。 这里就教大家换成中科院国家授时中心的服务器,同步就方便多了。 1.双击右下角的时间。 2.把服务器改成210.72.145.44 3.按同步就可以了,一般不会出错。即使是高峰时期,三次之内闭成功,比美国的服务器好多了。 另外系统默认的时间同步间隔只是7天,我们无法自由选择,使得这个功能在灵活性方面大打折扣。其实,我们也可以通过修改注册表来手动修改它的自动同步间隔。 1. 在“开始”菜单→“运行”项下输入“Regedit”进入注册表编辑器 2. 展开[HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\W32Time\TimeProviders\Nt pClient ] 分支,并双击SpecialPollInterval 键值,将对话框中的“基数栏”选择到“十进制”上 3. 而这时在对话框中显示的数字正是自动对时的间隔(以秒为单位),比如默认的604800就是由7(天)×24(时)×60(分)×60(秒)计算来的,看明白了吧,如果您想让XP以多长时间自动对时,只要按这个公式算出具体的秒数,再填进去就好了。比如我填了3天,就是259200。 Windows time服务用于和Internet同步系统时间,如果时间无法同步有可能是服务没有随系统启动,可以在运行处输入"services.msc"打开服务控制台,找到"windows time"服务设置为自动并启动即可。 如果启动该服务时提示: 错误1058:无法启动服务,原因可能是已被禁用与其相关联的设备没有启动。 原因是windows time服务失效。 修复: 1.运行cmd 进入命令行,然后键入 w32tm /register 正确的响应为:W32Time 成功注册。 如果提示w32tm命令不内部或外部命令……,是因为系统盘下的system32目录不存在w32tm.exe和w32time.dll这两个文件,到网上下载一个或者到其他电脑复制过来放下这个目录下再运行 2.如果上一步正确,在cmd命令行或运行里用net start "windows time" 或net start w32time 启动服务。 如果无法启动Windows Time服务,同时提示:系统提示“错误1083:配置成在该可执行

华东电网时钟统一(同步)系统技术规范标准

华东电网时间同步系统技术规范 Technical Specification for Time Synchronism System of EastChina Electric Power Network 前言 华东电网已初步建成以超高压输电、大机组和自动化为主要特征的现代化大电网。它的运行实行分层控制,设备的运行往往要靠数百公里外的调度员指挥;电网运行瞬息万变,发生事故后更要及时处理,这些都需要统一的时间基准。为保证电网安全、经济运行,各种以计算机技术和通信技术为基础的自动化装置广泛应用,如调度自动化系统、故障录波器、微机继电保护装置、事件顺序记录装置、变电站计算机监控系统、火电厂机组自动控制系统、雷电定位系统等等。这些装置的正常工作和作用的发挥,同样离不开统一的全网时间基准。 自动化装置内部都带有实时时钟,其固有误差难以避免,随着运行时间的增加,积累误差越来越大,会失去正确的时间计量作用,因此,如何对实时时钟实现时间同步,达到全网的时间统一,长期来一直是电力系统追求的目标。目前,这些装置内部的实时时钟一般都带有时间同步接口,可以由某一种与外部输入的时间基准同步或自带高稳定时间基准的标准时钟源,如GPS标准时间同步钟对其实现时间同步,这为建立时间同步系统,实现时间统一,提供了基础。有越来越多的单位已经建立或将要建立这样的时间同步系统。为了规范、指导时间同步系统的管理、设计、安装、测试和运行,特制订《华东电网时间同步系统技术规范》(以下简称《规范》)。 本《规范》根据国内外涉及时间、时间统一技术的有关标准、建议、规范或规约,结合华东电网“统一时钟系统技术研究”的实践和有关时间同步的具体情况制订的。本《规范》的贯彻、实施,对提高华东电网全网时间统一准确度和改进系统运行、管理质量将起推动作用。 本标准由国家电力公司华东公司提出。 本标准由国家电力公司华东公司归口。 本标准由国家电力公司华东公司生产科技部负责起草并解释。 本标准主要起草人:朱缵震陈洪卿宋金安

全厂网络时钟同步方案

全厂网络时钟同步方案 陈银桃,陆卫军,张清,章维 浙江中控技术股份有限公司,浙江杭州,310053 摘要:当前工控领域石化项目如乙烯、炼油日益趋向大型化、一体化和智能化。一个大型石化项目往往集成多套独立系统如DCS、SIS、CCS等,同时要求所有系统使用同一套网络时钟同步系统。本文提供了几种全厂网络时间同步方案,并分析了每个方案的优缺点和适用场合。 关键词:全厂网络时钟同步,SNTP,二级网络时钟同步方案,Private VLAN,ACL,路由,NAT Ways to Implement The Network Time Synchronization In The Plant Chen Yintao Zhejiang SUPCON Co., Ltd., Hangzhou, Zhejiang, 310053 Abstract:The petrochemical projects in the industrial control area run to large, integrative and intelligentized.A large petrochemical project always need to be integrated with many systems like DCS, SIS, CCS and so on .The network of these systems must be independent,while they should use the same network time synchronizer to achieve time synchronization.This article propose several implements of the network time synchronization in the whole plant. Keywords:Network Time Synchronization, NTP, Private VLAN, ACL, Route, NAT. 引言 随着国民经济发展,工控领域也随之蓬勃发展,石化项目如乙烯、炼油等日益趋向大型化、一体化和智能化。大型化体现在项目规模的剧增,典型项目如百万吨乙烯、千万吨炼油。一体化体现在一个大型石化项目往往集成多套系统如DCS、SIS、CCS,这些系统在功能、网络上分别独立,但需要实现全厂统一的时钟同步,以保持全厂所有系统的时钟同步。 普通的网络时钟同步服务器提供的网口较少,一般都在4个以下,同时可支持1-4个网络的系统时钟同步。当需要同步的子系统较多时,则需要配置可同时支持二三十个网络的特殊网络时钟同步服务器。但是在企业建设初期,往往很难准确预计将来的网络发展规模,这就需要事先规划设计

主板时钟电路工作原理

时钟电路工作原理:3.3v电源经过二极管和电感进入分频器后,分频器开始工作,和晶体一起产生振荡,在晶体的两脚均可以看到波形。晶体的两脚之间的阻值在450---700欧之间。在它的两脚各有1V左右的电压,由分频器提供。晶体两脚常生的频率总和是14.318M。 总频(OSC)在分频器出来后送到PCI槽的B16脚和ISA的B30脚。这两脚叫OSC测试脚。也有的还送到南桥,目的是使南桥的频率更加稳定。在总频OSC线上还电容。总频线的对地阻值在450---700欧之间,总频时钟波形幅度一定要大于2V电平。如果开机数码卡上的OSC灯不亮,先查晶体两脚的电压和波形;有电压有波形,在总频线路正常的情况下,为分频器坏;无电压无波形,在分频器电源正常情况下,为分频器坏;有电压无波形,为晶体坏。 没有总频,南、北桥、CPU、CACHE、I/O、内存上就没有频率。有了总频,也不一定有频率。总频一定正常,可以说明晶体和分频器基本上正常,主要是晶体的振荡电路已经完全正常, 反之就不正常。 当总频产生后,分频器开始分频,R2将分频器分过来的频率送到南桥,在南桥处理过后送到P CI槽B8和ISA的B20脚,这两脚叫系统测试脚,这个测试脚可以反映主板上所有的时钟是否正常。系统时钟的波形幅度一定要大于1.5V,这两脚的阻值在450---700欧之间,由南桥提供。 在主板上RESET和CLK者是南桥处理的,在总频正常下,如果RESET和CLK都没有,在南桥电源正常情况下,为南桥坏。主板不开机,RESET不正常,先查总频。在主板上,时钟线 比AD线要粗一些,并带有弯曲。 二、主板时钟芯片电路及时序关系讲解 1、概述 主板时钟芯片电路提供给CPU,主板芯片组和各级总线(CPU总线,AGP总线,PCI总线,ISA总线等)和主板各个接口部分基本工作频率,有了它,电脑才能在CPU控制下,按步就班,协调地完成各项功能工作: 2、石英晶体多谐振荡器 a、解释说明,主板时钟芯片即分频器的原始工作振荡频率,由石英晶体多谐振荡器的谐振频率来产生,提供给分频率一个基准的14.318MHZ的振荡频率,它是一个多谐振荡器的正反馈环电路,也就是说它把输入作为输出,把输出作为输入的反馈频率,象这样一个永无休止的循环自激过程。 b、基本电路部分: c、分频器(时钟芯片)电路部分:分频器基本工作条件;石英晶体多谐振荡器提供14.318MHZ基准频率.;VCC(3.3V)工作电压(依具体时钟芯片而定);V SS接地线(~);滤波电容(对分频器产生的各级频率进行标正微调;分频器产生的各级总线时钟;CPU外部总线时钟频率(CPU CLOCK):66MHZ.100MHZ.133MHZ内存控制管理器总线时钟频率(DIMM):66MHZ.100.133MHZ;AGP总线时钟频率:66MH Z;PCI总线时钟频率:33MHZ;ISA总线时钟频率:8MHZ。 d、基本时序关系: CPU 66、100、133 PCI(33MHZ) ISA(8MHZ) 三、图解 频率发生器芯片

大楼工程弱电时钟系统解决方案

大楼工程弱电系统 时钟系统 解决方案 西安同步电子科技有限公司二零一四年

大楼工程弱电时钟系统解决方案 时钟系统概述 概述 根据大楼建设工程弱电系统设计要求,本工程设置时钟系统用于统一区域内的时间信息。 标准时钟系统是为工作人员准确、标准的时间,同时也可以为其它智能化系统提供标准的时间源。标准时钟系统的设计将结合实际需要,保证相关人员都能清晰地看到的时钟,并掌握准确时间。 本工程时钟系统主要由网络时间服务器、网络数字式子钟组成。 本系统从GPS地球同步卫星上获取标准时钟信号信息,将这些信息TCP/IP网络传输,传输到各个壁挂网络数字时钟,实现整个子母钟系统的时间统一。 系统特点 精确度高 本系统能够接收来自GPS的标准时间信号,通过网络授时协议NTP/SNTP发送至系统的各个部分,实现无累积误差运行。 可靠性高(系统冗余) 本系统对时间服务器的关键设备都采用无风扇设计,具有四个独立的网络授时接口,当某个网络授时单元发生故障时,能够切换到另外一个单元,实现冗余备份的目的。 兼容性好 系统采用分布式结构,由标准化的软件及硬件组成,用户可按照需要灵活配置和扩容。 根据将来发展的需要,可以将子钟接口分别扩展到128个或256个以满足系统扩容要求。 维护方便 本系统所有主控板、信号板、接口板均采用了目前国际上流行的模块化设计,使相同规格的设备和接口板具有可互换性;积木式结构还为业主未来系统的增容和扩展提供极大的便利。 时钟系统设计与制造技术规范 系统设计规范 采用标准 电气装置安装工程施工及验收规范GBJ/232-92 设备可靠性试验规范GB50807-86 国际电气与电子工程师协会(IEEE) 国际电子学会(IEC)

最新轨道交通时钟系统解决方案复习过程

轨道交通时钟系统解决方案 轨道交通时钟系统解决方案 地铁通信系统一般包括: 时钟系统是轨道交通重要的组成部分之一,而其在地铁站的主要作用是为上班族、来往的游客工作人员提供准确的时间信息,同时时

钟系统要为其他监控系统、控制系统等弱电子系统提供统一的时钟信号,使各系统的定时集中同步,在整个地铁系统中使用相同的定时标准。站厅及站台位置的时钟可以为旅客提供准确的时间信息;各车站办公室内及其它停车场内的时钟可以为工作人员提供准确的时间信息;向其它地铁通信子系统提供的时钟信息为地铁运行提供了标准的时间,保证了轻轨系统运行的准时,安全。 时钟子系统能够向地铁全部通信子系统提供准确的时钟信号。时钟信号以卫星自动定位系统所发的格林威治标准世界时间为准辅以铷原子钟或石英钟。时钟系统的控制中心向各分站或车场二级母钟发送时钟信号,再由二级母钟向其对应的子钟发送时钟信号;同时每站的各路时钟信号均需上传至时钟系统的监控中心,使之可以完成对全路各站所有时钟工作状态的监测和控制,并可在相应的管理客户机上完成各种需要的管理及配置功能。

设计区域:换乘大厅、进出口、监控室、控制室控制中心调度大厅和各车站的站厅、站台、车站控制室、公安安全室、票务室、变电所控制室及其它与行车有关的处所,并在车辆段/停车场信号楼运转室、值班员室、停车列检库、联合检修库等有关地点设置子钟。

相关产品 第一章教育和教育学 1 教育的发展 一、教育的概念 考点:教育是培养人的一种社会活动,是传承社会文化、传递生产经验的和社会生活经验的基本途径。 考点广义:凡是增进人们的知识和技能,影响人们思想观念的活动,都具有教育作用。 狭义:主要指学校教育。 学校教育是教育者根据一定的教育要求,有目的、有计划、有组织的通过学校的教育工作,对受教育者的身心施加影响,促使他

单片机实时时钟电路的原理及应用

单片机实时时钟电路的原理及应用 1 引言现在流行的串行时钟电路很多,如DS1302、DS1307、PCF8485 等。这些电路的接口简单、价格低廉、使用方便,被广泛地采用。本文介绍的 实时时钟电路DS1302 是DALLAS 公司的一种具有涓细电流充电能力的电路, 主要特点是采用串行数据传输,可为掉电保护电源提供可编程的充电功能,并 且可以关闭充电功能。采用普通32.768kHz 晶振。 2 DS1302 的结构及工作原理DS1302 是美国DALLAS 公司推出的一种高性能、低功耗、带RAM 的实 时时钟电路,它可以对年、月、日、周日、时、分、秒进行计时,具有闰年补 偿功能,工作电压为2.5V~5.5V。采用三线接口与CPU 进行同步通信,并可 采用突发方式一次传送多个字节的时钟信号或RAM 数据。DS1302 内部有一个31×8的用于临时性存放数据的RAM 寄存器。DS1302 是DS1202 的升级产品,与DS1202 兼容,但增加了主电源/后背电源双电源引脚,同时提供了对后背电 源进行涓细电流充电的能力。 2.1 引脚功能及结构图1 示出DS1302 的引脚排列,其中Vcc1 为后备电源,VCC2 为主电源。在主电源关闭的情况下,也能 保持时钟的连续运行。DS1302 由Vcc1 或Vcc2 两者中的较大者供电。当Vcc2 大于Vcc1+0.2V 时,Vcc2 给DS1302 供电。当Vcc2 小于Vcc1 时,DS1302 由Vcc1 供电。X1 和X2 是振荡源,外接32.768kHz 晶振。RST 是复位/片选线,通过把RST 输入驱动置高电平来启动所有的数据传送。RST 输入有两种功能:首先,RST 接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST 提供终止单字节或多字节数据的传送手段。当RST 为高电平时,所有的数据传 送被初始化,允许对DS1302 进行操作。如果在传送过程中RST 置为低电平, 则会终止此次数据传送,I/O 引脚变为高阻态。上电运行时,在Vcc≥2.5V之前,RST 必须保持低电平。只有在SCLK 为低电平时,才能将RST 置为高电平。

网络时钟施工方案设计

实用文档 网络时钟施工方案

目录 一、工程概况 1.工程简述 2.系统说明 二、主要工程量和主要实物工程量 1.主要工程量 2.主要实物工程量 三、安装调试 1. 安装要求 2.系统调试时需具备的条件 3.验收测试方法及测试标准

一、项目概况 1.工程简述 根据XXX综合楼项目弱电系统设计要求,本工程设置集中监控时钟系统。 时钟系统供应商-烟台持久钟表集团有限公司在本工程时钟系统建设中,本着“国际领先、国内一流”的投标目标,使医院智能化楼宇工程时钟系统完全符合相关国家及行业规范和标准,并严格按照医院智能化楼宇工程对时钟系统的各种特殊要求,将之建成一个技术先进、智能化高、功能齐全完善的时钟系统,实现整个医院内时间标准的统一,以便于整个医院内工作人员和患者随时掌握准确、统一的时间信息,使各业务部门、职能部门工作井然有序、协调一致地进行工作,为各功能部门之间有机协调、密切配合提供标准的时间依据,确保适应医院智能化楼宇各种相关业务高速运转的需求。 医院时钟系统是一个大型联网计时系统。该系统采用分布式系统结构,系统母钟与各子钟之间采用以太网接口方式,扩展方便。该系统的信号接收单元具有接收GPS标准时间信号的功能,为整个系统提供校时信号,消除计时系统的积累误差。该系统还采用了母钟热备份、自动切换保护、反馈控制、抗干扰及冗余等技术,是一个高精度、高可靠性的多子母钟系统。 烟台持久钟表有限公司自主开发生产的大区域时钟系统已被成功应用于苏州大学附属第二医院、东莞康华医院、天津泰达医院、青岛东部医院、首都国际机场T3航站楼、上海浦东国际机场、成都双流国际机场、宁波栎社机场、沈阳桃仙国际机场、深圳宝安国际机场、大连周水子国际机场、重庆江北机场改扩建工程、昆明火车站改扩建工程、海南海口美兰机场、长春龙嘉

电力时钟同步系统解决方案

电力GPS时钟同步系统解决方案 北京创想京典科技发展有限公司 科 技 领先铸就最佳

什么是时间? 时间是一个较为抽象的概念,爱因斯坦在相对论中提出:不能把时间、空间、物质三者分开解释,"时"是对物质运动过程的描述,"间"是指人为的划分。时间是思维对物质运动过程的分割、划分。 在相对论中,时间与空间一起组成四维时空,构成宇宙的基本结构。时间与空间都不是绝对的,观察者在不同的相对速度或不同时空结构的测量点,所测量到时间的流逝是不同的。广义相对论预测质量产生的重力场将造成扭曲的时空结构,并且在大质量(例如:黑洞)附近的时钟之时间流逝比在距离大质量较远的地方的时钟之时间流逝要慢。现有的仪器已经证实了这些相对论关于时间所做精确的预测,并且其成果已经应用于全球定位系统。另外,狭义相对论中有“时间膨胀”效应:在观察者看来,一个具有相对运动的时钟之时间流逝比自己参考系的(静止的)时钟之时间流逝慢。 就今天的物理理论来说时间是连续的,不间断的,也没有量子特性。但一些至今还没有被证实的,试图将相对论与量子力学结合起来的理论,如量子重力理论,弦理论,M理论,预言时间是间断的,有量子特性的。一些理论猜测普朗克时间可能是时间的最小单位。

什么是时间? 根据斯蒂芬·威廉·霍金(Stephen William Hawking)所解出广义相对论中的爱因斯坦方程式,显示宇宙的时间是有一个起始点,由大霹雳(或称大爆炸)开始的,在此之前的时间是毫无意义的。而物质与时空必须一起并存,没有物质存在,时间也无意义。

卫星时钟系统为什么含有精确的时间信息? 地球本身是一个不规则的圆,加上地球自转和公转的误差,如果仅仅依靠经度、纬度、海拔高度三个参数来定位的偏差会很大,所以 引入了一个时间参数,每个卫星都内置了一个高稳定度的原子钟!

2016---TI杯大学生电子设计竞赛题目

2016年TI杯大学生电子设计竞赛 A题:降压型直流开关稳压电源 1.任务 以TI公司的降压控制器LM5117芯片和CSD18532KCS MOS场效应管为核心器件,设计并制作一个降压型直流开关稳压电源。额定输入直流电压为时,额定输出直流电压为,输出电流最大值为。测试电路可参考图1。 L R 图1 电源测试连接图 2.要求 (1)额定输入电压下,输出电压偏差:;(10分) (2)额定输入电压下,最大输出电流:;(10分) (3)输出噪声纹波电压峰峰值:;(10分) (4)从满载变到轻载时,负载调整率: ;(10分) (5)变化到17.6V和13.6V,电压调整率: (10分)(6)效率;(15分) (7)具有过流保护功能,动作电流;(10分) (8)电源具有负载识别功能。增加1个2端子端口,端口可外接电阻R(1kΩ-10kΩ)作为负载识别端口,参考图1。电源根据通过测量端口识别电阻R的阻值,确定输出电压,;(10分) (9)尽量减轻电源重量,使电源不含负载的重量。(15分) (10)设计报告(20分)

3.说明 (1) 该开关稳压电源不得采用成品模块制作。 (2) 稳压电源若含其它控制、测量电路都只能由端口供电,不得增加其他辅助电源。 (3) 要求电源输出电压精确稳定,或,作品不参与测试。 2016年TI 杯大学生电子设计竞赛题 B 题:物品分拣搬送装置 1.任务 在一个以木条(截面不大于 3cm×4cm,木质本色)围成的100cm×150cm 的A 区域内,散落着 边长均为4cm 的正方体。设计一自动物体搬运系统,能够快速将 这些 正方体移至指定区域。A 区域的颜色为白色,B 区域为黑色,C 区域 为红色。 2.要求 (1) 在A 区域内任意放置

跨时钟域信同步方法种

跨时钟域信号同步方法6种 ASIC中心 1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。本文总结出了几种同步策略来解决跨时钟域问题。 2 异步设计中的亚稳态 触发器是FPGA设计中最常用的基本器件。触发器工作过程中存在数据的建立(setup)和保持(hold)时间。对于使用上升沿触发的触发器来说,建立时间就是在时钟上升沿到来之前,触发器数据端数据保持稳定的最小时间。而保持时间是时钟上升沿到来之后,触发器数据端数据还应该继续保持稳定的最小时间。我们把这段时间成为setup-hold时间(如图1所示)。在这个时间参数内,输入信号在时钟的上升沿是不允许发生变化的。如果输入信号在这段时间内发生了变化,输出结果将是不可知的,即亚稳态 (Metastability) 图1 一个信号在过渡到另一个时钟域时,如果仅仅用一个触发器将其锁存,那么采样的结果将可能是亚稳态。这也就是信号在跨时钟域时应该注意的问题。如图2所示。 信号dat经过一个锁存器的输出数据为a_dat。用时钟b_clk进行采样的时候,如果a_dat正好在b_clk的setup-hold时间内发生变化,此时b_ dat就既不是逻辑"1",也不是逻辑"0",而是处于中间状态。经过一段时间之后,有可能回升到高电平,也有可能降低到低电平。输出信号处于中间状态到恢复为逻辑"1"或逻辑"0"的这段时间,我们

基于FPGA位同步时钟提取方案的设计

一种基于FPGA的新型位同步时钟提取方案及实现2 位同步时钟提取方案的原理 本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两 种 情 况, 如图1和图2所示: 图1 码流滞后于本地时钟△T示意图图2 码流超前于本地时钟△T示意图 从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。用VHDL语言描述为: if (code_in’event and code_in=’1’) then if (code_in and clk)=’1’ then q<=’1’ else q<=’0’ end if end if 程序中输出信号q可作为控制电路的输入信号。 本设计方案的系统框图如图3所示: 框图中,鉴相器作用是鉴别出码流和本地时钟的相位超前滞后关系,控制计数器采用双向计数器,鉴相器输出q作为控制计数器的计数方向输入,q为1则向上计数,q为0则向下计数。控制计数器的计数输出用来控制相位调整选择模块的选择端。相位调整选择模块由相位调整和相位选择功能。 图3 系统功能框图 3 设计实现

依据图3系统功能框图,利用Altera 公司的Quartus II 设计软件,采用自顶向下的模块化设计方法,用VHDL 语言和电路原理图混合输入设计对位同步时钟提取电路的各个部件分别进行设计。 本设计方案的鉴相器原理相对简单,不需要用VHDL语言设计,仅用两个 与门和一个D触发器就可以实 现,如图4 所示。图中的 的第二个与门(inst23)是为了实现D 触发器的时钟输入端与数据输入端 同步。 控制计数器设计使用Quartus II的MegaWizard Plug_In Manager工具来实现一个简单 的双向 数器,计数方向由鉴相器输出q控 制,q为1则计数器向上计数,q为0则计数器向下计数,计数系数由Count Modulus设定,设定的数值要求等于分频器的分频系数N。在原理图输入时可以任意改变分频器的分频系数和计数器的计数系数。 分频器设计输出时钟信号的占空比为50%,且分频系数N可调,用VHDL 语言实现并由软件自动生成元件符号供原理图调用,如图5所示。 下面给出分频器的VHDL语言关键描述语句 if(clk'event and clk='1') then if(count=N-1)then --计数周期 count<=0; else count<=count+1; if count<(integer(N/2)) then --产生分频脉冲 outclk<='0'; else outclk<='1'; end if; end if; end if; 相位调整选择模块的相位调整功能可以用延迟方式实现。在FPGA中要产生延时,信号必须经过一定的物理资源。在硬件描述语言中有关键词Wait for xx ns,需要说明的是该语法是仅仅用于仿真而不能用于综合的,可综合的延时方法有: (1)使信号经过逻辑门得到延时(如非门); (2) 使用器件提供的延时单元(如Altera公司的LCELL); (3)使用移位寄存器。 由于当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己,而且门延迟时间相对于具体器件是不固定的,LCELL延时单元也可以用来产生一定的延时,但这样形成的延时在FPGA芯片中并