433M扩频模块 UART接口 SEMTECH sx1276, sx1278

APC340 APC340扩频技术无线数传模块VER1.20

APC340模块是高度集成低功耗半双工小功率无线数据传输模块,其嵌入高速低功耗单片机和高性能扩频射频芯片SX127X,创新的采用高效的循环交织纠检错编码,抗干扰和灵敏度都大大提高,APC340模块提供了多个频道的选择,可在线修改串口速率,收发频率,发射功率,射频速率等各种参数。

APC340模块工作电压为2.1-3.6V,可定制3.5-5.5V工作电压,在接收状态下仅消耗13mA。APC340

模块四种工作模式,各模式之间可任意切换,在1SEC 周期轮询唤醒省电模式(Polling mode)

应用:

●无线水气热表抄表

●极远距离数据通讯

●集装箱信息管理

●无线自动化数据采集

●野外数据遥控、遥测

●各种变送器,流量计智能仪表

●楼宇小区自动化与安防

●矿山石油设备控制通讯

●环境、节能、温度监测

●电气电力设备状态监测下,接收仅仅消耗几十uA,一节3.6V/3.6AH时的锂亚电池可工作数年,非常适合电池供电的系统。

特点:

●3000米传输距离(0.81Kbps)

●频率

433MHz/470MHz/868MHz/915MHz ●-132dBm@810bps高灵敏度

●100mW发射功率(可设置)

●多频道可设,双256Bytes数据缓冲区●零等待唤醒,具有空中唤醒功能

●高效的循环交织纠错编码

●四种工作模式,待机电流2.5uA

●内置看门狗

APC340模块是新一代的多通道嵌入式无线数传模块,可设置多个频道,步进为1KHz,发射功率最大100mW,体积32.1mm x18.3mm x6.0mm,很方便客户嵌入系统之内,APC340模块具有较低的功耗,非常适合于电池供电系统。

APC340模块采用了扩频调制和高效的纠错编码,其编码增益较传统的调制方式(如FSK,GFSK以及PSK)高出近10dBm,抗突发干扰和灵敏度都较大的改善。同时编码也包含可靠检错能力,能够自动滤除错误及虚假信息,真正实现了透明的连接,在同等的发射功率下是传统的模块近一倍的距离。所以APC340模块适合于恶劣环境或对距离有要求的场合。

APC340模块内设双256Bytes大容量缓冲区,在缓冲区为空的状态下,用户可以1次传输256Bytes的数据,当设置空中波特率大于串口波特率时,可1次传输无限长度的数据,同时APC340模块提供标准的UART/TTL接口,1200/2400/4800/9600/19200/38400/57600bps七种速率,和三种接口校验方式。APC340模块外部接口采用透明数据传输传输方式,能适应标准或非标准的用户协议,所收的数据就是所发的数据。

设置模块采用串口设置模块参数,具有丰富便捷的软件编程设置选项,包括频点,空中速率,以及串口速率,校验方式,等都可设置,设置方式有二种方式,一是通过本公司提供的设置软件RF-Magic利用PC串口即可,二是动态在线设置,用串口发命令动态修改,具体方法参见APC340模块的参数设置章节。

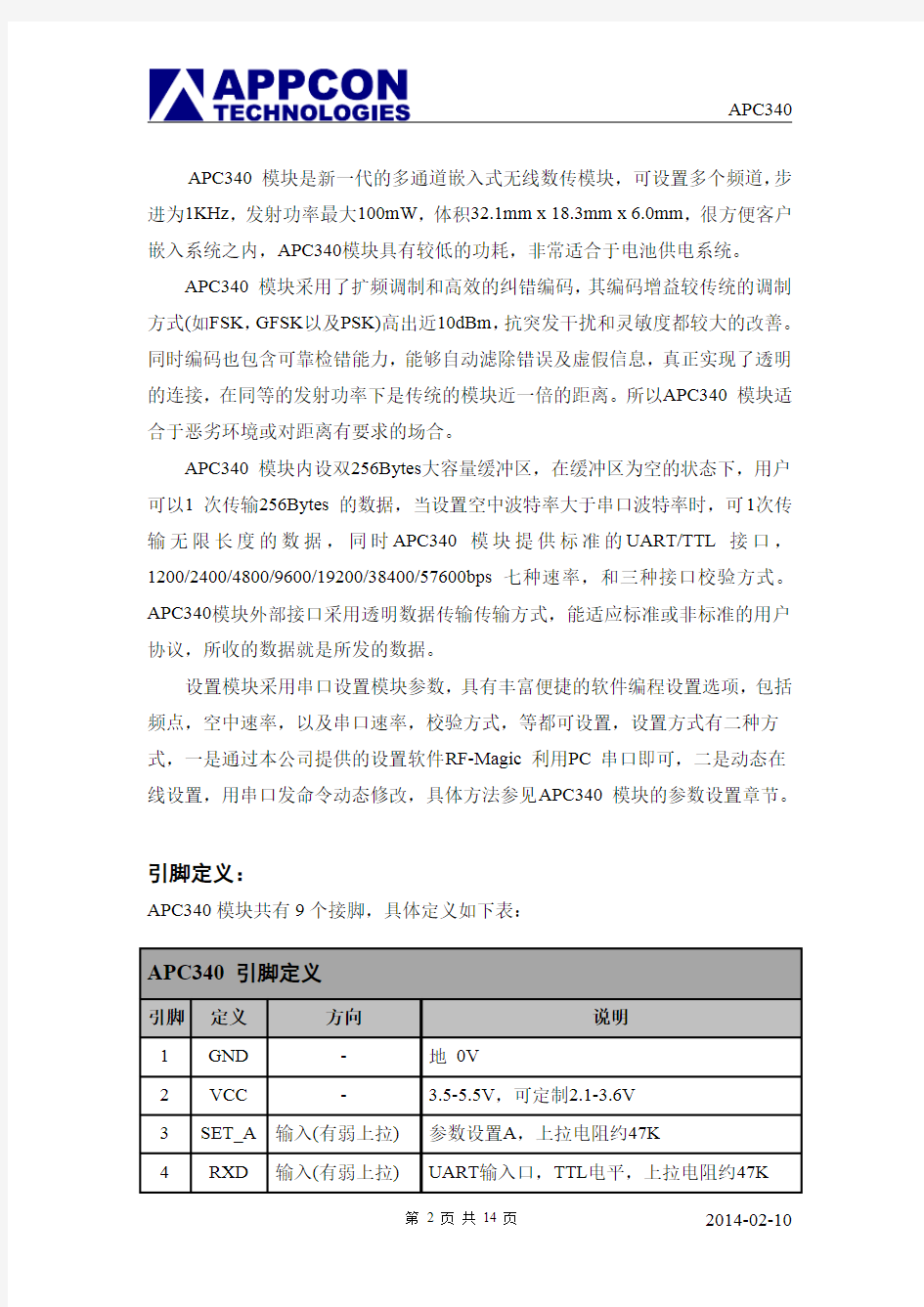

引脚定义:

APC340模块共有9个接脚,具体定义如下表:

APC340引脚定义

引脚定义方向说明

1GND-地0V

2VCC- 3.5-5.5V,可定制2.1-3.6V

3SET_A输入(有弱上拉)参数设置A,上拉电阻约47K

4RXD输入(有弱上拉)UART输入口,TTL电平,上拉电阻约47K

5TXD输出UART输出口,TTL电平

6AUX输出数据输入输出指示

7SET_B输入(极弱上拉)参数设置B,上拉电阻约10M 8NC-接地或悬空

9NC-接地或悬空

表一APC340引脚定义表

产品尺寸:

图一产品尺寸图

工作模式:

典型的无线收发机编码如下图。

PREAMBLE (前导码)SYNCWORD

(同步码)

DATA+CRC with FEC

(数据+CRC检错具有前向纠错)

前导码的作用是使目的接收机时钟与发射机同步,正常模式下前导码长度一般为8符号位即可,如工作在省电模式时序下,前导码还有唤醒接收机的功能,

此时发射机必须发送较长的前导码将省电模式下的接收机唤醒进入正常的工作状态。如设置接收机1秒钟唤醒一次,那么接收机每间隔1秒钟唤醒一次搜索前导码(tw),持续长度一般为不到2个符号位。而发射机首先发射1秒以上的前导码再发射后面得同步码等,这意味着接收机在唤醒的周期,只要信道中发现前导码,在正常情况下都能够可成功检测到并唤醒接收,示意图见图四。

APC340有四种工作模式,分别为:1)正常模式,2)唤醒模式,3)省电模式,4)休眠模式,这四种工作模式是由SET_A和SET_B的电平决定的。

一)正常模式(模式1):SET_A=0,SET_B=0。

A)发送:当模块RXD脚输入第一个字节后,模块置低AUX,并且开始判断SET_B的电平,RXD脚接收完最后一个字节后,等待2-3Bytes时间,如没有数据输入,则模块置高AUX脚并切换到发射状态,然后发送前导码,同步码和数据,发送结束后,并根据SET_A和SET_B的电平转入相应的状态状态。

处于该模式下模块发送数据时并没有发送较长的前导码,所以要求接收方必须处于模式1或模式2,即持续接收状态。

B)接收:串口打开,模块处于持续接收状态,如模块从当前信道中接收到数据后,经过解交织纠错检错确认数据无误时,置低AUX并立刻从串口输出数据,串口发送结束后重新置高AUX。正常模式收发时序,请参见图二。

图二:正常模式收发时序图

有些情况,用户需要连续多包无线发射,空中尽量少得间隔,这时可以利用AUX脚,当RXD脚接收到数据后AUX脚会变低,在开始发射时AUX重新变高,此时用户可以再次通过RXD脚发送第二包数据,模块会在无线发送第一包数据之后,不会等待2-3Bytes时间,而是立刻将缓冲区的数据发走,时序见图三。

图三:正常模式持续多包发射时序图

二)唤醒模式(模式2):SET_A=0,SET_B=1。

A)发送:当模块RXD脚输入第一个字节后,模块置低AUX,并且开始判断SET_B的电平,RXD脚接收完最后一个字节后,等待2-3Bytes时间,如没有数据输入,则模块置高AUX脚并切换到发射状态,然后发送前导码长度为一个唤醒周期(如1秒)加上同步码等,发送结束后根据SET_A和SET_B的电平转入相应的状态,发射示意图见图四。

处于该模式下模块发送数据时发送了较长的前导码,所以接收方处于模式1,模式2或模式3均能够接收到数据。

B)接收:串口打开,模块处于持续接收状态,如模块从当前信道中接收到数据后,经过解交织纠错检错确认数据无误时,置低AUX并立刻从串口输出数据,发送结束后重新置高AUX。与模式1不同的是模块在模式2状态下接收时,每当接收到一包数据都会在数据的最后补上一个字节接收场强(RSSI),详细说明见应用方式章节。

三)省电模式(模式3):SET_A=1,SET_B=0。

串口处于关闭状态,接收机在一个唤醒周期(如1秒)后打开并搜索信道中是否有前导码,如没有则立刻休眠状态等待下一个唤醒周期再被唤醒,如有前导码则继续接收,同时监控前导码并等待同步码到来后,将数据接收下来。经过解交织

纠错检错确认数据无误时,置低AUX以唤醒下位机,等待5ms后打开串口并输出数据。串口输出结束后,关闭串口,置高AUX,如模式设置没有改变则再次进入立刻休眠状态等待下一个唤醒周期。该模式的接收示意图见图四。

图四:发射处于模式2状态,接收处于模式3状态示意图

四)休眠模式(模式4):SET_A=1,SET_B=1。

串口处于关闭状态,对外接口电平保持,模块处于休眠状态。此模式下,模块的射频电路,CPU主时钟与外设均被软件关闭,但watchdog和低频时钟仍在工作,并周期唤醒CPU极短的时间,以便清除watchdog定时器和检查模块状态,这种模式下平均耗电仅仅约2.5uA。

此外,模块的设置是休眠模式完成的,具体过程见参数设置的章节。

应用方式:

APC340模块的四种模式是通过SET_A,SET_B的高低电平转换的,四种模式可以任意转换,模块与下位机的连接图见图五。APC340的SET_A和SET_B有弱上拉电阻,但在正常工作时不能悬空,必须有明确的电平,否则可能造成模块工作不稳定。

用户的上位机可以直接与APC340相连,但是一定要注意接口电平必须与

APC340相近,一般不要误差超过±0.3V,否则会导致有较大的灌电流或拉电流。比如APC340的供电是3.3V,那么用户的MCU供电应该在3.0-3.6V范围内。

图五:模块与下位机的连接图

APC340休眠模式是通过用软件方式实现的,休眠时模块的接口均保持相应的电平,并且能快速切换各种状态,从休眠至唤醒仅仅需要20uS,这意味模块在休眠状态时,置低SET_A脚后20uS就可以通过UART口输入数据至模块。

需注意的是模块在接收或发送过程中,即使设置模块至模式3或4,模块也要将接收或发送过程执行完毕再进入省电模式或休眠模式,利用这个特点,当模块处于模式3或模块4状态,用户在置低SET_A脚使模块唤醒并通过RXD输入数据,模块在接收到第一个字节后,立刻将AUX置低(见图二),并且判断SET_B脚的电平,若高则在发射数据前发送较长的前导码用于唤醒对方的接收机,若低发送正常的前导码。用户如需在发射后将模块休眠,可在AUX为低后,置高SET_A 脚休眠,而不必等到模块将数据无线发送完毕,模块在数据发送结束后会自动检测SET_A脚,如为高则立刻进入休眠状态。

APC340模块具有收发2个256Bytes缓冲区,APC340模块在UART口接收到数据后,两个条件将促使APC340模块开始无线发送数据:一)RXD脚收到数据后,等待2-3个字节的时间都没有收到数据,例如用9600bps的串口波特率,2-3个字节的时间大约为2-3ms,二)RXD脚收到的数据大与或等于99个字节(用户可定制字节长度),此时APC340模块会将接收缓冲器的99字节的数据立刻编码发送,此时RXD脚依然可以接收串口数据。99字节的数据发送结束后,如接收缓冲器里有数据,APC340模块不管有多少数据,会将余下的数据一起发送。

如前文所述,在APC340发送数据时,SET_A是为低电平的,SET_B的电平决定了是否发送较长的前导码用于唤醒对方的接收机。

在正常接收时,SET_A是为低电平的,而SET_B的电平决定决定是否输出场强,如果SET_B为低,模块正常接收,如SET_B为高,模块将在输出的每一包数据后增加一个字节的场强信息,场强的表示为:

RSSI[dBm]=-137+RSSI_value

需特别注意的是,APC340模块对于较大的数据是切包发送的,如接收端输出场强,则会在每个小包后加一个场强字节。

在电池供电的电路中,正常可将从模块(如水气表)设置在模式3上,当主模块(如采集器或收抄机)在模式2下发送数据,从模块唤醒后接收数据,完成后利用AUX脚将下位机MCU唤醒,再将数据输出,MCU接收到数据后,可将从模块切换至模式1,应答主模块。如主模块收到应答后也可被切换至模式1,这时主从模块均处于正常模式下,可以实现高速数据传输。如主模块收到应答后,后续无数据交换可将从机再次切换至模式3处于省电模式下,等待下一次的唤醒,而主模块可以切换至模式4休眠状态。

因为省电是通过周期性唤醒休眠再唤醒实现的,所以在省电模式下的功耗与唤醒周期和每次唤醒搜索前导码的时间(tw),以及休眠的静态功耗有关。唤醒周期用户可以在线设置范围是50ms至5s.每次搜索前导码时间与射频传输的速率有关,射频传输的速率也是可设的,在4.56Kbps速率的速率下唤醒搜索前导码时间平均约为2.1ms。

在省电模式下电池的使用寿命可以通过以下公式算出:

使用寿命=

电池容量mAH

(搜索前导码时间/(唤醒周期+搜索前导码时间))*接收电流+休眠电流

例如:电池是 3.6V/3.6AH ER18505锂亚离子电池,APC340接收电流为

13mA,休眠电流2.5uA。射频传输速率4.56Kbps,唤醒周期为1SEC,那么电池使用寿命是:

=

3600mAH

(2.1ms/(1000ms+2.1ms))*13.0mA+0.0025mA

≈121037Hour≈13.81Year 考虑到电池的自放电,不同电流下的容量差异,温度以及客户端MCU的休

眠功耗和正常的使用,1节3.6V/3.6AH ER18505锂亚离子电池正常情况下有超过几年的使用寿命。这里要注意,锂亚离子电池虽然有自放电比较低,容量大等优点,但是一般的锂亚离子电池都有钝化现象,表现为在小电流下放电下内阻会逐渐增大,所以必要时需并联低泄漏电流的超级电容(super capacitor)如0.47F/5V ,以降低内阻,提高瞬间供电能力。

省电模式的工作方式非常适合水气热表抄表,集装箱信息管理,数据采集系统等使用不是太频繁但要求用电池长期工作的场合。

参数设置:

APC340模块使用相当的灵活,可以根据用户的需求设置不同的选项。图六:RF-Magic 设置软件

用户可以对串口参数,串口效验,收发频率,空中速率,输出功率进行设置,设置的方法有二种方式。一是本公司开发设置收发模块的软件RF-Magic 见图六,通过PC 修改。用RF-Magic 软件设置是通过模块的UART/TTL 口完成的(4,5PIN),所以必须接UART/TTL to RS232接口转换板在连接到PC 完成设置,或使

无线速率收发频率

无线功率

串口校验

串口速率

设置串口写操作读操作状态栏软件说明

唤醒周期

发射长度

空中延时

用本公司提供的串口转换板和USB转换板,见图七。设置方法是,首先连接好通讯线,打开RF-Magic打开软件,然后打开模块电源,最后插入模块到测试板,此时,软件的状态栏应显示Found Device(发现模块),这时就可以进行相应的读写操作。

图七:软件设置接线图

二是通过在线进行修改。在线软件设置也是通过模块的UART/TTL口完成的(4,5PIN)完成的。当模块上电500ms后,模块即可正常工作。设置时,首先应将模块其他模式(如模式1,2,3)切换至模式4,APC340模块进入休眠模式,约10ms 后,可以进行设置。当串口的输入口(RXD)输入设置命令后能将模块重新唤醒,此时无论UART口是何状态,模块自动将UART口转变为9600bps,无效验模式。设置命令如正确则应答响应命令,此后模块自动复位重新初始化,500ms后模块即可在设置的参数上运行。如果输入设置命令有误,模块将不做任何应答,但仍能引起一次复位和重新初始化,用户可以利用特点,在模块长期休眠后或需要重新启动时复位模块。

APC340设置采用HEX码,波特率为9600,无效验模式,设置命令有二条,格式如下:

1)读设置命令:0xFF,0x56,0xAE,0x35,0xA9,0x55,0xF0。

应答:0x24,模块型号,版本号,频率,空中速率,发射功率,串口速率,串口效验,唤醒时间。

2)写设置命令:0xFF,0x56,0xAE,0x35,0xA9,0x55,0x90频率,空中速

率,发射功率,串口速率,串口效验,唤醒时间

应答:0x24,模块型号,版本号,频率,空中速率,发射功率,串口速率,串口效验,唤醒时间

其中参数表示用HEX表示,方法如表二:

参数表示方法

参数字节数说明

模块型号1APC340模块型号代码为十进制的14,模块型号固化在FLASH内不可设置

版本号1当前版本,范围0-255,版本号固化在FLASH内不可设置频率3单位KHz,如433.920MHz用表示为0x06,0x9F,0x00

空中速率10.81K,1.46K,2.6K,4.56K,9.11K,18.23Kbps表示为0x00,0x01,0x02,0x03,0x04,0x05

发射功率10至7。表示为0x00至0x07。设置每增加1发射功率增加约3dBm,最大设置为7,发射功率约为20dBm

串口速率11200,2400,4800,9600,19200,38400,57600,115200bps 表示为0x00,0x01,0x02,0x03,0x04,0x05,0x06,0x07

串口效验10x00为无效验,0x01为奇校验,0x02为偶校验

唤醒时间150ms,100ms,200ms,400ms,600ms,1s,1.5s,2s,2.5s,3s,4s,5s表示为0x00至0x0b

表二模块的参数设置表

如将模块设置为,频率433.92MHz,空中速率4.56K bps,发射功率100mW,串口速率9600bps,无效验,唤醒时间1S。

写设置为:0xFF,0x56,0xAE,0x35,0xA9,0x55,0x90,0x06,0x9F,0x00,0x03,0x07,0x03,0x00,0x05

应答:0x24,0x0a,0x01,0x06,0x9F,0x00,0x03,0x07,0x03,0x00,0x05 APC340技术指标:

APC340技术指标(测试条件:3.3V,25℃±5℃)

工作频率410-440MHz,855-885MHz,900-930MHz

频率步进1KHz设置步进

调制方式扩频调制

发射功率100mW@3.3V(0-7,8级可调,每级递增3dBm,最大100mW)接收灵敏度-132dBm@0.81Kbps,-118.5dBm@18.23K bps

空中传输速率/(占用带宽)0.81K/(BW125K),1.46K/(BW125K),2.6K/(BW125K),4.56K/(BW125K),9.11K/(BW250K),18.23K/(BW500K)

接口速率1200–115200bps

接口效验方式8N1/8E1/8O1

接口缓冲空间双256Bytes

工作湿度10%~90%(无冷凝)

工作温度-30℃-85℃

电源 2.1–3.6V,可定制3.5–5.5V

发射电流(典型值)100mA@100mW

谐波抑制小于等于1GHz:<-36dBm,大于1GHz:<-30dBm 持续接收电流VS

接收速率(典型值)

13mA@4.56Kbps,15mA@18.23Kbps

休眠电流 2.5uA@3.3V(典型值),最大4.0uA

唤醒搜索前导码时间(tw)14.6ms@0.81Kbps,7.3ms@1.46Kbps,3.8ms@2.6Kbps,2.1ms@4.56Kbps,1.2ms@9.11Kbps,0.7ms@18.23Kbps

传输距离3000米@0.81Kbps,2000米@9.11K bps,(开阔地可视距离)设置擦写次数300K

尺寸32.1mm x18.3mm x6.0mm

天线口阻抗50欧姆

表三APC340技术指标

APC340模块的注意的问题:

考虑到空中传输的复杂性,无线数据传输方式固有的一些特点,应考虑以

下几个问题。

1)APC340模块的组网应用

APC340的通信信道是半双工的,可以完成一点对一点,一点对多点的通讯。这二种方式首先需要设1个主站,其余为从站,所有站点都必须设置一个唯一的地址。通信的协调由主站控制,主站采用带地址码的数据帧发送数据或命令,所有从站全部都接收,并将接收到的地址码与本机地址码比较,地址不同则将数据丢掉,不做响应,若地址码相同,则将接收的数据传送出去。组网必须保证在任何一个瞬间,同一个频点通信网中只有一个电台处于发送状态,以免相互干扰。APC340可以设置多个频道,所以可以在一个区域实现多个网络并存。

2)无线通信中数据的延迟

由于无线通信发射端是从终端设备接收到一定数量的数据后,或等待一定的时间没有新的数据才开始发射,无线通信发射端到无线通信接收端存在着几十到几百毫秒延迟(具体延迟是由串口速率,空中速率以及数据包的大小决定),另外从无线通信接收端到终端设备也需要一定的时间,但同样的条件下延迟时间是固定的。

3)差错控制

APC340模块具有较强的抗干扰能力,在编码已经包含了强大的纠检错能力。但在极端恶劣的条件下或接收地的场强已处于APC340模块接收的临界状态,难免出现接收不到或丢包的状况。此时客户可增加对系统的链路层协议的开发,如增加类似TCP/IP中滑动窗口及丢包重发等功能,可大大提高无线网络的使用可靠性和灵活性。

4)天线的选择

天线是通信系统的重要组成部分,其性能的好坏直接影响通信系统的指标,用户在选择天线时必须首先注重其性能。一般有两个方面,第一选择天线类型;第二选择天线的电气性能。选择天线类型的意义是:所选天线的方向图是否符合系统设计中电波覆盖的要求;选择天线电气性能的要求是:选择天线的频率带宽、增益、额定功率等电气指标是否符合系统设计要求。

常见问题解答:

常见问题解答

设备之间不能正常通讯1.两端的通讯参数不一致,如:波特率,校验不一致2.两端的频点,空中波特率不一致

3.不是同一系列产品

4.电源连接不正常

5.模块已损坏

6.模块模式设置错误

7.通讯距离超过范围,或天线接触不良

传输距离近1.电压超过范围

2.电源纹波过大

3.天线接触不良或天线类型不对

4.天线过与靠近金属表面或模块接地面积太小5.接收环境恶劣,如建筑物密集,有强干扰源6.有同频干扰

接收有错误数据1.接口设置不当

2.接口接触不良

3.接口电缆线过长

4.波特率设置不对

表四APC340常见问题解答

UART IP设计

UART IP设计文档 1,主要特征; UART采用的是一种起止式异步协议,特点是一个字符一个字符地传输,并且传送一个字符总是以起始位开始,以停止位结束,字符之间没有固定的时间间隔要求。一个字符传送完成后,奇偶校验位之后的停止位和空闲位都规定为高电平,而起始位为低电平,这样就保证起始位开始处一定有个下降沿,这个下降沿用来界定一个字符传输的开始,它的到来就表示下面是数据位,要准备接收;而停止位标志一个字符的结束,它的出现表示一个字符传送完毕,这样就为通信双方提供了何时开始收发和何时结束的标志。 2,整体框图 图2.1 UART IP整体框图 UART IP的整体框图如图2.1所示。它有控制电路模块、发送控制模块和接收控制模块三部分组成。CPU通过对控制电路模块中的寄存器进行设置达到对内部电路的控制和管理,从而实现UART和CPU以及其它UART模块间的数据收发功能。3,整个模块的外部接口 图3.1 UART IP外部接口 4,子模块说明 (一)控制电路模块 该模块的主要功能为:a、与CPU接口,将CPU对内部控制寄存器的写操作转化

为对发送控制器和接收控制器的控制信号;b、将CPU写入到内部数据发送寄存器的数据进行锁存并提供给发送控制器;c、将接收控制器接收的数据提交给CPU,同时提交接收数据的状态信息;d、对收、发控制器的中断进行管理。对于中断寄存器的读操作同时对寄存器清零,以避免重复产生中断,这需要专门的电路进行维护和管理。 (二)发送控制模块 该模块的主要功能为:a、根据clk_div_ctl给出的时钟分频比将xmt_data上的数据按照从低位到高位的顺序依次发出。在数据发送过程中需要根据规范插入起始位、奇偶校验位和停止位。b、发送控制器在xmt_en为高电平时开始向线路方向发送数据。完成当前字节发送后通过xmt_over通知控制电路当前发送完成,由控制电路负责产生中断和进行中断管理。 发送控制模块的仿真波形如下: 图4.1发送控制模块仿真波形 a.当发送状态机处于idle状态时,如果xmt _en有效则产生一个clk_cnt_clr 信号,用于对时钟计数器清零,同时进入start状态,见图4.1中“1”处。 b.在start状态下,如果sample有效则输出起始位,同时进入data状态,见图 4.1中“2”处。 c.在data状态下,在sample有效时连续输出8位数据。最后一个比特开始输出后进入parity状态,准备输出奇偶校验位,,见图4.1中“3”处。 d.在parity状态下,如果出现sample则进入stop状态,在stop状态下如果sample有效则输出截止位,并进入waiting状态,见图4.1中“4”处。 e.在waiting状态下,截止位保持有效,并在sample有效时进入idle状态,sdout 持续为1,见图4.1中“5”处。 f在由waiting进入idle状态时,输出xmt_over信号,通知控制电路当前数据发送完成。注意这里的xmt_over信号只是在一个时钟周期内保持有效,见图4.1中“6”处. (三)接收控制模块 该模块的主要功能为:a、检测接收数据中的起始位,并完整地接收数据。b、根

UART串口通信设计实例

2.5 UART串口通信设计实例(1) 接下来用刚才采用的方法设计一个典型实例。在一般的嵌入式开发和FPGA设计中,串口UART是使用非常频繁的一种调试手段。下面我们将使用Verilog RTL编程设计一个串口收发模块。这个实例虽然简单,但是在后续的调试开发中,串口使用的次数比较多,这里阐明它的设计方案,不仅仅是为了讲解RTL编程,而且为了后续使用兼容ARM9内核实现嵌入式开发。 串口在一般的台式机上都会有。随着笔记本电脑的使用,一般会采用USB转串口的方案虚拟一个串口供笔记本使用。图2-7为UART串口的结构图。串口具有9个引脚,但是真正连接入FPGA开发板的一般只有两个引脚。这两个引脚是:发送引脚TxD和接收引脚RxD。由于是串行发送数据,因此如果开发板发送数据的话,则要通过TxD线1 bit接着1 bit 发送。在接收时,同样通过RxD引脚1 bit接着1 bit接收。 再看看串口发送/接收的数据格式(见图2-8)。在TxD或RxD这样的单线上,是从一个周期的低电平开始,以一个周期的高电平结束的。它中间包含8个周期的数据位和一个周期针对8位数据的奇偶校验位。每次传送一字节数据,它包含的8位是由低位开始传送,最后一位传送的是第7位。

这个设计有两个目的:一是从串口中接收数据,发送到输出端口。接收的时候是串行的,也就是一个接一个的;但是发送到输出端口时,我们希望是8位放在一起,成为并行状态(见图2-10)。我们知道,串口中出现信号,是没有先兆的。如果出现了串行数据,则如何通知到输出端口呢?我们引入“接收有效”端口。“接收有效”端口在一般情况下都是低电平,一旦有数据到来时,它就变成高电平。下一个模块在得知“接收有效”信号为高电平时,它就明白:新到了一个字节的数据,放在“接收字节”端口里面。

UART原理及接受模块设计

2 UART 原理 2.1 UART 的通信原理 UART 即通用异步收发器,是一种串行通信方式。数据在传输过程中是通过一位一位地进行传输来实现通信的,串行通信方式具有传输线少,成本底等优点,缺点是速度慢。串行通信分为两种类型:同步通信方式和异步通信方式。但一般多用异步通信方式,主要因为接受和发送的时钟是可以独立的这样有利于增加发送与接收的灵活性。异步通信是一个字符接着一个字符传输,一个字符的信息由起始位、数据位、奇偶校验位和停止位组成。每一个字符的传输靠起始位来同步,字符的前面一位是起始位,用下降沿通知收方开始传输,紧接着起始位之后的是数据位,传输时低位在前高位在后,字符本身由5~8位数据位组成。数据位后面是奇偶校验位,最后是停止位,停止位是用高电平来标记一个字符的结束,并为下一个字符的传输做准备。停止位后面是不同长度的空闲位。停止位和空闲位都规定为高电平,这样可以保证起始位有一个下降沿。UART 的帧格式如图2.1所示。 图2.1 UART 的帧格式 Figure 2.1 The frame format of UART UART 的帧格式包括线路空闲状态(idle ,高电平)、起始位(start bit ,低电平)、5~8位数据位(data bits)、校验位(parity bit ,可选)和停止位(stop bit ,位数可为1、1.5、2位)。 在串口的异步通信中,数据以字节为单位的字节帧进行传送。发送端和接收端必须按照相同的字节帧格式和波特率进行通信。其中字节帧格式规定了起始位、数据位、寄偶效验位、停止位。起始位是字节帧的开始。使数据线处于逻辑0状态 ,用于向接收端表明开始发送数据帧,起到使发送和接收设备实现同步。停止位是字节帧的终止,使数据线处于逻辑1状态。用于向接收端表明数据帧发送完毕。波特率采用标准速度9600bit/s 。

FPGA的UART完整设计

第三章UART设计 3、1 UART得帧格式 在UART 中,数据位就是以字符为传送单位,数据得前、后要有起始位、停止位,另外可以在停止位得前面加上一个比特(bit)得校验位。其帧格式如图所示。 文章通过分析UART得功能,利用有限状态机来描述UART核心控制逻辑得方法,将其核心功能集成,从而使整个设计更加稳定、可靠。基本得UART通信只需要两条信号线就可以完成数据得相互通信。UART得功能模块如图3_2所示。

3、2 UART模块 在大规模电路得设计中,广泛采用层次化,结构化得设计方法。它将一个完整得硬件设计任务从系统级开始,划分为若干个可操作得模块,编制出相应得模型并进行仿真验证,最后在系统级上进行组合。这样在提高设计效率得同时又提高了设计质量,就是目前复杂数字系统实现得主要手段,也就是本文设计思想得基础。其系统模块可划分为4个部分,如波特发生器,控制器,接收器,发送器,如图3-3所示: 3 Data_in:并行输入data_out:并行输出 Cs:通知cpu接收数据位ks:通知cpu发送准备位 Reset:重启输入state:uart状态输入 Clk:48M时钟输入

3、2、2UART主体程序 `timescale 1ns/1ns module gs_opt( input wire read, input wire clk, input wire reset, input wire state, input wire [7:0] dat_in, output wire send, output wire cs, output wire ks, output wire [7:0] dat_out ); wire send_enable; wire read_enable; wire clk_enable3; wire clk_enable4; wire clear3 ; wire clear4 ; wire clk_enable; wire [7:0] counters; wire clear ; wire t1; /* read,send,cs,ks,reset,state,clk,dat_in,dat_out); //module uart(read,send,cs,ks,reset,state,clk,dat_in,dat_out); input read,clk,reset,state; //read为串行输入,clk为时钟输入50MHZ,reset为重启键input[7:0] dat_in;//并行数据输入 output send,cs,ks; //send为串行输出,cs为通知cpu接收数据位,ks为发送准备位output[7:0] dat_out;//并行数据输出 wire clear,clk_enable,read_enable,clear3,send_enable,clear4,t1; wire[7:0] counters,dat_in;*/

UART收发器设计实例

11.5U A R T收发器设计实例 U A R T(U n i v e r s a l A s y n c h r o n o u s R e c e i v e r T r a n s m i t t e r,通用异步收发器)是广泛使用的异步串行数据通信协议。下面首先介绍U A R T硬件接口及电平转换电路,分析U A R T的传输时序并利用V e r i l o g H D L语言进行建模与仿真,最后通过开发板与P C相连进行R S-232通信来测试U A R T收发器的正确性。 1.5.111.5.1U A R T界面介绍 本节所介绍的U A R T即美国电子工业协会定义的R S-232C,简称R S-232。R S-232的接口一般有9针的D B9和25针的D B25,这里以9针为例,它的各个引脚的定义如表11-8所示。 表11-8D B9的引脚定义 引脚功能缩写 1资料载波检测D C D 2接收数据R X D 3发送数据T X D 4数据终端准备就绪D T R 5信号地G N D 6数据准备就绪D S R 7发送请求R T S 8清除发送C T S 9振铃提示R I 由于R S-232的电气特性与F P G A引脚不相同,因此它们之间不能直接相连,对于R S-232的数据线,当为逻辑“1”时,对应电平是-15V~-3V;当为逻辑“0”时,对应电平是15V~3V。因此,与F P G A相连之前必须进行电平转换,转换原理图如图11-39所示。

图11-39R S-232电平转换原理图 1.5.211.5.2U A R T传输时序 U A R T传输时序如图11-40所示。 图11-40U A R T传输时序 发送数据过程:空闲状态,线路处于高电位;当收到发送数据指令后,拉低线路一个数据位的时间T,接着数据按低位到高位依次发送,数据发送完毕后,接着发送奇偶校验位和停止位(停止位为高电位),一帧资料发送结束。 接收数据过程:空闲状态,线路处于高电位;当检测到线路的下降沿(线路电位由高电位变为低电位)时说明线路有数据传输,按照约定的波特率从低位到高位接收数据,数据接收完毕后,接着接收并比较奇偶校验位是否正确,如果正确则通知后续设备准备接收数据或存入缓存。 由于U A R T是异步传输,没有传输同步时钟。为了能保证数据传输的正确性, U A R T采用16倍数据波特率的时钟进行采样。每个数据有16个时钟采样,取中

UART原理及接收模块设计原理

UART 原理 2.1 UART 的通信原理 UART 即通用异步收发器,是一种串行通信方式。数据在传输过程中是通过一位一位地进行传输来实现通信的,串行通信方式具有传输线少,成本底等优点,缺点是速度慢。串行通信分为两种类型:同步通信方式和异步通信方式。但一般多用异步通信方式,主要因为接受和发送的时钟是可以独立的这样有利于增加发送与接收的灵活性。异步通信是一个字符接着一个字符传输,一个字符的信息由起始位、数据位、奇偶校验位和停止位组成。每一个字符的传输靠起始位来同步,字符的前面一位是起始位,用下降沿通知收方开始传输,紧接着起始位之后的是数据位,传输时低位在前高位在后,字符本身由5~8位数据位组成。数据位后面是奇偶校验位,最后是停止位,停止位是用高电平来标记一个字符的结束,并为下一个字符的传输做准备。停止位后面是不同长度的空闲位。停止位和空闲位都规定为高电平,这样可以保证起始位有一个下降沿。UART 的帧格式如图2.1所示。 图2.1 UART 的帧格式 Figure 2.1 The frame format of UART UART 的帧格式包括线路空闲状态(idle ,高电平)、起始位(start bit ,低电平)、5~8位数据位(data bits)、校验位(parity bit ,可选)和停止位(stop bit ,位数可为1、1.5、2位)。 在串口的异步通信中,数据以字节为单位的字节帧进行传送。发送端和接收端必须按照相同的字节帧格式和波特率进行通信。其中字节帧格式规定了起始位、数据位、寄偶效验位、停止位。起始位是字节帧的开始。使数据线处于逻辑0状态 ,用于向接收端表明开始发送数据帧,起到使发送和接收设备实现同步。停止位是字节帧的终止,使数据线处于逻辑1状态。用于向接收端表明数据帧发送完毕。波特率采用标准速度9600bit/s 。

FPGA的UART完整设计说明

第三章UART设计 3.1 UART的帧格式 在UART 中,数据位是以字符为传送单位,数据的前、后要有起始位、停止位,另外可以在停止位的前面加上一个比特(bit)的校验位。其帧格式如图所示。 数据位 起始位D0 D1 D2 D3 ——————D7 校验位停止位 以9600波特率接收或发送,每一位时间为 1/9600秒,或48MHZ晶振5000次计数 图3_1数据帧格式 文章通过分析UART的功能,利用有限状态机来描述UART核心控制逻辑的方法,将其核心功能集成,从而使整个设计更加稳定、可靠。基本的UART 通信只需要两条信号线就可以完成数据的相互通信。UART的功能模块如图3_2所示。

波特发生器 Uart控制器 接收模块发送模块 对象模块 图3_2UART的功能模块图

3.2 UART模块 在大规模电路的设计中,广泛采用层次化,结构化的设计方法。它将一个完整的硬件设计任务从系统级开始,划分为若干个可操作的模块,编制出相应的模型并进行仿真验证,最后在系统级上进行组合。这样在提高设计效率的同时又提高了设计质量,是目前复杂数字系统实现的主要手段,也是本文设计思想的基础。 其系统模块可划分为4个部分,如波特发生器,控制器,接收器,发送器,如图3-3所示: read send clear_check read send Clr3 clr4 ks cs Data_in Data_out clear Read_enable send_enable counters counters reset Counters(control) state T1 clk_enable Clk_clear Clk(波特发生器) clk

八位MCU的UART设计

八位MCU的UART设计 UART是用来将传输数据由并行格式转变成串行格式,或将传输数据由串行 格式转变成并行格式。单片机的功能越来越强大,应用性越来越强,应用范围也越来越广,基于应用过程中通信的需求,现在绝大部分MCU芯片也都集成有UART功能。如果MCU芯片中没有集成UART,通信时则需要软件实现UART功能,这将占用CPU时间而且比硬件实现UART价格高,而且这使得MCU芯片与别的处理器之间进行的数据传输变得比较复杂。 为了使MCU在进行通信时有着很高的灵活性,我们可以在进行MCU的设计时就直接集成UART模块,并能保证可靠性和稳定性。现在数字IC的设计基本上都是采用自顶向下的设计方法,编写硬件描述语言对硬件功能逐层的进行描述,利 用仿真软件对设计进行逐层的功能验证。在前仿真没有问题后,就可以用综合工具将其中需转变为具体电路的模块组合综合到器件库所对应的门级电路网表。 然后,利用自动布局布线工具再将网表转换为需要实现的实际电路布线结构。在进行数据通信时,要遵循数据通信协议,这样才能保证数据通信的正确性与可 靠性。在进行接收数据时,UART对外部串行发送来的数据进行接收,在接收完成 时产生接收中断标志,并将传输数据由串行格式转变成并行格式,还可验证接收 到数据的正确性。 在进行数据的发送时,UART会将从发送缓冲寄存器读取的并行数据转变成 串行格式,并在一帧有效数据前附加上一位起始位,在有效数据位之后加上一位 可选的奇偶校验位和一位停止位,并在发送完成时产生发送中断标志,可以验证 发送数据的正确性。本文所设计的UART是集成在一个8位单片机上一个模块, 拥有高精度的波特率发生器。该UART有四种工作模式可供选择,以满足不同应用

FPGA的UART完整设计

UART设计 第三章UART设计 3.1 UART的帧格式 在UART 中,数据位是以字符为传送单位,数据的前、后要有起始位、停止位,另外可以在停止位的前面加上一个比特(bit)的校验位。其帧格式如图所示。 数据位 起始位D0 D1 D2 D3 ——————D7 校验位停止位 以9600波特率接收或发送,每一位时间为 1/9600秒,或48MHZ晶振5000次计数 图3_1数据帧格式 文章通过分析UART的功能,利用有限状态机来描述UART核心控制逻辑的方法,将其核心功能集成,从而使整个设计更加稳定、可靠。基本的UART 通信只需要两条信号线就可以完成数据的相互通信。UART的功能模块如图3_2所示。 波特发生器 Uart控制器 接收模块发送模块 对象模块 图3_2UART的功能模块图

3.2 UART 模块 在大规模电路的设计中,广泛采用层次化,结构化的设计方法。它将一个完整的硬件设计任务从系统级开始,划分为若干个可操作的模块,编制出相应的模型并进行仿真验证,最后在系统级上进行组合。这样在提高设计效率的同时又提高了设计质量,是目前复杂数字系统实现的主要手段,也是本文设计思想的基础。 其系统模块可划分为4个部分,如波特发生器,控制器,接收器,发送器,如图3-3所示: read send Clr3 clr4 ks cs Data_in Data_out clear Read_enable send_enable counters counters reset Counters(control) state T1 clk_enable Clk_clear Clk(波特发生器) clk 图3-3uart 结构图 3.2.1主要引脚功能介绍 Read:串行输入 send:串行输出 Data_in:并行输入 data_out:并行输出 Cs:通知cpu 接收数据位 ks:通知cpu 发送准备位 Reset:重启输入 state:uart 状态输入 Clk:48M 时钟输入 read send clear_check

基于FPGA的UART设计

郑州轻工业学院 课程设计说明书题目:基于FPGA的UART设计 姓名:王鹏飞 院(系):电子信息工程学院 专业班级:电子信息工程13-01 学号:0135 指导教师:杜海明 成绩: 时间:2016年6月21日至2016年6月28日

郑州轻工业学院 课程设计任务书 题目基于FPGA的UART设计 专业、班级电子信息工程13-01学号 35 姓名王鹏飞 主要内容、基本要求、主要参考资料等: 主要内容: 要求学生使用硬件描述语言描述硬件功能,利用FPGA并采用模块化设计方法设计UART(通用异步收发器)的各个模块。其中包括波特发生器,程序控制器,UART数据接收器和UART数据发送器,本文采用的外部时钟为48MHZ,波特率为9600。在软件上进行设计、编译和仿真。 基本要求: 1、掌握FPGA 的程序设计方法。 2、掌握硬件描述语言语法。 3、程序设计完成后要求在软件中实现功能仿真。 主要参考资料: 1、夏宇闻. Verilog 数字系统设计教程[M].北京:北京航空航天大学出版社,2003 2、潘松,王国栋.VHDL实用教程「M].成都:电子科技大学出版社,2003. 完成期限:—指导教师签名: 课程负责人签名: 2016年6月18日

基于FPGA的UART设计 摘要 UART作为RS232协议的控制接口得到了广泛的应用,将UART的功能集成到FPGA 芯片中,可使整个系统更为灵活、紧凑,减小整个电路的体积,提高系统的可靠性和稳定性。提出了一种基于FPGA的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。 关键词FPGA UART模块化有限状态机

单片机软件UART的设计资料

单片机软件UART的设计资料 目前扩展串口的方法主要有以下方法, ①、采用串 口扩展芯片实现,如ST16C550、ST16C554、SP2538、MAX3110等,虽然成本较高, 但系统的可靠性得到了保证,适用于数据量较大、串口需求较多的系统;②、采用分时切换的方法将一个串口扩展与多个串口设备通信, 分时复用的方法成本低, 但只适用于数据量不大的场合, 并且只能由这个单片机主动和多个设备通信,实时性 差;③、用软件模拟的方法扩展串口,其优势也是成本低、实时性好, 但要占用一些CPU时间。 一般的软件模拟扩展串口方法,使用1个I/O端口、1个INT外部中断和定时器,该方法扩展的串口有2个缺点,①、由于使用了INT外部中断,故只能使用2个INT外部中断扩展2个串口。②、文中的发送和接收数据的效率 比较低,占用了CPU的大量时间,不能与其他任务同时 进行,所以使用范围有限。 本文提出的模拟串口方法,仅使用2个普通I/O和1 个定时器,由于不需要INT的限制,可以扩展出多个串口,且带FIFO的功能,该方法扩展模拟串口的收发数据在中断服务中完成,所以非常效率高,一般的单片机都 支持定时器中断,所以所以该方法在大多数单片机上都

可以应用。 对于低速度的单片机(如89S51)可以扩展出低速串口(9600、4800等),对于高速单片机(如AVR、PIC、C8051、STC12)可以扩展高速串口(如19200、28800、38400、57600等)。目前单片机的处理速度越来越高,而价格越 来越便宜,本文使用的STC12C1052芯片就具有高速度和低价格,价格仅为每片人民币3.8元。电子产品的开发 设计时,要求在保证性能的情况下降低硬件成本,软件 模拟扩展串口提供了一种降低成本的好方法。 1、串口通讯原理 在串口的异步通信中,数据以字节为单位的字节帧进行传送,发送端和接收端必须按照相同的字节帧格式和 波特率进行通信,其中字节帧格式规定了起始位、数据位、寄偶效验位、停止位。起始位是字节帧的开始,使 数据线处于逻辑0状态,用于向接收端表明开始发送数 据帧,起到使发送和接收设备实现同步。停止位是字节 帧的终止,使数据线处于逻辑1状态,用于向接收端表 明数据帧发送完毕。波特率采用标准速度,如4800、9600、19200、28800、38400、57600等。 2、软件UART的设计思想 在本设计对硬件要求方面,仅仅占用单片机的任意2 个I/O端口和1个定时器,利用定时器的定时中断功能实

Uart串口设计

Uart串口设计总结及实验 QinZhanAo 1.串口说明 电脑上通常位Rs232口,为9针口,可以在机箱后面找到。现在基本上都用USB转串口来实现串口的功能,需要注意的是,如果用USB转串口来实现串口功能的话,需要下载安装USB转串口驱动,否则不能实现。台式机可以直接用串口线来实现,而一般笔记本已经没有串口了,那么必须用USB转串口。 2.串口发端设计 2.1发端时序 串口发送数据端的时序如下图所示。 从时序图上可以看出,需要发送的数据低位先发出去,在发送数据之前,需要先发送一个开始特征比特,值为0,TXD数据线空闲状态为1。发送完数据最高位后发送一个停止比特,值为1。 2.2 设计思路 设计时钟: 根据前述的SPI模块设计时提出的一个思想:所有低速接口时钟都以进入接口时钟的2分频时钟来进行发送或者采样。 这里需要的波特率是38400Hz,那么进入串口发送模块的时钟为76800Hz,板上时钟50MHz,也就是需要进行652分频,分频计数为(652/2)- 1 = 325,计数值计到324即时钟翻转。 验证实验: 利用板上的两个按键,sw1按一下,计数值加1,并通过串口调试助手显示,sw2使得计数清零。 2.3 源码公布 发送端IP:

Uart Tx顶层源码:

2.4 功能仿真 功能仿真波形如下: 2.5 上板调试结果显示

3.串口接收端设计 3.1 接收端时序 串口接收端时序图如下: 由时序图可知,收端先收数据的低位直到收到停止位,RXD线空闲电平为高,直到检测到一个低电平开始采样数据。 3.2 串口接收端设计 时钟设计: 和发送端一样,采用时钟是进入接收端模块时钟的2分频,这样能保证采样时刻在数值的中间,避免了亚稳态等问题。 设计时序: 发送模块偷了个懒没有给出设计时序图,这里给下设计之初的接收模块的时序图,如上图所示。slot是最下面的红色的那个,蓝色的那个slot画错了。 验证设计: 这里因为只有4个led,所以设计验证是通过串口助手发送数通过4个led的二进

基于FPGA的UART设计

一、题目 基于FPGA的UART设计 二、设计要求 1)支持数据格式:起始位(1bit)+数据(8bit)+奇偶校验位(1bit)+终止位(1bit)2)奇/偶校验可配置 3)可配置支持115200以下的常见波特率 4)支持115200以下的波特率自适应,自适应过程如下: a.复位后,UART首先接收输入,不断自动调整波特率,直到以一定波特率正确连 续接收到3个bytes的0x55 b.接着UART以此波特率连续发送3个bytes 0xaa c.之后两端以此波特率进行通信 d.波特率自适应只在电路复位后进行一次,如欲再次自适应波特率应对电路再次 复位 e.波特率自适应过程中不能对UART的波特率作任何设置,自适应完成后可以对 波特率作设置 5)自动计算校验位用于发送数据;对接收到的校验位和数据进行校验,发现错误应设置错误标志,并丢弃数据 6)对接收不正常数据(如无终止位、无校验位、数据位数不正确等)应能自动识别并设置错误标志、丢弃 三、UART 的工作原理 异步通信时,UART发送/接收数据的传输格式如图1所示,一个字符单位由开始位、数据位、停止位组成。 异步通信的一帧传输经历以下步骤: (1)无传输。发送方连续发送信号,处于信息“1”状态。 (2)起始传输。发送方在任何时刻将传号变成空号,即“1”跳变到“0”,并持续1位 时间表明发送方开始传输数据。而同时,接收方收到空号后,开始与发送方同步,并期望收到随后的数据。 (3)奇偶传输。数据传输之后是可供选择的奇偶位发送或接收。 (4)停止传输。最后是发送或接收的停止位,其状态恒为“1”。 发送或接收一个完整的字节信息,首先是一个作为起始位的逻辑“0”位,接着是8个数据位,然后是停止位逻辑“1”位,数据线空闲时为高或“1”状态。起始位和停止位的作用是使接收器能把局部时钟与每个新开始接收的字符再同步。异步通信没有可参

UART控制器设计

西安电子科技大学 可编程逻辑器件原理、应用与实验课程实验报告 实验名称UART控制器设计及验证 研究生院学院代培生班Array姓名学号 同作者 实验日期2017 年 4 月23日

目录 一任务简介 (1) 1.1 实验目的 (1) 1.2 开发工具平台 (1) 二模块设计 (2) 2.1输入模块设计 (2) 2.1.1机械按键消抖 (2) 2.1.2矩阵键盘扫描 (3) 2.1.3参量输入及显示输入 (5) 2.2显示模块 (6) 2.3三态门控制模块 (8) 2.4 UART通信协议帧格式及波特率设置 (9) 2.5 UART通信模块 (10) 2.5.1串口数据发送模块 (11) 2.5.2串口数据接收模块 (12) 三系统介绍 (13) 3.1系统结构介绍 (13) 3.2系统子模块介绍 (15) 3.3 开发板实验结果 (17) 四总结 (20)

一任务简介 1.1实验目的 本次任务的目标为设计一个基于FPGA的串口通信控制器,具体技术要求如下: (1) 实现与PC的双向通信; (2) 可以通过输入模块在开发板上定义向PC发送的数据; (3) 数据帧长度可调(6/7/8位); (4) 通信波特率可调; (5) 在数码管上实现波特率、输入数据、接收数据的显示。 (6) 按键A用于接收模式和输入模式的选择,按键B用于选择输入模式为波特率设置 还是发送数据设置,按键C为发送确认键,按键D用于选择数据帧长度,矩阵键盘(0~9)用于输入波特率因子和发送数据(十六进制显示);各种模式均有数码管显示相应内容,其中数据帧长度由四个LED灯表示。 (7) 操作流程: 1. 通信参数设置:在开发板上选择数据帧长度、设置波特率、输入发送数据帧;在PC端的串口通信助手中设置波特率和数据帧长度; 2. 数据发送:按下C键向PC发送数据,在PC端确认接收的数据; 3. 数据接收:由PC端向开发板发送数据,在开发板上选择数据接收模式即可显示; 4. 默认设置:UART控制器默认波特率为9600,默认发送数据为8?h18; (8) 以上内容均需在开发板上验证;实验截图在本文第三部分给出。 1.2 开发工具平台 (1)基于CycloneII EP2C5Q208C8核心的MAGIC3200_EP2C5开发板,具有四位扫描式数码管,RS232串口等外设,时钟CLK为50MHz; (2)开发软件为Quartus II 13sp; (3)串口通信助手; (4)基于LP2303的USB-UART转接线,用于与笔记本电脑进行串口通信。 MAGIC3200_EP2C5开发板USB-UART转接线

基于FPGA的UART串口接收模块设计.pdf

UART串口接收模块设计 实验目标:实现FPGA接收其他设备通过UART协议发送过来的数据。 知识点: 1、URAT通信协议工业环境下数据接收实现。 2、In system sources and probes editor(ISSP)调试工具的使用。 UART发送端发送一个字节数据时序图: 对于其中的每一位进行采样,一般情况下每一位数据的中间点是最稳定的,因此一般应用中, : 采集中间时刻时的数据即可,如下图所示 但是在工业应用中,往往有非常强的电磁干扰,只采样一次就作为该数据的电平判定,是不保险的,有可能恰好采集到被干扰的信号而导致结果出错,因此需要使用多次采样求概率的方式进行。 以下为改进型的单bit数据接收方式示意图: 12345678910111213141516 在这张图中,将每一位数据又平均分成了16小段,对于Bit_x这一位数据,考虑到数据在刚刚发生变化和即将发生变化的这一时期,数据极有可能不稳定的(用红色标出的两段),在这两个时间段采集数据,很有可能得到错误的结果,因此这两段时间的电平无效,采集时直接忽略。而中间这一时间段(用绿色标出),

数据本身是比较稳定的,一般都代表了正确的结果。但是也不排除该段数据受强电磁干扰而出现错误的电平脉冲,因此对这一段电平,进行多次采样,并求高低电平发生的概率,6次采集结果中,取出现次数多的电平作为采样结果。例如,采样6次的结果分别为1/1/1/1/0/1/,则取电平结果为1,若为0/0/1/0/0/0,,则取电平结果为0,当6次采样结果中1和0各占一半(各3次),则可判断当前通信线路环境非常恶劣,数据不具有可靠性。 串口发送模块包含两个主要组件: 1、起始位检测进程(低电平,下降沿) 2、波特率产生模块 3、数据接收模块 串口接收模块整体结构图: 波特率时钟计算:

UART课程设计

课程设计——题目:UART的设计与实现 2012 年10月20 日

摘要 本文对通用异步收发器——UART进行了概述,描述了UART的功能以及模块化的设计思路,给出了设计的VHDL语言程序,并进行了相应的仿真验证。 摘要 16页空? 目录 字号:正文小四号 注意空白与图片大小

第一章设计要求 整个课程设计的要求如下: a.采用8位宽的数据总线,16位宽的地址总线; b.具有完整的数据收发功能,且波特率可调; c.8位数据位、1位奇校验位、1位停止位; d.一级数据缓冲; e.具备奇校验检错功能;

第二章原理概述 一、UART的整体框图 异步收发器的原理框图如图1-1所示。 图1-1 二、UART的原理 (一)UART简述 UART即Universal Asynchronous Receiver Transmitter通用异步收发器,是一种应广泛的短距离串行传输接口。往往用于短距离、低速、低成本的微机与下拉机的通讯中。8250、8251、NS16450等芯片都是常见的UART器件。 “异步”指不需要额外的时钟线进行数据的同步传输,是一种串行总线接口,只需占用两根线就可以完成数据的收发(一根接收数据,

一根发送数据)。常用的传输率有4800bps、9600bps、19200bps和115200bps等。 (二)基本帧格式 1.基本概念 ①在信号线上有两种状态,可分别用逻辑1和逻辑0来区分。在发送空闲时,数据线应保持在逻辑1状态; ②起始位。发送器是通过发送起始位而开始一个字符传送,起始位使数据线处于逻辑0状态,提示接收器数据传输即将开始; ③数据位。起始位之后就是传送数据位。数据位一般为一个字节的数据(也有6位、7位的情况),低位(LSB)在前,高位(MSB)在后; ④校验位。可以认为是一个特殊的数据位。校验位一般用来判断接收的数据位有无错误,一般是奇偶校验。本课程设计里,UART 使用1比特的奇校验位; ⑤停止位。停止位在最后,用以标志一个字符传送的结束,它对应于逻辑1状态; ⑥位时间。即每个位的时间宽度。起始位、数据位、校验位的位宽度是一致的,停止位有0.5位、1位、1.5位格式,一般为1位; ⑦帧。从起始位开始到停止位结束的时间间隔称之为一帧; ⑧波特率。UART的传送速率,用于说明数据传送的快慢。在串行通信中,数据是按位进行传送的,因此传送速率用每秒钟传送数据位的数目来表示,称之为波特率。

UART串口学习笔记

UART总线 UART (Universal Asynchronous Receiver/Transmitter) 通用异步收发器。 UART是用于控制计算机与串行设备的芯片。有一点要注意的是,它提供了RS-232C数据终端设备接口,这样计算机就可以和调制解调器或其它使用RS-232C接口的串行设备通信了。 作为接口的一部分,UART还提供以下功能:将由计算机内部传送过来的并行数据转换为输出的串行数据流。将计算机外部来的串行数据转换为字节,供计算机内部使用并行数据的器件使用。在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验。在输出数据流中加入启停标记,并从接收数据流中删除启停标记。处理由键盘或鼠标发出的中断信号(键盘和鼠票也是串行设备)。可以处理计算机与外部串行设备的同步管理问题。有一些比较高档的UART还提供输入输出数据的缓冲区,现在比较新的UART是16550,它可以在计算机需要处理数据前在其缓冲区内存储16字节数据,而通常的UART是8250。现在如果您购买一个内置的调制解调器,此调制解调器内部通常就会有16550 UART。 UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。在嵌入式设计中,UART用来与PC进行通信,包括与监控调试器和其它器件,如EEPROM通信。 UART通信 UART首先将接收到的并行数据转换成串行数据来传输。消息帧从一个低位起始位开始,后面是7个或8个数据位,一个可用的奇偶位和一个或几个高位停止位。接收器发现开始位时它就知道数据准备发送,并尝试与发送器时钟频率同步。如果选择了奇偶,UART就在数据位后面加上奇偶位。奇偶位可用来帮助错误校验。

基于FPGA的UART设计与实现

基于FPGA的UART设计与实现 时间:2010-08-09 07:08:53 来源:现代电子技术作者:何勇 0 引言 通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)可以和各种标准串行接口,如RS 232和RS 485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。一般UART由专用芯片如8250,16450来实现,但专用芯片引脚都较多,内含许多辅助功能,在实际使用时往往只需要用到UART的基本功能,使用专用芯片会造成资源浪费和成本提高。 一般而言UART和外界通信只需要两条信号线RXD和TXD,其中RXD是UART的接收端,TXD是UART的发送端,接收与发送是全双工形式。由于可编程逻辑器件技术的快速发展,FPGA的功能日益强大,其开发周期短、可重复编程的优点也越来越明显,在FPGA芯片上集成UART功能模块并和其他模块组合可以很方便地实现一个能与其他设备进行串行通信的片上系统。 1 UART功能设计 1.1 UART的工作原理 异步通信时,UART发送/接收数据的传输格式如图1所示,一个字符单位由开始位、数据位、停止位组成。 异步通信的一帧传输经历以下步骤: (1)无传输。发送方连续发送信号,处于信息“1”状态。 (2)起始传输。发送方在任何时刻将传号变成空号,即“1”跳变到“O”,并持续1位时间表明发送方开始传输数据。而同时,接收方收到空号后,开始与发送方同步,并期望收到随后的数据。 (3)奇偶传输。数据传输之后是可供选择的奇偶位发送或接收。 (4)停止传输。最后是发送或接收的停止位,其状态恒为“1”。 发送或接收一个完整的字节信息,首先是一个作为起始位的逻辑“0”位,接着是8个数据位,然后是停止位逻辑“1”位,数据线空闲时为高或“1”状态。起始位和停止位的作用是使接收器能把局部时钟与每个新开始接收的字符再同步。异步通信没有可参照的时钟信号,发送器可以随时发送数据,任何时刻串行数据到来时,接收器必须准确地发现起始位下降沿的出现时间,从而正确采样数据。 设计时可参考由专用芯片实现的UART的功能并进行一定精简,如可以用FPGA的片内RAM替代UART的FIFO,不用单独在UART模块中实现。设计的基本原则是保留最主要的功能,

Altium教程Simple UART LH79520软件设计B1

Logic Zoom SDK - Simple UART - LH79520软件设计 第一部分 原理图 1.1Logic Zoom SDK - Simple UART.SchDoc U20

1.2hardware.c /********************************************************************\ |* |* Version : 1.0 |* |* Copyright : Copyright (C) 2006, PurPer |* |* Description : This project uses the serial interface of the Logic |* Zoom development board to output a message and echo |* some text to an HyperTerminal interface for example. |* \********************************************************************/ #include "hardware.h" #include