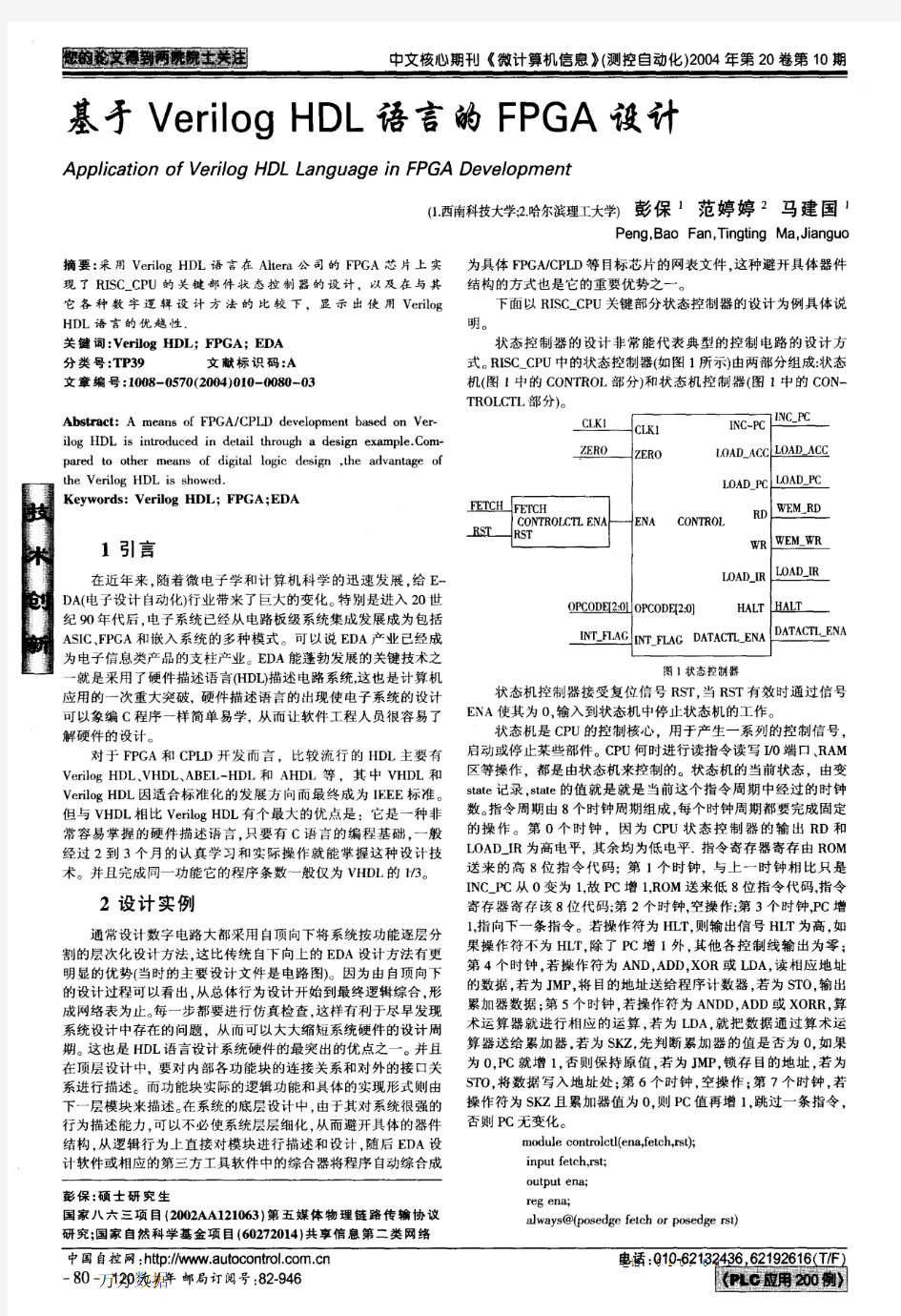

基于Verilog+HDL语言的FPGA设计

万方数据

万方数据

万方数据

基于Verilog HDL语言的FPGA设计

作者:彭保, 范婷婷, 马建国

作者单位:彭保,马建国(621002,四川绵阳西南科技大学信控学院), 范婷婷(150090,哈尔滨,哈尔滨理工大学)

刊名:

微计算机信息

英文刊名:CONTROL & AUTOMATION

年,卷(期):2004,20(10)

被引用次数:10次

参考文献(4条)

1.夏宇闻Verilog数字系统设计教程 2003

2.候伯亨;顾新VHDL硬件描述语言与数字逻辑电路设计 1997

3.王诚;薛小刚;钟信潮FPGA/CPLD设计具XILINX ISE5.X使用详解 2003

4.夏宇闻复杂数字电路与系统的Verilog HDL设计 1998

相似文献(10条)

1.期刊论文李桂林.苗长新.Li Guilin.Miao Changxin基于Verilog HDL的FPGA数字系统设计优化-计算机与数字工程2010,38(8)

文章介绍了基于FPGA的数字系统设计优化的两种重要技术:流水线设计技术和资源共享设计技术,并通过两个具体的示例,详细说明了如何利用Verilog HDL语言来编写优化程序,并通过定时分析及资源耗用结果对比分析了优化设计前后电路在速度与资源利用率等性能指标上的差别.

2.期刊论文田佳.王一平.TIAN Jia.WANG Yi-ping基于FPGA的带CRC校验的异步串口通信-现代电子技术

2010,33(20)

由于FPGA具有速度快.效率高,灵活稳定.集成度高等优点,所以为了提高串口通信的速度和效率,在串行通信中采用FPGA来实现串口通信是十分必要的.由于通信传输的不确定性以及干扰等原因,串行通信经常会出现异常情况.然而,在串行通信中添加CRC校验,可以提高通信的可靠性.采用Verilog HDL设计的一个带CRC校验的串口通信程序,对其下栽到FPGA芯片中进行实验验证,得到的结论是用FPGA进行串口通信,可大大提高通信的速度和效率,且CRC校验确保了通信的准确性及卡可靠性.

3.期刊论文谭安菊.龚彬.TAN Anju.GONG Bin USB2.0控制器CY7C68013与FPGA接口的Verilog HDL实现-电子工程师2007,33(7)

USB(通用串行总线)控制器CY7C68013因其数据传输速率快和多样的接口方式为ATA、FPGA(现场可编程门阵列)和DSP(数字信号处理器)等提供了简单和无缝连接接口而得到广泛使用,介绍了此控制器与FPGA接口的控制和HDL(硬件描述语言)实现方法.利用CY7C68013控制器的Slave FIFO从机方式,用Verilog HDL在FPGA中产生相应的控制信号,实现对数据的快速读写.试验结果表明此方案传输速度快、数据准确,可扩展到其他需要通过USB进行快速数据传输的系统中.

4.期刊论文彭保.吴坚.于青梅.马建国Verilog HDL语言在FPGA/CPLD开发中的应用-今日电子2004(5)

通过设计实例详细介绍了用Verilog HDL语言开发FPGA/CPLD的方法,并通过与其他各种输入方式的比较,显示出使用Verilog HDL语言的优越性.

5.期刊论文邓莉.徐国华.曾志林.Deng Li.Xu Guo-hua.Zeng Zhi-lin基于FPGA水声通讯编码的设计与实现-电子测量技术2010,33(11)

针对一套用于AUV(autonomous underwater vehicle)自救系统的水声应答器,提出了基于大规模逻辑器件FPGA(field-programmable gate array)的软件化分频及编码.在QuartusⅡ开发环境下,采用Verilog HDL(hardware-description-language)语言及参数化的程序设计方法,在FPGA上实现了这种软件式的分频和频率编码,与原本数字电路的实现方式比较,提高了该水声应答器系统的可靠性和集成度,降低了功耗,同时使系统的可扩展性等到了增强. 6.期刊论文罗浩.许艳.仲佳嘉.Luo Hao.Xu Yan.Zhong Jiadia用Verilog HDL实现基于FPGA的通用分频器的设计-科技广场2008(10)

在数字逻辑电路设计中,常常遇到一些对时钏分频的需求.本文实现了一种基于FPGAFPGA的软件化的分频方法,通过对不同的Verilog HDL语言程序语句进行比较分析和仿真综合.

7.期刊论文黄志文.扈晓兰.邵平.HUANG Zhi-wen.HU Xiao-lan.SHAO Ping基于FPGA的四相步进电动机控制器的设计-工矿自动化2010,36(4)

介绍了一种基于FPGA的四相步进电动机控制器的设计方案,给出了其控制原理、相关模块的设计及应用实例.该控制器采用全数字化控制,使用Verilog HDL语言编程,能够实现四相步进电动机的复位、脱机、转速和正反转控制.仿真及应用结果表明,该控制器控制灵活、调速范围大、精度高、运行稳定可靠.

8.期刊论文吴长江.赵不贿.郑博.于小燕.WU Chang Jiang.ZHAO Bu Hui.ZHENG Bo.YU Xiao Yan基于FPGA的动态目标跟踪系统设计-电子技术应用2010,36(3)

为了解决基于PC机的视频动态目标跟踪实时性瓶颈问题,设计出一种基于FPGA的动态目标跟踪系统.设计遵循图像处理金字塔模型,针对低层和中层算法简单、数据量大且存在一定并行性等特点采用FPGA硬件实现,而高层较复杂算法使用Nios Ⅱ软核进行C语言编程.整个设计采用Verilog-HDL对算法完成建模与实现,并在QUARTUS Ⅱ上进行了综合、布线等工作,最后以Altera公司的DE2开发板为硬件平台实现了整个系统.

9.期刊论文陈科.唐宁.雷求胜.邓玉清.CHEN Ke.TANG Ning.LEI Qiusheng.DENG Yuqing一种状态优化的I2C总线

主控制器的FPGA设计-电子器件2010,33(6)

I2C总线是一种简单的双向二线制串行通信总线.在此对传统的I2C总线控制器进行改进,对I2C总线读写状态进行了优化,该方法采用移位寄存器计数来控制状态转移,利用移位寄存器结构灵活的特点达到简化状态,优化状态机性能的目的.最后采用Verilog HDL语言的行为描述,并给出系统仿真波形,仿真结果表明,设计芯片的功耗大约降低10%,面积减少25%.所设计的总线接口良好,符合I2C通信标准,实现了I2C的总线的数据通信.

10.期刊论文苏维嘉.张澎.SU Wei-jia.ZHANG Peng基于FPGA的TFT-LCD控制器的设计和实现-液晶与显示

2010,25(1)

在Verilog HDL设计的行、场扫描时序基础上,设计并实现了基于FPGA的TFT-LCD控制器.该控制器在修改行、场扫描时序后可以驱动不同分辨率的TFT-LCD,具有很好的移植性.

引证文献(10条)

1.胡林锋.于映H.264/AVC解码端帧内预测的设计与实现[期刊论文]-微计算机信息 2009(9)

2.徐燕.孙丽华基于FPGA实现变采样率FIR滤波器的研究[期刊论文]-微计算机信息 2009(20)

3.江健康基于Verilog HDL的FIR数字滤波器设计与仿真[期刊论文]-微计算机信息 2007(8)

4.陈媛.黄贤英基于EDA技术的定向型计算机硬件设计[期刊论文]-微计算机信息 2007(29)

5.蒋昊.李哲英基于多种EDA工具的FPGA设计流程[期刊论文]-微计算机信息 2007(32)

6.陈媛TDN-CM++系统中断功能的实现[期刊论文]-微计算机信息 2007(32)

7.齐京礼.宋毅芳.陈建泗VHDL语言在FPGA中的应用[期刊论文]-微计算机信息 2006(35)

8.郭文彬.孙智权.赵不贿.徐雷钧基于NiosⅡ的USB接口模块设计[期刊论文]-微计算机信息 2006(29)

9.聂翔.王春侠基于FSM的电梯控制系统的设计与实现[期刊论文]-微计算机信息 2006(25)

10.周贤伟.程柏.覃伯平基于软件无线电的自定义相位扩频编码与FPGA实现[期刊论文]-微计算机信息 2006(17)

本文链接:https://www.360docs.net/doc/b613087078.html,/Periodical_wjsjxx200410038.aspx

授权使用:大连理工大学图书馆(dllg),授权号:4c179d07-d75a-4af6-b049-9eda013049a8

下载时间:2011年5月5日

(完整版)FPGA温度测量设计毕业设计

毕业论文FPGA温度测量设计

摘要 温度作为一种最基本的环境参数,与人民的生活有着密切关系。温度的测量和控制在工业、农业、国防、医疗等各个领域中应用普遍。温度测量仪是一种常用的检测仪器。 本文首先介绍了DS18B20的工作原理,利用数字温度传感器DS18B20的数据接口特点,展示了FPGA(Field-Programmable Gate Array,即现场可编程逻辑门阵列)的使用方法以及Verilog HDL (HDL:Hardware Discription Language)语言的编程,完成了基本温度测量功能。给出了硬件电路和软件设计,此设备具有结构简单、转换速度快、精确性高,扩展性好等优点。 关键词:FPGA;DS18B20;测温;Verilog HDL语言

Design of temperature measurement based on FPGA Abstract Tenperture is one of the most basic environmental parameters, and it industry, agriculture, national defense,medical and other fields, temperature measurement and control was widely used.The temperature measuring instrument is a kind of common testing instrument. In this paper,first we introduces the work principle of DS18B20,and the characteristics of data interface of digital temperature sensor DS18B20, demonstrated Language)programming language,accomplished the function of temperature measurement. Given the .The device . Key Words: FPGA;DS18B20;Temperature measurement;Verilog HDL language 目录 中文摘要 (1) 英文摘要 (2) 1绪论 (1) 1.1题目背景意义 (1) 1.2工作内容 (2)

(完整版)基于FPGA的智能交通灯的设计毕业设计

目录 摘要 ............................................................. I 1 前言 (1) 2 交通红绿灯控制电路的发展与技术现状 (2) 2.1 交通控制系统以及交通红绿灯控制电路的发展现状 (2) 2.2 智能交通红绿灯控制电路技术的现状 (3) 3 VHDL、FPGA、Quartus ii简介 (5) 3.1 VHDL简介 (5) 3.1.1 VHDL简介 (5) 3.1.2 VHDL语言的特点 (6) 3.2 FPGA简介 (8) 3.2.1 PLD器件的设计特点 (8) 3.2.2 FPGA的基本结构 (10) 3.2.3 采用FPGA设计逻辑电路的优点 (11) 3.3 Quartus II 的简介 (12) 4 具体方案论证与设计 (13) 4.1 具体方案论证 (13) 4.2系统算法设计 (15) 4.3 具体电路原理图 (16) 4.4 电路仿真图 (16) 5 实验结果 (17) 总结 (18) 参考文献 ......................................... 错误!未定义书签。附录: .. (19)

基于FPGA的十字路口交通信号灯 摘要 本文主要介绍十字路口交通灯控制器的设计。首先,介绍交通控制系统以及交通红绿灯控制电路的发展现状;然后采用硬件描述语言进行的交通灯控制器设计。重点介绍了控制系统各部分的设计,以及各个模块之间的同步处理。为了克服交通信号灯控制系统传统设计方法的弊端,更加适应城镇交通现状,利用VHDL语言、采用层次化混合输入方式,设计了具有3种信号灯和倒计时显示器的交通信号灯控制系统,在 QuartusⅡ下进行仿真,并下载到FPGA中制作成实际的硬件电路进行了模拟运行.使用该方法设计的交通灯控制系统电路简单、运行可靠、易于实现,可实现对交通信号的控制和显示功能。 关键词 FPGA;QUARTUS ii;HDPLD;十字路口交通灯控制器; Based on FPGA intersection traffic lights Abstract This paper describes the design of intersection traffic signal controller.First, the introduction of traffic control systems and traffic light control circuit of the development status; then using language designed for the traffic light controller.Focus on various parts of the control system

基于FPGA的多功能数据选择器设计与实现

基于FPGA的多功能数据选择器设计与实现 章军海201022020671 [摘要]传统的数字系统设计采用搭积木式的方法来进行设计,缺乏设计的灵活性。随着可编程逻辑器件(PLD)的出现,传统设计的缺点得以弥补,基于PLD的数字系统设计具有很好的灵活性,便于电路系统的修改与调试。本文采用自顶向下的层次化设计思想,基于FPGA设计了一种多功能数据选择器,实现了逻辑单元可编程、I/O单元可编程和连线可编程功能,并给出了本设计各个层次的原理图和仿真时序图;本文还基于一定的假设,对本设计的速度和资源占用的性能进行了优化。 [关键词]层次化设计;EDA;自顶向下;最大时延 0引言: 在现代数字系统的设计中,EDA(电子设计自动化)技术已经成为一种普遍的工具。基于EDA技术的设计中,通常有两种设计思想,一种是自顶向下的设计思想,一种是自底向上的设计思想[1]。其中,自顶向下的设计采用层次化设计思想,更加符合人们的思维习惯,也容易使设计者对复杂系统进行合理的划分与不断的优化,因此是目前设计思想的主流。基于层次化设计思想,实现逻辑单元、I/O单元和连线可编程可以提高资源的利用效率,并且可以简化数字系统的调试过程,便于复杂数字系统的设计[2][3]。 1系统原理图构架设计 1.1系统整体设计原理 本设计用于实现数据选择器和数据分配器及其复用的I/O端口和连线的可编程却换,提高系统的资源利用效率。系统顶层原理框图如图1所示,系统拥有两个地址选择端口a0、a1,一个功能选择端口ctr,还有五路I/O复用端口。其中,地址选择端口用于决定数据选择器的数据输入端和数据分配器的数据输出端;功能选择端口用于切换数据选择器和数据分配器,以及相应的I/O端口和连线;I/O复用端口数据的输入和输出,其功能表如表一所示。 图1顶层模块原理图 表一顶层系统功能表

基于单片机的毕业设计题目

单片机类 业设计 刷电子时钟的设计 刷全自动节水灌溉系统--硬件部 刷数 式温度计的设计 刷温度 控系统设计 刷基于单片机的语音提示测温系统的研究 刷简易无线电遥控系统 刷数 流 计 刷基于单片机的全自动洗衣机 刷水塔智能水 控 系统 刷温度箱模拟控 系统 刷超声波测距仪的设计 刷基于51单片机的L司号点阵显示屏系统的设计与实 16×16点阵显示屏 刷基于A切89分51单片机的数 电子时钟 刷基于单片机的步 电机的控 刷基于单片机的交流调 器设计 刷基于单片机的数 电压表的设计 刷单片机的数 钟设计 刷智能散热器控 器的设计 刷单片机打铃系统设计 刷基于单片机的交通信 灯控 电路设计 刷基于单片机的电话 程控 家用电器系统设计 刷基于单片机的安全 警器 刷基于单片机的 路抢答器设计 刷基于单片机的超声波测距系统的设计 刷基于MC分-51数 温度表的设计 刷电子体温计的设计 刷基于A切89C51的电话 程控 系统 刷基于A三R单片机幅度 调的号号分信 发生器 刷基于单片机的数控稳压电源的设计 刷基于单片机的室内一氧化碳 测及 警系统的研究 刷基于单片机的空调温度控 器设计 刷基于单片机的 编程多 能电子定时器 刷单片机的数 温度计设计 刷红外遥控密码锁的设计 刷基于61单片机的语音识别系统设计 刷家用 燃气体 警器的设计 刷基于数 温度计的多点温度检测系统 刷基于凌 单片机的语音实时采集系统设计 刷基于单片机的数 频率计的设计 刷基于单片机的数 电子钟设计 刷设施 境中温度测 电路设计 刷汽车倒车 撞 警器的设计 刷篮球赛计时记 器

刷基于单片机的家用智能总线式开关设计 刷设施 境中湿度检测电路设计 刷基于单片机的音乐合成器设计 刷设施 境中二氧化碳检测电路设计 刷基于单片机的水温控 系统设计 刷基于单片机的数 温度计的设计 刷基于单片机的火灾 警器 刷基于单片机的红外遥控开关设计 刷基于单片机的电子钟设计 刷基于单片机的红外遥控电子密码锁 刷大棚温湿度自动 控系统 刷基于单片机的电器遥控器的设计 刷单片机的语音 储与 放的研究 刷基于单片机的电 热炉温度控 系统设计 刷红外遥控电源开关 刷基于单片机的 频信 发生器设计 刷基于单片机的呼叫系统的设计 刷基于PIC16F876A单片机的超声波测距仪 刷基于单片机的密码锁设计 刷单片机步 电机转速控 器的设计 刷由A切89C51控 的太 能热水器 刷 盗与恒温系统的设计与 作 刷A切89分52单片机实验系统的开发与 用 刷基于单片机控 的数 气压计的设计与实 刷智能压力传感器系统设计 刷智能定时器 刷基于单片机的智能火灾 警系统 刷基于单片机的电子式转速 程表的设计 刷 交车汉 显示系统 刷单片机数 电压表的设计 刷精密三F转换器与MC分-51单片机的接口技术 刷基于单片机的居室安全 警系统设计 刷基于89C2051 IC卡读/写器的设计 刷PC机与单片机串行通信设计 刷球赛计时计 器设计 刷 系列PCL五层电 控 系统设计 刷自动起闭光控窗帘设计 刷单片机控 交通灯系统设计 刷基于单片机的电子密码锁 刷基于51单片机的多路温度采集控 系统 刷点阵电子显示屏-- 业设计 刷超声波测距仪-- 业设计 刷单片机对玩 小车的智能控 业设计论文 刷基于单片机控 的电机交流调速 业设计论文

fpga毕业设计开题报告.doc

fpga毕业设计开题报告 FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。以下是fpga毕业设计,欢迎阅读。 1选题目的意义和可行性 在这个时间就是金钱的年代里,数字电子钟已成为人们生活中的必需品。目前应用的数字钟不仅可以实现对年、月、日、时、分、秒的数字显示,还能实现对电子钟所在地点的温度显示和智能闹钟功能,广泛应用于车站、医院、机场、码头、厕所等公共场所的时间显示。随着现场可编程门阵列( field program-mable gate array ,FPGA) 的出现,电子系统向集成化、大规模和高速度等方向发展的趋势更加明显,作为可编程的集成度较高的ASIC,可在芯片级实现任意数字逻辑电路,从而可以简化硬件电路,提高系统工作速度,缩短产品研发周期。故利用FPGA这一新的技术手段来研究电子钟有重要的现实意义。设计采用FPGA现场可编程技术,运用自顶向下的设计思想设计电子钟。避免了硬件电路的焊接与调试,而且由于FPGA的I /O 端口丰富,内部逻辑可随意更改,使得数字电子钟的实现较为方便。本课题使用Cyclone EP1C6Q240的FPGA器件,完成实现一个可以计时的数字时钟。该系统具有显示时、分、秒,智能闹钟,按键实现校准时钟,整点报时等功能。满足人们得到精确时间以及时间提醒的需求,方便人们生活。 2 研究的基本内容与拟解决的主要问题 2.1研究的基本内容 数字时钟是采用电子电路实现对时间进行数字显示的计时

装置,由于数字集成电路的发展和石英晶体振荡器的广泛应用,使得数字钟的精度不断提高。 数字时钟系统的实现有很多,可以利用VerilogDHL语言在Quartus II里实现时、分、秒计数的功能。在芯片内部存储器设24个字节分别存放时钟的时、分、秒信息。数字时钟首先是秒位(共8位)上按照系统时钟CLK进行计数,存储器内相应的秒值加1;若秒位的值达到60(110000),则将其清零,并将相应的分位(共8位)的值加1;若分值达到60(110000),则清零分位,并将时位(共8位)的值加1;若计数满24(100100)后整个系统从0开始重新进行计数。 本设计使用Cyclone EP1C6Q240的FPGA器件为核心,通过编写程序,完成此电子时钟的主要功能显示时,分,秒,以及通过按键实现校准时钟主要功能,使用LED液晶屏显示,分别显示时,分,秒。并且能够实现附加功能----闹铃设置功能和整点报时。 2.2 拟要解决的问题 本设计电子钟系统功能简单,用Cyclone EP1C6Q240的FPGA器件为核心,通过编写程序,完成此电子时钟的主要功能。 本课题主要解决以下问题: (1) 学习VerilogDHL语言、运用Quartus II环境进行程序设计。 用VerilogDHL语言能进行综合的电路设计,也可用于电路的仿真;设计的 规模是任意的,语言不对设计规模施加任何限制;内置各种基本的逻辑门。便于改进和扩充,有利于本系统的研制,并使其性能更完备的。

基于FPGA下的交通灯控制器设计

引言 随着城乡的经济发展,车辆的数量在迅速的增加,交通阻塞的问题已经严重影响了人们的出行。 现在的社会是一个数字化程度相当高的社会,很多的系统设计师都愿意把自己的设计设计成集成电路芯片,芯片可以在实际中方便使用。随着EDA技术的发展,嵌入式通用及标准FPGA器件的呼之欲出,片上系统(SOC)已经近在咫尺。FPGA/CPLD 以其不可替代的地位及伴随而来的极具知识经济特征的IP芯片产业的崛起,正越来越受到业内人士的密切关注。FPGA就是在这样的背景下诞生的,它在数字电路中的地位也越来越高,这样迅速的发展源于它的众多特点。交通等是保障交通道路畅通和安全的重要工具,而控制器是交通灯控制的主要部分,它可以通过很多种方式来实现。在这许许多多的方法之中,使用FPGA和VHDL语言设计的交通灯控制器,比起其他的方法显得更加灵活、易于改动,并且它的设计周期性更加短。 城市中的交通事故频繁发生,威胁着人们的生命健康和工作生活,交通阻塞问题在延迟出行时间的同时,还会造成更多的空气污染和噪声污染。在这种情况下,根据每个道路的实际情况来设置交通灯,使道路更加通畅,这对构建和谐畅通的城市交通有着十分重要的意义。

第一章软件介绍 1.1 QuartusⅡ介绍 本次毕业设计是基于FPGA下的设计,FPGA是现场可编程门阵列,FPGA开发工具种类很多、智能化高、功能非常的强大。可编程QuartusⅡ是一个为逻辑器件编程提供编程环境的软件,它能够支持VHDL、Verilog HDL语言的设计。在该软件环境下,设计者可以实现程序的编写、编译、仿真、图形设计、图形的仿真等许许多多的功能。在做交通灯控制器设计时选择的编程语言是VHDL语言。 在这里简单的介绍一下QuartusⅡ的基本部分。图1-1-1是一幅启动界面的图片。在设计前需要对软件进行初步的了解,在图中已经明显的标出了每一部分的名称。 图 1-1-1 启动界面 开始设计前我们需要新建一个工程,首先要在启动界面上的菜单栏中找到File,单击它选择它下拉菜单中的“New Project Wizard”时会出现图1-1-2所显示的对话框,把项目名称按照需要填好后单击Next,便会进入图 1-1-3 显示的界面。

基于FPGA的脉冲发生器的设计

【基础?应用】 基于FP GA 的脉冲发生器的设计 ① 张 涛 (北方交通大学电子信息工程学院,北京100044)【摘 要】 以脉冲发生器为研究对象,介绍了脉冲发生器的基本原理、硬件构成和实现方法,阐述了一种基于DSP -FP G A 数字系统的PWM 控制脉冲生成方法,并给出了仿真及实测实验结果。 【关键词】 脉宽调制;脉冲发生器;可编程门阵列 1 FP G A 简介 FP G A (Field Programmable G ate Array ,可编程门阵列)是美国Xinlinx 公司推出的一种采用单元型结构的新型PLD 器件。它采用CMOS 、SRAM 工艺制作,在结构上与阵列型PLD 不同,它的内部由许多独立的可编程逻辑单元构成,各逻辑单元之间可以灵活地相互连接,具有密度高、速度快、编程灵活和可重新配置等诸多优点。FP G A 已成为当前主流的PLD 器件之一。 1.1 PLD 的主要特点 (1)缩短研制周期。 (2)降低设计成本。用PLD 来设计和改造电子产品可以大幅度地减少印制板的面积和接插件,降低装配和调试费用。 (3)提高设计灵活性和可靠性。大量分立式元器件在向印制板上装配时,往往会发生由于虚焊或接触率近似于线性增加,且线性斜率较小;肝脏中大小不同的散射源对不同频率的声波存在有不同的散射效应。 由于肝脏组织结构的非均匀性、复杂性及其各部分散射相关长度分布的不一致性,其散射谱随深度增加而衰减变化,并非完全呈线性关系,而呈现较复杂的关系变化。 ⑵肝叶边缘部分及表层区域,其结构散射近似呈瑞利散射特征;肝叶表层以下与肝叶中心之间的中间区域,其结构散射呈随机散射特征;肝叶中心区域,其结构散射呈扩散漫射特征,也有较强的反射。 ⑶利用区域结构散射特征谱,不仅可对各特征区域组织微结构作出粗略估计,而且可通过区域散射谱特征的变化,对生物软组织的生理病理变化的判断提供依据。 综上所述,利用超声散射谱分析,可为B 超的形态学图像信息诊断提供一个组织特征的信息,在临床上是有应用前景的。 参考文献 [1]Luigi Landini et al.IEEE Trans on U FFC.1990,37(5):448-456 [2]陈启敏等.声学学报.1995,Vol.21,No.4:692-699 [3]E.J.Feleppa ,et al.IEEE Annual International Conference ,EMB ,1990;12(1):337 (责任编辑:常 平) 2003年4月第19卷第2期 武警工程学院学报JOURNAL OF EN GG COLL EGE OF ARMED POL ICE FORCE Apr.2003Vol.19No.2 ①收稿日期:2002-12-06作者简介:张涛(1968.07-),1994年毕业于西安交通大学工业电器自动化专业,现在北方交通大学电子信息工程学院电子与信息工程专业攻读硕士学位。

基于FPGA的数字频率计设计毕业论文

武汉轻工大学 毕业设计外文参考文献译文本 2013届 原文出处:from Vin Skahill.VHDL for Programmable Logic page 76-88 毕业设计题目:基于FPGA的数字频率计设计 院(系):电气与电子工程学院 专业名称:电子信息科学与技术 学生姓名: 学生学号: 指导教师:

Introduction of digital frequency meter Digital Frequency is an indispensable instrument of communications equipment, audio and video, and other areas of scientific research and production . In addition to the plastic part of the measured signal, and digital key for a part of the show, all the digital frequency using Verilog HDL designed and implemented achieve in an FPGA chip. The entire system is very lean, flexible and have a modification of the scene. 1 、And other precision measuring frequency Principle Frequency measurement methods can be divided into two kinds: (1) direct measurement method, that is, at a certain time measurement gate measured pulse signal number. (2) indirect measurements, such as the cycle frequency measurement, VF conversion law. Frequency Measurement indirect measurement method applies only to low-frequency signals. Based on the principles of traditional frequency measurement of the frequency of measurement accuracy will be measured with the decline in signal frequency decreases in the more practical limitations, such as the accuracy and frequency of measurement not only has high accuracy, but also in the whole frequency region to maintain constant test accuracy. The main method of measurement frequency measurement Preferences gated signal GATE issued by the MCU, GATE time width on the frequency measurement accuracy of less impact, in the larger context of choice, as long as the FPGA in 32 of 100 in the counter b M Signals are not overflow line, in accordance with the theoretical calculation GATE time can be greater than the width Tc 42.94 s, but due to the single-chip microcomputer data processing capacity constraints, the actual width of less time, generally in the range of between 0.1 s choice, that is, high-frequency, shorter gate;, low gate longer. This time gate width Tc based on the size of the measured frequency automatically adjust frequency measurement in order to achieve the automatic conversion range, and expanded the range of frequency measurement; realization of the entire scope of measurement accuracy, reduce the low-frequency measurement error. The design of the main methods of measuring the frequency measurement and control block diagram as shown in Figure 1. Figure 1 Preferences gated signal GA TE issued by the MCU, GA TE time width of less frequency measurement accuracy, in the larger context of choice, as long as the FPGA in 32 of 100 in the counter b M

基于FPGA的四层电梯控制系统设计毕业设计论文

毕业论文Array 基于FPGA的四层电梯控制系统设计

毕业设计(论文)原创性声明和使用授权说明 原创性声明 本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。 作者签名:日期: 指导教师签名:日期: 使用授权说明 本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。 作者签名:日期:

学位论文原创性声明 本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。本人完全意识到本声明的法律后果由本人承担。 作者签名:日期:年月日 学位论文版权使用授权书 本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。 涉密论文按学校规定处理。 作者签名:日期:年月日 导师签名:日期:年月日

通过Verilog实现交通灯设计实验报告

电子科技大学 实 验 报 告 一、实验室名称:虚拟仪器实验室 二、实验项目名称:交通灯设计实验 三、实验学时:4学时 四、实验原理

假设交通灯处于南北和东西两条大街的“十”字路口,如图1所示。用FPGA 开发板的LED 灯来模拟红、黄、绿3种颜色信号,并按一定顺序、时延来点亮LED ,如图2所示。图3给出了交通灯的状态转移图。设计使用频率为1Hz 的时钟来驱动电路(注1:仿真时采用1MHz 的时钟来驱动电路),则停留1个时钟可得到1S 的延时,类似停留3个时钟可得到3S 的延时,停留15个时钟可得到15S 的延时(注2:开发板工作时钟为50MHz )。 北 南 西东 图1. 六个彩色LED 可以表示一组交通信号灯 图2. 交通灯状态 南北 东西 红 黄 绿 红 黄 绿 S0 1 0 0 0 0 1 S1 1 0 0 0 1 0 S2 1 0 0 1 0 0 S3 0 0 1 1 0 0 S4 0 1 0 1 0 0 S5 1 0 0 1 0 0

图3. 交通灯的状态转移图 顶层模块 时钟分频模块状态机跳转模块 图4. 交通灯的原理框图 五、实验目的 本实验是有限状态机的典型综合实验,掌握如何使用状态转移图来定义Mealy状态机和Moore状态机,熟悉利用HDL代码输入方式进行电路的设计和仿真的流程,掌握Verilog语言的基本语法。并通过一个交通灯的设计掌握利用EDA软件(Xilinx ISE 13.2)进行HDL代码输入方式的电子线路设计与仿真的详细流程。。 六、实验内容 在Xilinx ISE 13.2上完成交通灯设计,输入设计文件,生成二进制码流文件下载到FPGA开发板上进行验证。 七、实验器材(设备、元器件)

基于FPGA的模拟IIC接口设计与实现

研究生课程论文 课程名称基于FPGA的模拟IIC接口设计与实现授课学期2012 学年至2013 学年第一学期学院电子工程学院 专业电子与通信工程 学号2012011603 姓名 任课教师 交稿日期2013.01.10 成绩 阅读教师签名 日期 广西师范大学研究生学院制

基于FPGA的模拟I2C接口设计与实现 摘要:本文论述了I2C总线的基本协议,以及基于FPGA 的模拟I2C 总线接口模块的设计,在QuartusII软件中用Verilog HDL语言编写了部分I2C总线接口功能的程序代码,生成原理图模块。并连接好各个模块,进行了时序仿真。最后,下载到FPGA的板运行测试。 关键词:I2C 接口FPGA Verilog 1课题研究意义、现状及应用分析 目前市场上主流的嵌入式设备主要是微处理器、DSP等,但FPGA 以其独有的高抗干扰性、高安全性正在逐步取得开发公司的青睐,在FPGA上开发I2C势在必行。并且利用EDA 工具设计芯片实现系统的功能,已经成为支撑电子设计的通用平台,并逐步向支持系统级的设计方向发展。模块化的设计思想在软件设计过程中越来越被重视。I2C总线是Philips 公司推出的双向两线串行通讯标准,具有接口线少、通讯效率高等特点。因此,基于FPGA的I2C总线设计有着广泛的应用前景。

2课题总体方案设计及功能模块介绍 本设计主要分三大模块,分别是I2C 总线接口模块、按键输入控制模块、数码管显示模块。I2C总线模块集成了I2C协议用于和总线相接EEPROM的通信;按键输入控制模块用于控制I2C模块的页读、页写、字节读、字节写功能;数码管显示模块用于显示通过I2C总线读取EEPROM中的数据。 3I2C接口设计原理 I2C总线最主要的优点是其简单性和有效性。由于接口直接在组件之上,因此I2C总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。总线的长度可高达25英尺,并且能够以10 Kbps的最大传输速率支持40个组件。I2C总线的另一个优点是,它支持多主控(multimastering),其中任何能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率。 3.1总线的构成 I2C总线是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。在CPU与被控IC之间、IC与IC之间进行双向传送,最高传送速率100kbps。各种被控制电路均并联在这条总线上,但就像电话机一样只有拨通各自的号码才能工作,所以每个电路和模块都

电子类毕业设计题目

盼盼电子设计网本网站承接电子类毕业设计论文一条龙服务!!! 电子毕业设计:12 1.基于FPGA的PCI总线设计 2.基于FPGA的UART接口设计 3.基于单片机的数字电压表 4.单片机控制的全自动洗衣机毕业设计 电梯控制的设计与实现 6.恒温箱单片机控制 7.单片机脉搏测量仪 8.单片机控制步进电机毕业设计论文 9.函数信号发生器设计论文 变电所一次系统设计 11.报警门铃设计论文 单片机交通灯控制 13.单片机温度控制系统 通信系统中的接入信道部分进行仿真与分析 15.仓库温湿度的监测系统 16.基于单片机的电子密码锁 17.单片机控制交通灯系统设计 18.基于DSP的IIR数字低通滤波器的设计与实现

19.智能抢答器设计 20.基于LabVIEW的PC机与单片机串口通信设计的IIR数字高通滤波器 22.单片机数字钟设计 23.自动起闭光控窗帘毕业设计论文 24.三容液位远程测控系统毕业论文 25.基于Matlab的PWM波形仿真与分析 26.集成功率放大电路的设计 27.波形发生器、频率计和数字电压表设计 28.水位遥测自控系统毕业论文 29.宽带视频放大电路的设计毕业设计 30.简易数字存储示波器设计毕业论文 31.球赛计时计分器毕业设计论文 数字滤波器的设计毕业论文 机与单片机串行通信毕业论文 34.基于CPLD的低频信号发生器设计毕业论文 35. 基于labVIEW虚拟滤波器的设计与实现序列在扩频通信中的应用 37.正弦信号发生器 38.红外报警器设计与实现 39.开关稳压电源设计 40.基于MCS51单片机温度控制毕业设计论文

41.步进电动机竹竿舞健身娱乐器材 42.单片机控制步进电机毕业设计论文 43.单片机汽车倒车测距仪 44.基于单片机的自行车测速系统设计 45.水电站电气一次及发电机保护 46.基于单片机的数字显示温度系统毕业设计论文 47.语音电子门锁设计与实现 48.工厂总降压变电所设计-毕业论文 49.单片机无线抢答器设计 50.基于单片机控制直流电机调速系统毕业设计论文 51.单片机串行通信发射部分毕业设计论文 52.基于VHDL语言PLD设计的出租车计费系统毕业设计论文 53.超声波测距仪毕业设计论文 54.单片机控制的数控电流源毕业设计论文 55.声控报警器毕业设计论文 56.基于单片机的锁相频率合成器毕业设计论文 57.基于Multism/protel的数字抢答器 58.单片机智能火灾报警器毕业设计论 59.无线多路遥控发射接收系统设计毕业论文 60.单片机对玩具小车的智能控制毕业设计论文 61.数字频率计毕业设计论文 62.基于单片机控制的电机交流调速毕业设计论文

基于fpga的eeprom设计

二线制I2C CMOS 串行EEPROM 的FPGA设计 姓名:钱大成 学号:080230114 院系:物理院电子系 2011年1月1日

一、课程设计摘要: (1)背景知识: A、基本介绍: 二线制I2C CMOS 串行EEPROM AT24C02/4/8/16 是一种采用CMOS 工艺制成的串行可用电擦除可编程只读存储器。 B、I2C (Inter Integrated Circuit)总线特征介绍: I2C 双向二线制串行总线协议定义如下: 只有在总线处于“非忙”状态时,数据传输才能被初始化。在数据传输期间,只要时钟线为高电平,数据线都必须保持稳定,否则数据线上的任何变化都被当作“启动”或“停止”信号。图1 是被定义的总线状态。· ①总线非忙状态(A 段) 数据线SDA 和时钟线 SCL 都保持高电平。 ②启动数据传输(B 段) 当时钟线(SCL)为高电平状态时,数据线(SDA)由高电平变为低电平的下降沿被认为是“启动”信号。只有出现“启动”信号后,其它的命令才有效。

③停止数据传输(C 段) 当时钟线(SCL)为高电平状态时,数据线(SDA)由低电平变为高电平的上升沿被认为是“停止”信号。随着“停在”信号出现,所有的外部操作都结束。 ④数据有效(D 段) 在出现“启动”信号以后,在时钟线(SCL)为高电平状态时数据线是稳定的,这时数据线的状态就要传送的数据。数据线(SDA)上的数据的改变必须在时钟线为低电平期间完成,每位数据占用一个时钟脉冲。每个数传输都是由“启动”信号开始,结束于“停止”信号。 ⑤应答信号 每个正在接收数据的EEPROM 在接到一个字节的数据后,通常需要发出一个应答信号。而每个正在发送数据的EEPROM 在发出一个字节的数据后,通常需要接收一个应答信号。EEPROM 读写控制器必须产生一个与这个应答位相联系的额外的时钟脉冲。在EEPROM 的读操作中,EEPROM 读写控制器对EEPROM 完成的最后一个字节不产生应答位,但是应该给EEPROM 一个结束信号。 C、3. 二线制I2C CMOS 串行EEPROM读写操作 ① EEPROM 的写操作(字节编程方式) 所谓EEPROM 的写操作(字节编程方式)就是通过读写控制器把一个字节数据发送到EEPROM 中指定地址的存储单元。其过程如下:EEPROM 读写控制器发出“启动”信号后,紧跟着送4 位I2C 总线器件特征编码1010 和3 位EEPROM 芯片地址/页地址XXX 以及写状态的R/W 位(=0),到总线上。这一字节表示在接收到被寻址的EEPROM 产生的一个应答位后,读写控制器将跟着发

FPGA毕业设计论文英文

[1] Using FPGA technology towards the design of an adaptive fault tolerant framework Erdogan, Sevki (University of Hawaii); Gersting, Judith L.; Shaneyfelt, Ted; Duke, Eugene L. Source: Conference Proceedings - IEEE International Conference on Systems, Man and Cybernetics, v 4, IEEE Systems, Man and Cybernetics Society, Proceedings - 2005 International Conference on Systems, Man and Cybernetics, 2005, p 3823-3827 ISSN: 1062-922X CODEN: PICYE3 Conference: IEEE Systems, Man and Cybernetics Society, Proceedings - 2005 International Conference on Systems, Man and Cybernetics, Oct 10-12 2005, Waikoloa, HI, United States Sponsor: IEEE Systems, Man and Cybernetics Society Publisher: Institute of Electrical and Electronics Engineers Inc. Abstract: In this paper we propose architecture for a Reconfigurable, Adaptive, Fault-Tolerant (RAFT) framework for application in real time systems with require multiple levels of redundancy and protection. Typical application environments include distributed processing, fault-tolerant computation, and mission and safety-critical systems. The framework uses Field Programmable Gate Array (FPGA) technologies with on the fly partial programmability achieving reconfiguration of a system component when the existing components fail or to provide extra reliability as required in the specification. The framework proposes the use an array of FPGA devices to implement a system that, after detecting an error caused by a fault, can adaptively reconfigure itself to achieve fault tolerance. The FPGAs that are becoming widely available at a low cost are exploited by defining a system model that allows the system user to define various levels of reliability choices, providing a monitoring layer for the system engineer. ? 2005 IEEE. (21 refs.) [2]METHOD FOR PROTECTING COMPUTER THROUGH REAL-TIME MONITORING BY PROTECTING EXECUTION FILE, AND COMPUTER AND SYSTEM PROTECTED BY THE SAME Patent number: KR20040083409 Publication date: 2004-10-01 Inventor: AHN MU GYEONG Applicant: SAFEI CO LTD Classification: - international: G06F11/30; G06F11/30; (IPC1-7): G06F11/30 - european: Application number: KR20040072633 20040910 Priority number(s): KR20040072633 20040910 View INPADOC patent family View forward citations

基于FPGA的交通灯课程设计报告

总体设计要求和技术要点 1.任务及要求 (1)设计一个交通信号灯控制器,由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外。 (2)红、绿、黄发光二极管作信号灯,用传感器或逻辑开关作检测车辆是否到来的信号。 (3)主干道处于常允许通行的状态,支干道有车来时才允许通行。主干道亮绿灯时,支干道亮红灯;支干道亮绿灯时,主干道亮红灯。 (4)主、支干道均有车时,两者交替允许通行,主干道每次放行45秒,支干道每次放行25秒,设立45秒、25秒计时、显示电路。 (5)在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,使行驶中的车辆有时间停到禁行线外,设立5秒计时、显示电路。 (6)按《湖南涉外经济学院课程设计管理办法》要求提交课程设计报告。 工作内容及时间进度安排 第17周:周1---周2 :立题、论证方案设计 周3---周5 :程序设计与调试 第18周:周1---周3 :硬件调试与测试、撰写课程设计报告 周4---周5 :验收答辩 课程设计成果 1.与设计内容对应的软件程序 2.课程设计总结报告

摘要 本实验为自主选题设计实验,实验选择具有倒计时显示功能的红黄绿三色交通设计,实验中采用VHDL 作为设计功能描述语言,选用Altera公司的EP1K30144-PIN TQFP最为主控芯片,实验报告中简要介绍了FPGA器件,并给出了设计原理图,详细的介绍了交通灯的设计流程,实验报告中还附有实验代码实验结果照片图。 Abstract This experiment designed for independent choice experiment, experiment choice which has the function of the countdown display red yellow green traffic design, description language (VHDL as design function is applied in the experiments, the most main control chip select MAX II EPM240T100C5 Altera company, experiment report, this paper briefly introduces the MAX II device series, and gives the design diagram, detailed introduces the traffic lights of the design process, the experiment report with the code results photo graph.