多通道ADC&DMA配置

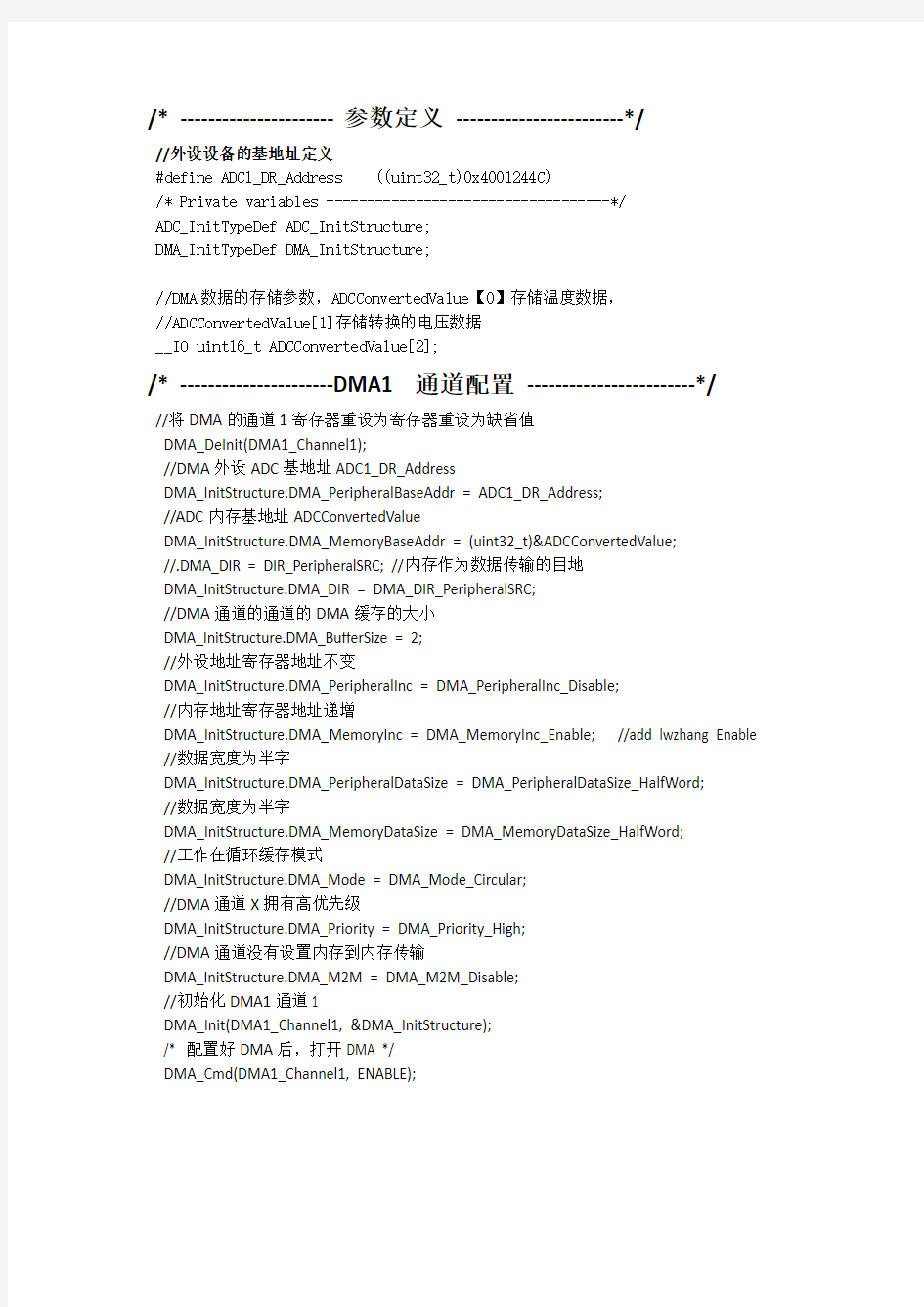

/* ----------------------参数定义------------------------*/

//外设设备的基地址定义

#define ADC1_DR_Address ((uint32_t)0x4001244C)

/* Private variables -----------------------------------*/

ADC_InitTypeDef ADC_InitStructure;

DMA_InitTypeDef DMA_InitStructure;

//DMA数据的存储参数,ADCConvertedValue【0】存储温度数据,

//ADCConvertedValue[1]存储转换的电压数据

__IO uint16_t ADCConvertedValue[2];

/* ----------------------DMA1通道配置------------------------*/

//将DMA的通道1寄存器重设为寄存器重设为缺省值

DMA_DeInit(DMA1_Channel1);

//DMA外设ADC基地址ADC1_DR_Address

DMA_InitStructure.DMA_PeripheralBaseAddr = ADC1_DR_Address;

//ADC内存基地址ADCConvertedValue

DMA_InitStructure.DMA_MemoryBaseAddr = (uint32_t)&ADCConvertedValue;

//.DMA_DIR = DIR_PeripheralSRC; //内存作为数据传输的目地

DMA_InitStructure.DMA_DIR = DMA_DIR_PeripheralSRC;

//DMA通道的通道的DMA缓存的大小

DMA_InitStructure.DMA_BufferSize = 2;

//外设地址寄存器地址不变

DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable;

//内存地址寄存器地址递增

DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable; //add lwzhang Enable //数据宽度为半字

DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_HalfWord;

//数据宽度为半字

DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_HalfWord;

//工作在循环缓存模式

DMA_InitStructure.DMA_Mode = DMA_Mode_Circular;

//DMA通道X拥有高优先级

DMA_InitStructure.DMA_Priority = DMA_Priority_High;

//DMA通道没有设置内存到内存传输

DMA_InitStructure.DMA_M2M = DMA_M2M_Disable;

//初始化DMA1通道1

DMA_Init(DMA1_Channel1, &DMA_InitStructure);

/* 配置好DMA后,打开DMA */

DMA_Cmd(DMA1_Channel1, ENABLE);

/* ----------ADC1 configuration---------------*/ //ADC1、ADC2工作在独立模式

ADC_InitStructure.ADC_Mode = ADC_Mode_Independent;

//模数转换工作在扫描模式

ADC_InitStructure.ADC_ScanConvMode = ENABLE;

//模数转换工作在连续转换模式

ADC_InitStructure.ADC_ContinuousConvMode = ENABLE;

//外部触发转换关闭

ADC_InitStructure.ADC_ExternalTrigConv = ADC_ExternalTrigConv_None;

//数据存储格式采用右对齐格式

ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right;

//ADC采集通道数目2

ADC_InitStructure.ADC_NbrOfChannel = 2;

//初始化ADC1

ADC_Init(ADC1, &ADC_InitStructure);

//ADC规则通道顺序配置

ADC_RegularChannelConfig(ADC1,16, 1, ADC_SampleTime_55Cycles5);

ADC_RegularChannelConfig(ADC1, ADC_Channel_14, 2, ADC_SampleTime_55Cycles5);

/* Enable the temperature sensor and vref internal channel */

//启用STM32的内部温度传感器和VREF内部通道

ADC_TempSensorVrefintCmd(ENABLE);

/* Enable ADC1 DMA */

//要使用ADC的DMA就要使能ADC的DMA

//开启ADC的DMADMA支持(要实现支持(要实现DMA功能,

//还需独立配置功能,还需独立配置DMA通道等参数(上面已经配置了))

ADC_DMACmd(ADC1, ENABLE);

/* Enable ADC1 */

//使能指定的ADC

ADC_Cmd(ADC1, ENABLE);

/*-----------开启ADC校验----------------*/

/* 使能ADC1校准寄存器复位*/

ADC_ResetCalibration(ADC1);

/*检查ADC1复位后校准寄存器状态*/

while(ADC_GetResetCalibrationStatus(ADC1));

/* 启动ADC1校准*/

ADC_StartCalibration(ADC1);

/* 检查ADC1校准后的状态*/

while(ADC_GetCalibrationStatus(ADC1));

/* 启动ADC1软件转换使能*/

ADC_SoftwareStartConvCmd(ADC1, ENABLE);

void GPIO_Configuration(void)

{

GPIO_InitTypeDef GPIO_InitStructure;

/* Configure PC.04 (ADC Channel14) as analog input -------------------------*/ GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AIN;

GPIO_Init(GPIOC, &GPIO_InitStructure);

}

基于AD7606 的可扩展多通道同步采样数据采集系统的布局考虑

电路笔记 CN-0148 连接/参考器件 8通道DAS ,内置16位、双极性、同步采样ADC AD7606利用ADI 公司产品进行电路设计 Rev.0 “Circuits from the Lab” from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 https://www.360docs.net/doc/d7287111.html, Fax: 781.461.3113 ?2010 Analog Devices, Inc. All rights reserved. AD7606-66通道DAS ,内置16位、双极性、同步采样ADC 放心运用这些配套产品迅速完成设计。 欲获得更多信息和/或技术支持,请拨打4006-100-006或访问AD7606-44通道DAS ,内置16位、双极性、同步采样ADC https://www.360docs.net/doc/d7287111.html,/zh/circuits 。 ADR421 精密、低噪声XFET ?基准电压源 基于16位8通道DAS AD7606的可扩展多通道 同步采样数据采集系统(DAS)的布局考虑 电路描述 电路功能与优势 AD7606是一款集成式8通道数据采集系统,片内集成输入放大器、过压保护电路、二阶模拟抗混叠滤波器、模拟多路复用器、16位200 kSPS SAR ADC 和一个数字滤波器。在电力线路测量和保护系统中,需要对多相输配电网络的大量电流和电压通道进行同步采样。这些应用中,通道数量从6个到64个以上不等。AD7606 8通道数据采集系统(DAS)集成16位双极性同步采样SAR ADC 和片内过压保护功能,可大大简化信号调理电路,并减少器件数量、电路板面积和测量保护板的成本。高集成度使得每个AD7606只需9个低值陶瓷去耦电容就能工作。 图1所示电路包括两个AD7606器件,可以配置为使用2.5 V 内部基准电压源或2.5 V 外部基准电压源ADR421。如果REF SELECT 引脚接逻辑高电平,则选择内部基准电压源。如果REF SELECT 引脚接逻辑低电平,则选择外部基准电压源。 在测量和保护系统中,为了保持多相电力线网络的电流和电压通道之间的相位信息,必须具备同步采样能力。AD7606具有宽动态范围,是捕获欠压/欠流和过压/过流状况的理想器件。输入电压范围可以通过引脚编程设置为±5 V 或±10 V 。 此电路笔记详细介绍针对采用多个AD7606器件应用而推荐的印刷电路板(PCB)布局。该布局在通道间匹配和器件间匹配方面进行了优化,有助于简化高通道数系统的校准程序。当通道间匹配非常重要时,此电路可以使用2.5 V 内部基准电压源AD7606;而对于要求出色绝对精度的高通道数应用,此电路可以使用外部精密基准电压源ADR421,它具有高精度(B 级:最大值±1 mV )、低漂移(B 级:最大值3 ppm/°C )、低噪声(典型值1.75 μV p-p ,0.1 Hz 至10 Hz )等特性。低噪声及出色的稳定性和精度特性使得ADR421非常适合高精度转换应用。这两个器件相结合,能够实现业界前所未有的集成度、通道密度和精度。 电源要求如下:AV CC = 5 V ,V DRIVE = 2.3 V 至5 V (取决于外部逻辑接口要求)。 本电路笔记描述一个评估板的布局和性能,其中内置两个AD7606,构成一个16通道数据采集系统。欲浏览完整的16通道DAS PC 板文档,请访问: https://www.360docs.net/doc/d7287111.html,/CN0148_PCB_Documentation 。 为实现良好的通道间匹配和器件间匹配,模拟输入通道和器件去耦的对称布局非常重要。所示数据支持利用图1所示16通道ADC 实现的匹配性能。 16通道DAS 的双路AD7606板布局 在内置多个AD7606器件的系统中,为确保器件之间的性能匹配良好,这些器件必须采用对称布局。图2显示采用两个AD7606器件的布局。

多通道同步数据采集与处理系统的设计与实现_王浩

297 2009年第01期,第42卷 通 信 技 术 Vol.42,No.01,2009总第205期 Communications Technology No.205,Totally 收稿日期:2008-06-26。 作者简介:王 浩(1982-),男,硕士研究生,主要研究方向为电路设计及D S P 技术;刘文怡(1970-),男,副教授,主要研究方向 为测控系统、信息识别、数据记录,以及相关软件技术;韩志军(1983-),男,硕士研究生,主要研究方向为电路设计。 多通道同步数据采集与处理系统的设计与实现 王 浩, 刘文怡, 韩志军 (中北大学 电子测试技术国家重点实验室,山西 太原 030051) 【摘 要】设计了一种基于DSP 与CPLD 的多通道同步数据采集与处理系统,系统分为多通道同步数据采集模块和DSP 数据处理模块。多通道同步数据采集可实现相关信号同时测量,进行相关分析后,得到信号间的相关信息的要求,而数据处理模块可满足数据处理,实现相关算法等功能。实验中DSP 内嵌数据压缩算法的试验结论表明,该系统能够满足多通道同步数据采集与处理的要求,性能安全,可靠。 【关键词】DSP ;CPLD ;多通道同步数据采集;数据处理 【中图分类号】TN919.5 【文献标识码】A 【文章编号】1002-0802(2009)01-0297-03 Design and Implementation of Multi-channel Synchronous Data Acquisition System WANG Hao , LIU Wen-yi ,HAN Zhi-jun (State Key Laboratory for Electronic Measurement Technology, North University of China, Taiyuan Shaanxi 030051, China) 【Abstract 】Multi-channel synchronous data acquisition system based on DSP and CPLD is designed. The system is constituted by multi-channel synchronous data acquisition module and DSP data processing module.Multi-channel synchronous data acquisition module can realize simulatneous test of the related signal and receive the related information after being analyzed. Data processing module can implements data processing and the related functions of the algorithm. The experiment on the data compression algorithm embedded in DSP indicated that this system can satisfy multichannel synchronous data acquisition and processing requirements,and its performance is secure and reliable. 【Key words 】DSP ;CPLD ;multi-channel synchronous data acquisition ;data processing 0 引言 在现代信号处理系统中,数据采集处理系统越来越广泛地用于各行各业。文中设计实现了基于DSP 与CPLD 的多通道同步数据采集与处理系统,其中,多通道同步数据采集可实现在实际应用中要求对一些相关信号同时进行测量,进行相关分析后,得到信号间的相关信息的要求,而处理模块可满足数据处理,在其系统框架内实现其算法等功能。文章设计的多通道同步数据采集与处理系统,通过程序控制,接口设计,DSP 初始化,DSP 的算法实现具有功能模块化、接口标准化、能够根据用户需求应用灵活多变的特点。 1 多通道同步数据采集模块组成及原理 多通道同步数据采集模块的硬件结构框图如图1所示,模拟信号通过SIN 和AGND 输入,经调理后,通过CPLD 对采样保持器的S/H 控制进行多路同步采样保持,通过CPLD 对模拟开关的SEL 控制进行路选通,这时,XCR3256控制AD 进行单路16位量化采集,然后将采集数据写入到FIFO 缓冲器中。 多通道同步数据采集模块的程序控制采用Verilog HDL 语言,VerilogHDL 是用于逻辑设计的硬件描述语言,并且已成为IEEE 标准[1]。

以太网通道

以太网通道(EthernetChannel)(端口汇聚) 一、基本定义 将两台设备之间的多个物理以太网接口进行逻辑绑定,形成一条虚拟链路,以便增加带 宽。实现负载均衡、主备备份等的一种链路技术,必须是双数链路. 以太网通道必须遵循的一些规则 ●参与捆绑的端口必须都处于同一个VLAN。 ●如果端口配置的是中继模式,那么,应该在链路两端将通道中的所有端口配置成相同的中继模式。 ●所有参与捆绑的端口的物理参数设置必须相同。应该有同样的速度和全双工或者半双工模式设置。也就是说,参与捆绑的链路,速率必须相同。 二、配置 注意事项: Speed Duplex 要一致 相关特性要一致 具体配置: 配置2层以太网通道 Switch(config)#interface fastEthernet 0/1 Switch(config-if)#switchport mode access Switch(config-if)#switchport access vlan 2 Switch(config-if)#channel-group 5 mode ? active Enable LACP unconditionally auto Enable PAgP only if a PAgP device is detected desirable Enable PAgP unconditionally on Enable Etherchannel only passive Enable LACP only if a LACP device is detected Switch(config-if)#channel-group 5 mode auto Switch#show run 配置3层以太网通道 在3750及以前系列中应该首先通过全局命令手动创建一个端口通道逻辑接口 然后使用channel-group 接口配置命令把逻辑接口添加到通道组中 Switch(config-if)#interface port-channel 15 Switch(config-if)#no switchport Switch(config-if)#ip address 192.168.2.2 255.255.255.0 Switch(config-if)#end Switch# 把物理接口添加到通道组中 Switch(config)#interface fastEthernet 0/3 Switch(config-if)#no ip address Switch(config-if)#no switchport

电力系统中多通道同步采样ADC(AD7606)与浮点DSP(ADSP-21479)通信的设计与实现

电力系统中多通道同步采样ADC(AD7606)与浮点 DSP(ADSP-21479)通信的设计与实现 内容 1.简介31.1 AD7606 简介31.2 ADSP-21479 简介4 2.AD7606 和ADSP- 21479 配置与连接5 3.时序分析6 4.测试结果和结论74.1 测试结果74.2 结论10 5.DSP 参考代码10 6.参考文献12 1.简介1.1 AD7606 简介AD7606 是16 位,8 通道同步采样模数数据采集系统。AD7606 完全满足电力系统的要求,具有灵活的数字滤波器、 2.5V 基准电 压源、基准电压缓冲以及高速串行和并行接口。它采用5V 单电源供电,可以 处理±10V 和±5V 真双极性输入信号、同时所有通道均能以高 达200kSPS 的吞吐率采样。图1 AD7606 的内部原理框图。图2 AD7606 的管脚图。AVcc 模拟电源,4.75V~5.25V Vdrive 逻辑部分电源Vdd 模拟输入部 分正电压Vss 模拟输入部分负电压DGND 数字地AGND 模拟地 1.2 ADSP-21479 简介ADSP-21479 是SIMD (单指令多数据)SHARC 家族中的一员,它基于65nm 的最新工艺,具有低成本,低功耗的的特点,是一 颗集成有大容量片上SRAM 和ROM 的32/40 位浮点DSP。ADSP-21479 是性 能出色,266MHZ/1596MFLOP: 266 MHz/1596FLOPS SIMD SHARC 内核,支持32-bit 浮点、40-bit 浮点以及16/32-bit 定点数据类型支持多达5 Mb 片内SRAM 支持16 位宽SDR、SDRAM 存储器接口数字应用接口DAI,支持多达8 个的高速同步串 口(SPORT)及SPI 串口 2 个精确时钟发生器20 线数字I/O 端口 3 个定时器、UART、I2C 兼容接口ROM/JTAG 安全模式供应196 引脚CSP_BGA 封装与100 引脚LQFP 封装产品,适合于工业客户的要求供应商业级、工业级温度与

以太网通道+VLAN+STP+HSRP+3层交换配置

以太网通道+VLAN+STP+HSRP+3层交换配置 由于水平有限,不对的地方还望高手指教,这里先谢过了。由于cisco的PACKET TRACER 5。2还不支持HSRP ,所以只写出了配置步骤。 1.先上拓扑图。 1.路由器RA的配置步骤,这里没有涉及到路由器的很多配置,都是很简单的基本配置,不在详细说明,直接上SHOW R RA#show s % Ambiguous command: "show s" RA#show r Building configuration... Current configuration : 838 bytes ! version 12.2 no service timestamps log datetime msec

no service timestamps debug datetime msec no service password-encryption ! hostname RA ! ! ! ! ! ! ! ! ! ! no ip domain-lookup ! ! ! ! ! ! interface FastEthernet0/0 ip address 192.168.2.1 255.255.255.0 duplex auto speed auto ! interface FastEthernet1/0 ip address 192.168.1.1 255.255.255.0 duplex auto speed auto ! interface Serial2/0 no ip address shutdown ! interface Serial3/0 no ip address shutdown ! interface FastEthernet4/0 no ip address shutdown ! interface FastEthernet5/0

多通道AD采样同步设计

64 | 电子制作 2019年02-03月 变,也可进行试验过程中所需电压、电流等物理量的测量。在数据测量过程中,如果采集通道数量较多,采集速度要求较高时,如何保证多个测量点的测量数据保持同步性是如今数据采集系统设计中需要解决的问题。保持多块采集板卡之间的同步性,可以使用时钟同步线,或者以太网同步时间戳等方式完成。基于单块采集板卡多通道之间的同步设计问题是本文的研究内容。 在具体介绍本文的设计之前需要解释两个问题:①为了保证单块板卡多通道同步问题,采集板卡的硬件设计显然不 能使用单一AD 芯片加多通道切换方式,因为通道切换产生 的时间间隔就已经使得各通道之间不能保持同步;②多个AD 芯片寄存器的同步读写可以使用FPGA 作为很好的解决方案,但是考虑到FPGA 使用门槛较高,并且在完成数据采集系统其他功能,例如:CAN 总线通讯、以太网通讯、触摸屏显示等方面不是那么的方便快捷。所以本文采用飞思卡尔的i.MX6Q 处理器加多路AD7734作为硬件结构,在此基础 上完成多通道的同步采集设计。 作为转换芯片,每一个AD7734芯片有四路采样输入通道可供切换,可以满足每一个测量通道三路不同种类模拟信号的采集。具体AD 转换电路见图1。 AD7734数模转换芯片共有4个模拟输入口AIN0~ AIN3,可以通过操作相应寄存器进行四个通道的切换采样。最高可接受10V 单极或双极电压输入,并具有超量程或欠 量程检测功能。与主控芯片连接的通讯口共6个管脚功能如表1所示。 表1 AD7734 IO管脚定义 管脚功能 SCLK 寄存器操作时钟DOUT 寄存器读取管脚DIN 寄存器写入管脚C _____ S 片选 R ________D Y 数模转换完成标志位管脚 R ____________ E S E T 复位管脚为了能够保证采集模块中8个AD 转换芯片的同步操作, 硬件设计示意图如图2所示(图中只示意性的画了4个AD 芯片)。 图1?AD 转换电路图

交换机以太通道中继线路的配置

实验一 一.实验拓扑图 二.实验要求 1、在两台2950交换机上创立VLAN10、VLAN20、VLAN30和VLAN40。 2、把两个交换机上的interface f0/21 分配给VLAN10,interface f0/22 分配给VLAN20,interface f0/23 分配给VLAN30,interface f0/24 分配给VLAN40。 3、每台交换机的interface f0/5 配置为两台交换机的中继端口,实现VLAN数据传输。 4、配置两台交换机的interface f0/1 ,interface f0/2 的端口做以太通道中继线路。三.网络接口 2950A接口1<--→2950B接口1 2950A接口2<--→2950B接口2 2950A接口5<--→2950B接口5 四.实验配置 2950交换机的配置: Switch>en //进入特权模式 Switch#config t //进入全局配置模式 Switch(config)#hostname 2950A//设置主机名为2950A 2950A(config)#no ip do lo //关闭域名解析功能 2950A(config)#line con 0 //进入控制线0 2950A(config-line)#logg syn //光标同步 2950A(config-line)#exec-time 0 0 //对Console口进行空闲超时时间的配置2950A(config-line)#exit // 返回全局配置模式 2950A(config)#end //返回特权模式 2950A#vlan database //进入VLAN数据库 2950A(vlan)#vlan 10 //创建VLAN10 VLAN 10 added: Name: VLAN0010 2950A(vlan)#vlan 20 //创建VLAN20 VLAN 20 added: Name: VLAN0020 2950A(vlan)#vlan 30 //创建VLAN30 VLAN 30 added: Name: VLAN0030 2950A(vlan)#vlan 40 //创建VLAN40 VLAN 40 added: Name: VLAN0040

高速多通道同步采样ADC MAX1312及其应用

高速多通道同步采样ADC MAX1312及其应用 【摘要】阐述了MAX1312的特性和工作原理,介绍了MAX1312与通用8位微处理器AT89C52的硬件接口设计以及软件编程方法,最后简述了该模数转换器在多相电机控制中的应用。 【关键词】模数转换器;多通道;同步采样;MAX1312 Abstract:The principle,features and application of multi-channel synchronized sample ADC MAX1312 are introduced,including its hardware interface design and software programming method between MAX1312 and Micro-processor.AT89C52.At last,it describes the application of MAX1312 in controlling the polyphase electric engine. Keywords:A/D converter;multi-channel;synchronized sample;MAX1312 1.引言 在电子测量技术中,必须把模拟信号转换为数字信号,才能够用计算机系统进行处理,模/数转换的速度和精度一直是测量的关键。但是高速和高精确度的转换器仍然难以满足某些特殊场合的要求,例如:在多相电机控制、多相电源监控等场合,要求对多路数据进行精确同步的采集,一般的单通道A/D和多通道轮流采集A/D都不满足这种场合的要求。MAX1312是美国美信公司(MAXIM)新推出的一种高速同步采样模数转换器,它具有12位的精度,8路模拟信号输入,单电源+5V供电,完成8个通道的转换时间仅需要1.96us,对外提供了一个12位20MHZ并行数字接口,可以很方便与各种微处理器相连接,使用十分方便[1]。 2.MAX1312简介 MAX1312是美国美信公司(MAXIM)新推出的多通道同步采样、并行输出模数转换器。采用TQFP48封装,引脚形式如图1所示。 其中: CH0-CH7为八路模拟信号的输入端; D0-D7为八位双向数据总线,用来写入控制字或读出低8位转换结果; D8-D11为高四位数据输出口,当RD=1或CS=1时为高阻状态; CS为片选引脚低电平有效,低电平将激活数字接口,保持高电平时,数字总线为高阻状态;

电力系统中多通道同步采样AD7606与浮点DSP通信的设计与实现

电力系统中多通道同步采样AD7606与浮点DSP通信的设计与实现

电力系统中多通道同步采样ADC(AD7606)与浮点DSP (ADSP-21479)通信的设计与实现 内容 1. 简介3 1.1 AD7606简介3 1.2 ADSP-21479简介4 2. AD7606和ADSP-21479配置与连接5 3. 时序分析6 4. 测试结果和结论7 4.1测试结果7 4.2结论10 5. DSP参考代码10 6. 参考文献12 1简介 1.1AD7606简介 AD7606是16位,8通道同步采样模数数据采集系统。AD7606完全满足电力系统的要求,具有灵活的数字滤波器、2.5V基准电压源、基准电压缓冲以及高速串行和并行接口。它采用5V单电源供电,可以处理±10V和±5V真双极性输入信号、同时所有通道均能以高达200kSPS 的吞吐率采样。

图1 AD7606的内部原理框图。 图2 AD7606的管脚图。 ? A Vcc 模拟电源,4.75V~5.25V ? Vdrive 逻辑部分电源 ? Vdd 模拟输入部分正电压 ? Vss 模拟输入部分负电压

? DGND 数字地 ? AGND 模拟地 1.2ADSP-21479简介 ADSP-21479是SIMD (单指令多数据)SHARC家族中的一员,它基于65nm的最新工艺,具有低成本,低功耗的的特点,是一颗集成有大容量片上SRAM和ROM的32/40位浮点DSP。ADSP-21479是性能出色,266MHZ/1596MFLOP: ? 266 MH z/1596FLOPS SIMD SHARC内核,支持32-bit浮点、40-bit浮点以及16/32-bit 定点数据类型 ? 支持多达5 Mb 片内SRAM ? 支持16位宽SDR、SDRAM存储器接口 ? 数字应用接口DAI,支持多达8个的高速同步串口(SPORT)及SPI串口 ? 2个精确时钟发生器 ? 20线数字I/O端口 ? 3个定时器、UART、I2C兼容接口 ? ROM/JTAG安全模式 ? 供应196引脚CSP_BGA封装与100引脚LQFP封装产品,适合于工业客户的要求? 供应商业级、工业级温度与汽车级温度等级产品 图3 ADSP-21479的内部原理框图。

配置以太网跨板链路聚合组

配置以太网跨板链路聚合组 跨板链路聚合组(DLAG)可以提高链路可靠性、减少保护倒换的影响面,并提高网络升级的安全性和便捷性。配置了DLAG后,当主用单板检测到任一端口链路故障、单板离线、单板硬件故障时,设备的交叉单板会将主用单板上的发生故障的业务切换到备用单板,实现业务保护。 创建DLAG 设置两块相同单板上对应端口的主备用关系和恢复模式,实现端口的1+1保护。 前提条件 用户具有“网元操作员”及以上的网管用户权限。 背景信息 DLAG功能使用限制: ?配置DLAG的设备必须与运行LACP协议的设备对接。若配置了DLAG的两个设备之间存在中间节点,则该中间节点设备必须支持协议报文的透传。 ?只能在两个相同单板间形成主备保护关系,备用板的端口只能用于保护主用板的端口。 ?一个DLAG最多包括两个端口,且端口号必须一致。 ?备用板不能配置业务(包括以太网业务、LAG、交叉链接、LPT和VCTRUNK端口绑定通道)。 ?备用板所在槽位的带宽必须大于或等于主用板的带宽。 ?同一块以太网数据板上BPS、PPS和DLAG保护不能共存。 ?配置DLAG的端口必须是以太网外部物理端口,同一端口不能同时配置DLAG和LAG。 ?配置DLAG组时,备用端口属性会自动与主用端口保持一致。 ?禁止对需要配置DLAG的外部物理端口自环。 ?如果已创建了以太网业务,需要保证通道时隙的绑定级别和配置交叉业务的级别一致。 ?如果已创建了以太网业务,需要保证需配置DLAG的外部物理端口不能和其它外部物理端口共享同一VCTRUNK端口。 ?DLAG的一个外部物理端口可以对应多个VCTRUNK端口,而一个VCTRUNK端口只能对应DLAG的一个外部物理端口。不同DLAG的外部物理端口不能配置在同一个VB,因为这样会导致一个VCTRUNK端口对应多个外部物理端口。

电力系统中多通道同步采样AD7606与浮点DSP通信的设计与实现

电力系统中多通道同步采样ADC(AD7606)与浮点DSP (ADSP-21479)通信的设计与实现 内容 1. 简介3 1.1 AD7606简介3 1.2 ADSP-21479简介4 2. AD7606和ADSP-21479配置与连接5 3. 时序分析6 4. 测试结果和结论7 4.1测试结果7 4.2结论10 5. DSP参考代码10 6. 参考文献12 1简介 1.1AD7606简介 AD7606是16位,8通道同步采样模数数据采集系统。AD7606完全满足电力系统的要求,具有灵活的数字滤波器、2.5V基准电压源、基准电压缓冲以及高速串行和并行接口。它采用5V单电源供电,可以处理±10V和±5V真双极性输入信号、同时所有通道均能以高达200kSPS 的吞吐率采样。

图1 AD7606的内部原理框图。 图2 AD7606的管脚图。? A Vcc模拟电源,4.75V~5.25V ? Vdrive逻辑部分电源 ? Vdd模拟输入部分正电压 ? Vss模拟输入部分负电压 ? DGND 数字地

? AGND 模拟地 1.2ADSP-21479简介 ADSP-21479是SIMD (单指令多数据)SHARC家族中的一员,它基于65nm的最新工艺,具有低成本,低功耗的的特点,是一颗集成有大容量片上SRAM和ROM的32/40位浮点DSP。ADSP-21479是性能出色,266MHZ/1596MFLOP: ? 266 MHz/1596FLOPS SIMD SHARC内核,支持32-bit浮点、40-bit浮点以及16/32-bit 定点数据类型 ? 支持多达5 Mb 片内SRAM ? 支持16位宽SDR、SDRAM存储器接口 ? 数字应用接口DAI,支持多达8个的高速同步串口(SPORT)及SPI串口 ? 2个精确时钟发生器 ? 20线数字I/O端口 ? 3个定时器、UART、I2C兼容接口 ? ROM/JTAG安全模式 ? 供应196引脚CSP_BGA封装与100引脚LQFP封装产品,适合于工业客户的要求? 供应商业级、工业级温度与汽车级温度等级产品 图3 ADSP-21479的内部原理框图。

华为以太网通道配置

2层3层以太网通道建立

配置2层以太网通道 Switch(config)#interface fastEthernet 0/1 Switch(config-if)#switchport mode access Switch(config-if)#switchport access vlan 2 Switch(config-if)#channel-group 5 mode ? active Enable LACP unconditionally auto Enable PAgP only if a PAgP device is detected desirable EnablePAgP unconditionally on Enable Etherchannel only passive Enable LACP only if a LACP device is detected Switch(config-if)#channel-group 5 mode auto Switch#show run 配置3层以太网通道 Switch(config-if)#interface port-channel 15 Switch(config-if)#no switchport Switch(config-if)#ip address 192.168.2.2 255.255.255.0 Switch(config-if)#end Switch# 把物理接口添加到通道组中 Switch(config)#interface fastEthernet 0/3 Switch(config-if)#no ip address Switch(config-if)#no switchport

以太网通道概述

以太网通道概述 9.6 以太网通道基础 本节将介绍如何在Cisco Catalyst交换机的二层和三层端口上配置以太网通道(也就是说有二层以太网通道和三层以太网通道之分)。以太网通道可以为交换机、路由器和服务器间提供高速容错链路。可以用它来提高配线室和数据中心间的带宽,也可以在网络中任何认为有可能出现性能瓶颈的位置部署它。 以太网通道通过重新分配负载,在当前可用的链路上恢复失效的链路。如果一个链路失效了,以太网通道会自动重定向失效途径链路上的通信到正常工作的链路上。 9.6.1 以太网通道概述 如图9-8所示是由多个千兆以太网链路捆绑在一起形成的一个单一逻辑链路的以太网通道的典型示例。 一个快速以太网通道最高可以在你的交换机和其他交换机或主机间提供800 Mb/s的全双工带宽(实际上是1.6Gb/s),而一个千兆以太网通道可以在你的交换机和其他交换机或主机间提供最高8Gb/s的全双工带宽(实际上是16Gb/s)。但要注意,以上所说的都是基于双绞线以太网端口的,因为光纤通道不支持全双工配置,所以最高支持的带宽也就在以上基础上减半了。

每个以太网通道可以包括最多8个适当配置的以太网端口,以太网通道中的所有端口都必须配置为二层或三层端口。交换机可以创建的以太网通道的数量因为系列不同而有所不同,如在Catalyst 3750及以前系列的Cisco 交换机中,以太网通道的数量限制为最多48个,而Catalyst 4500系列则允许最多配置64个以太网通道,Catalyst 6500系列则允许最多有128个以太网通道,具体参见相应产品的说明书。三层以太网通道端口是由可路由端口组成的。可路由端口是物理接口通过no switchport 接口配置命令配置成三层端口的。 可以手动配置以太网通道,也可以用以下两种协议来自动形成以太网通道:PAgP (Port Aggregation Protocol ,端口汇聚协议)、LACP (Link Aggregation Control Protoco ,链路汇聚控制协议)。但是以太网通道中的两端必须是相同协议的。PAgP 是Cisco 专有的协议,而LACP 是在IEEE 802.3ad 标准中定义的。 PAgP 与LACP 相互不兼容,也就是说在一个以太网通道中不能同时存在这两种协议。当在PAgP 或LACP 模式下配置一端的以太网通道时,系统会自动与以太网通道的另一端协商,以决定激活哪个端口。通道中的其余端口被置于暂停状态。自Cisco IOS 12.2(35)SE 版本开始,取代挂起状态( Suspended State ),本地端口被置于独立状态(Independent State ),可以继续承载数据通信,就像其他单一链路端口一样。通道中的这些端口配置没有改变,但它们不再参与到以太网通道中。 表9-13列出了用户可配置的以太网通道模式。 表9-13 以太网通道模式

以太网业务配置流程

点到点EPL业务配置方法:EFT---EFS01. 一.了解业务需求及环路使用情况。 根据电路调度单查看要开通电路的带宽,需要绑定2M数量;查看基站所在环路是否能满足以太网业务配置的传输需求。 二.配置SDH交叉连接。 在路径配置视图下,点击基站EFT单板选用第二个VC4中时隙;点击EFS0单板选择第四个或者第八个VC4中的时隙,根据SDH业务配置原则进行业务配置,并激活电路。 注意:EFT/EFS单板一般插放在小盒子上,且小盒子不支持时分交叉,所以在EFT/EFS单板选择的时隙要和线路侧选择的时隙一致。三.配置以太网板

EFT单板配置 1以太网业务配置 网元管理器---选中EFT单板---配置---以太网业务 根据电路调度单选择port端口(EFT单板的port端口和vctrunk 是绑定),在绑定通道一栏下,点击配置: 可配置端口---port端口和vctrunk是绑定的,这里不需要选择。级别:VC12级别(根据实际需求选择,本次是配置2M业务) 方向:双向。 可选时隙:选择配置SDH路径的时隙。 2以太网接口管理 网元管理器---选中EFT单板---配置---以太网接口管理 外部端口: 基本属性,选择需要配置的port端口:端口是能选择使能,工作模

式:根据具体情况选择(华为设备一般不选自适应工作模式)。 内部端口: 不用更改属性,选择默认。

3以太网接口协议设置: 内部端口:保证互开业务的内部端口的封装协议一致。(一般选为GFP协议) EFS0单板配置: 1以太网业务配置 网元管理器---选中EFS0单板---配置---以太网业务 根据电路调度单选择port端口,在绑定通道一栏下,点击新建:单板:选择本次配置单板 业务类型。 级别:VC12级别(根据实际需求选择,本次是配置2M业务) 方向:双向。 源端口:根据调单号选择port端口。 宿端口:选择vctrunk(一般port和VCTRUNK保持一致,便于维

CISCO中以太通道配置

实验三以太通道 一、实验目的 1):本实验的目的是通过配置以太通道,让我们对以太通道的工作原理有更深的认识。 2):掌握以太通道配置方法,对以太通道在网络上的应用有更深的了解。 二、实验要求: 1):知道以太通道工作原理 2): 知道如何配置以太通道 实验拓朴: 1) 创建SW1和SW2的Etherchannel SW1(config)#int port-channel 1 SW2(config)#int port-channel 1 2) 设置物理接口将其加入到通道中 SW1(config)#int rang f0/1 -2 SW1(config-if)#channel-group 1 mode on SW2(config)#int rang f0/1 -2 SW2(config-if)#channel-group 1 mode on 3) 设置物理接属性 SW1(config-if)#switchport mode trunk SW1(config-if)#speed 100 SW1(config-if)#duplex full SW2(config-if)#switchport mode trunk SW2(config-if)#speed 100 SW2(config-if)#duplex full 4) 配置etherchannel负载均衡 SW1(config)#port-channel load-banlance src-mac SW2(config)#port-channel load-banlance src-mac 5) 查看etherchannel SW1#sh etherchannel detailk

以太网通道配置

以太网通道配置 2011-05-05 13:06 以太网通道 以太网通道 负载均衡实现 1.提高带宽 2.实现冗余 最多可以捆绑八条物理链路 以太网通道要求: 1.参与捆绑的端口必须属于同一VLAN 2.如果端口配置的是中继模式,那么,应该在链路两端将通道中的所有端口 配置成相同的中继模式 3.所用参与捆绑的端口的物理参数设置必须相同,同样的速度和全/半双工模 式设置。lacp要求端口只能工作在全双工模式下。 Pagp(端口汇聚协议)和LACP(链路汇聚控制协议) Cisco交换机提供了两种进行协商以太网通道的协议:端口聚合协议Pagp和链路聚合控制协议LACP Pagp是Cisco专用的以太网通道协议 模式有开启(on),关闭(off),自动(auto),企望(desirable) LACP是IEEE802.3ad标准协议。 模式有开启(on),关闭(off),被动(passive),主动(active) 1.所用主机和服务器都属于VLAN20 2.交换机之间接口配置为Trunk模式

配置过程: Sw1配置vlan 20 和端口加入vlan20 Switch>en Switch#conf t Switch(config)#host sw1 sw1(config)#vlan 20 sw1(config-vlan)#exit sw1(config)#int range f0/3 -4 sw1(config-if-range)#switchport mode access sw1(config-if-range)#switchport access vlan 20 sw1(config-if-range)#exit 配置Pagp以太网通道 sw1(config)#int range f0/1 -2 sw1(config-if-range)#switchport m t channel-protocol pagp (LACP) sw1(config-if-range)#channel-group 1 mode on(auto \ desirable) sw1(config-if-range)#end sw2配置 创建vlan 20 Switch>en Switch#conf t Switch(config)#vlan 20 Switch(config-vlan)#exit 配置Pagp以太网通道 Switch(config)#int range f0/1 -2 Switch(config-if-range)#switchport m t channel-protocol pagp(LACP) Switch(config-if-range)#channel-group 1 mode on(auto \ desirable) Switch(config-if-range)#exit 端口加入vlan 20 Switch(config)#int f0/3 Switch(config-if)#switchport mode access Switch(config-if)#switchport access vlan 20 Switch(config-if)#exit Switch(config)#exit sw1(config-if-range)#exit