PCB Layout Recommendations for BGA packages

? 2011 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at https://www.360docs.net/doc/db11169796.html,/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

February 2011

Technical Note TN1074

Introduction

As Ball Grid Array (BGA) packages become increasingly popular and become more populated across the array with higher pin count and smaller pitch, it is important to understand how they are affected by various board layout techniques. This document provides a brief overview of PCB layout considerations when working with BGA pack-ages. It outlines some of the most common problems and provides tips for avoiding them at the design stage. A key challenge of adopting fine-pitch (0.8 mm or less) BGA packages is the design of a route fanout pattern that maxi-mizes I/O utilization while minimizing fabrication cost. This technical note provides an overview of PCB design examples provided by Lattice Semiconductor.

For more information and design examples see the PCB Design Support page at the Lattice Semiconductor web site (https://www.360docs.net/doc/db11169796.html,/support/pcbdesignsupport.cfm ).

BGA Board Layout Recommendations

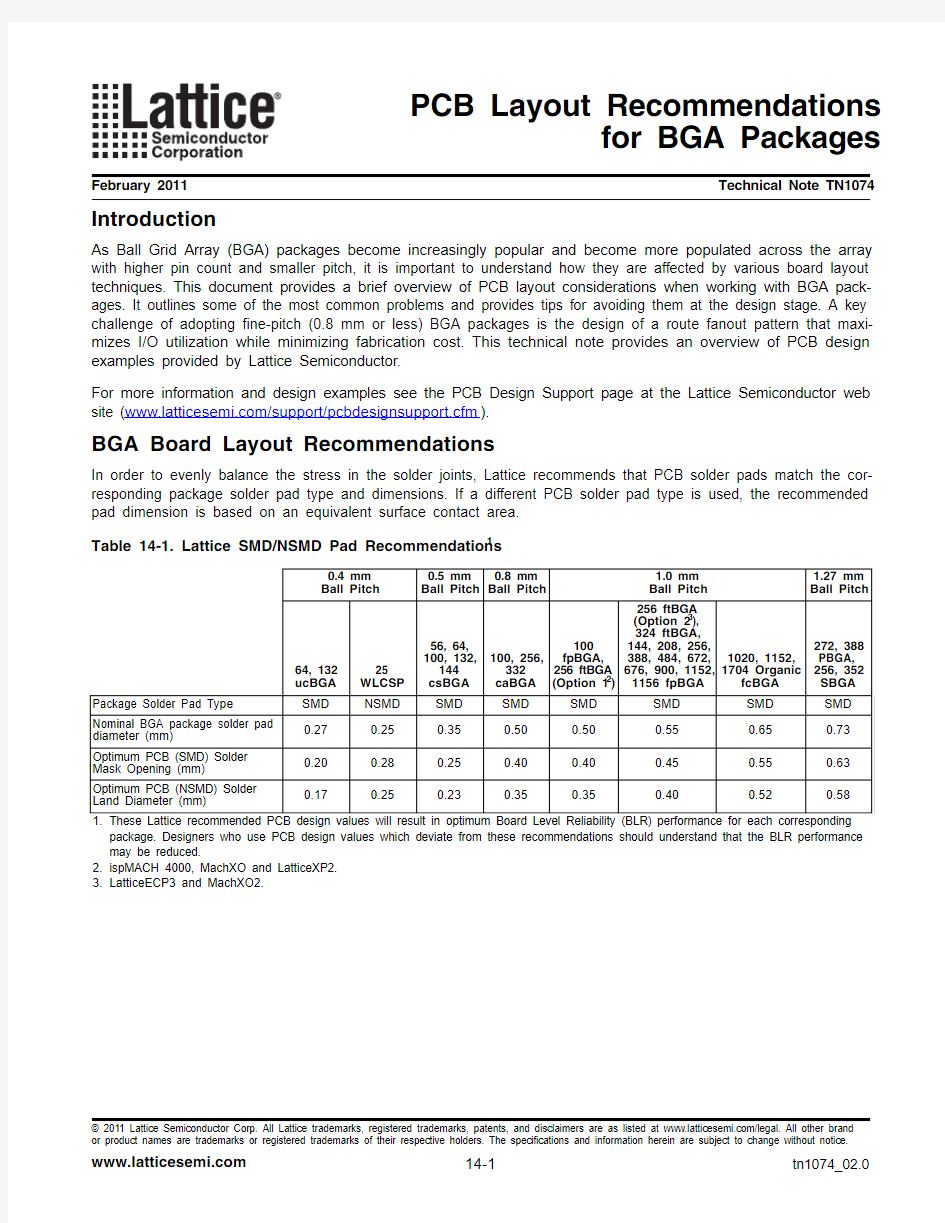

In order to evenly balance the stress in the solder joints, Lattice recommends that PCB solder pads match the cor-responding package solder pad type and dimensions. If a different PCB solder pad type is used, the recommended pad dimension is based on an equivalent surface contact area.Table 14-1. Lattice SMD/NSMD Pad Recommendations 1

0.4 mm Ball Pitch

0.5 mm Ball Pitch 0.8 mm Ball Pitch

1.0 mm Ball Pitch

1.27 mm Ball Pitch

64, 132 ucBGA

25 WLCSP 56, 64, 100, 132, 144 csBGA 100, 256, 332 caBGA 100

fpBGA,

256 ftBGA (Option 12)256 ftBGA (Option 23), 324 ftBGA,144, 208, 256, 388, 484, 672, 676, 900, 1152, 1156 fpBGA 1020, 1152, 1704 Organic

fcBGA 272, 388

PBGA, 256, 352 SBGA Package Solder Pad T ype SMD NSMD SMD SMD SMD SMD SMD SMD Nominal BGA package solder pad diameter (mm)

0.270.250.350.500.500.550.650.73Optimum PCB (SMD) Solder Mask Opening (mm)

0.200.280.250.400.400.450.550.63Optimum PCB (NSMD) Solder Land Diameter (mm)

0.17

0.25

0.23

0.35

0.35

0.40

0.52

0.58

1.These Lattice recommended PCB design values will result in optimum Board Level Reliability (BLR) performance for each corresponding package. Designers who use PCB design values which deviate from these recommendations should understand that the BLR performance may be reduced.

2.ispMACH 4000, MachXO and LatticeXP2.

https://www.360docs.net/doc/db11169796.html,tticeECP3 and MachXO2.

PCB Layout Recommendations

for BGA Packages

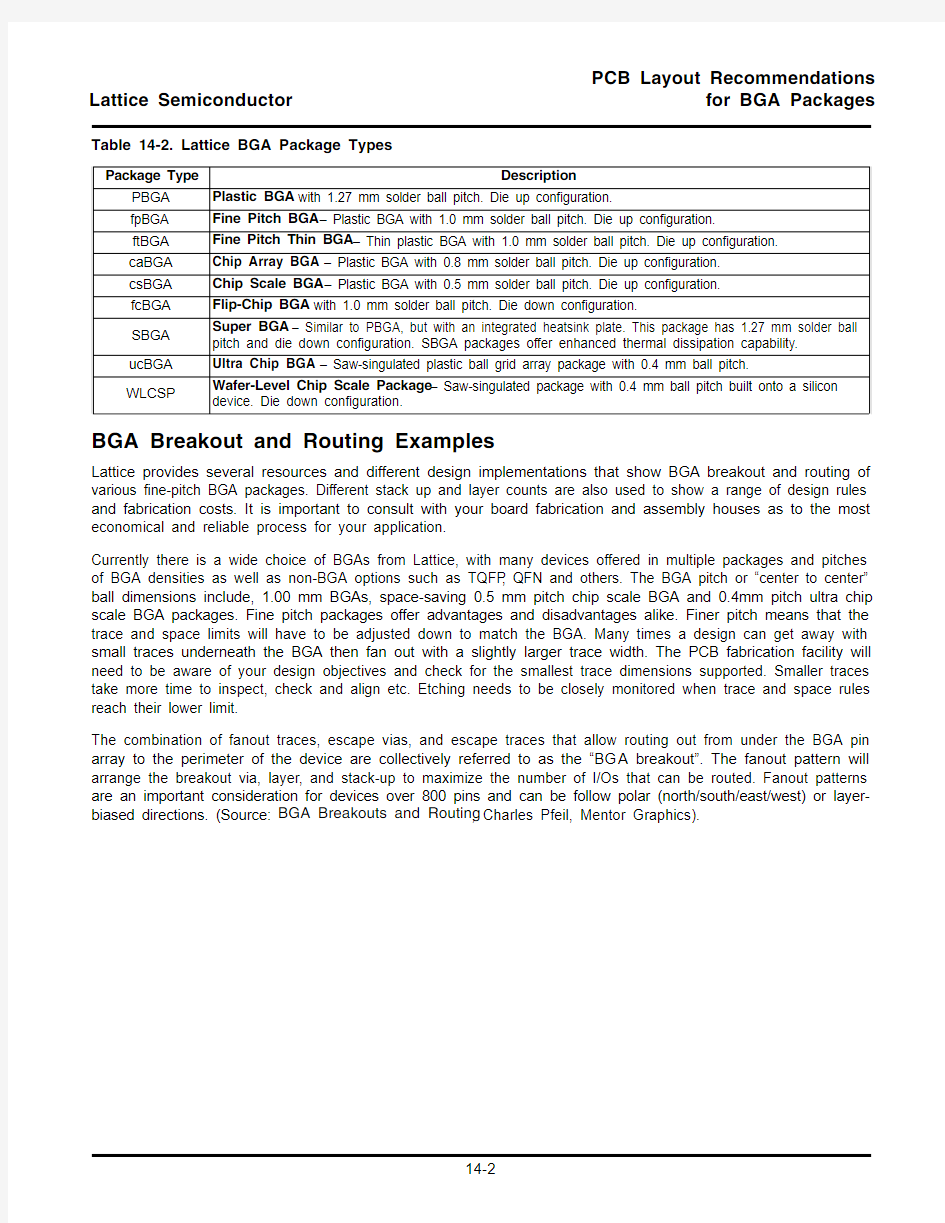

Table 14-2. Lattice BGA Package Types

BGA Breakout and Routing Examples

Lattice provides several resources and different design implementations that show BGA breakout and routing of various fine-pitch BGA packages. Different stack up and layer counts are also used to show a range of design rules and fabrication costs. It is important to consult with your board fabrication and assembly houses as to the most economical and reliable process for your application.

Currently there is a wide choice of BGAs from Lattice, with many devices offered in multiple packages and pitches of BGA densities as well as non-BGA options such as TQFP , QFN and others. The BGA pitch or “center to center” ball dimensions include, 1.00 mm BGAs, space-saving 0.5 mm pitch chip scale BGA and 0.4mm pitch ultra chip scale BGA packages. Fine pitch packages offer advantages and disadvantages alike. Finer pitch means that the trace and space limits will have to be adjusted down to match the BGA. Many times a design can get away with small traces underneath the BGA then fan out with a slightly larger trace width. The PCB fabrication facility will need to be aware of your design objectives and check for the smallest trace dimensions supported. Smaller traces take more time to inspect, check and align etc. Etching needs to be closely monitored when trace and space rules reach their lower limit.

The combination of fanout traces, escape vias, and escape traces that allow routing out from under the BGA pin array to the perimeter of the device are collectively referred to as the “BG A breakout”. The fanout pattern will arrange the breakout via, layer, and stack-up to maximize the number of I/Os that can be routed. Fanout patterns are an important consideration for devices over 800 pins and can be follow polar (north/south/east/west) or layer-biased directions. (Source: BGA Breakouts and Routing , Charles Pfeil, Mentor Graphics).

Package Type

Description

PBGA Plastic BGA with 1.27 mm solder ball pitch. Die up configuration.

fpBGA Fine Pitch BGA – Plastic BGA with 1.0 mm solder ball pitch. Die up configuration.

ftBGA Fine Pitch Thin BGA – Thin plastic BGA with 1.0 mm solder ball pitch. Die up configuration.caBGA Chip Array BGA – Plastic BGA with 0.8 mm solder ball pitch. Die up configuration.csBGA Chip Scale BGA – Plastic BGA with 0.5 mm solder ball pitch. Die up configuration.fcBGA Flip-Chip BGA with 1.0 mm solder ball pitch. Die down configuration.

SBGA Super BGA – Similar to PBGA, but with an integrated heatsink plate. This package has 1.27 mm solder ball pitch and die down configuration. SBGA packages offer enhanced thermal dissipation capability.ucBGA Ultra Chip BGA – Saw-singulated plastic ball grid array package with 0.4 mm ball pitch.

WLCSP

Wafer-Level Chip Scale Package – Saw-singulated package with 0.4 mm ball pitch built onto a silicon device. Die down configuration.

Figure 14-1. BGA Breakout Routing Terms

Lattice provides BGA breakout and routing examples for various fine pitch packages (https://www.360docs.net/doc/db11169796.html,/sup-port/pcbdesignsupport/bgabreakoutroutingexample/index.cfm ). Each package example is built to comply with IPC7351 (https://www.360docs.net/doc/db11169796.html,) specifications and nomenclature conventions. Some examples include different layout options depending on design and cost goals. For example, the 256-ball chip array BGA (BN256/BG256) examples demonstrate a design with fully-utilized I/Os, fine trace width and pitch, on a 6-layer PCB stack-up and a less expensive design with relaxed design rules, and fewer I/O pads routed, on a 4-layer PCB stack up.Table 14-3. Package Layout Example Summary

For mechanical dimension details on packages, see the Lattice Package Diagrams document.

In order to show how some of the routing challenges are solved, examples are provided for fine-pitch BGA pack-ages from the MachXO? and the ispMACH ? 4000ZE families. Principles for these apply to other Lattice BG A packaged products.

Package Example #

Pitch (mm)

Signal/Power Layers Trace/Width-Space (mm)Ball Pad (mm)Ball Mask (mm)Via Pad (mm)Via Drill (mm)MN64/MG6410.56.100/.1000.230.330.300.125UMN64/UMG6410.46.100/.1000.180.280.250.10MN100 10.54.085/.0850.230.380.450.2020.54.100/.1000.230.380.450.20MN132/MG13210.54.085/.0850.230.380.400.1520.54.100/.1000.230.380.400.15MN144 10.56.100/.1000.230.330.300.12520.54.100/.1000.230.380.300.125BN256/BG256

10.86.100/.1000.350.500.400.1252

0.8

4

.100/.100

0.35

0.50

0.40

0.15

64-ball csBGA BGA Breakout and Routing Example

This example places an ispMACH 4000ZE CPLD in a 5x5 mm, 0.5 mm pitch, 64-ball csBGA package (LC4064ZE-MN64) in an 6-layer stack up with maximum I/O utilization. Figure 14-2. CAM Artwork Screen Shots 64-Ball csBGA

Layer 1 Primary

Layer 2 Signal

Layer 3 GND

Layer 4 Power

Layer 5 Signal

Layer 6 Secondary

64-ball ucBGA BGA Breakout and Routing Example

This example places an ispMACH 4000ZE CPLD in a 4x4 mm, 0.4 mm pitch, 64-ball ucBGA package (LC4064ZE-UMN64) in an n-layer stack up with maximum I/O utilization. This example demonstrates a modified dogbone fanout technique to get access to all pins yet limiting number of layers and via schedules, while setting up layers to use reference planes for high-speed signal traces.

Figure 14-3. CAM Artwork Screen Shots, 64-Ball ucBGA

Layer 1 Primary

Layer 2 GND

Layer 3 Signal

Layer 4 Signal

Layer 5 Power

Layer 6 Secondary

100-ball csBGA BGA Breakout and Routing Examples

These examples place a MachXO PLD in a 8x8 mm, 0.5 mm pitch, 100-ball csBG A package (LCMXO640-M100/MN100) into two fabrication scenarios. One for a 6-layer stack up with maximum I/O utilization and a 4-layer with about 15% fewer I/Os. The 4-layer (Example #2) design makes maximum use of via and trace geometry to reduce layer count and ease fabrication while still maintaining high I/O usage. Figure 14-4. CAM Artwork Screen Shots, Example #1, 100-ball csBGA

Layer 1 Primary

Layer 2 GND

Layer 3 Power

Layer 4 Secondary

Figure 14-5. CAM Artwork Screen Shots, Example #2, 100-ball csBGA

Layer 1 Primary

Layer 2 GND

Layer 3 Power

Layer 4 Secondary

132-ball csBGA BGA Breakout Examples

These examples place a MachXO PLD in a 8x8 mm, 0.5 mm pitch, 132-ball csBG A package (LCMXO640-M132/MN132) into two fabrication scenarios. One for a 6-layer stack up with maximum I/O utilization and a 4-layer with about 15% fewer I/Os.

Figure 14-6. CAM Artwork Screen Shots, Example #1, 132-ball csBGA

Layer 1 Primary

Layer 2 GND

Layer 3 Power

Layer 4 Secondary

Figure 14-7. CAM Artwork Screen Shots, Example #2, 132-ball csBGA

Layer 1 Primary

Layer 2 GND

Layer 3 Power

Layer 4 Secondary

144-ball csBGA BGA Breakout Examples

These examples place an ispMACH 4000ZE in a 7x7 mm, 0.5 mm pitch, 144-ball csBGA package (LC4256ZE-MN144) into two fabrication scenarios. One for a 6-layer stack up with maximum I/O utilization and a 4-layer with about 5% fewer I/Os. The 6-layer (Example #1) design avoids uses of micro vias and takes advantage of removed pads on inner layers to route all pins out to 6 layers with good layer structure for high-speed signal integrity.Figure 14-8. CAM Artwork Screen Shots, Example #1, 144-ball csBGA

Layer 1 Primary

Layer 2 GND

Layer 3 Signal

Layer 4 Signal

Layer 5 Power

Layer 6 Secondary

Figure 14-9. CAM Artwork Screen Shots, Example #2, 144-ball csBGA

Layer 1 Primary

Layer 2 GND

Layer 3 Power

Layer 4 Secondary

256-ball caBGA BGA Breakout Examples

This BGA breakout and routing example places a MachXO PLD in a 14x14 mm, 0.8 mm pitch, 256-ball caBGA package (LCMXO2280-B256/BN256) into two fabrication scenarios. One for a 6-layer stack up with maximum I/O utilization and a 4-layer with about 10% fewer I/Os. The 6-layer design (Example #1), demonstrates the best use of mechanically drill blind vias to place caps near power pins to minimize layers.

Figure 14-10. CAM Artwork Screen Shots, Example #1, 256-Ball caBGA

Layer 1 Primary

Layer 2 Signal

Layer 3 GND

Layer 4 Power

Layer 5 Signal

Layer 6 Secondary

Figure 14-11. CAM Artwork Screen Shots, Example #2, 256-ball caBGA

PCB Fabrication Cost and Design Rule Considerations

PCB fabrication cost is a key consideration for many electronics products. By reviewing the IC device package ball density and pitch, I/O signal requirements of your application, and the manufacturing constraints of your PCB fabri-cation facility you can better weigh the trade-offs between design decisions.Choosing the best package for your application involves answering a few questions:

?What is the driving factor in the application? The smallest possible form factor or a low PCB cost??How many I/O signals does the application require?

?What PCB layer stack up will provide the best I/O density within budget??What layout design rules does the printed-circuit board (PCB) vendor support??How many PCB layers does the budget allow?

As the ball pitch becomes smaller with each new BGA generation, new PCB fabrication techniques and signal via type have been developed to handle the complexities. Micro vias, laser vias, filled, buried and blind vias, even bur-ied and plated over vias. Complex boards use a combination of most of these.

Layer 1 Primary

Layer 2 GND

Layer 3 Power

Layer 4 Secondary

Stack-up types, ordered by cost, high-to-low include:

?High-Density Interconnect (HDI) build up with micro vias

?Laminated with blind and buried vias

?Laminated with through vias

Figure 14-12. Stack-up Example

HDI is a “sandwich” with older-style larger geometry in the middle with fully drilled through holes and then a stack of fine geometry of blind, buried or mixed via, laminated both on the top and bottom of the middle stack-up. The laminated layers are thinner than traditional layers and allow finer drilling technology. Staggered micro vias allow vias within close tolerance or connected to a BGA pad to go down to the next layer or more to route away for escape routing or underneath the BGA device for further interconnect. HDI type interconnect is used on complex boards and takes extra steps in the processing flow due to special drilling, plating an laminations. It is a mix of older technology mixed with newer technology that results in a board that is highly routable.

Figure 14-13. HDI Stack-up with Staggered Micro Vias

Advantages and Disadvantages of BGA Packaging

As pin counts increase and board space becomes more valuable, it is important to place as many circuits per square inch as possible. BGA offer the best I/O density for a given PCB area. Lattice offers a range of packages from a 4x4 mm 64-ball csBGA to a 33x33 mm 1704-ball fcBGA.

One of the greatest advantages of BGA packaging is that it can be supported with existing placement and assem-bly equipment. BG As also offer significantly more misalignment tolerance and less susceptibility to co-planarity issues. Even if the solder paste is misaligned or the device is slightly offset, the BGA will self-center during the

reflow process. This is due to the surface tension of the solder and flux in its molten state pulling each ball into the center of the pad.

Figure 14-14. Misalignment of BGA Balls vs. QPF Leads

Controlling the oven re-flow profile is one of the most important assembly parameters for consistent and reliable BGA placement. Profiles are typically tested on a pre-run. One or two panels are run to dial in the process, then visual and X-ray inspection equipment are used for verification.

BGA packages present numerous benefits previously unobtainable in surface mount packaging technology. BGAs provide higher pin counts in a much smaller area than was previous possible. No longer is the package design lim-ited to connections along the periphery on the outside quadrants of the package edge like a PQFP or TQFP out-line. Fully populated ball grid arrays with pitches as small as 0.4 mm are available.

Some BGA devices are arranged with de-populated interconnect near or around the center. These are dependent on the die size and number of pins. The area void of interconnect in the middle of the array has some advantages, it can be used for escape routing vias or tying directly to the ground or power planes.

Although the packages can be quite complex and densely populated, all of these packages receive strict quality and reliability testing and are widely accepted today by designers and PCB fabrication/assembly houses. All of this is due to advances in equipment and technology that have allowed a smooth transition into the assembly flow. BGA Package Test and Assembly

How can a pad/ball/pin be tested that can’t be seen? All connections are hidden under the substrate at the ball interconnect, making it impossible to directly probe or test. To address this limitation, Lattice programmable devices provide JTAG, BSCAN, and boundary scan cells that allow electronic test and continuity of each pin with a bound-ary scan tester. This can be embedded into the system itself or driven externally from a high-speed test head. The boundary scan can test the pins or board for simple continuity tests or full functional test by shifting in test patterns through the JTAG port.

For debug or prototype boards it may be necessary to place test points, open vias, or pads to have access to a given set of pins in order to drive, over-drive or observe a given set of signals. These can be very small, as many

pogo pin type probes are extremely small and can handle GHz range DC frequency. Zero ohm resistors are also commonly used in first-run boards as a way to gain access to a pad or pin.

After assembly, BGA solder point quality and integrity is visually inspected with X-ray technology as part of the fab-rication process. A special X-ray machine can look through the plastic package, substrate and silicon to directly view the BGA solder balls, vias, traces and pads.

Figure 14-15. Example of How Defects May Appear in an X-Ray Image

The X-ray image in Figure 14-16 shows proper alignment; no voids or defects are noted. Balls, vias and traces are visible.

Figure 14-16. X-Ray Inspection Plot of ispMACH 4000ZE 144-ball csBGA

(Photo Courtesy of CEM, Ltd., https://www.360docs.net/doc/db11169796.html,)

PCB cross-sectioning is another method used to verify BGA and PCB quality and reliability. After a new process has been developed or changed or when qualifying a new vendor, it is a good practice to get physical information from the vendor on their BGA reflow. When trace/space and drill or laser tolerances are nearing their limits, board yield can be as be as low as 50% for the bare board fab. Cross-sections give you a good idea if the process is cor-rect but do not guarantee each batch or each board design will behave the same way due to layout dimensions, thermal issues, flux/paste and alignment, etc.

Figure 14-17 shows a BGA cross-section that uses a non-soldermask over bare copper-defined pad. (NSMD) pad. Figure 14-17. BGA Cross-Section

Figure 14-18 shows “offset” micro via stack routing between layers.

Figure 14-18. Cross-Section of Micro Vias

High-resolution video cameras are used for edge inspection to verify ball seating, distortion, solder wetting, flow, contaminates, etc. Figure 14-19 is a video view of a side/edge shot looking at BGA balls soldered down to the isp-MACH 4000ZE Pico Evaluation Board (https://www.360docs.net/doc/db11169796.html,/4000ze-pico-kit), an FR4 4-layer PCB.

Figure 14-19. Edge View Camera Inspection

In the photos samples above, trained technicians and computer camera recognition equipment are used for inspec-tion of the X-ray results, looking for voids, shorts, missing connections, contaminants, alignment or other gross fail-ure mechanisms. For example, in Figure 14-19, the BGA ball connections appear to be squashed downward, with mild distortion, insuring that proper oven profile temperatures were achieved.

These technologies help in the successful placement and long term use of BGAs in the industry’s latest products. Further advancements have been made in material content to conform to environmental issues, toxic materials and recycling. Another issue that relates to board design is the physical silkscreen logos and information related to recycling, lead content and other hazardous waste components, strict adherence must be paid to these require-ments. Although a documentation and silkscreen issue, it can become a challenge to fit this information on the board in some cases due to component population and must be accounted for in overall board real estate.

PCB Design Support

Lattice provides a collection of PCB design resources at https://www.360docs.net/doc/db11169796.html,/support/pcbdesignsupport.cfm including schematic libraries, PCB CAM viewers, technical notes, and BGA breakout and routing examples. Technical Support Assistance

Hotline:1-800-LATTICE (North America)

+1-503-268-8001 (Outside North America)

e-mail:techsupport@https://www.360docs.net/doc/db11169796.html,

Internet:https://www.360docs.net/doc/db11169796.html,

Revision History

Date Version Change Summary

January 200501.0Initial release.

November 200501.1Figures updated.

June 200601.2Removed NSMD content.

September 200601.3Added note to BGA Board Layout Recommendations table.

Reformatted BGA Package T ypes section in tabular format.

March 200801.4Revised recommended Solder Mask Defined and Non Solder Mask

Defined PCB solder pad dimensions to match industry standards.

May 200901.5Updated BGA Board Layout Recommendations table and BGA Pack-

age T ypes table for 0.4 mm pitch ucBGA package.

February 201001.6Edits to most sections and additional links and graphics added for each

example.

March 201001.7Replaced Lattice BGA Naming Conventions table with Lattice Semicon-

ductor BGA Package T ypes table and SMD/NSMD Pad Recommenda-

tions table.

August 201001.8Lattice Semiconductor SMD/NSMD Pad Recommendations table:

Specified nominal Solder Mask Opening for each Lattice BGA package,

clarified recommended Solder Mask Opening and Solder Pad Diame-

ters and added cautionary note.

September 201001.9Lattice Semiconductor SMD/NSMD Pad Recommendations table -

Added 64 csBGA to 0.5mm pitch column.

February 201102.0Updated BGA Board Layout Recommendations text section.

Updated Lattice SMD/NSMD Pad Recommendations table.

Added WLCSP to Lattice SMD/NSMD Pad Recommendations table.

相关开关电源原理及电路图

相关开关电源原理及电路图 2012-06-03 17:39:37 来源:21IC 关键字:开关电源电路图 什么是开关电源?所谓开关电源,故名思议,就是这里有一扇门,一开门电源就通过,一关门电源就停止通过,那么什么是门呢,开关电源里有的采用可控硅,有的采用开关管,这两个元器件性能差不多,都是靠基极、(开关管)控制极(可控硅)上加上脉冲信号来完成导通和截止的,脉冲信号正半周到来,控制极上电压升高,开关管或可控硅就导通,由220V整流、滤波后输出的300V电压就导通,通过开关变压器传到次级,再通过变压比将电压升高或降低,供各个电路工作。振荡脉冲负半周到来,电源调整管的基极、或可控硅的控制极电压低于原来的设置电压,电源调整管截止,300V电源被关断,开关变压器次级没电压,这时各电路所需的工作电压,就靠次级本路整流后的滤波电容放电来维持。待到下一个脉冲的周期正半周信号到来时,重复上一个过程。这个开关变压器就叫高频变压器,因为他的工作频率高于50HZ低频。那么推动开关管或可控硅的脉冲如何获得呢,这就需要有个振荡电路产生,我们知道,晶体三极管有个特性,就是基极对发射极电压是0.65-0.7V是放大状态,0.7V以上就是饱和导通状态,-0.1V- -0.3V就工作在振荡状态,那么其工作点调好后,就靠较深的负反馈来产生负压,使振荡管起振,振荡管的频率由基极上的电容充放电的时间长短来决定,振荡频率高输出脉冲幅度就大,反之就小,这就决定了电源调整管的输出电压的大小。那么变压器次级输出的工作电压如何稳压呢,一般是在开关变压器上,单绕一组线圈,在其上端获得的电压经过整流滤波后,作为基准电压,然后通过光电耦合器,将这个基准电压返回振荡管的基极,来调整震荡频率的高低,如果变压器次级电压升高,本取样线圈输出的电压也升高,通过光电耦合器获得的正反馈电压也升高,这个电压加到振荡管基极上,就使振荡频率降低,起到了稳定次级输出电压的稳定,太细的工作情况就不必细讲了,也没必要了解的那么细的,这样大功率的电压由开关变压器传递,并与后级隔开,返回的取样电压由光耦传递也与后级隔开,所以前级的市电电压,是与后级分离的,这就叫冷板,是安全的,变压器前的电源是独立的,这就叫开关电源。 图开关电源原理图1

开关电源电路详解图

开关电源电路详解图 一、开关电源的电路组成 开关电源的主要电路是由输入电磁干扰滤波器(EMI)、整流滤波电路、功率变换电路、PWM控制器电路、输出整流滤波电路组成。辅助电路有输入过欠压保护电路、输出过欠压保护电路、输出过流保护电路、输出短路保护电路等。 开关电源的电路组成方框图如下: 二、输入电路的原理及常见电路 1、AC 输入整流滤波电路原理: ①防雷电路:当有雷击,产生高压经电网导入电源时,由MOV1、MOV2、MOV3:F1、F2、F3、FDG1 组成的电路进行保护。当加在压敏电阻两端的电压超过其工作电压时,其阻值降低,使高压能量消耗在压敏电阻上,若电流过大,F1、F2、F3 会烧毁保护后级电路。 ②输入滤波电路:C1、L1、C2、C3组成的双π型滤波网络主要是对输入电源的电磁噪声及杂波信号进行抑制,防止对电源干扰,同时也防止电源本身产生的高频杂波对电网干扰。当电源开启瞬间,要对C5充电,由于瞬间电流大,加RT1(热敏电阻)就能有效的防止浪涌电流。因瞬时能量全消耗在RT1电阻上,一定时间后温度升高后RT1阻值减小(RT1是负温系数元件),这时它消耗的能量非常小,后级电路可正常工作。 ③整流滤波电路:交流电压经BRG1整流后,经C5滤波后得到较为纯净的直流电压。若C5容量变小,输出的交流纹波将增大。

2、DC 输入滤波电路原理: ①输入滤波电路:C1、L1、C2组成的双π型滤波网络主要是对输入电源的电磁噪声及杂波信号进行抑制,防止对电源干扰,同时也防止电源本身产生的高频杂波对电网干扰。C3、C4 为安规电容,L2、L3为差模电感。 ② R1、R2、R3、Z1、C6、Q1、Z2、R4、R5、Q2、RT1、C7组成抗浪涌电路。在起机的瞬间,由于C6的存在Q2不导通,电流经RT1构成回路。当C6上的电压充至Z1的稳压值时Q2导通。如果C8漏电或后级电路短路现象,在起机的瞬间电流在RT1上产生的压降增大,Q1导通使Q2没有栅极电压不导通,RT1将会在很短的时间烧毁,以保护后级电路。 三、功率变换电路 1、MOS管的工作原理:目前应用最广泛的绝缘栅场效应管是MOSFET(MOS管),是利用半导体表面的电声效应进行工作的。也称为表面场效应器件。由于它的栅极处于不导电状态,所以输入电阻可以大大提高,最高可达105欧姆,MOS管是利用栅源电压的大小,来改变半导体表面感生电荷的多少,从而控制漏极电流的大小。 2、常见的原理图: 3、工作原理: R4、C3、R5、R6、C4、D1、D2组成缓冲器,和开关MOS管并接,使开关管电压应力减少,EMI减少,不发生二次击穿。在开关管Q1关断时,变压器的原边线圈易产生尖

元件库和封装库的制作原则doc.

PCB元件库和封装库的制作 Protel99se建库规则 1 、框架结构:分为原理图元件库和PCB元件库两个库,每个库做为一个单独的设计项目 1.1 依据元器件种类,原理图元件库包括以下16个库: 1.1.1 单片机 1.1.2 集成电路 1.1.3 TTL74系列 1.1.4 COMS系列 1.1.5 二极管、整流器件 1.1.6 晶体管:包括三极管、场效应管等 1.1.7 晶振 1.1.8 电感、变压器件 1.1.9 光电器件:包括发光二极管、数码管等 1.1.10 接插件:包括排针、条型连接器、防水插头插座等 1.1.11 电解电容 1.1.12 钽电容 1.1.13 无极性电容 1.1.14 SMD电阻 1.1.15 其他电阻:包括碳膜电阻、水泥电阻、光敏电阻、压敏电阻等 1.1.16 其他元器件:包括蜂鸣器、电源模块、继电器、电池等 1.2 依据元器件种类及封装,PCB元件封装库包括以下11个库: 1.2.1 集成电路(直插) 1.2.2 集成电路(贴片) 1.2.3 电感 1.2.4 电容 1.2.5 电阻 1.2.6 二极管整流器件 1.2.7 光电器件 1.2.8 接插件 1.2.9 晶体管 1.2.10 晶振 1.2.11 其他元器件 2 PCB元件库命名规则 2.1 集成电路(直插) 用DIP-引脚数量+尾缀来表示双列直插封装 尾缀有N和W两种,用来表示器件的体宽 N为体窄的封装,体宽300mil,引脚间距2.54mm

W为体宽的封装, 体宽600mil,引脚间距2.54mm 如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装 2.2 集成电路(贴片) 用SO-引脚数量+尾缀表示小外形贴片封装 尾缀有N、M和W三种,用来表示器件的体宽 N为体窄的封装,体宽150mil,引脚间距1.27mm M为介于N和W之间的封装,体宽208mil,引脚间距1.27mm W为体宽的封装, 体宽300mil,引脚间距1.27mm 如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装 若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm 2.3 电阻 2.3.1 SMD贴片电阻命名方法为:封装+R 如:1812R表示封装大小为1812的电阻封装 2.3.2 碳膜电阻命名方法为:R-封装 如:R-AXIAL0.6表示焊盘间距为0.6英寸的电阻封装 2.3.3 水泥电阻命名方法为:R-型号 如:R-SQP5W表示功率为5W的水泥电阻封装 2.4 电容 2.4.1 无极性电容和钽电容命名方法为:封装+C 如:6032C表示封装为6032的电容封装 2.4.2 SMT独石电容命名方法为:RAD+引脚间距 如:RAD0.2表示的是引脚间距为200mil的SMT独石电容封装 2.4.3 电解电容命名方法为:RB+引脚间距/外径 如:RB.2/.4表示引脚间距为200mil, 外径为400mil的电解电容封装 2.5 二极管整流器件 命名方法按照元件实际封装,其中BAT54和1N4148封装为1N4148 2.6 晶体管 命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名 2.7 晶振 HC-49S,HC-49U为表贴封装,A T26,A T38为圆柱封装,数字表规格尺寸 如:A T26表示外径为2mm,长度为8mm的圆柱封装 2.8 电感、变压器件 电感封封装采用TDK公司封装 2.9 光电器件 2.9.1 贴片发光二极管命名方法为封装+D来表示 如:0805D表示封装为0805的发光二极管 2.9.2 直插发光二极管表示为LED-外径 如LED-5表示外径为5mm的直插发光二极管 2.9.3 数码管使用器件自有名称命名 2.10 接插件 2.10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm 如:SIP7-2.54表示针脚间距为2.54mm的7针脚单排插针 2.10.2 DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm

开关电源各模块原理实图讲解

开关电源原理 一、开关电源的电路组成: 开关电源的主要电路是由输入电磁干扰滤波器(EMI)、整流滤波电路、功率变换电路、PWM F3、FDG1组成的电路进行保护。当加在压敏电阻两端的电压超过其工作电压时,其阻值 降低,使高压能量消耗在压敏电阻上,若电流过大,F1、F2、F3会烧毁保护后级电路。 ②输入滤波电路:C1、L1、C2、C3组成的双π型滤波网络主要是对输入电源的电磁噪声及 杂波信号进行抑制,防止对电源干扰,同时也防止电源本身产生的高频杂波对电网干扰。 当电源开启瞬间,要对C5充电,由于瞬间电流大,加RT1(热敏电阻)就能有效的防止浪 涌电流。因瞬时能量全消耗在RT1电阻上,一定时间后温度升高后RT1阻值减小(RT1是 负温系数元件),这时它消耗的能量非常小,后级电路可正常工作。 ③整流滤波电路:交流电压经BRG1整流后,经C5滤波后得到较为纯净的直流电压。若C5 容量变小,输出的交流纹波将增大。

时Q2导通。如果C8漏电或后级电路短路现象,在起机的瞬间电流在RT1上产生的压降增 大,Q1导通使Q2没有栅极电压不导通,RT1将会在很短的时间烧毁,以保护后级电路。 三、功率变换电路: 1、MOS管的工作原理:目前应用最广泛的绝缘栅场效应管是MOSFET(MOS管),是利用半导 体表面的电声效应进行工作的。也称为表面场效应器件。由于它的栅极处于不导电状态,所以输入电阻可以大大提高,最高可达105欧姆,MOS管是利用栅源电压的大小,来改变半导体表面感生电荷的多少,从而控制漏极电流的大小。 2、常见的原理图: 3、工作原理: R4、C3、R5、R6、C4、D1、D2组成缓冲器,和开关MOS管并接,使开关管电压应力减少,EMI减少,不发生二次击穿。在开关管Q1关断时,变压器的原边线圈易产生尖峰电压和尖峰电流,这些元件组合一起,能很好地吸收尖峰电压和电流。从R3测得的电流峰值信号参与当前工作周波的占空比控制,因此是当前工作周波的电流限制。当R5上的电压达到1V时,UC3842停止工作,开关管Q1立即关断。 R1和Q1中的结电容C GS、C GD一起组成RC网络,电容的充放电直接影响着开关管的开关速度。R1过小,易引起振荡,电磁干扰也会很大;R1过大,会降低开关管的开关速度。Z1通常将MOS管的GS电压限制在18V以下,从而保护了MOS管。 Q1的栅极受控电压为锯形波,当其占空比越大时,Q1导通时间越长,变压器所储存的能量

发动机总体构造认识

发动机总体构造认识 一、桑塔纳2000AJR发动机在整车中的位置 汽车发动机是汽车的动力源泉,为整个汽车提供动力。一般轿车来说,除个别型号的汽车外,发动机通常安装在车头箱中。 1—AJR发动机 2—离合器 3—变速器 4—真空助力器 5—防抱死制动系统(ABS) 6—动力转向器 7—传动轴 8—盘式制动器(前轮) 9—前悬架 10—排气系统 11—燃油箱 12—后悬架 13—鼓式制动器(后轮) 14—车身 二、AJR 发动机技术参数 1.发动机代码 AJR 2.排量 1.781L 3.缸径 81mm 4.冲程 86.4mm 5.压缩比 9.5 6.功率 74kW 7.额定功率时转速 5200 r/min 8.最大扭矩 155Nm 9.最大扭矩是转速 3800 r/min 10.使用汽油标号(研究法辛烷值) 90 RON 11.喷射控制系统 M.3.8.2 12.点火系统 M.3.8.2. 13.爆震控制有 14.自诊断有 15.λ控制有 三、AJR发动机总体结构 1.作用发动机的作用主要是将燃料燃烧的热能转化成机械能,并对外输出。

2.组成汽油发动机基本上都是由2大机构和5大系统组成:曲柄连杆机构、配气机构、燃料供给系、润滑系、冷却系、点火系和起动系。 1—正时齿形带护罩 2—空调压缩机A/C 3—空调压缩机带轮 4—多楔带 5—曲轴带轮 6—张紧轮 7—发电机带轮 8—导向轮 9—动力转向泵带轮10—动力转向油泵 11—发电机 12—进气歧管 13—燃油分配管 14—油尺 15—气缸盖罩 四、电控系统结构 1.作用电控系统的作用主要是保证发动机在不同工况下,实现最佳的燃油喷射和点火时机,从而达到最佳的经济性、动力性和排放。 2.组成电控系统一般由三部分组成:电控单元(ECU)、传感器和执行器。 1)电控单元桑塔纳2000发动机的电控单元(ECU)采用的是博世M3.8.2系统。其作用是根据各种传感器输入的信号及内存信息,进行判断、运算、处理后,确定最佳的喷油和点火控制等信号,并将其输送给喷油器、点火器等执行器。 2)传感器作用是检测发动机运行中有关的各种信息(水温、转速等),并将检测结果转变为电信号输入电控单元。桑塔纳2000发动机传感器主要有:空气质量计、爆震传感器、凸轮轴位置传感器、发动机转速传感器、进气温度传感器、节气门位置传感器、冷却液温度传感器、氧传感器。 3)执行器接受电控单元(ECU)输出的控制信号,进行相应的动作。桑塔纳2000发动机执行器主要有:活性炭罐电磁阀、喷油器、点火控制组件、节气门控制部件(怠速)。

Allegro元件封装(焊盘)制作方法总结

Allegro元件封装(焊盘)制作方法总结 ARM+Linux底层驱动 2009-02-27 21:00 阅读77 评论0 字号:大中小 https://www.360docs.net/doc/db11169796.html,/html/PCBjishu/2008/0805/3289.html 在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。元件封装大体上分两种,表贴和直插。针对不同的封装,需要制 作不同的Padstack。 Allegro中Padstack主要包括以下部分。 1、PAD即元件的物理焊盘 pad有三种: 1. Regular Pad,规则焊盘(正片中)。可以是:Circle 圆型、S quare 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八 边型、Shape形状(可以是任意形状)。 2. Thermal relief 热风焊盘(正负片中都可能存在)。可以是: Null(没有)、Circle 圆型、Square 方型、Oblong 拉长圆型、 Rectangle 矩型、Octagon 八边型、flash形状(可以是任意形 状)。 3. Anti pad 抗电边距(负片中使用),用于防止管脚与其他的网 络相连。可以是:Null(没有)、Circle 圆型、Square 方型、 Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形 状(可以是任意形状)。 2、SOLDERMASK:阻焊层,使铜箔裸露而可以镀涂。 3、PASTEMASK:胶贴或钢网。 4、FILMMASK:预留层,用于添加用户需要添加的相应信息,根据需要使用。 表贴元件的封装焊盘,需要设置的层面及尺寸: Regular Pad: 具体尺寸根据实际封装的大小进行相应调整后得到。推荐使用《IPC-SM-78 2A Surface Mount Design and Land Pattern Standard》中推荐的尺寸进行尺寸设计。同时推荐使用IPC-7351A LP Viewer。该软件包括目前常用的大多数S

开关电源入门必读:开关电源工作原理超详细解析

开关电源入门必读:开关电源工作原理超详细解析 第1页:前言:PC电源知多少 个人PC所采用的电源都是基于一种名为“开关模式”的技术,所以我们经常会将个人PC电源称之为——开关电源(Sw itching Mode P ow er Supplies,简称SMPS),它还有一个绰号——DC-DC转化器。本次文章我们将会为您解读开关电源的工作模式和原理、开关电源内部的元器件的介绍以及这些元器件的功能。 ●线性电源知多少 目前主要包括两种电源类型:线性电源(linear)和开关电源(sw itching)。线性电源的工作原理是首先将127 V或者220V市电通过变压器转为低压电,比如说12V,而且经过转换后的低压依然是AC交流电;然后再通过一系列的二极管进行矫正和整流,并将低压AC交流电转化为脉动电压(配图1和2中的“3”);下一步需要对脉动电压进行滤波,通过电容完成,然后将经过滤波后的低压交流电转换成DC直流电(配图1和2中的“4”);此时得到的低压直流电依然不够纯净,会有一定的波动(这种电压波动就是我们常说的纹波),所以还需要稳压二极管或者电压整流电路进行矫正。最后,我们就可以得到纯净的低压DC直流电输出了(配图1和2中的“5”) 配图1:标准的线性电源设计图

配图2:线性电源的波形 尽管说线性电源非常适合为低功耗设备供电,比如说无绳电话、PlayStation/W ii/Xbox等游戏主机等等,但是对于高功耗设备而言,线性电源将会力不从心。 对于线性电源而言,其内部电容以及变压器的大小和AC市电的频率成反比:也即说如果输入市电的频率越低时,线性电源就需要越大的电容和变压器,反之亦然。由于当前一直采用的是60Hz(有些国家是50Hz)频率的AC市电,这是一个相对较低的频率,所以其变压器以及电容的个头往往都相对比较大。此外,AC市电的浪涌越大,线性电源的变压器的个头就越大。 由此可见,对于个人PC领域而言,制造一台线性电源将会是一件疯狂的举动,因为它的体积将会非常大、重量也会非常的重。所以说个人PC用户并不适合用线性电源。 ●开关电源知多少 开关电源可以通过高频开关模式很好的解决这一问题。对于高频开关电源而言,AC输入电压可以在进入变压器之前升压(升压前一般是50-60KHz)。随着输入电压的升高,变压器以及电容等元器件的个头就不用像线性电源那么的大。这种高频开关电源正是我们的个人PC以及像VCR录像机这样的设备所需要的。需要说明的是,我们经常所说的“开关电源”其实是“高频开关电源”的缩写形式,和电源本身的关闭和开启式没有任何关系的。 事实上,终端用户的PC的电源采用的是一种更为优化的方案:闭回路系统(closed loop system)——负责控制开关管的电路,从电源的输出获得反馈信号,然后根据PC的功耗来增加或者降低某一周期内的电压的频率以便能够适应电源的变压器(这个方法称作PW M,Pulse W idth Modulation,脉冲宽度调制)。所以说,开关电源可以根据与之相连的耗电设备的功耗的大小来自我调整,从而可以让变压器以及其他的元器件带走更少量的能量,而且降低发热量。 反观线性电源,它的设计理念就是功率至上,即便负载电路并不需要很大电流。这样做的后果就是所有元件即便非必要的时候也工作在满负荷下,结果产生高很多的热量。 第2页:看图说话:图解开关电源 下图3和4描述的是开关电源的PW M反馈机制。图3描述的是没有PFC(P ow er Factor Correction,功率因素校正)电路的廉价电源,图4描述的是采用主动式PFC设计的中高端电源。 图3:没有PFC电路的电源 图4:有PFC电路的电源 通过图3和图4的对比我们可以看出两者的不同之处:一个具备主动式PFC电路而另一个不具备,前者没有110/220V转换器,而且也没有电压倍压电路。下文我们的重点将会是主动式PFC电源的讲解。

制作焊盘(元件封装)步骤

制作焊盘(元件封装)步骤 先制作引脚焊盘,再制作元件封装。 焊接通孔-焊盘制作 1.查元件/接插件数据手册(Datasheet),找到“Layout Recommendation”或“Mounting Pattern”页。 2.找到通孔推荐钻孔尺寸,比如: 如图Ф0.89x10 其中0.89即为推荐钻孔直径,x10 表示同样的孔有10个。 3. (一般取0.3mm足够焊接操作) 比如: 钻孔直径为Ф0.89,则焊盘外径可取Ф1.19mm或Ф1.2mm。 4. 足够。 比如:钻孔直径为Ф0.89,焊盘外径取Ф1.2mm,则Soldermask直径可取Ф1.3mm。5.确定热风焊盘(Flash Symbol)(两种): 方热风焊盘(PIN1)命名: str A x A o B x B (命名规则) 解释: str: Square Thermal Relief;方形散热槽 A x A: 确定阻焊盘Anti pad 边长= A; B x B: 内边长;

圆热风焊盘命名: tr ID x OD x SW – SA (命名规则) 解释: tr: Thermal Relief;散热槽 内径; 一般取焊盘外径即可。 OD: Out Diameter 外径; ) 一般加0.1mm足够。 保留整数位,一般取0.5mm。 SA:Spoke Angle 开口角度。 SA = 45度。 6.给通过孔焊盘命名(两种): 方焊盘(PIN1)命名: A Sq B d A: 正方形焊盘边长;B:钻孔直径;Sq: Square; d: 钻孔的孔壁必须上锡 比如:2Sq1p7d 方焊盘,正方形焊盘边长2mm,钻孔直径1.7mm。 圆焊盘命名: A Cir B d A: 焊盘外径B:钻孔直径;Cir:Circle;d: 钻孔的孔壁必须上锡 比如:2Sq1p7d 圆焊盘,焊盘外径2mm,钻孔直径1.7mm。 7.启动软件“Allegro PCB Design GXL”制作热风焊盘。 File→New, Drawing Type选择:Flash Symbol。。。。。 设置Setup→ Design Parameters→ Design, 单位选Millimeter; Accuracy: 4 修改Extents区域。 设置Setup→ Grid, 设置格点参数。 A:制作方热风焊盘: Shape→ Filled shape 或者Polygon,然后画出图形。 B:制作圆热风焊盘: Add→ Flash, 然后输入参数,确定即可。 8.启动软件“Pad Designer(Pad Editor)”制作通过孔焊盘(PIN1方焊盘)。 File→New, Padstack Type 选择:Thru Pin; Padstack name 选择要保存的目录,再输入孔名,比如:Pad1p2Sq0p89d (方焊盘)。 窗口下边栏修改单位Units:Millimeter; 精度(小数点位数)Decimal places: 4; Start页:Select Padstack usage:Thru Pin; Select the default pad geometry: Square;(方焊盘) Drill 页:Hole type:Circle;(钻孔形状:圆孔)

开关电源原理图精讲.pdf

开关电源原理(希望能帮到同行的你更加深入的了解开关电源,温故而知新吗!!) 一、开关电源的电路组成[/b]:: 开关电源的主要电路是由输入电磁干扰滤波器(EMI)、整流滤波电路、功率变换电路、PWM控制器电路、输出整流滤波电路组成。辅助电路有输入过欠压保护电路、输出过欠压保护电路、输出过流保护电路、输出短路保护电路等。 开关电源的电路组成方框图如下: 二、输入电路的原理及常见电路[/b]:: 1、AC输入整流滤波电路原理: ①防雷电路:当有雷击,产生高压经电网导入电源时,由MOV1、MOV2、MOV3:F1、F2、F3、FDG1组成的电路进行保护。当加在压敏电阻两端的电压超过其工作电压时,其阻值降低,使高压能量消耗在压敏电阻上,若电流过大,F1、F2、F3会烧毁保护后级电路。 ②输入滤波电路:C1、L1、C2、C3组成的双π型滤波网络主要是对输入电源的电磁噪声及杂波信号进行抑制,防止对电源干扰,同时也防止电源本身产生的高频杂波对电网干扰。当电源开启瞬间,要对C5充电,由于瞬间电流大,加RT1(热敏电阻)就能有效的防

止浪涌电流。因瞬时能量全消耗在RT1电阻上,一定时间后温度升高后RT1阻值减小(RT1是负温系数元件),这时它消耗的能量非常小,后级电路可正常工作。 ③整流滤波电路:交流电压经BRG1整流后,经C5滤波后得到较为纯净的直流电压。若C5容量变小,输出的交流纹波将增大。 2、 DC输入滤波电路原理: ①输入滤波电路:C1、L1、C2组成的双π型滤波网络主要是对输入电源的电磁噪声及杂波信号进行抑制,防止对电源干扰,同时也防止电源本身产生的高频杂波对电网干扰。C3、C4为安规电容,L2、L3为差模电感。 ② R1、R2、R3、Z1、C6、Q1、Z2、R4、R5、Q2、RT1、C7组成抗浪涌电路。在起机的瞬间,由于C6的存在Q2不导通,电流经RT1构成回路。当C6上的电压充至Z1的稳压值时Q2导通。如果C8漏电或后级电路短路现象,在起机的瞬间电流在RT1上产生的压降增大,Q1导通使Q2没有栅极电压不导通,RT1将会在很短的时间烧毁,以保护后级电路。 三、功率变换电路[/b]:: 1、 MOS管的工作原理:目前应用最广泛的绝缘栅场效应管是MOSFET(MOS管),是利用半导体表面的电声效应进行工作的。也称为表面场效应器件。由于它的栅极处于不导电状态,所以输入电阻可以大大提高,最高可达105欧姆,MOS管是利用栅源电压的大小,来改变半导体表面感生电荷的多少,从而控制漏极电流的大小。 2、常见的原理图:

(完整版)元器件封装大全

元器件封装大全 A. 名称Axial 描述轴状的封装 名称 AGP (Accelerate Graphical Port) 描述加速图形接口 名称 AMR (Audio/MODEM Riser) 描述声音/调制解调器插卡 B. 名称 BGA (Ball Grid Array) 描述 球形触点阵列,表面贴 装型封装之一。在印刷基板 的背面按阵列方式制作出 球形凸点用以代替引脚,在 印刷基板的正面装配LSI 芯片,然后用模压树脂或灌 封方法进行密封。也称为凸 点阵列载体(PAC) 名称 BQFP (quad flat package with bumper) 描述 带缓冲垫的四侧引脚扁 平封装。QFP封装之一,在 封装本体的四个角设置突 (缓冲垫)以防止在运送过 程中引脚发生弯曲变形。 C.陶瓷片式载体封装 名称 C- (ceramic) 描述 表示陶瓷封装的记号。 例如,CDIP 表示的是陶瓷 DIP。 名称C-BEND LEAD 描述名称CDFP 描述

名称Cerdip 描述 用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。带有玻璃窗口的Cerdip 用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。 名称CERAMIC CASE 描述 名称 CERQUAD (Ceramic Quad Flat Pack) 描述 表面贴装型封装之一, 即用下密封的陶瓷QFP,用 于封装DSP 等的逻辑LSI 电路。带有窗口的Cerquad 用于封装EPROM 电路。散热 性比塑料QFP 好,在自然空 冷条件下可容许 1.5~2W 的功率 名称CFP127 描述 名称 CGA (Column Grid Array)描述 圆柱栅格阵列,又称柱栅阵列封装 名称 CCGA (Ceramic Column Grid Array) 描述陶瓷圆柱栅格阵列 名称CNR 描述CNR是继AMR之后作为INTEL的标准扩展接口 名称CLCC 描述 带引脚的陶瓷芯片载体,引脚从封装的四个侧面引出,呈丁字形。带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。此封装也称为QFJ、QFJ-G.

电脑开关电源原理及电路图

2.1、输入整流滤波电路 只要有交流电AC220V输入,ATX开关电源,无论是否开启,其辅助电源就一直在工作,直接为开关电源控制电路提供工作电压。图1中,交流电AC220V经过保险管FUSE、电源互感滤波器L0,经BD1—BD4整流、C5和C6滤波,输出300V左右直流脉动电压。C1为尖峰吸收电容,防止交流电突变瞬间对电路造成不良影响。TH1为负温度系数热敏电阻,起过流保护和防雷击的作用。L0、R1和C2组成Π型滤波器,滤除市电电网中的高频干扰。C3和C4为高频辐射吸收电容,防止交流电窜入后级直流电路造成高频辐射干扰。 2.2、高压尖峰吸收电路 D18、R004和C01组成高压尖峰吸收电路。当开关管Q03截止后,T3将产生一个很大的反极性尖峰电压,其峰值幅度超过Q03的C极电压很多倍,此尖峰电压的功率经D18储存于C01中,然后在电阻R004上消耗掉,从而降低了Q03的C极尖峰电压,使Q03免遭损坏。 2.3、辅助电源电路 整流器输出的300V左右直流脉动电压,一路经T3开关变压器的初级①~②绕组送往辅助电源开关管Q03的c极,另一路经启动电阻R002给Q03的b极提供正向偏置电压和启动电流,使Q03开始导通。Ic流经T3初级①~②绕组,使T3③~④反馈绕组产生感应电动势(上正下负),通过正反馈支路C02、D8、R06送往Q03的b极,使Q03迅速饱和导通,Q03上的Ic电流增至最大,即电流变化率为零,此时D7导通,通过电阻R05送出一个比较电压至IC3(光电耦合器Q817)的③脚,同时T3次级绕组产生的感应电动势经D50整流滤波后一路经R01限流后送至IC3的①脚,另一路经R02送至IC4(精密稳压电路TL431),由于Q03饱和导通时次级绕组产生的感应电动势比较平滑、稳定,经IC4的K端输出至IC3的②脚电压变化率几乎为零,使IC3发光二极管流过的电流几乎为零,此时光敏三极管截止,从而导致Q1截止。反馈电流通过R06、R003、Q03的b、e极等效电阻对电容C02充电,随着C02充电电压增加,流经Q03的b极电流逐渐减小,使③~④反馈绕组上的感应电动势

发动机整体认识

一、单选题(每题2分,共40分) 1、汽车发动机的功用是(B)。 A、将热能转化成机械能 B、将化学能转化成机械能 C、将机械能转化成热能 D、将化学能转化成热能 2、内燃机有自然吸气(非增压)式发动机和强制进气(增压式)发动机。这是按什么方式进行分类的(A)。 A、按照进气系统分类 B、按照气缸排列方式分类 C、按照冷却方式分类 D、按照燃料分类 3、内燃机可分为水冷发动机和风冷发动机。这是按什么方式进行分类的(C)。 A、按照进气系统分类 B、按照气缸排列方式分类 C、按照冷却方式分类 D、按照气缸数目分类 4、内燃机有汽油机、柴油机、天然气发动机。这是按什么方式进行分类的(D)。 A、按照进气系统分类 B、按照气缸数目分类 C、按照冷却方式分类 D、按照燃料分类 5、上止点是指活塞离曲轴回转中心(C)位置。 A、最远 B、最近 C、最高 D、最低 6、下止点是指活塞离曲轴回转中心(D)位置。 A、最远 B、最近 C、最高 D、最低 7、压缩比是指气缸(B)容积与()容积之比。 A、工作…燃烧室 B、总…燃烧室 C、总…工作 D、燃烧室…工作 8、下面发动机零件属于曲柄连杆机构的是(A)。 A、气缸体 B、进气门 C、水泵 D、散热器 9、能够保证发动机在合适的工作温度下工作的系统是(D)。 A、润滑系 B、点火系 C、起动系 D、冷却系 10、下面发动机零件属于配气机构的是(A)。 A、凸轮轴 B、活塞 C、曲轴箱 D、水泵 11、能够提供发动机从静止状态达到混合气燃烧作功所需要转速的系统是(C)。 A、进气系统 B、润滑系统 C、起动系统 D、点火系统 12、发动机排量是指发动机各缸(C)之和。 A、总容积 B、燃烧室容积 C、工作容积 D、压缩比 13、四冲程发动机在进行压缩冲程时( D )。 A、进气门开启,排气门关闭 B、进气门开启,排气门开启 C、进气门关闭,排气门开启 D、进气门关闭,排气门关闭 14、曲轴转两圈,活塞运动四个行程完成一个工作循环的发动机称为( D )冲程发动机。 A、一冲程 B、二冲程 C、三冲程 D、四冲程 15、汽油机最高燃烧温度(A)柴油机最高燃烧温度。 A、高于 B、低于 C、等于 D、低于或等于 16、四缸四冲程发动机作功间隔角为(A)曲轴转角。 A、180° B、120° C、360° D、720° 17、曲轴与凸轮轴的传动比为(B)。 A、1:02 B、2:1 C、4:1 D、1:01 18、柴油机在进气行程中进入气缸的是(C)。 A、柴油 B、柴油和空气的混合气 C、纯空气 D、氧气

常用元器件及元器件封装总结

常用元器件及元器件封装总结 一、元器件封装按照安装的方式不同可以分成两大类。(1) 直插式元器件封装直插式元器件封装的焊盘一般贯穿整个电路板,从顶层穿下,在底层进行元器件的引脚焊接,如图所示。 典型的直插式元器件及元器件封装如图所示。 (2)表贴式元器件封装。表贴式的元器件,指的是其焊盘只附着在电路板的顶层或底层,元器件的焊接是在装配元器件的工作层面上进行的,如图所示。

典型的表贴式元器件及元器件封装如图所示。在PCB元器件库中,表贴式的元器件封装的引脚一般为红色,表示处在电路板的顶层(TopLayer)。在PCB元器件库中,表贴式的元器件封装的引脚一般为红色,表示处在电路板的顶层(Top Layer)。 二、常用元器件的原理图符号和元器件封装 在设计PCB的过程中,有些元器件是设计者经常用到的,比如电阻、电容以及三端稳压源等。在Protel 99 SE中,同一种元器件虽然相同电气特性,但是由于应用的场合不同而导致元器件的封装存在一些差异。前面的章节中已经讲过,电阻由于其负载功率和运用场合不同而导致其元器件的封装也多种多样,这种情况对于电容来说也同样存在。因此,本节主要向读者介绍常用元器件的原理图符号和与之相对应的元器件封装,同时尽量给出一些元器件的实物图,使读者能够更快地了解并掌握这些常用元器件的原理图符号和元器件封装。(1)、电阻。电阻器通常简称为电阻,它是一种应用十分广泛的电子元器件,其英文名字为“Resistor”,缩写为“Res”。电阻的种类繁多,通常分为固定电阻、可变电阻和特种电阻3大类。固定电阻可按电阻的材料、结构形状及用途等进行多种分类。电阻的种类虽多,但常用的电阻类型主要为RT型碳膜电阻、RJ型金属膜电阻、RX型线绕电阻和片状电阻等。固定电阻的原理图符号的常用名称是“RES1”和“RES2”,如图F1-5(a)所示。常用的引脚封装形式为AXIAL系列,包括AXIAL-0.3、AXIAL-0.4、AXIAL-0.5、AXIAL-0.6、AXIAL-0.7、AXIAL-0.8、AXIAL-0.9和AXIAL-1.0等封装形式,其后缀数字代表两个焊盘的间距,单位为“英寸”,如图F1-5(b)所示。常用固定电阻的实物图如图F1-5(c)所示。

ALLEGRO元件封装制作

1. Allegro 零件库封装制作的流程步骤。 2. 规则形状的smd 焊盘制作方法。 3. 表贴元件封装制作方法。 4. 0805贴片电容的封装制作实例。 先创建焊盘,再创建封装 一、先制作焊盘 制作焊盘软件路径:candence\Release 16.6\PCB Editor Utilities\Pad Designer Pad Designer 界面 solderMask_top 比其它层大0.1mm,焊盘数据可以用复制、粘贴来完成。 当前层

Null:空; Circle:圆形; Square: 正方形; Oblong:椭圆形; Rectangle:长方形; Octagon: 八边形; Shape:形状; 封装制作完成后,选择路径,命名后进行保存Rect_x1_15y1_45 二、制作封装 操作步骤:打开Allegro 软件(allegro PCB design GXL ) file(new) OK 进入零件封装编辑界面。 设置图纸的尺寸(元件尺寸太小,所以图纸的尺寸也要设置小) 单位:毫米 X \Y:坐标原点绝对坐标设置 精度: 4 封装类型 线(机械)设置 栅格点设置,setup--Grid

第20讲 一、正式绘制元件封装 操作步骤: layout Pins 如果要把焊盘放在原点(0,0),选择好焊盘后,在命令(command )行输入x 0 0 ,然后回车,这样焊盘就自动跳到坐标原点(0,0)上啦。 二、盘放置好后,绘制零件的框。步骤如下: Add Line 输入坐标的方式输入,用命令(command )输入 如下图 表示具有电气连接的焊盘 表示没有电气连接的焊盘或引脚 选择路径,找到需要的焊盘 Rectangular:焊盘直线排列 Polar:焊盘弧形排列 Qty:表示直线排列数量; Spacing:两个焊盘中心 点之间的距离; Order:排列方向 旋转角度 Pin#:焊盘编号1 Inc:表示增量为1 Text block:表示字符的大小 OffsetX:表示字符放在焊盘中心 Class 与subclass 要选好 单独显示这一层的效果

,PCB制作元件封装大全

DXP2004下Miscellaneous Devices.Intlib元件库中常用元件有: 电阻系列(res*)排组(res pack*) 电感(inductor*) 电容(cap*,capacitor*) 二极管系列(diode*,d*) 三极管系列(npn*,pnp*,mos*,MOSFET*,MESFET*,jfet*,IGBT*) 运算放大器系列(op*) 继电器(relay*) 8位数码显示管(dpy*) 电桥(bri*bridge) 光电耦合器( opto* ,optoisolator ) 光电二极管、三极管(photo*) 模数转换、数模转换器(adc-8,dac-8) 晶振(xtal) 电源(battery)喇叭(speaker)麦克风(mic*)小灯泡(lamp*)响铃(bell) 天线(antenna) 保险丝(fuse*) 开关系列(sw*)跳线(jumper*) 变压器系列(trans*) ????(tube*)(scr)(neon)(buzzer)(coax) 晶振(crystal oscillator)的元件库名称是Miscellaneous Devices.Intlib, 在search栏中输入*soc 即可。 ########### DXP2004下Miscellaneous connectors.Intlib元件库中常用元件有: (con*,connector*) (header*) (MHDR*) 定时器NE555P 在库TI analog timer circit.Intlib中 电阻AXIAL 无极性电容RAD 电解电容RB- 电位器VR 二极管DIODE

超详细的反激式开关电源电路图讲解

反激式开关电源电路图讲解 一,先分类 开关电源的拓扑结构按照功率大小的分类如下: 10W以内常用RCC(自激振荡)拓扑方式 10W-100W以内常用反激式拓扑(75W以上电源有PF值要求) 100W-300W 正激、双管反激、准谐振 300W-500W 准谐振、双管正激、半桥等 500W-2000W 双管正激、半桥、全桥 2000W以上全桥 二,重点 在开关电源市场中,400W以下的电源大约占了市场的70-80%,而其中反激式电源又占大部分,几乎常见的消费类产品全是反激式电源。 优点:成本低,外围元件少,低耗能,适用于宽电压范围输入,可多组输出. 缺点:输出纹波比较大。(输出加低内阻滤波电容或加LC噪声滤波器可以改善) 今天以最常用的反激开关电源的设计流程及元器件的选择方法为例。给大家讲解如何读懂反激开关电源电路图! 三,画框图 一般来说,总的来分按变压器初测部分和次侧部分来说明。开关电源的电路包括以下几个主要组成部分,如图1

图1,反激开关电源框图 四,原理图 图2是反激式开关电源的原理图,就是在图1框图的基础上,对各个部分进行详细的设计,当然,这些设计都是按照一定步骤进行的。下面会根据这个原理图进行各个部分的设计说明。 图2 典型反激开关电源原理图

五,保险管 图3 保险管 先认识一下电源的安规元件—保险管如图3。 作用:安全防护。在电源出现异常时,为了保护核心器件不受到损坏。 技术参数:额定电压 ,额定电流 ,熔断时间。 分类:快断、慢断、常规 计算公式:其中:Po:输出功率 η效率:(设计的评估值) Vinmin :最小的输入电压 2:为经验值,在实际应用中,保险管的取值范围是理论值的1.5~3倍。 0.98: PF值 六,NTC和MOV NTC 热敏电阻的位置如图4。 图4 NTC热敏电阻

发动机总体构造认识教案

发动机总体构造认识教 案 -CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN

项目二发动机总体构造认识 一、目的和要求: 1.掌握发动机电子控制系统总体组成; 2.区分与识别发动机电子控制系统的主要传感器、执行器; 3.掌握发动机电子控制系统的工作原理。 二、实训课时: 2课时 三、实训器材 1、工具:常用工具1套。 2、设备:科鲁兹轿车科鲁兹型发动机、别克电喷发动机故障实训台各一台,科鲁兹和丰田皇冠轿车整车各一辆。 一、科鲁兹发动机在整车中的位置 汽车发动机是汽车的动力源泉,为整个汽车提供动力。一般轿车来说,除个别型号的汽车外,发动机通常安装在车头箱中。 2

1—科鲁兹发动机 2—离合器 3—变速器 4—真空助力器5—防抱死制动系统(ABS) 6—动力转向器 7—传动轴 8—盘式 制动器(前轮) 9—前悬架 10—排气系统 11—燃油箱 12—后悬架 13—鼓式制动器(后轮) 14—车身 二、科鲁兹发动机技术参数 1.发动机代码科鲁兹 2.排量 1.781L 3.缸径 81mm 4.冲程 86.4mm 5.压缩比 9.5 6.功率 74kW 7.额定功率时转速 5200 r/min 8.最大扭矩 155Nm 9.最大扭矩是转速 3800 r/min 10.使用汽油标号(研究法辛烷值) 90 RON 11.喷射控制系统 M.3.8.2 12.点火系统 M.3.8.2. 13.爆震控制有 14.自诊断有 15.λ控制有 三、科鲁兹发动机总体结构 1.作用发动机的作用主要是将燃料燃烧的热能转化成机械能,并对外输出。 2.组成汽油发动机基本上都是由2大机构和5大系统组成:曲柄连杆机构、配气机构、燃料供给系、润滑系、冷却系、点火系和起动系。 3