SRAM存储基本单元

SRAM存储基本单元

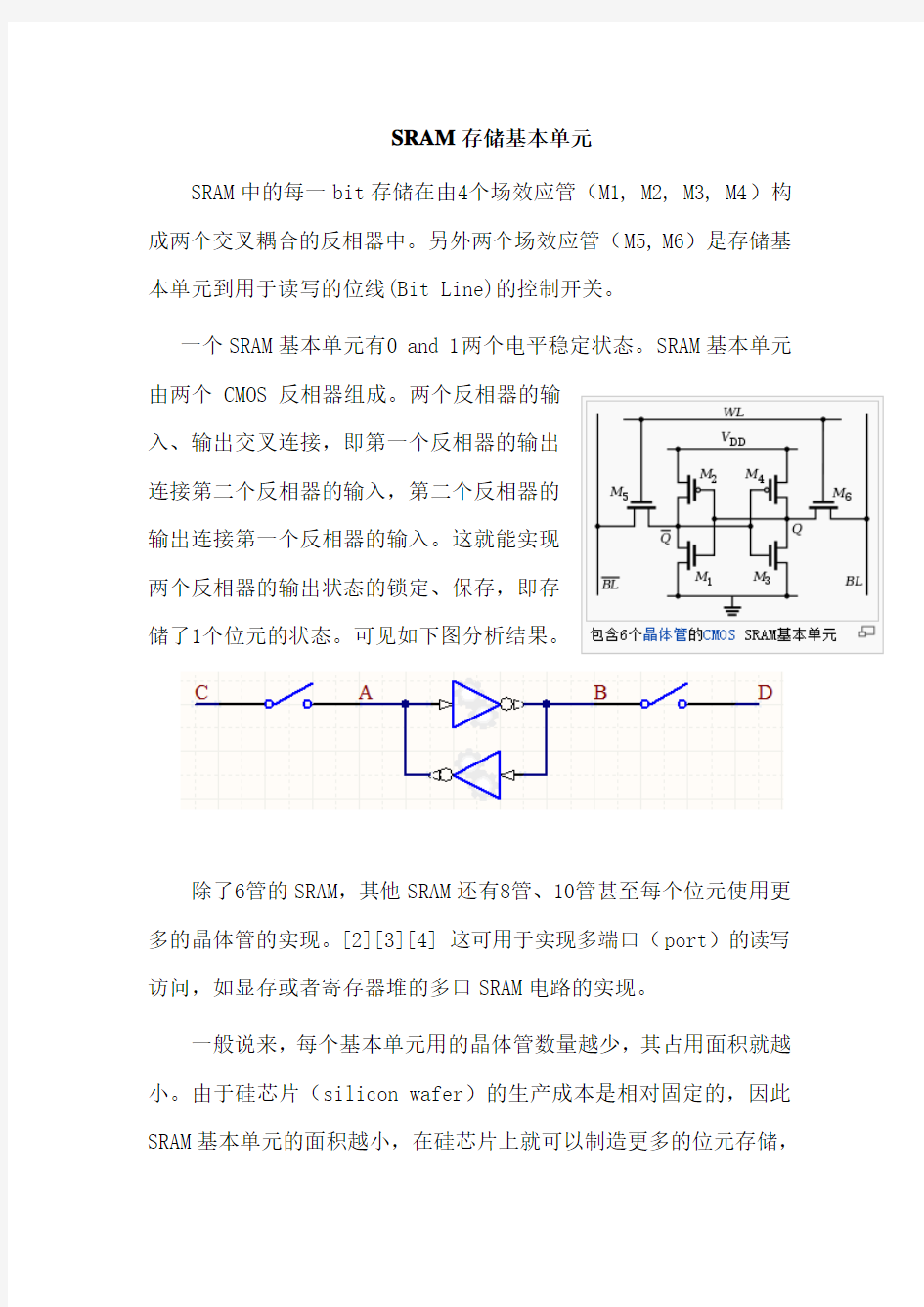

SRAM中的每一bit存储在由4个场效应管(M1, M2, M3, M4)构成两个交叉耦合的反相器中。另外两个场效应管(M5, M6)是存储基本单元到用于读写的位线(Bit Line)的控制开关。

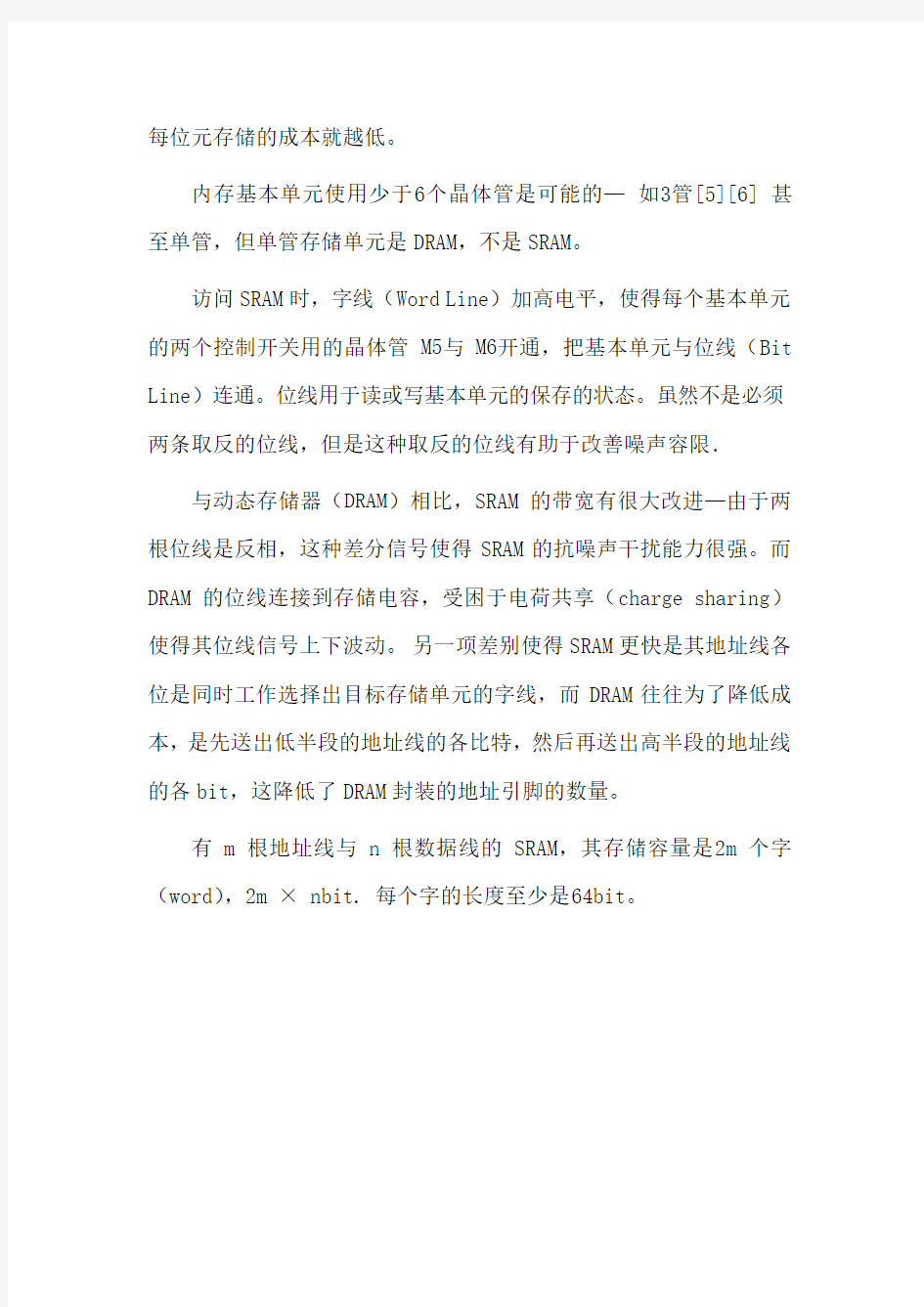

一个SRAM基本单元有0 and 1两个电平稳定状态。SRAM基本单元由两个CMOS反相器组成。两个反相器的输

入、输出交叉连接,即第一个反相器的输出

连接第二个反相器的输入,第二个反相器的

输出连接第一个反相器的输入。这就能实现

两个反相器的输出状态的锁定、保存,即存

储了1个位元的状态。可见如下图分析结果。

除了6管的SRAM,其他SRAM还有8管、10管甚至每个位元使用更多的晶体管的实现。[2][3][4] 这可用于实现多端口(port)的读写访问,如显存或者寄存器堆的多口SRAM电路的实现。

一般说来,每个基本单元用的晶体管数量越少,其占用面积就越小。由于硅芯片(silicon wafer)的生产成本是相对固定的,因此SRAM基本单元的面积越小,在硅芯片上就可以制造更多的位元存储,

每位元存储的成本就越低。

内存基本单元使用少于6个晶体管是可能的—如3管[5][6] 甚至单管,但单管存储单元是DRAM,不是SRAM。

访问SRAM时,字线(Word Line)加高电平,使得每个基本单元的两个控制开关用的晶体管M5与M6开通,把基本单元与位线(Bit Line)连通。位线用于读或写基本单元的保存的状态。虽然不是必须两条取反的位线,但是这种取反的位线有助于改善噪声容限.

与动态存储器(DRAM)相比,SRAM的带宽有很大改进—由于两根位线是反相,这种差分信号使得SRAM的抗噪声干扰能力很强。而DRAM的位线连接到存储电容,受困于电荷共享(charge sharing)使得其位线信号上下波动。另一项差别使得SRAM更快是其地址线各位是同时工作选择出目标存储单元的字线,而DRAM往往为了降低成本,是先送出低半段的地址线的各比特,然后再送出高半段的地址线的各bit,这降低了DRAM封装的地址引脚的数量。

有m根地址线与n根数据线的SRAM,其存储容量是2m个字(word),2m × nbit. 每个字的长度至少是64bit。

EEPROM存储器概述

非易失性存储器概述 一、介绍 这篇文章论述了非易失性存储器(NVM)基本概况。第1部分介绍了非易失性存储器的主要背景以及一些存储器的基本术语。第2部分主要阐述了非易失性存储器的工作原理(通过热电子注入实现编程)。第3部分包含了非易失性存储器的擦除原理,以及隧道效应。第4部分介绍了用于预测非易失性存储器的编程特性的模型,用“幸运电子”模型来表述热电子注入模式。第5部分主要介绍非易失性存储器可靠性,包括在数据保存、耐受力和干扰影响下的可靠性。 关键词:非易失性,存储器,热电子注入,隧道效应,可靠性,保存,存储干扰,EEPROM,Flash EEPROM。 存储器分为两大类:易失性存储器和非易失性存储器。易失性存储器在掉电后会失去其所存储的数据,故而需要继续不断的电源才能保存数据。大部分的随机存取存储器(RAM)都是易失性的。非易失性存储器则在掉电后不会丢失数据。一个非易失性存储器(NVM)本质上是一个MOS管,由一个源极、一个漏极、一个门极,以及一个浮栅。与常用的MOSFET 不同的是,NVM多了一个浮栅,浮栅与其它部分是绝缘的。非易失性存储器又细分为两个主要的分类:浮栅型和电子俘获型。Kahng 和Sze在1967年发明了第一个浮栅型器件。在这种器件中,电子受隧道效应的影响,通过一个3nm厚的二氧化硅层,从一个浮栅中转移到基层中。通过隧道效应,非易失性存储器可以更容易地被擦除或改写,通常隧道效应只在厚度小于12nm的氧化物中存在。浮栅中存储电子后,可以使得阈值电压被降低或者提高,而阈值电压的高低也就分别代表了逻辑值1或0。 在浮栅型存储器件中,电子(也即是数据)存储在浮栅中,故而掉电后,数据不会丢失。所有的浮栅型存储器件都是一样的存储单元结构,如下图1所示,一个存储单元由门极MOS 管堆叠而成。第一个门是浮栅门,被埋在栅氧化层(Gate Oxide)和内部多晶硅绝缘层(IPD)之间,位于控制门(Control Gate)的下方。内部多晶硅绝缘层将浮栅隔绝起来,它可以是氧化物,或者氧化物-氮化物-氧化物层(ONO)。SiO2绝缘层将MOS管包围起来,作为保护层,使其免受划伤和杂质污染。第二个门极是控制门,这个门是可以被外部所接触到的。浮栅门常用在EPROM里(Electrically Programmable Read Only Memory)和EEPROM 里(Electrically Erasable and Programmable Read Only Memory)。 图1:基本的浮栅门结构

存储系统概述

存储系统概述 第3章存储系统第3章存储系统3.1存储器概述3.2半导体读写存储器3.3半导体只读存储器和闪速存储器3.4主存储器与CPU的连接3.5并行存储器3.6高速缓冲存储器(Cache)3.7虚拟存储器3.8外存储器典型习题与解答 3.1存储器概述 3.1.1存储器分类 3.1.2存储系统的设计及分级结构 3.1.3主存储器的性能指标 3.1.1存储器分类存储器:计算机硬件系统中用于存放程序和数据等二进制信息的部件。 1、按存储介质分类 2、按存取方式分类 3、按在计算机中的功能分类 4、其他分类1、按存储介质分类(1)由半导体器件组成的半导体存储器; (2)由磁性材料做成的磁表面存储器,例如磁盘存储器和磁带存储器; (3)由光介质构成的光介质存储器,一般做成光盘。 2、按存取方式分类(1)随机存取存储器RAM(Random Access Memory) 存储单元都能按地址访问,而且存取时间与存储单元的物理位置无关的存储器,称为RAM。 例如半导体读写存储器

主要用途:主存、Cache、外设缓存。 (2)顺序存取存储器SAM(Sequential Access Memory) 信息按顺序写入或读出的存储器,称为SAM。以记录块为单位编址。例如:磁带存储器 特点:存储容量大,位价格低廉,存取速度慢。 主要用途:辅助存储器。 (3)直接存取存储器DAM(Direct Access Memory) 首先按存取信息的区域随机访问,然后在指定区域用顺序方式存取的存储器,称为DAM。例如:磁盘存储器 特点:容量较大,速度和位价格介于SAM和RAM之间 主要用途:辅助存储器。 3、按在计算机中的功能分类(1)主存储器(主存) 用于存放计算机运行期间的大量程序和数据的存储器,CPU能直接访问。 由动态MOS存储器构成 (2)高速缓冲存储器Cache Cache:介于CPU和主存之间的高速小容量存储器,用于存放最活跃的程序块和数据。特点:速度快,但容量小。(3)辅助存储器(外存储器)存放当前暂不参与运行的程序和数据,需要时再与主存成批交换 信息的存储器。 组成:磁表面存储器,光盘存储器。 特点:容量大,可存放大量的程序和数据,但速度慢。 外存的信息需要调入主存后才能被CPU使用。(4)控制存储器CM

F28335存储器功能概述

F28335存储器功能概述 班级: 姓名: 学号:

F28335芯片整体功能框图 存储器映射 1、F28335使用32位数据地址线和22位程序地址线。 2、32位数据地址线可访问4GB的数据空间, 16位/32位 3、22位程序地址线可访问4MB的程序空间。 16位/32位。 4、存储器模块采用统一编址方式映射到程序空间和数据空间。F28335的存储器分为以下几部分: 1. 单周期访问RAM(SARAM) 2. Flash存储器 3. OTP存储器 4. Boot ROM(装载了引导程序) 5. 安全模块 6. 外设存储器(片内的外设) 7. 片外存储器 一、单周期访问RAM(SARAM) 共分10部分: (1)M0和M1,可映射到数据空间或程序空间

(2)L0~L3、 L4~L7,可映射到数据空间或程序空间 二、flash存储器 闪存的英文名称是"Flash Memory",一般简称为"Flash",它属于内存器件的一种,是一种不挥发性( Non-Volatile )内存。闪存的物理特性与常见的内存有根本性的差异:目前各类 DDR 、 SDRAM 或者 RDRAM 都属于挥发性内存,只要停止电流供应内存中的数据便无法保持,因此每次电脑开机都需要把数据重新载入内存;闪存在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何flash器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。F28335的Flash存储器一般可以把程序烧写到Flash中,以避免带着仿真器试调。F28335器件包含256K*16位的嵌入式闪存存储器,被分别放置在8个32k*16位扇区内。 三、OTP存储器 OTPROM(One Time Programmable Read-Only Memory),可以进行片内编程操作,而且可以增强加密功能。然而OTP ROM MCU的OTPROM 存在一个缺点:不可擦除,也就是说只能编程一次,不能实现重复编程,不利于大量普及使用。当程序从仿真器移植到单片机的OTPROM 时,并不能保证程序的一次成功性,由于单片机的不可擦除性,若程序脱机一次就使用一片单片机,显然将造成巨大的资源浪费。另一方面,对于复杂系统,16 KB的OTPROM容量如果不够,则需要采用扩展外部存储器,为了保证有效实现加密功能,应保留一部分程序在

计算机存储器概述

计算机存储器概述 位(bit)是二进制数的最基本单位,也是存储器存储信息的最小单位,8位二进制数称为一个字节(byte)。当一个数作为一个整体存入或取出时,这个数叫做存储字。存储字可以是一个字节,也可以是若干个字节。若干个忆记单元组成一个存储单元,大量的存储单元的集合组成一个存储体(MemoryBank)。 为了区分存储体内的存储单元,必须将它们逐一进行编号,称为地址。地址与存储单元之间一一对应,且是存储单元的唯一标志。应注意存储单元的地址和它里面存放的内容完全是两回事。 存储器在计算机中处于不同的位置,可分为主存储器和辅助存储器。在主机内部,直接与CPU交换信息的存储器称主存储器或内存储器。在执行期间,程序的数据放在主存储器内,各个存储单元的内容可通过指令随机访问,这样的存储器称为随机存取存储器(RAM)。另一种存储器叫只读存储器(ROM),里面存放一次性写入的程序或数据,仅能随机读出。RAM和ROM共同分享主存储器的地址空间。 因于结构、价格原因,主存储器的容量受限。为满足计算的需要而采用了大容量的辅助存储器或称外存储器,如磁盘、光盘等。 存储器的主要技术指标 存储器的特性由它的技术参数来描述。 一、存储容量:存储器可以容纳的二进制信息量称为存储容量。主存储器的容量是指用地址寄存器(MAR)产生的地址能访问的存储单元的数量。如N位字长的MAR能够编址最多达2N个存储单元。一般主存储器(内存)容量在几十K到几M字节左右;辅助存储器(外存)在几百K到几千M字节。 二、存储周期:存储器的两个基本操作为读出与写入,是指将信息在存储单元与存储寄存器(MDR)之间进行读写。存储器从接收读出命令到被读出信息稳定在MDR的输出端为止的时间间隔,称为取数时间TA;两次独立的存取操作之间所需的最短时间称为存储周期TMC。半导体存储器的存储周期一般为100ns-200ns。 三、存储器的可靠性:存储器的可靠性用平均故障间隔时间MTBF来衡量。MTBF可以理解为两次故障之间的平均时间间隔。MTBF越长,表示可靠性越高,即保持正确工作能力越强。 四、性能价格比:性能主要包括存储器容量、存储周期和可靠性三项内容。性能价格比是一个综合性指标,对于不同的存储器有不同的要求。对于外存储器,要求容量极大,而对缓冲存储器则要求速度非常快,容量不一定大。因此性能/价格比是评价整个存储器系统很重要的指标。(俞欣)

Flash存储器概述

This document contains information on one or more products under development at Spansion LLC. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion LLC reserves the right to change or discontinue work on this proposed product without notice. Publication Number FlashOverview_AN Revision A Amendment 0 Issue Date November 10, 2005 Introduction All computer-based systems contain memory. Memory is where information is stored while waiting to be operated on by the Central Processing Unit (CPU) of the computer . There are two types of memory. They are volatile memory and non-volatile memory. Volatile memory retains its information only while power is applied to the memory de-vice. The contents of this memory type may be easily and quickly changed. Non-volatile memory retains its information even when no power is applied to the memory device. Although the information in most non-volatile memories may be changed, the process involved is much slower than for volatile memory. Volatile Memory Volatile memory loses its contents when the device loses power . Random Access Mem-ory (RAM) is the traditional name used for volatile memory. The name refers to the ability to access any location of the memory quickly with no particular order of accesses needed. Static RAM (SRAM) and Dynamic RAM (DRAM) are two examples of volatile memories that have this characteristic. SRAM typically uses six transistors for each memory bit (cell) to retain data as long as power is being supplied. This makes each memory cell relatively large and limits SRAM to use in lower density memories. SRAM can provide faster access to data, use less standby power , and tends to be more expensive than DRAM. DRAM uses a single transistor and a small capacitor for each bit of memory. Since ca-pacitors do not hold a charge indefinitely, DRAM cells must be frequently recharged (refreshed) to avoid losing the contents. These smaller memory cells allow DRAM to be used for high density, low cost memories, but are typically slower than SRAM. Flash Memory: An Overview Application Note