HDI产品介绍

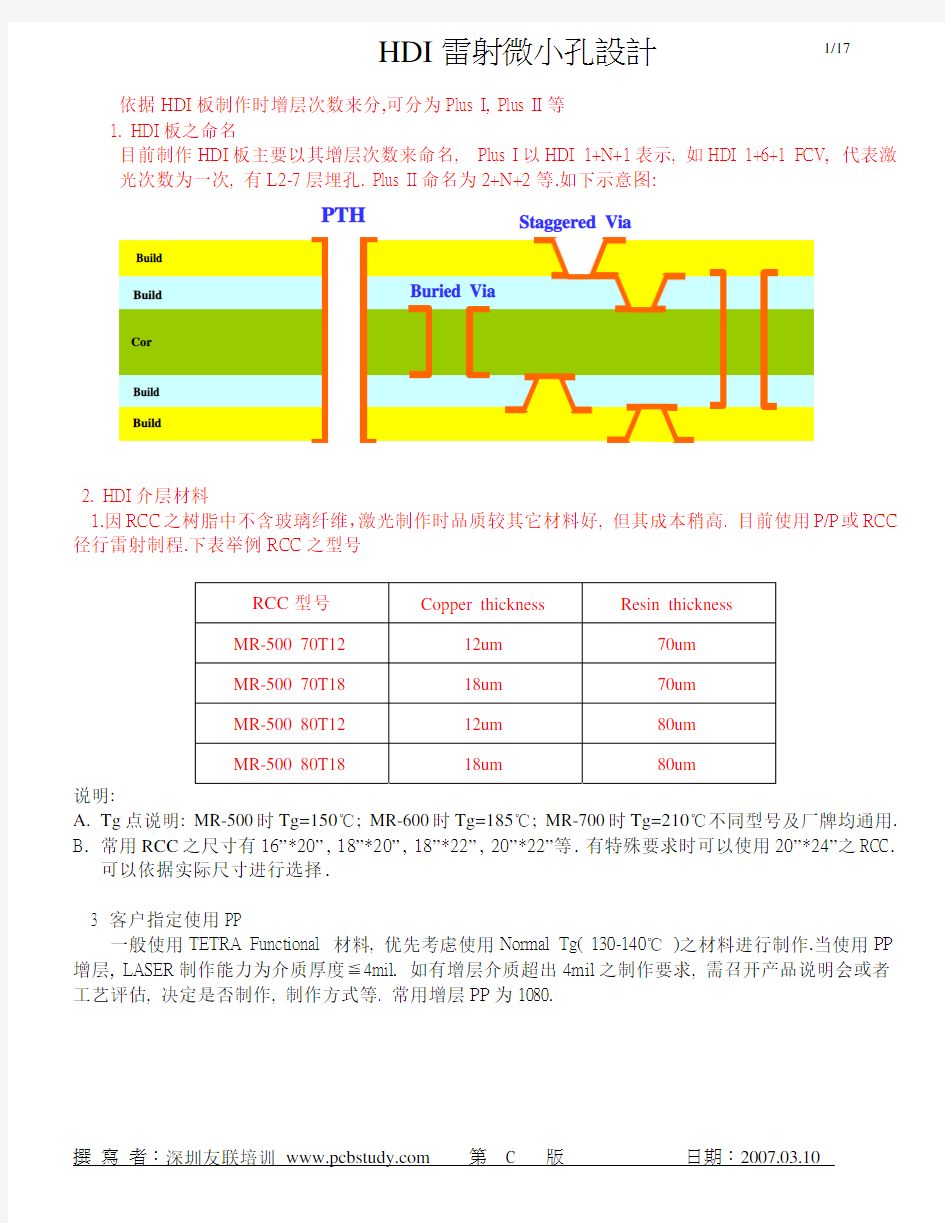

依据HDI 板制作时增层次数来分,可分为Plus I, Plus II 等 1. HDI 板之命名

目前制作HDI 板主要以其增层次数来命名, Plus I 以HDI 1+N+1表示, 如HDI 1+6+1 FCV, 代表激光次数为一次, 有L2-7层埋孔. Plus II 命名为2+N+2等.如下示意图:

Staggered Via PTH

2. HDI 介层材料

1.因RCC 之树脂中不含玻璃纤维,激光制作时品质较其它材料好, 但其成本稍高. 目前使用P/P 或RCC 径行雷射制程.下表举例RCC 之型号

RCC 型号 Copper thickness

Resin thickness

MR-500 70T12 12um 70um MR-500 70T18 18um 70um MR-500 80T12 12um 80um MR-500 80T18

18um

80um

说明:

A. Tg 点说明: MR-500时Tg=150℃; MR-600时Tg=185℃; MR-700时Tg=210℃不同型号及厂牌均通用.

B. 常用RCC 之尺寸有16”*20”, 18”*20”, 18”*22”, 20”*22”等. 有特殊要求时可以使用20”*24”之RC

C.可以依据实际尺寸进行选择.

3 客户指定使用PP

一般使用TETRA Functional 材料, 优先考虑使用Normal Tg( 130-140℃ )之材料进行制作.当使用PP 增层, LASER 制作能力为介质厚度≦4mil. 如有增层介质超出4mil 之制作要求, 需召开产品说明会或者工艺评估, 决定是否制作, 制作方式等. 常用增层PP 为1080.

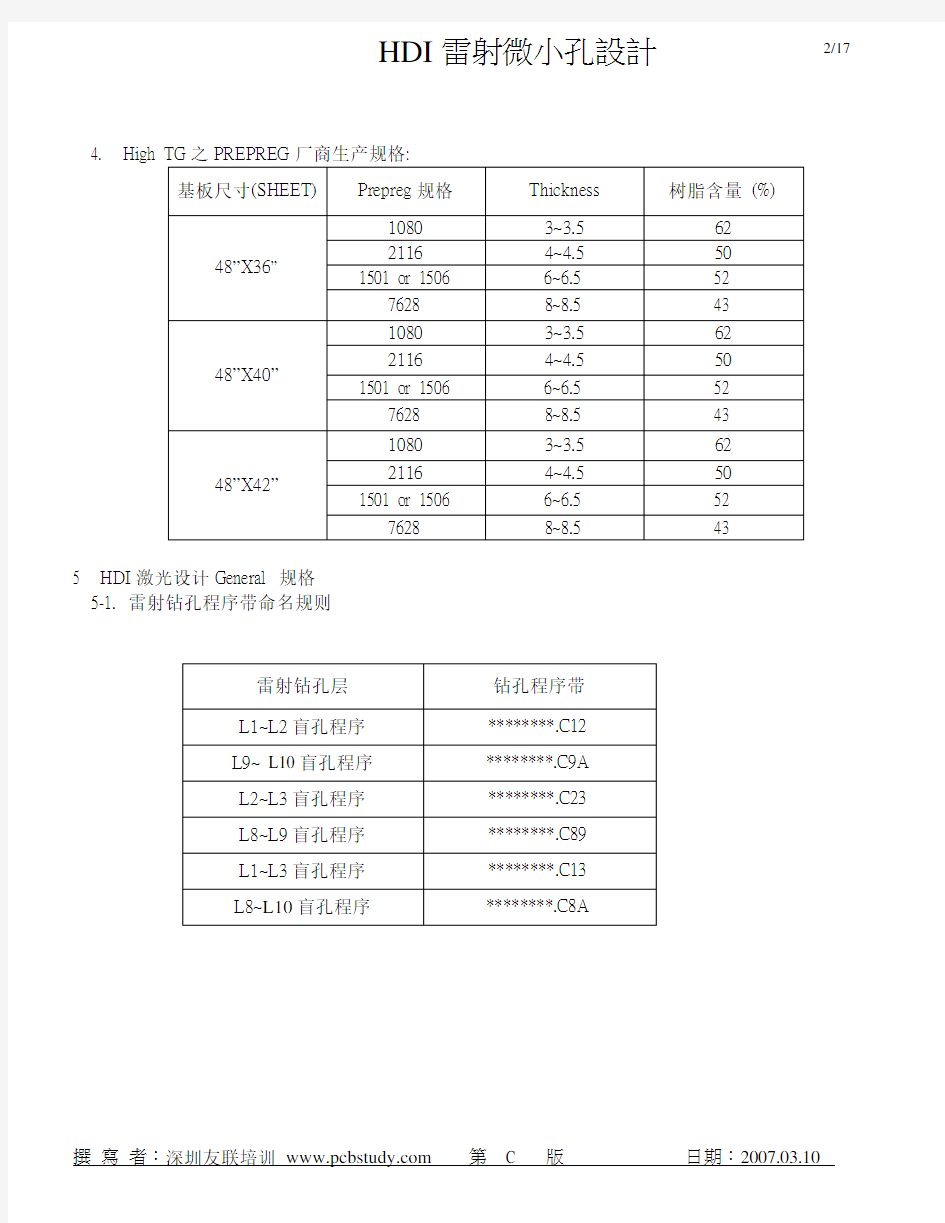

4. High TG之PREPREG厂商生产规格:

基板尺寸(SHEET)Prepreg规格Thickness树脂含量(%)

10803~3.562

21164~4.550

48”X36”

1501 or 1506 6~6.5 52

7628 8~8.5 43

10803~3.562

21164~4.550

48”X40”

1501 or 1506 6~6.5 52

7628 8~8.5 43

10803~3.562

21164~4.550

48”X42”

1501 or 1506 6~6.5 52

7628 8~8.5 43

5 HDI激光设计General 规格

5-1. 雷射钻孔程序带命名规则

雷射钻孔层钻孔程序带

L1~L2盲孔程序********.C12

L9~ L10盲孔程序********.C9A

L2~L3盲孔程序********.C23

L8~L9盲孔程序********.C89

L1~L3盲孔程序********.C13

L8~L10盲孔程序********.C8A

5-2. 雷射钻孔设计制作能力举例:

HDI Board Capability (Laser Buried & Blind Via)

RCC

Layer to Layer Reg. ± 5 mil±

4 mil±3 mil ±2 mil Impedance control ± 10%(±5Ω)± 10%(±4Ω

)± 7 % (±3Ω) ± 5%(± 2.5Ω)

0.004 “

0.008 “

0.004 “0.004 “

0.004 “/0.004”

Laser Via PCB Capability

Feature Mass Production Sample Run

(Normal)

Lower cost)

(High V ol.

Normal (Small V ol.)

(High V ol.

Higher cost)

Line /Spacing Width (Tra. Layers)

Drill Via Diameter

0.005 “/0.005”

0.010 “

0.004 “/0.004”

0.010 “0.010 “

(PTH)

Line /Spacing Width (HDI Layers) 0.005 “/0.005” 0.003 “/0.003” 0.0025

0.003 0.0025 “/0.0025”

Drill Capture Pad (PTH)

Microvia Diameter (Unfinished)

Microvia Capture Pad

0.022 “0.020 “0.018 “

0.011 “

0.016 “

0.003 “

0.009 “

0.014 “0.012 “

6. HDI (1+N+1) FCV设计规则

6-1 HDI板常用叠构(蓝色为laser孔,绿色为机械孔)

A.HDI(1+2+1) Simple

B. HDI(1+4+1) Simple

C. HDI(1+6+1) Simple …依此类推Aspect Ratio (PTH) 8 : 19 : 110 : 1 11 : 1

0.6 : 10.8 : 10.9 : 1 1 : 1 Aspect Ratio (MicroVia)

Microvia Diameter (Unfinished)

Microvia Ca ture Pad

0.004 “

0.011 “

0.003“

0.010 “

0.014 “

0.005 “

0.012 “

0.004“

PP

p

HDI Simple制作流程(Tenting)

裁板→内钻→内层压膜→内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→外层压合→MASK制作(压膜、曝光及显影、蚀刻、去膜) →AOI→雷射孔对位→雷射钻孔→Desmear、Micro-etching、BLASER →钻孔→电镀→外层曝光→显影、蚀刻、去膜→AOI检查及VRS→塞孔→静电喷涂→文字印刷→浸镍金→捞型→测试→目检→包装及出货。

A.HDI(1+2+1) FCV

B. HDI(1+4+1) FCV

C. HDI(1+6+1) FCV

HDI(1+6+1) FCV制作流程如下:

裁板→内钻→内层压膜(内一) →内层曝光

→显影、蚀刻、去膜→AOI检查及VRS

→黑化还原→叠板及压合(一压) →盲(埋)孔钻孔→电镀→(埋孔)塞孔→研磨→内层压膜(内二) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→压合→MASK制作(含压膜、曝光及显影、蚀刻、去膜) →AOI→雷射孔对位→雷射钻孔→Desmear、Micro-etching、BLASER →钻孔→电镀→外层曝光→显影、蚀刻、去膜→AOI检查及VRS→塞孔→静电喷涂→文字印刷→浸镍金→捞型→测试→目检→包装及出货。

C.HDI(1+6+1) Scaled FCV …依此类推

HDI(1+3+3+1) FCV(含L2-L7埋孔)制作流程如下:

裁板→内钻→内层压膜(内一) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→叠板及压合(一压) →去黑膜→盲(埋)孔钻孔→电镀→(埋孔)塞孔一→研磨→内层压膜(内二) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→压合(二压) →去黑膜→减

铜, 研磨 → 埋孔钻孔 → 电镀 → 塞孔 → 研磨 → 内层压膜(内三) → 内层曝光 →显影、蚀刻、去

膜 → AOI 检查及VRS → 黑化还原 →外层压合 → MASK 制作(含压膜、曝光及显影、蚀刻、去膜) → AOI → 雷射孔对位 → 雷射钻孔 → Desmear 、Micro-etching 、BLASER → 钻孔? 电镀 → 外层曝光 → 显影、蚀刻、去膜 → AOI 检查及VRS →塞孔→静电喷涂→文字印刷→浸镍金→捞型→测试→目检→包装及出货。

7 PLUSII (HDI 2+N+2) 设计规则

较常使用之PLUSII 孔型设计有Staggered via, Step via, Skip via 及Stacked via. 以下将以L1-2-3为例, 针对其设计方式及构成详述如下:

A. Staggered via

分别导通L1-L2及L2-L3的孔,其特征是上下两层激光也是错开的, 不在同一位置上。

设计方式

a. L1-L2及L2-L3单层孔径大小及设计方式同PLUS 1的雷射盲孔设计方式。

b. L1-L2孔径下幅和L2-L3孔径上幅同NET 相距至少5 MIL 。 Min 3 mil

e d p

m j

B. Skip via

分别导通L1-L2及L2-L3的孔, 导通L1和L3但不导通L2.

设计方式

(1) 此种孔的设计样式类似PLUS 1的雷射盲孔,但因介层较厚,在考虑ASPECT RATIO ≦0.8下,孔径需做比较大。最小孔径设计如下:

孔上幅=L1至L3的厚度(孔深)÷纵横比0.8

孔下幅=孔上幅-2 × L1至L3的介层厚度 × tan15° MASK 设计值=孔上幅-蚀刻补偿值

Ps. (I)此处 L1至L3厚度是含制做MASK 时的面铜厚,但不含L3铜厚。

(2) 在PAD 的设计(最小值)部份如下:

CAPTURE PAD =孔径上幅+ 6 MIL +蚀刻补偿值

L2的ANTI-PAD =孔径于L2时宽度+ 6 MIL-蚀刻补偿值 TARGET PAD =孔径下幅+12 MIL+蚀刻补偿值

PS:(I)孔径于L2时的宽度值可依孔上下幅的计算方式得之。

(II)第三个式子中的12 MIL 是考虑两次压合,每次以3 MIL(单边)计算。 d/h ≦ 0.8

由于此料号在制作时不是很好控制, 其制作良率不高.因此,如果客户在原始设计中要求以此种孔型设计时, 需向客户建议在保证电性导通的前提下改以STEP VIA 或stacked via 进行制作.

各项设计参数

厚度v.s. 最小孔径单位(mil)

L1至L3厚度孔径上幅(MIN) 孔径下幅MASK设计值CAPTURE PAD(MIN)TARGET PAD(MIN)

5.0 (4.5)

6.25 3.84 5.75 14.25 16.75

5.5 (5.0) 7.0 4.32

6.5 15.0 1

7.25

6.0 (5.5)

7.5 4.55 7.0 15.5 17.5

6.5 (6.0) 8.25 5.03

7.75 16.25 1

8.0

PS. 第一栏括号内的值为L1至L3的介层厚度

孔径v.s. 最小锡垫unit:mil L1-L3介层厚度孔径上幅孔径下幅MASK CAPTURE PAD (MIN)TARGET PAD (MIN)

6.5 4.0 6.0 14.5 16.75

7.0 4.5 6.5 15.0 17.25

4.5

7.5 5.0 7.0 15.5 17.75

8.0 5.5 7.5 16.0 18.25

8.5 6.0 8.0 16.5 18.75

9.0 6.5 8.5 17.0 19.25

7.5 4.75 7.0 15.5 17.5

8.0 5.25 7.5 16.0 18.0

5.0

8.5 5.75 8.0 16.5 18.5

9.0 6.25 8.5 17.0 19.0

9.5 6.75 9.0 17.5 19.5

10.0 7.25 9.5 18.0 20.0

8.0 5.0 7.5 16.0 17.75

8.5 5.5 8.0 16.5 18.25

5.5

9.0 6.0 8.5 17.0 18.75

9.5 6.5 9.0 17.5 19.25

10.0 7.0 9.5 18.0 19.75

10.5 7.5 10.0 18.5 20.25

8.5 5.25 8.0 16.5 18.0

9.0 5.75 8.5 17.0 18.5

6.0

9.5 6.25 9.0 17.5 19.0

10.0 6.75 9.5 18.0 19.5

10.5 7.25 10.0 18.5 20.0

11.0 7.75 10.5 19.0 20.5

9.0 5.5 8.5 17.0 18.25

9.5 6.0 9.0 17.5 18.75

6.5

10.0 6.5 9.5 18.0 19.25

10.5 7.0 10.0 18.5 19.75

11.0 7.5 10.5 19.0 20.25

11.5 8.0 11.0 19.5 20.75

9.5 5.75 9.0 17.5 18.5

10.0 6.25 9.5 18.0 19.0

7.0 10.5 6.75 10.0 18.5 19.5

11.0 7.25 10.5 19.0 20.0 11.5 7.75 11.0 19.5 20.5 12.0

8.25

11.5

20.0

21.0

C. STEP VIA :

也称为TELESCOPIC VIA, 为同时导通L1、L2和L3的孔(即L1-L2-L3)。为防止因对准度造成的对位偏移, 此种孔于L1-L2

A. 设计方式

(1) 孔径分L1-L2及L2-L3两个部份,设计(MIN)如下: L2至L3孔径

=同PLUS 1的雷射盲孔设计方式 L1至L2孔径上幅= L1至L2孔径下幅+ 0.5 MIL L1至L2孔径下幅= L2至L3孔径上幅+ 6 MIL L2的MASK 设计= L2至L3孔径上幅-蚀刻补偿值 L1的MASK 设计= L1至L2孔径上幅-蚀刻补偿值

PS: L1至L2孔径因overshooting 的原因, 上下幅约相差0.5 MIL 。

(2) 在PAD 方面的设计(MIN)如下:

CAPTURE PAD =上幅孔径+ 6 MIL+蚀刻补偿

L2的PAD =L1至L2孔径的下幅+ 6 MIL+蚀刻补偿 TARGET PAD =孔径下幅+ 6 MIL+蚀刻补偿值

Min 3 mil

unit :mil

L2-L3孔径 L1-L2孔径(MIN) L2 MASK L1 MASK CAPTURE PAD (MIN)L2 PAD (MIN)TARGET PAD (MIN)

4.0 3.5 10.5 10.0 18.5 16.5 9.75 4.5 4.0 11.0 10.5 19.0 17.0 10.25

5.0 4.5 11.5 11.0 19.5 17.5 10.75 5.5

5.0

12.0

11.5

20.0

18.0

11.25

6.0

5.5

12.5

12.0

20.5

18.5

11.75

2dow D D 2u

P 2midd D. STACKED VIA :

为同时导通L1、L2和L3的孔(即L1-L2-L3)。此种孔L1-L2和L2-L3孔处于同一位置,且大小一致.制作时L2-L3孔内以电镀填满铜, 以保证正确的导通性.

设计方式

a. L1-L2及L2-L3单层孔径大小及设计方式分别同PLUS 1的雷射盲孔设计方式。

b. STACKED VIA 盲孔孔径更小, 制作主要是电镀制程不同. 以电镀填孔的方式将L2-3的盲孔用铜镀满然后在盲孔上进行第二次激光制作, 以更小的盲孔大小削减layout 面积来达到比Step & telescopic via 更密集的线路设计.

7.3.7 PlusII(2+N+2) 以8层板为例, 常用Plus II 设计叠板结构如下图

2+N+2 FCV 2+N+2 Simple 2+N+2 Scaled

8 以PLUS II (2+4+2) Simple(含L2-L7埋孔)、须塞孔的浸金板, 其制作流程如下:

裁板→内钻→内层压膜(内一) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→叠板及压合(一压) →后处理→MASK制作(一)(含压膜、曝光及显影、蚀刻、去膜) →AOI→雷射孔对位→雷射钻孔→Desmear、Micro-etching、BLASER →埋孔钻孔→电镀→(埋孔)塞孔→研磨→内层压膜(内二) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→压合(二压) →后处理→MASK制作(含压膜、曝光及显影、蚀刻、去膜) →AOI→雷射钻孔→Desmear、Micro-etching、BLASER →外层钻孔→电镀→外层曝光→显影、蚀刻、去膜→AOI检查及VRS→塞孔→静电喷涂→文字印刷→浸镍金→捞型→测试→目检→包装出货

PLUS II (2+4+2) Simple(含L2-L7埋孔)、电镀填孔(一次电镀); 优先以一次电镀进行制作.

其简略制作流程如下:

裁板→内钻→内层压膜(内一) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→叠板及压合(一压) →后处理→MASK制作(一)(含压膜、曝光及显影、蚀刻、去膜) →AOI→雷射孔对位→雷射钻孔→Desmear、Micro-etching、BLASER →埋孔钻孔→一次铜?连续电镀→减铜?(埋孔)塞孔→研磨→内层压膜(内二) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→压合(二压) →后处理→MASK制作(含压膜、曝光及显影、蚀刻、去膜) →AOI→雷射钻孔→Desmear、Micro-etching、BLASER →外层钻孔→电镀→外层曝光→显影、蚀刻、去膜→AOI检查及VRS→塞孔→静电喷涂→文字印刷→浸镍金→捞型→测试→目检→包装出货

PLUS II (2+4+2) Simple(含L2-L7埋孔)、电镀填孔(二次电镀); 制作流程如下:

裁板→内钻→内层压膜(内一) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→叠板及压合(一压) →后处理→MASK制作(一)(含压膜、曝光及显影、蚀刻、去膜) →AOI→雷射孔对位→雷射钻孔→Desmear、Micro-etching、BLASER?一次铜?连续电镀→减铜→埋孔钻孔→电镀→(埋孔)塞孔→研磨→内层压膜(内二) →内层曝光→显影、蚀刻、去膜→AOI检查及VRS →黑化还原→压合(二压) →后处理→MASK制作(含压膜、曝光及显影、蚀刻、去膜) →AOI→雷射钻孔→Desmear、Micro-etching、BLASER →一次铜?连续电镀→减铜→外层钻孔→电镀→外层曝光→显影、蚀刻、去膜→AOI检查及VRS→塞孔→静电喷涂→文字印刷→浸镍金→捞型→测试→目检→包装出货

9 TEST KEY设计

为仿真板内雷射钻孔对准度情形,在折断边设计不同clearance之测试用Pattern. 在电测时若导通则以万用表量测就会发出声音, 业界称之为响度测试. 根据设计之clearance和实测响度, 即能了解雷射钻孔偏移情形。(clearance以2.25mil为起始,间隔0.5mil为一响)

A. PLUS I TEST KEY

L1

L2

Clearance

L3

Pattern设计:

1. Laser孔及MASK大小: 介质为RCC时LASER及MASK大小为4mil, 介质

为PP时LASER及MASK大小为4.5mil.

2. 外层PAD和PAD之pitch为40mil、trace width为30mil、L2 & L3 PAD size 为30mil

3. L1层pattern右侧多一半圆pad系辨别方向用

4. 当target层中铜箔厚度为H oz时, 工作片clearance1.75mil, 铜箔厚度为1 oz 时, 工作片clearance1.25mil; 每响以0.5mil递增.

B. STAGGERED VIA TEST KEY

单层之TEST KEY 依PLUS I 设计规则设计, L2层之TEST KEY 需拉出至外层测试.

LAYER 1

LAYER 2

LAYER 3

LAYER 4

C. SKIP VIA TEST KEY

mask 7.5 mil

孔徑8.0 mil pad 24 mil LAYER 1

LAYER 3

pad 30 mil 除9.0 mil

除14.0 mil

除15.0 mil

除16.0 mil

除11.0 mil

除12.0 mil

除13.0 mil

除10.0 mil

套除18.0 mil

套除17.0 mil

LAYER 2

凈空

LAYER 4 (若為2+2+2,此P A TTERN 可不作。) pad 30 mil

设计注意事项:

(I) 若面铜厚为1.0 oz(无电镀铜),则蚀刻补偿为1.25 mil ,而最小套除(最右侧)要改为8.5 mil ,往左依次加1.0 mil 。

(II) 面铜厚为1.5 mil(含电镀铜),则蚀刻补偿约为1.5 mil ,而最小套除(最右侧)要改为8.25 mil ,往左依次加1.0 mil 。

(III) mask 的面铜厚为H oz ,则蚀刻补偿为0.75 mil ,而mask 设计改为7.25 mil 。

(IV) 若依厂内最大纵横比算出的孔径大于8.0 mil (L1至L3厚度> 6.4 mil),则Test Key 的孔径同板内,其它patterns 依理论作设计。

D. STEP VIA (TELESCOPIC VIA) TEST KEY

需依Staggered via 做法将之拆分为两段分别进行测试. 具体方法同Stagered via

E. STACKED VIA TEST KEY

需依Staggered via 做法将之拆分为两段分别进行测试. 具体方法同Stagered via

10 VIA CHAIN TEST PATTERN 设计

测试Microvia 的连通性, 主要测试雷射盲孔品质以及电镀导通性. 以电测或信赖性试验检验.量测两端的TEST PAD 即可得知其导通性能.

A. PLUS I VIA CHAIN

L1

TEST PAD

L2

设计方式:

1. Capture PAD & Target PAD 尺寸以 雷射孔径 + (基铜1/3oz) ring 3.75mil (基铜1/2oz) ring 4.25mil (基铜1oz) ring 4.5mil

2. Test PAD 尺寸为30mil ,trace 为4mil ,

3. PAD 和PAD pitch 为50mil B. STAGGERED VIA CHAIN

30x80 mils

TOP VIEW (5X20)* The sizes of unmarked pads and holes are the same as those on PCB. (L2-L3) 1 (Size: 7 mils)

设计方式:

,用以量测L1-L2、L2-L3的电镀品质。

可,详见图。 m X 3.81 mm) . SKIP VIA CHAIN

IA CHAIN 设计, L2层以凈空设计即可. 径大小即可。

等。 m X 3.81 mm)

. STEP(TELESCOPIC) VIA CHAIN

在L2层添加独立PAD. 以便制作L1-2和L2-3两种不同孔径, 测

1. 设计2组

2. 样式同PLUS 1的Via chain ,孔径同板内孔径大小即

3. 外层须用蚀刻标示测式层别,如L1-L2、L2-L3、L1-L3……等。

4. 两面添加,位置同PLUS 1.

5. size: 0.690” X 0.150”(17.6 m

C 设计方式同PLUS I V 1. 设计2组,用以量测L1-L3的电镀品质。

2. 样式同PLUS 1的Via chain ,孔径同板内孔

3. 外层须用蚀刻标示测式层别,如L1-L2、L2-L3、L1-L3……

4. 两面添加,位置同PLUS 1.

5. size: 0.690” X 0.150”(17.6 m

D 设计样式同SKIP VIA CHAIN, 但试其导通性.

LAYER 1LAYER 3

LAYER 2TOP VIEW

Test-Pad (30x80 mils)

30 mils

30 mils

3 (Size: 7mils)

1 (Size: 7 mils)

* The sizes of unmarked pads and holes are the same as those on PCB.

(L1-L2-L3) 35 columns

设计方式:

,用以量测L1-L3的电镀品质。

径大小即可。

等。

m X 3.81 mm)

E. STACKED VIA CHAIN

COPIC) VIA CHAIN, 但L1-2和L2-3两种孔径大小相同.LAYER 1 LAYER 2 LAYER 3

1. 设计2组

2. 样式同PLUS 1的Via chain,孔径同板内孔

3. 外层须用蚀刻标示测式层别,如L1-L2、L2-L3、L1-L3……

4. 两面添加,位置同PLUS 1.

5. size: 0.690” X0.150”(17.6 m

设计样式同STEP(TELES

TOP VIEW (10X35)

30 mils

Test-Pad (30x80 mils)

30 mils

Trace on Layers 3

(Size: 7mils)

(Size: 7mils)

* The sizes of unmarked pads and holes are the same as those on PCB.

(L1-L2-L3)

35 columns

设计方式:

,用以量测L1-L3的电镀品质。

径大小即可。

等。 m X 3.81 mm) 7.3.11 切片COUPON PATTERN 设计

镀后切片用,详见如下图说明。

孔型中的最小的孔径;PAD 到的切片孔位置须错开。 . PLUS I 切片孔设计 SECTION VIEW

LAYER 1

LAYER 2

LAYER

3

1. 设计2组

2. 样式同PLUS 1的Via chain ,孔径同板内孔

3. 外层须用蚀刻标示测式层别,如L1-L2、L2-L3、L1-L3……

4. 两面添加,位置同PLUS 1.

5. size: 0.690” X 0.150”(17.6 m

(1) 须依板内孔结构加设切片孔,供电(2) 雷射孔切片孔各层的PAD 固定为40 MIL ;孔径大小同板内同结构的PAD 间PITCH 为100 MIL 。

(3) COMP SIDE 和SOLD SIDE

A

PITCH :100 MIL

LAYER 1

LAYER 2

. STAGGERED VIA 切片孔设计

二组,位置错开。

. STACKED & STEP(TELESCOPIC) VIA 切片孔 . SKIP VIA 切片图

B 同PLUS 1,但设L1-L2及L2-L3C

PITCH :100 MIL

LAYER 1 LAYER 2

LAYER 3

D PITCH :100 MIL LAYER 1

LAYER 2

LAYER 3

HDI制作工艺

HDI制作工艺 导读:二阶盲孔制板在我司从实验至今,已一年有余,作为一种新工艺,从HDI的发展趋势来看,将会继续向高密度互连发展。而且二阶盲孔制板过程繁杂,多次往返内、外层。随着该类板市场前景越来越好,我部在样品制作及设备引入方面都做了一些准备工作,我们将从样板制作方面归纳一些经验,希望在此与大家互相交流,以做进一步提高,希望在批量推广过程中能起到借鉴作用。 二阶盲孔比例分析统计该类定单的产品结构(如附图),可看出Staggered via的二阶盲孔即将成为主流产品。二阶盲孔的分类二阶盲孔常用材料 镭射的开窗形式 制作流程设计 Staggered via 单次盲孔制作流程同一阶盲孔采用X-ray + 板边孔+ Conformal Mask+CO2(UV)的钻孔工艺优点:工艺成熟、通孔与盲孔配套好缺点:孔易鼓形 采用X-ray + Large window+CO2(UV)的钻孔工艺优点:对位好,孔形好,简化流程。降低电镀难度缺点:增加X-ray的产能,镭射要求高、不适合Pad size小的板采用 X-ray+Conformal mask工艺优点:对位好,提高与Capture Pad的对位缺点:孔型控制难采用UV开窗

+CO2的钻孔工艺优点:实现微小孔化,避免漏开窗、孔径均一缺点:产能低采用UV 直接钻孔优点:微小孔化,避免漏开窗,刮内层靶标,与Target Pad 对位极好、孔径均一缺点:产能极低,易伤底铜 Staggered via按照工艺的优缺点选择方法孔径D:当D≤ 2mil时只能选择UV直接钻孔当2 <> 当D>4mil时采用Conformal Mask或Large window工艺锡圈:如果锡圈小于 4mil时最好用X-ray+Conformal mask工艺 Stack via (Telescopicvia) 采用UV+CO2的钻孔工艺适用于RCC材料采用Conformal Mask+CO2+UV+CO2的钻孔工艺适用于FR4材料及外层表铜为镀铜的板 Skip via(可以融合到Staggered via或Stack via的设计中)制作流程1(以含IVH八层板,负片流程为例) 适用二阶盲孔范围:交错盲孔和叠加盲孔中的plating filling 的制板生产控制重点:镭射钻孔:正常的开窗+CO2的钻孔电镀:采用正常的直流电镀或填平电镀线制作 制作流程2(以含IVH八层板,负片流程为例) 适用二阶盲孔范围:常规的Stacked via的制板生产控制重点:镭射钻孔:1、镭射钻孔的流程指定2、不同孔径的钻孔参数及FA电镀:采用三合一(沉铜两次)+脉冲电

HDI板生产流程(华神)

江苏华神电子有限公司

Hua Xin Jiangsu Huashen Electronics Co., Ltd.

PCB(2+4+2)-生产流程简介

编制:吴林旺 2016年6月13日

目录

一:2+4+2叠构流程图例 二:排版设计 三:生产流程简介

一:2+4+2叠构流程图例

一般二阶HDI板有三种设计方式,如下图为以八层板为例的叠层设计。从成本上来说, 第一种最低、第二种次之、第三种最高(不建议用第三种设计)。 一 二 三

以以上第二种作生产流程介绍: 1、内层芯板制作:开料---内层(L4&L5层)线路---AOI 2、IVH制作:压合---钻埋孔---电镀---L3&L6层线路---AOI 3、SBU1制作:树脂塞孔---压合---激光钻孔---填孔电镀---L2&L7层线路---AOI 4、外层制作:压合---激光钻孔---钻通孔---填孔电镀---外层线路---AOI---防焊---印选化油墨 ---化金---字符---成型---电测---FQC---OSP---FQA抽检---包装

二:排版设计

排版设计

三:生产流程简介--开料

开料:将供应商提供的大料切切割成我们的working PNL。

一)覆铜箔层压板(Copper Clad Laminate),简称覆铜板(芯板)

1)根据客户铜厚要求和板厚要求,选择对应的芯板。Toz&Hoz 2)现手机板设计越来越密集,线路越来越细,鉴于不会走高电流,所建议采用Hoz薄铜,不 建议采用Hoz以上铜厚。

COPPER FOIL 铜箔

49” 37” (41”) (43”) 24.4” 24.4” 18.4” ( 20.4”)

Epoxy Glass 玻璃布 COPPER FOIL 铜箔

(21.4”)