算数逻辑单元

一、实验目的:

1、掌握简单运算器的数据传送通路

2、验证运算器的组合功能

二、实验原理:

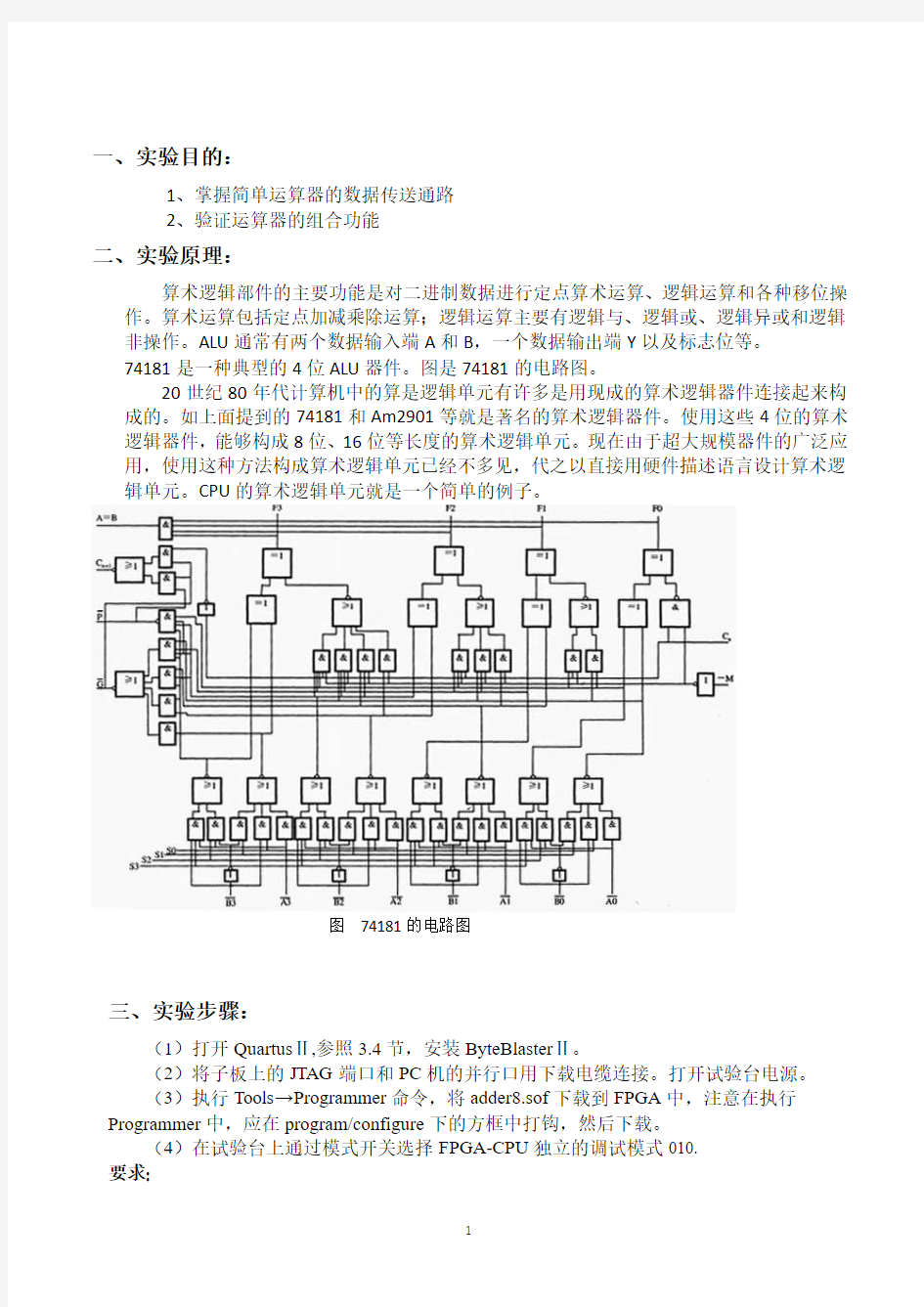

算术逻辑部件的主要功能是对二进制数据进行定点算术运算、逻辑运算和各种移位操作。算术运算包括定点加减乘除运算;逻辑运算主要有逻辑与、逻辑或、逻辑异或和逻辑非操作。ALU通常有两个数据输入端A和B,一个数据输出端Y以及标志位等。

74181是一种典型的4位ALU器件。图是74181的电路图。

20世纪80年代计算机中的算是逻辑单元有许多是用现成的算术逻辑器件连接起来构成的。如上面提到的74181和Am2901等就是著名的算术逻辑器件。使用这些4位的算术逻辑器件,能够构成8位、16位等长度的算术逻辑单元。现在由于超大规模器件的广泛应用,使用这种方法构成算术逻辑单元已经不多见,代之以直接用硬件描述语言设计算术逻辑单元。CPU的算术逻辑单元就是一个简单的例子。

图74181的电路图

三、实验步骤:

(1)打开QuartusⅡ,参照3.4节,安装ByteBlasterⅡ。

(2)将子板上的JTAG端口和PC机的并行口用下载电缆连接。打开试验台电源。

(3)执行Tools→Programmer命令,将adder8.sof下载到FPGA中,注意在执行Programmer中,应在program/configure下的方框中打钩,然后下载。

(4)在试验台上通过模式开关选择FPGA-CPU独立的调试模式010.

要求:

1、实验设计目标

设计一个16位算术逻辑单元,满足以下要求。

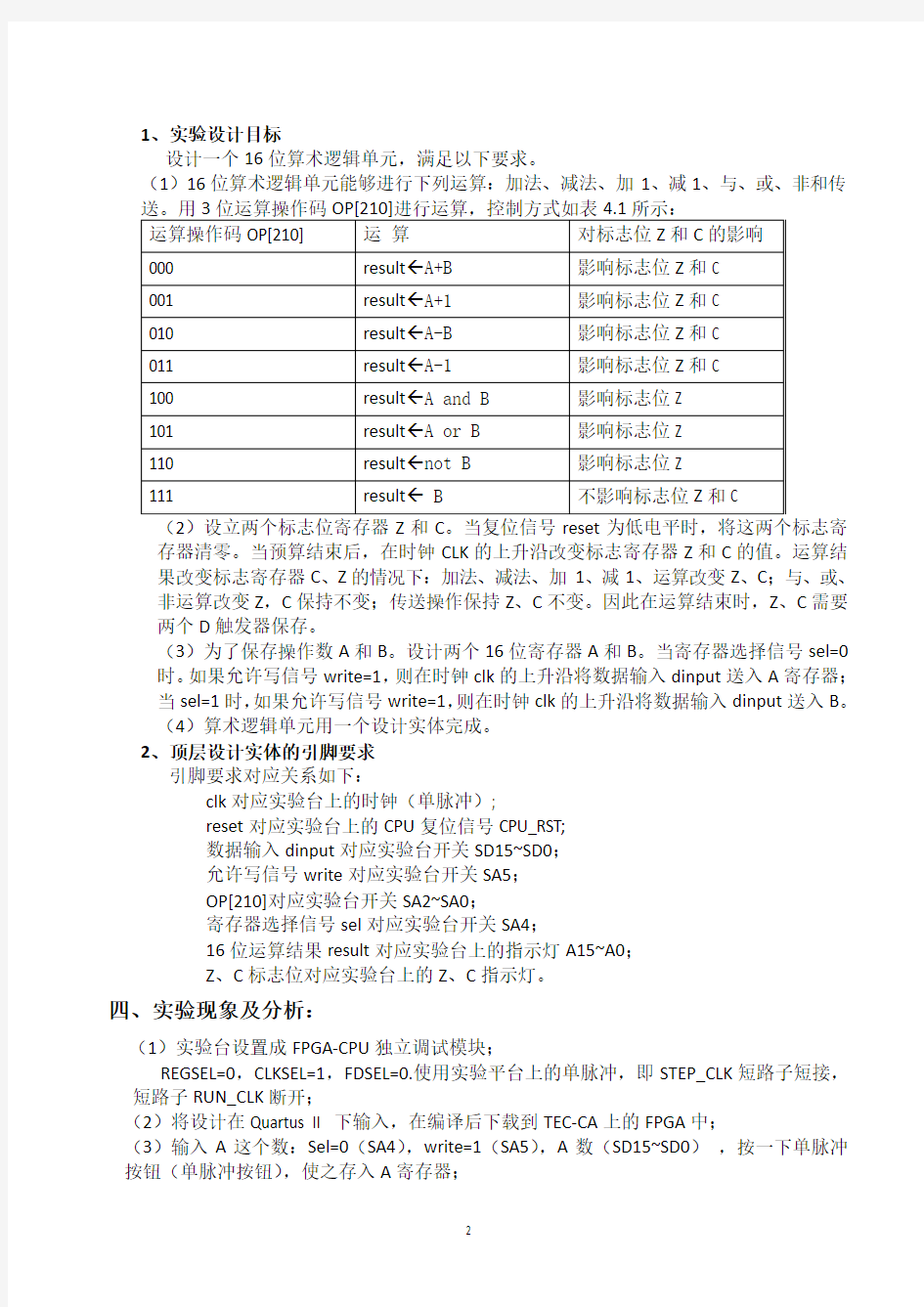

(1)16位算术逻辑单元能够进行下列运算:加法、减法、加1、减1、与、或、非和传

(2)设立两个标志位寄存器Z和C。当复位信号reset为低电平时,将这两个标志寄存器清零。当预算结束后,在时钟CLK的上升沿改变标志寄存器Z和C的值。运算结果改变标志寄存器C、Z的情况下:加法、减法、加1、减1、运算改变Z、C;与、或、非运算改变Z,C保持不变;传送操作保持Z、C不变。因此在运算结束时,Z、C需要两个D触发器保存。

(3)为了保存操作数A和B。设计两个16位寄存器A和B。当寄存器选择信号sel=0时。如果允许写信号write=1,则在时钟clk的上升沿将数据输入dinput送入A寄存器;

当sel=1时,如果允许写信号write=1,则在时钟clk的上升沿将数据输入dinput送入B。

(4)算术逻辑单元用一个设计实体完成。

2、顶层设计实体的引脚要求

引脚要求对应关系如下:

clk对应实验台上的时钟(单脉冲);

reset对应实验台上的CPU复位信号CPU_RST;

数据输入dinput对应实验台开关SD15~SD0;

允许写信号write对应实验台开关SA5;

OP[210]对应实验台开关SA2~SA0;

寄存器选择信号sel对应实验台开关SA4;

16位运算结果result对应实验台上的指示灯A15~A0;

Z、C标志位对应实验台上的Z、C指示灯。

四、实验现象及分析:

(1)实验台设置成FPGA-CPU独立调试模块;

REGSEL=0,CLKSEL=1,FDSEL=0.使用实验平台上的单脉冲,即STEP_CLK短路子短接,短路子RUN_CLK断开;

(2)将设计在Quartus II 下输入,在编译后下载到TEC-CA上的FPGA中;

(3)输入A这个数:Sel=0(SA4),write=1(SA5),A数(SD15~SD0),按一下单脉冲按钮(单脉冲按钮),使之存入A寄存器;

(4)输入B这个数:Sel=1(SA4),write=1(SA5),B数(SD15~SD0),按一下单脉冲按钮(单脉冲按钮),使之存入B寄存器;

(5)输入功能码OP[210](SA2~SA0),按一下单脉冲按钮(单脉冲按钮);

(6)观察16位运算结果result(A15~A0)及Z、C指示灯;

(7)重复实验步骤(3)--(6)对以下4组数据进行表4.1的8种运算,把运算结果及标志位填写在表中:

A、对第一组数据进行8种运算,A为0xAAAA,B为0x5555;

B、对第一组数据进行8种运算,A为0xFFFF,B为0x0000;

C、对第一组数据进行8种运算,A为0x0000,B为0xFFFF;

D、对第一组数据进行8种运算,A为0x8950,B为0x9863;

五、实验过程中遇到问题及解决方法:

设立两个标志位寄存器Z和C。当复位信号reset为低电平时,将这两个标志寄存器清零。当预算结束后,在时钟CLK的上升沿改变标志寄存器Z和C的值。运算结果改变标志寄存器C、Z的情况下:加法、减法、加1、减1、运算改变Z、C;与、或、非运算改变Z,C 保持不变;传送操作保持Z、C不变。

六、实验源码:(加注释)

--算数逻辑单元

libraryieee;

use ieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entity ALU is

port(

reset,clk : in std_logic;--reset复位信号,当reset为低电平时,两个标志寄存器清零。clk为时钟信号,clk为高电平,改变Z,C

OP: in std_logic_vector(2 downto 0);--运算操作码

sel: in std_logic;--选择信号,sel=0,若为写信号,clk上升则存入A寄存器,若sel=1则存入B寄存器

write: in std_logic;--写信号

C,Z: out std_logic;--Z,C为标志位

Dinput: in std_logic_vector(15 downto 0);--输入将写入的数据通过它存入A 寄存器或B寄存器

result: out std_logic_vector(15 downto 0)--输出结果

);

end ALU;

architecturebehav of alu is

componentreg is

port

(

clr: in std_logic;--寄存器复位信号

D: in std_logic_vector(15 downto 0);--寄存器输入信号clock: in std_logic;--时钟信号

write: in std_logic;--写信号

sel: in std_logic;--选择信号

Q: out std_logic_vector(15 downto 0)

);

end component;

signalz_tmp :std_logic;

signal A,B :std_logic_vector(15 downto 0);

signalresult_t: std_logic_vector(16 downto 0);

begin

A_reg: reg port map--A寄存器

(clr => reset,--对应ALU的复位信号

D =>Dinput,对应ALU的输入信号

clock =>clk, --对应ALU的时钟信号

write => write,

sel => (not sel), --sel=0则表示选择A寄存器

Q => A

);

B_reg: reg port map--B寄存器

(clr => reset,

D =>Dinput,

clock =>clk,

write => write,--sel=1则表示选择B寄存器

sel =>sel,

Q => B

);

alu_proc:process(OP,A,B)

begin

case OP is

when "000" =>

result_t<= ('0' & A) + ('0' & B);--A+B

when "001" =>

result_t<= ('0' & A) + '1';--A+1

when "010" =>

result_t<= ('0' & A) - ('0' & B);--A—B

when "011" =>

result_t<= ('0' & A) - '1';--A-1

when "100" =>

result_t<= ('0' & A) and ('0' & B);--与

when "101" =>

result_t<= ('0' & A) or ('0' & B);--或

when "110" =>

result_t<= not ('0' & B);--非

when "111" =>

result_t<= ('0' & B);--传递

end case;

end process;

result <= result_t(15 downto 0);

z_tmp<= (not result_t(15)) and (not result_t(14)) and (not result_t(13)) and (not result_t(12)) and

(not result_t(11)) and (not result_t(10)) and

(not result_t(9)) and (not result_t(8)) and

(not result_t(7)) and (not result_t(6)) and

(not result_t(5)) and (not result_t(4)) and

(not result_t(3)) and (not result_t(2)) and

(not result_t(1)) and (not result_t(0));

c_proc: Process(reset,clk,result_t,OP)

begin

if reset = '0' then--若按下复位信号则寄存器C为0

C <= '0';

elsifclk'event and clk = '1' then--若clk为上升

if OP(2) = '0' then

C <= result_t(16);

end if;

end if;

end process;

z_proc: process(reset,clk,z_tmp,OP)

begin

if reset = '0' then

Z <= '0';

elsifclk'event and clk = '1' then

if OP /= "111" then

Z <= z_tmp;

end if;

end if;

end process;

endbehav;

--16位寄存器

libraryieee;

use ieee.std_logic_1164.all;

entityreg is

port

(

clr: in std_logic;

D: in std_logic_vector(15 downto 0);

clock: in std_logic;

write: in std_logic;

sel: in std_logic;

Q: out std_logic_vector(15 downto 0) );

endreg;

architecturebehav of reg is

begin

process(clr,clock)

begin

ifclr = '0' then

Q <= x"0000";

elsif (clock'event and clock = '1') then

ifsel = '1' and write = '1' then

Q <= D;

end if;

end if;

end process;

endbehav;

燕山大学 EDA课程设计报告书题目:算术逻辑逻辑单元ALU 姓名: 班级: 学号: 成绩:

一、设计题目及要求 题目名称:算术运算单元ALU 要求: 1.进行两个四位二进制数的运算; 2.算术运算:A+B, A-B, A×B; 3.逻辑运算:A and B, A or B, A not, A xor B; 4. 用数码管显示算术运算结果,以LED指示灯显示逻辑运算结果。 二、设计过程及内容 1.整体设计思路 (1)根据设计要求将题目划分为五个模块。包括两个逻辑运算模块,两个算术运算模块,和一个控制模块。其中逻辑运算模块为A and B和A or B,A not和A xor B;算术模块为A±B,A×B。 (2)因为需要进行四位二进制数的运算,因此用A3,A2,A1,A0表示四位二进制数A,用B3,B2,B1,B0表示四位二进制数B,用C4,C3,C2,C1表示四位二进制数C。其中A,B为输入,C为输出。

2.分模块设计 (1)A+B和A-B模块(李佳乐负责) A+B可以直接通过74283 两个四位二进制数加法器实现。A-B可以看作A+(-B),即A加B的补码来实现。同时再设计一个转换控制端M。M=0时实现A+B,M=1时实现A-B。最后再设计一个总的控制端K1,K1=1时模块正常工作,K1=0时不工作。做加法时,C0为进位输出,C0输出1表示有进位,做减法时,C0为借位输出,C0输出1表示有借位。通过74283五位输出,进入译码器将五位变成八位输出,在通过数码管显示。 A+B,A-B总原理图如下:

A+B,A-B分原理图如下:

译码器原理图如下: 扫描电路原理图如下:

EDA技术与应用 实验报告 实验名称:ALU(算术逻辑运算单元)的设计 姓名: 学号: 班级:通信 时间:2013 南京理工大学紫金学院电光系

一、实验目的 1、学习包集和元件例化语句的使用。 2、学习ALU电路的设计。 二、实验原理 1、ALU原理 ALU的电路原理图如图1 所示,主要由算术运算单元、逻辑单元、选择单元构成。 图1 ALU功能表如表1 所示。 表1 2、元件、包集 在结构体的层次化设计中,采用结构描述方法就是通过调用库中的元件或者已经设计好的模块来完成相应的设计。在这种结构体中,功能描述就像网表一样来表示模块和模块之间的互联。如ALU 是由算术单元、逻辑单元、多路复用器互相连接而构成。而以上三个模块是由相应的VHDL 代码产生的,在VHDL 输入方式下,如果要将三个模块连接起来,就要用到元件例化语句。

元件例化语句分为元件声明和元件例化。 (1)元件声明 在VHDL 代码中要引入设计好的模块,首先要在结构体的说明部分对要引入的模块进行说明。然后使用元件例化语句引入模块。 元件声明语句格式: component 引入的元件(或模块)名 port( 端口说明); end component; 注意:元件说明语句要放在“architecture”和“begin”之间。 (2)元件例化语句 为将引入的元件正确地嵌入到高一层的结构体描述中,就必须将被引用的元件端口信号与结构体相应端口信号正确地连接起来,元件例化语句可以实现该功能。 元件例化语句格式: 标号名:元件名(模块名) port map(端口映射); 标号名是元件例化语句的唯一标识,且结构体中的标识必须是唯一的;端口映射分为:位置映射、名称映射。 位置映射指 port map 中实际信号的书写顺序与component 中端口说明中的信号书写顺序一致,位置映射对书写顺序要求很严格,不能颠倒;名称映射指port map 中将引用的元件的端口信号名称赋予结构体中要使用元件的各个信号,名称映射的书写顺序要求不严格,顺序可以颠倒。 (3)包集 在实体及结构体中定义的对象、数据类型,对另外代码的实体是不能使用的。但是在同一工程的不同VHDL 文件中,有些对象、数据类型、子程序等常常被重复使用。为方便VHDL 代码的编写,简化电路设计,故引入包集。包集也称为程序包。 包集主要由两部分组成:程序包说明和程序包体。其中,程序包体是可选的,一般程序包说明列出所有项的名称,而程序包体给出各项的细节。 程序包说明中包含的内容很多,只要是通用的全局量,都可以在程序包中加以说明。主要内容如下: 对象(常量、变量、信号)的数据类型说明。 对象(常量、变量、信号)子类型的数值范围说明。 函数与过程说明。 元件语句说明。 程序包说明的书写格式如下: package 程序包名 is 说明语句; end 程序包名; 程序包名:设计者自定义便于记忆的标识符。说明语句:包括各种类型的说明语句。

西华大学数学与计算机学院实验报告 课程名称:计算机组成原理年级:2011级实验成绩: 指导教师:祝昌宇姓名:蒋俊 实验名称:算术逻辑运算单元实验学号:312011*********实验日期:2013-12-15 一、目的 1. 掌握简单运算器的数据传输方式 2. 掌握74LS181的功能和应用 二、实验原理 (1)ALU单元实验构成 1、结构试验箱上的算术逻辑运算单元上的运算器是由运算器由2片74LS181构成8字长的ALU 单元。 2、2片74LS373作为2个数据锁存器(DR1、DR2),8芯插座ALU-OUT作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。 3、运算器的数据输出由一片74LS244(输出缓冲器)来控制,8芯插座ALU-OUT作为数据输出端,可通过短8芯扁平电缆把数据输出端连接到数据总线上。 (2)ALU单元的工作原理 数据输入锁存器DR1的EDR1为低电平,并且D1CK有上升沿时,把来自数据总线上的数据打入锁存器DR1。同样,使EDR2为低电平,并且D2CK有上升沿时,把来自数据总线上的数据打入锁存器DR2。 算术逻辑运算单元的核心是由2片74LS181构成,它可以进行2个8位二进制数的算术逻辑运算,74LS181的各种工作方式可通过设置其控制信号来实现(S0、S1、S2、S3、M、CN)。当实验者正确设置了74LS181的各个控制信号,74LS181会运算数据锁存器DR1、DR2内的数据。由于DR1、DR2已经把数据锁存,只要74LS181的控制信号不变,那么74LS181的输出数据也不会发生改变。 输出缓冲器采用74LS244,当控制信号ALU-O为低电平时,74LS244导通,把74LS181的运算结果输出到数据总线;ALU-O为高电平时,74LS244的输出为高阻。

实验二算术逻辑运算实验 一、实验目的 (1)了解运算器芯片(74LS181)的逻辑功能。 (2)掌握运算器数据的载入、读取方法,掌握运算器工作模式的设置。 (3)观察在不同工作模式下数据运算的规则。 二、实验原理 1.运算器芯片(74LS181)的逻辑功能 74LS181是一种数据宽度为4个二进制位的多功能运算器芯片,封装在壳中,封装形式如图2-3所示。 5V A1 B1 A2 B2 A3 B3 Cn4 F3 BO A0 S3 S2 S1 S0 Cn M F0 F1 F2 GND 图 2-3 74LS181封装图 主要引脚有: (1)A0—A3:第一组操作数据输入端。 (2)B0—B3:第二组操作数据输入端。 (3)F0—F3:操作结果数据输入端。 (4)F0—F3:操作功能控制端。 (5):低端进位接收端。

(6):高端进位输出端。 (7)M:算数/逻辑功能控制端。 芯片的逻辑功能见表2-1.从表中可以看到当控制端S0—S3为1001、M为0、 为1时,操作结果数据输出端F0—F3上的数据等于第一组操作数据输入端A0—A3上的数据加第二组操作数据输入端B0—B3上的数据。当S0—S3、M、 上控制信号电平不同时,74LS181芯片完成不同功能的逻辑运算操作或算数运算操作。在加法运算操作时,、进位信号低电平有效;减法运算操作时,、 借位信号高电平有效;而逻辑运算操作时,、进位信号无意义。 2.运算器实验逻辑电路 试验台运算器实验逻辑电路中,两片74LS181芯片构成一个长度为8位的运算器,两片74LS181分别作为第一操作数据寄存器和第二操作数据寄存器,一片74LS254作为操作结果数据输出缓冲器,逻辑结构如图2-4所示。途中算术运算操作时的进位Cy判别进位指示电路;判零Zi和零标志电路指示电路,将在实验三中使用。 第一操作数据由B-DA1(BUS TO DATA1)负脉冲控制信号送入名为DA1的第一操作数据寄存器,第二操作数据由B-DA2(BUS TO DATA2)负脉冲控制信号送入名为DA2的第二操作数据寄存器。74LS181的运算结果数据由(ALU TO BUS)低电平控制信号送总线。S0—S3、M芯片模式控制信号同时与两片74LS181的S0—S3、M端相连,保证二者以同一工作模式工作。实验电路的低端进位接收端Ci与低4位74LS181的相连,用于接收外部进位信号。低4为74LS181的与高4位74LS181的上相连,实现高、低4位之间进位信号的传递。高4位之间进位信号的传递。高4位74LS181的送进位Cy判别和进位指示电路。 表2-1 74LS181 芯片逻辑功能表

计算机原理与设计 实验报告 实验一算术逻辑单元ALU 姓名: XXX 学号: 2013551728 班级: 13级软件工程2班 实验日期: 2014年 10 月22 日

一.实验目的 1.理解算术逻辑单元ALU的工作原理。 2.掌握算术逻辑单元ALU的设计方法。 3.验证32位算术逻辑单元ALU的加、减、与、移位功能。 4.按给定数据,完成几种指定的算术和逻辑运算。 二.实验内容 算术逻辑单元ALU的设计如图1-1所示。其中运算器addsub32能实现32位的加减运算。参加运算的两个32位数据分别为A[31..0]和B[31..0],运算模式由aluc[3..0]的16种组合决定,而aluc[3..0]的值由4位2进制计数器LPM_COUNTER产生,计数时钟是Sclk(图1-1);r[31..0]为输出结果,Z为运算后的零标志位。ALU功能如表1-1所示。 表1-1 ALU的运算功能 注1、* 表示每一位都移至下一更高有效位, “+”是逻辑或,“加”是算术加

三.实验步骤 (1)设计ALU元件 ALU元件设计代码: module alu (a,b,aluc,r,z); input [31:0] a,b; input [3:0] aluc; output [31:0] r; output z; assign r = cal(a,b,aluc); assign z = ~|r; function [31:0] cal; input [31:0] a,b; input [3:0] aluc; casex (aluc) 4'bx000: cal=a+b; 4'bx100: cal=a-b; 4'bx001: cal=a&b; 4'bx101: cal=a|b; 4'bx010: cal=a^b; 4'bx110: cal={b[15:0],16'h0}; 4'bx011: cal=b<

实验报告 实验项目:算术逻辑运算实验(试验一) 课程名称:计算机组成原理 姓名:学号同组姓名:学号:实验位置(机号): 实验日期 实验1.掌握简单运算器的数据传送通路 目的2.验证运算器功能发生器(74LS181)的组合功能 3.验证带进为控制的算术运算器功能发生器(74LS181)的功能 4.按指定的数据完成几种制定的算术运算 5.验证移位控制的组合功能 实验YY-Z02计算机组成原理教学实验系统一台,排线若干。设备 实验 内容1.实验原理 (算 运算器实验原理图 法、 程 T4______ ALU-B 序、

_____ _____ 进位CyCn 步骤 299-B 判零_____ M 74LS2 电路CyNCn 和方 S0 99 ALU S1 法) (74LS181) S2 S3 _____I/O-RINPUT Ai =“0”B-DA1DA1 (74LS273)DA2

(74LS273)B-DA2 实验中所用的运算器数据通路图如图1-1所示,算术逻辑实验接线图如图1-2所示。图中所示的是由两片段74LS181芯片以并/串形式构成的8位字长的运算器。右方为低压4位运算芯片,左方为高4位运算芯片。低位芯片的进位输出端C(n+4)与高芯片的进位输入端CN相连,高位芯片的进位输出引至外部。两个芯片的控制端S0~S3和M各自相连。 2.实验步骤 1)算数逻辑运算 i.输入单元置数一 ii.设置I/O-R# = 0 iii.ALU-B# =1 iv.B-DA1 _| ̄|_将输入单元的输入数据存入DA1中 v.输入单元置数据二 vi.B-DA2 _| ̄|_将数据存入DA2中 vii.设置S 3 -------S 0、M、Cn根据要求按照定义操作设置完成运算viii. ix. x.I/O-R# = 1 ALU-B = 0运算结果送总线 IO-W ̄|_| ̄总线数据送显示单元显示 数据1.算数逻辑运算

大连理工大学城市学院 FPGA实验报告 实验内容:8位ALU 系别班级:电子1004班 学号: 姓名: 日期:2013.4.14

一.设计概述: 一种基于可编程逻辑器件FPGA和硬件描述语言的8位的ALU的设计方法。该ALU采用层次设计方法,有寄存器模块、控制模块和显示模块组成,能实现8位无符号数的取值、加减和4种逻辑运算(与、或、异或、同或)。该ALU在QuartusII软件环境下进行功能仿真,通过DE2验证。 二.设计功能: 1、该处理器的数据宽度为8bit,可以实现算术加法、减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。 2、用选择端opcode [2:0] 选择8种运算,2个操作数分别是a_r [7:0]和b_r[7:0],运算结果是alu_out[7:0];并定义选择如下。 3、使用DE2板上的3个拨码开关设置当前ALU的运算功能,再由8个拨码开关给定数据A和数据B,由一个按键key手动提供脉冲。 三.设计方案: 本设计共有5个模块。 1)脉冲输出器(key手动脉冲),计数依次产生4个脉冲到各个部件,第一个脉冲启动信号。 2)寄存器A,第二个脉冲来时锁存数据A,并在数码管上显示。 3)寄存器B,第三个脉冲来时锁存数据B,并在数码管上显示。 4)8位ALU,第四个脉冲来时进行运算,并锁存结果alu_out。 5)结果显示器,将结果显示通过DE2上的数码管显示。 四.程序分析: 主程序模块: module alu8(clk,clk_r,rst,a,b,alu_out,opcode,sw_ab,HEX1, HEX0, HEX7, HEX6, HEX5, HEX4); input clk,rst,clk_r; input [7:0] sw_ab; input [2:0] opcode; output [6:0] HEX1, HEX0, HEX7, HEX6, HEX5, HEX4;

实验二算术逻辑单元(ALU)的设计与实现 实验目的 1.认识算术逻辑单元的功能及意义 2.掌握算术逻辑单元的结构与实现 3.进一步熟练Modelsim、Vivado软件和Verilog硬件描述语言的使用 4.理解Digilent N4 DDR FPGA开发板上数码管显示原理 实验原理 1.ALU 算术逻辑单元(Arithmetic/Logic Unit , ALU)是现代计算机的核心部件之一。其内部由算术和逻辑操作部件组合而成,可以实现整数加、减等算术运算和与、或等逻辑运算。 一个典型的算术逻辑单元由两路N位输入、一路N位输出、一组功能选择信号和一些标志位(flag)组成。两路N位输入数据作为参与运算的两个操作数,输入到ALU中,通过改变功能选择信号,控制ALU对两操作数进行不同的算术或逻辑运算操作,并将N位的结果输出,与结果一同输出的还有运算产生的标志位,例如运算结果为零的标记信号Z(zero)与运算结果溢出的标记信号O(over)、进位标志C(CY)、符号位S(SF)等,如图2-1所示。 图2- 1ALU模块示意图 在本次实验中,我们把输入和输出的数据长度定为4位,数据输入命名为A、B,数据输出为F,功能控制信号输入为opcode,进位输入为C n,只产生结果为零的zero标志位。功能控制信号opcode的定义如表2-1所示。例如:opcode=0001,运算器实现加法运算。

2.数码管显示 关于N4 DDR开发板上数码管的显示原理,参见前面的实验准备部分内容。实验内容 1.基础实验。用实验调试软件验证ALU的功能,并操作分析、记录结果。 图2- 2 ALU虚拟实验示意图 (1)运算功能和控制信号 ①输入输出对于的开关指示灯分配如下: 输入信号A:SW(4-7) B:SW(3-0) Cn:SW8 opcode:SW(12-9) 输出信号F:LD(12-15) 标志位S :LD(3) Z LD(2) O: LD(1) C: LD(0) ②各种运算对应的控制信号及功能,如下表。

多功能算术逻辑单元(ALU)设计 安徽理工大学 计算机组成原理课程设计说明书 题目: 多功能算术逻辑单元设计 院系:计算机科学与工程学院专业班级:信息08-1班学号:20XX303007 学生姓名:指导教师: 20XX年 12 月 8 日 安徽理工大学课程设计任务书 计算机科学与工程学院计算机硬件教研室 学号 20XX303007 学生姓名专业信08-1 设计题目多功能运算逻辑单元设计设计技术参数系统平台:Windows xp 开发工具: QuartusII 设计要求工作量 1)实现5条及以上的指令系统的硬连线的控制器的设计; 2)需要增加的指令自己加入,完成设计、测试过程,并给出测试结果。课程设计报告要求不少于3000字。源程序要求不少于300行 11月16日- 11月22日查找相关资料 11月23日- 11月29日构建框架 11月30日-12月6日设计算法 12月6日-12月12日检查改错 12月12日-12月16日撰写课程设计报告工作计划参考资料 [1] 白中英.计算机组成原理.科学出版社.20XX [2] 姜

咏江.基于QuartusII的计算机核心设计.清华大学出版社.20XX [3] 林涛.数字电子技术基础.清华大学出版社.20XX 指导教师签字教研室主任签字 20XX 年 12月8日 安徽理工大学课程设计成绩评定表 学生姓名:学号:20XX303007 专业班级:信08-1 课程设计题目:多功能算术逻辑单元设计指导教师评语:成绩:指导教师: 年月日 目录 1、简要介绍 ................................................ ............. 1 2、详细设计 ................................................ ............. 1 使用QuartusII 设计逻辑电路................... 1 3、总结 ................................................ .. (7) 图1 c.验证4位ALU是否正确,先进行编译,编译成功后进行仿真验证。可在主菜单中选择processing,然后选择Simulator Tool,单击OPEN按钮建立仿真文件。在仿真波

实 验 报 告 实 验 人: 赵** 学 号: 09***** 日 期: 2010-10-08 院(系): 专业(班级): 09 实验题目: 四位ALU 算术逻辑单元设计实验 一. 实验目的 1. 了解ALU (算术逻辑单元)的功能和使用方法; 2. 认识和掌握超前(并行)进位的设计方法; 3. 认识和掌握ALU 的逻辑电路组成; 4. 认识和掌握ALU 的设计方法。 二. 实验原理 从结构原理图上可推知,本实验中的ALU 运算逻辑单元由4个一位的ALU 运算逻辑单元所组成。每一位的ALU 电路由全加器和函数发生器所组成,如下图(1)所示。事实上,ALU 的设计是在全加器的基础上,对全加器功能的扩展来实现符合要求的多种算术/逻辑运算的功能。为了实验多种功能的运算,An 、Bn 数据是不能直接与全加器相连接的,它们受到功能变量F3-F1的制约,因此,可由An 、Bn 数据和功能变量F3-F1组合成新的函数Xn 、Yn ,然后,再将Xn 、Yn 和下一位进位Cn-1通过全加器进行全加运算以实现所需的运算功能。ALU 中C0为最低位的进位输入端,C4 辑表达式(n=1、2、3、4)如下: Sn=Xn ⊕Yn ⊕Cn-1 Cn=XnYn+(Xn+Yn)Cn-1 令Pn=Xn+Yn , Gn=XnYn 则Cn=Gn+PnCn-1

实验要求进位位采用超前(先行、并行)进位实现。超前进位电路同时形成各位进位,因此实现快速进位,达到快速加法的目的。这种加法器称为超前进位加法器。 各超前(先行)进位位的形成根据表达式Cn=XnYn+(Xn+Yn)Cn-1来确定,其中n=1、2、3、4。后产生的进位与前进位有关,最终每个进位也只和Xn、Yn、C0有关,而Xn、Yn、又是An、Bn的函数,如: C1=G1+P1C0=X1Y1+(X1+Y1)C0 C2=G2+P2C1=X2Y2+(X2+Y2)X1Y1+(X2+Y2)(X1+Y1)CO 一些控制信号如F3-F1为功能控制信号,控制着4位ALU运算逻辑单元的八种功能操作:A4-A1和B4-B1为ALU的两组数据输入端;S4-S1为了4位ALU的4个输出端,S表示为S=SS43S2S1;C4为4位ALU的最高位进位输出端,依次还有C3、C2、C1。(考虑级联关系时,如有必要可增加级联控制端G)。 三. 实验内容 依照ALU的原理与逻辑结构原理图,用超前进位的方法设计能实现下面八种功能操作的4位ALU,并对电路进行封装。 要求: 输入信号:A4-A1、B4-B1、F3-F1、低位进位C0、(级联控制端G); 输出信号:S4-S1、进位C4。 4位ALU的八种功能如下:

实验五算术逻辑运算单元 一、目的: 1.能了算术逻辑运算单元(ALU)电路的设计原理。 2.能利用AHDL语言设计一个ALU电路。 3.能自行以CPLD数字电路实验系统验证所设计电路的正确性。 二、电路图:

三、实验仪配置图: 四、实验步骤与画面: 1.建立一个名为ALU_VerilogHDL.v的新文件,并在QuartusⅡ文字编辑器中,以VerilogHDL语言来设计程式,图U6-1为算术逻辑运算单元的VerilogHDL程式。 其中A、B为数据输入端口,s为功能控制端口,clk为时钟端口,d为数据输出端口。

2.存储、检查及编译。 3.创建元件符号。 4.创建波形文件,设定合适的端口信号,仿真元件的波形。

观察波形图可以看出当s端口选择不同功能时,芯片会对A、B 数据进行相应的操作。 5.请先设定s[2..]之值,以选择ALU之功能。再任意输入a[7..0] 及b[7..0]之二进制,观察记录其输出和d[7..0]并完成下表。 五、相关说明: 1.这个单元我们用AHDL语法来设计八位元ALU,您可以发现不仅较绘 图法简单许多,而且更容易为人了解,这就是硬体描述语言的优点。 2.在此要提醒您,由于二进位数的减法运算,是采用2’s补数的方 法,此方法是将减数取其2’s补数后,再与被减数相加,所得结果若有进位,则去掉进位后所得即为正式结果(为正值);若无进位,

则须再将结果取一次2’s补数后才是真正的结果(为负值)。例如:(00010001)-(00000101)=(00010001)+(11111011)=(00001100),进位为1所以去掉进位后,所得结果为+12。又如:(01011010)-(10000111)=(01011010)+(01111001)=(11010011),没有进位,所以要将结果再取一次2’s补数,正确的结果应为-00101101=-45。 六、自我练习 问题1:74181是一颗常用的四位元ALU,此ALU包含了所有的基本逻辑运算,并搭配各种算术运算组合而成,其功能模式如表 U6-1。我们可以将两颗74181予以并联而组成八位元ALU, 如图U6-3所示。请在ALTERA绘图环境下,绘制图U6-3,其 中的74181符号可自符号库(maxplus2\max21ib\mf)取得。 电路绘制完成后,再利用CPLD实验系统验证其功能是否正 确(接脚配置请参考图U6-4)。

湘 潭 大 学 实 验 报 告 课程名称 计算机原理与设计 实验名称 算术逻辑单元ALU设计实验 页数 专业 班级 同组者姓名 无 组别 学号 姓名 实验日期 一、 实验目的 a) 理解算术逻辑单元ALU 的工作原理。 b) 掌握算术逻辑单元ALU 的设计方法。 c) 验证32位算术逻辑单元ALU 的加、减、与、移位功能。 d) 按给定数据,完成几种指定的算术和逻辑运算。 二、 实验要求 1、做好实验预习,掌握运算器的数据传送通路和ALU 的功能特性,并熟悉本实验中所用的控制台开关的作用和使用方法。 2、写出实验报告,内容是: ①实验目的; ②按理论分析值填写好表1-2、表1-3,给出对应的仿真波形。 ③列表比较实验数据(2)的理论分析值与实验结果值;并对结果进行分析。实验结果与理论分析值比较,有没有不同?为什么? ④通过本实验,你对运算器ALU 有何认识,有什么心得体会? 三、 实验原理 算术逻辑单元ALU 的设计如图1-1所示。其中运算器addsub32能实现32位的加减运算。参加运算的两个32位数据分别为A[31..0]和B[31..0],运算模式由aluc[3..0]的16种组合决定,而aluc[3..0]的值由4位2进制计数器LPM_COUNTER 产生,计数时钟是Sclk (图1-1);r[31..0]为输出结果,Z 为运算后的零标志位。ALU 功能如表1-1所示。 表1-1 ALU 的运算功能 选择端aluc ALU 功能 3 2 1 0 * 0 0 0 B A R 加= * 0 0 1 B A R 与= * 0 1 0 B A R ⊕= * 1 0 0 B A F -= * 1 0 1 B A R +=

一:算术逻辑单元——(ALU) 1)比如二进制的00101010是十进制的42,所以表示储存数字是计算机的重要功能,但真正的目标是计算,有意义的处理数字:比如把“两个数相加”这些操作由计算机的“算术逻辑单元”处理,简称“ALU” 2)ALU是计算机的数学大脑,ALU*就是*计算机里负责运算的组件,基本其他所有部件都用到它。3)最著名的ALU——英特尔——74181,1970年,它是第一个封装在单个芯片的完整ALU。 4)用布尔逻辑做个简单的ALU电路,功能和74181一样,用它从头做出一台电脑 二:ALU有两个单元,1个算术单元和一个逻辑单元 1)算术单元:它负责计算机里的所有数字在操作,例:加减法。它还会做很多其他的事情,比如给某个数字加1,“把两个数字相加”这叫增量运算 2)最简单的加法电路:是拿2个bit加在一起(bit是0或1);有2个输入:A和B,一个输出,就是两个数字的和,需要注意的是:A,B,输出,这3个都是单个(bit)(0或1) 文案大全

3)输入只有4种可能:前三个是0+0=0 1+0=1 0+1=1 (记住在二进制里面,1与true相同,0与false相同。 4)这组输入和输出,和XOR门的逻辑完全一样, 所以我们可以把XOR用作1位加法器(adder) 但第四个输入组合,1+1,是个特例。1+1=2(显然)但二进制里面没有2,二进制里1+1的结果文案大全

是0,1进到下一位,和是10(二进制)XOR的输出。只对了一部分。1+1输出0,但我们需要一根额外的线代表“进位”只有输出是1和1时,进位才是true因为算出来的结果用一个bit 存不下,方便的是,我们刚好有个逻辑门能做这个事,“AND”门,只有当两个输入为“true” 的输出才为“true”所以我们把它加到电路中。这个电路叫叫“半加器” 文案大全

算术逻辑部件ALU实验报告 一、实验目的 (1)熟悉硬件描述语言及开发环境,了解硬件系统开发的基本过程。 (2)掌握ALU基本设计方法和简单运算器的数据传送通路。 (3)验证ALU的功能。 二、实验环境 (1)硬件环境:安装有Windows 7 或以上操作系统的PC,THINPAD教学计算机。(2)软件开发:FPGA开发工具软件Xilinx ISE 12.3或以上。 三、实验内容 (1)根据实验原理中的要求,用VHDL语言实现一个简单的ALU。 (2)在教学计算机THINPAD上验证实现的ALU的功能。 四、实验原理 算术逻辑部件ALU的主要功能是对二进制数据进行定点算术运算、逻辑运算和各种移位操作等。算术运算包括定点加减乘除运算,逻辑运算主要用逻辑与、逻辑或、逻辑异或和逻辑非等操作。ALU通常有两个数据输入端A和B输出操作数,一个数据输出端Y以及标志位输出结果,通过输入操作码op来确定所要进行的操作,本实验通过实现一个状态机,根据状态机状态的变化来输人操作数及操作码,并最终实现不同的运算,将结果和标志位呈现出来。 本实验中的ALU要求实现基本的算术运算、逻辑运算、移位运算等,具体功 五、实验步骤 本实验通过VHDL语言实现一个比较简单的ALU模块。 (1)用VHDL语言编写ALU功能代码,并用状态机对其进行控制,使其完成实验要求的操作。操作码和操作数的输入用微型开关SW0~SW15,计算结果的输出用数字机上的LED灯来展示。 (2)将代码下载到教学机的FPGA中,并调试完成。 (3)在THINPAD教学机上运行时,RST和时钟均用手动开关或按钮,便于演示。操作码和操作数在开关SW0~SW15上输入,为便于观察和调试,每次ALU得到操作数,最好可以在LED上显示一下,最后的运算结果在L0~L15上显示,标志位

运算器部件实验:加法器 一、实验目的 1、掌握运算器的工作原理。 2、验证运算器的功能。 二、实验原理 算术逻辑单元的主要功能是对二进制数据进行定点算术运算、逻辑运算和各种移位操作。算术运算包括定点加减乘除运算;逻辑运算主要有逻辑与、逻辑或、逻辑异或和逻辑非操作。ALU通常有两个数据输入端A和B,一个数据输出端Y以及标志位等。 74181是一种典型的4位ALU器件。下图是74181的逻辑电路图。 20世纪80年代计算机中的算术逻辑单元有许多是用现成的算术逻辑器件连接起来构成的,如上面提到的74181和Am2901等就是著名的算术逻辑器件。使用这些4位的算术逻辑器件,能够构成8位、16位等长度的算术逻辑单元。现在由于超大规模器件的广泛应用,使用这种方法构成算术逻辑单元已经不多见,代之以直接用硬件描述语言设计算术逻辑单元。 三、实验内容

设计一个16位算术逻辑单元,满足以下要求。 (1)16位算术逻辑单元能够进行下列运算:加法、减法、加1、减1、与、或、非和传送。用3位运算操作码OP[2…0]进行运算,控制方式如下表所示。 (2)设立两个标志寄存器Z和C。当复位信号reset为低电平时,将这两个标志寄存器清零。当运算结束后,在时钟clk的上升沿改变标志寄存器Z和C的值。运算结果改变标志寄存器C、Z的情况如下:加法、减法、加1、减1运算改变Z、C;与、或、非运算改变Z,C保持不变;传送操作保持Z、C不变。因此在运算结束时Z、C需要两个D触发器保存。 (3)为了保存操作数A和B,设计两个16位寄存器A和B。当寄存器选择信号sel=0时,如果允许写信号write=1,则在时钟clk的上升沿将数据输入dinput 送入A寄存器;当sel=1时,如果允许写信号write=1,则在时钟clk的上升沿将数据输入dinput送入B寄存器。 (4)算术逻辑单元用一个设计实体完成。 四、实验数据

福建农林大学计算机与信息学院信息工程类 实验报告 课程名称:《计算机组成原理》 名:姓 系:计算机系 计算机科学与技术业:专 年2007级:级 学号: 指导教师: 讲师职称: 日25 月5 年2009. 附件二:实验报告实验项目列表格式 实验项目列表

福建农林大学计算机与信息学院信息工程类实验报告级 系:计算机科学与技术 2007计算机系专业:年级: 姓名:学号:实验课程:计算机组成原理 实验室号:___田实验设备号: 1 实验时间: 2009年5月 4日指导教师签字:成绩: 算术逻辑运算实验实验一1.实验目的和要求 (1)掌握简单运算器的组成以及数据传送通路; (2)验证运算功能发生器(74LS181)的组合功能。 2.实验原理 图1-l 运算器数据通路图 实验中所用的运算器数据通路如图1-1所示。其中运算器由两片74LS181以并/串形式构成8位字长的ALU。运算器的两个数据输入端分别由两个锁存器(74LS273)锁存,锁存器的输入连至数据总线,数据输入开关用来给出参与运算的数据,并经过一三态门. (74LS245)和数据总线相连。运算器的输出经过一个三态门(74LS245)和数据总线相连。数据显示灯已和数据总线相连,用来显示数据总线内容。 图1-2中已将实验需要连接的控制信号用箭头标明(其他实验相同,不再说明)。其中除T4为脉冲信号,其它均为电平控制信号。实验电路中的控制时序信号均已内部连至相应时序信号引出端,进行实验时,还需将S3、S2、S1、S0、Cn、M、LDDR1、LDDR2、ALU_G、SW_G各电平控制信号与开关单元中的二进制数据开关进行跳线连接。其中ALU_G、SW_G为低电平有效,LDDR1、LDDR2为低电平有效。

理工大学城市学院 FPGA实验报告 实验容:8位ALU 系别班级:电子1004班 学号: : 日期:2013.4.14

一.设计概述: 一种基于可编程逻辑器件FPGA和硬件描述语言的8位的ALU的设计方法。该ALU 采用层次设计方法,有寄存器模块、控制模块和显示模块组成,能实现8位无符号数的取值、加减和4种逻辑运算(与、或、异或、同或)。该ALU在QuartusII软件环境下进行功能仿真,通过DE2验证。 二.设计功能: 1、该处理器的数据宽度为8bit,可以实现算术加法、减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。 2、用选择端opcode [2:0] 选择8种运算,2个操作数分别是a_r [7:0]和b_r[7:0],运算结果是alu_out[7:0];并定义选择如下。 3、使用DE2板上的3个拨码开关设置当前ALU的运算功能,再由8个拨码开关给定数据A和数据B,由一个按键key手动提供脉冲。 三.设计方案: 本设计共有5个模块。 1)脉冲输出器(key手动脉冲),计数依次产生4个脉冲到各个部件,第一个脉冲启动信号。 2)寄存器A,第二个脉冲来时锁存数据A,并在数码管上显示。 3)寄存器B,第三个脉冲来时锁存数据B,并在数码管上显示。 4)8位ALU,第四个脉冲来时进行运算,并锁存结果alu_out。 5)结果显示器,将结果显示通过DE2上的数码管显示。 四.程序分析: 主程序模块:

module alu8(clk,clk_r,rst,a,b,alu_out,opcode,sw_ab,HEX1, HEX0, HEX7, HEX6, HEX5, HEX4); input clk,rst,clk_r; input [7:0] sw_ab; input [2:0] opcode; output [6:0] HEX1, HEX0, HEX7, HEX6, HEX5, HEX4; output [7:0] a; output [7:0] b; output [7:0] alu_out; rega U1(.clk(clk),.rst(rst),.sw_ab(sw_ab),.a_r(a),.clk_r(clk_r),.HEX7(HEX7),. HEX6(HEX6)); regb U2(.clk(clk),.rst(rst),.sw_ab(sw_ab),.b_r(b),.clk_r(clk_r),.HEX5(HEX5),. HEX4(HEX4)); alur U3(.clk(clk),.rst(rst),.a_r(a),.b_r(b),.alu_out(alu_out),.opcode(opcode)); digital U4(.clk_r(clk_r),.rst(rst),.alu_out(alu_out),.HEX1(HEX1),. HEX0(HEX0)); endmodule 第一位数A模块: module rega (clk,clk_r,rst,sw_ab,a_r,HEX7,HEX6); input [7:0] sw_ab; input clk,clk_r,rst; output [7:0] a_r; reg [7:0] a_r; output reg[6:0] HEX7,HEX6; reg [3:0]t; always (posedge clk or negedge rst) if(!rst)t<=1'd0; else if(cnt==5)t<=1'd0; elset<=cnt+1'd1; always (posedge clk or negedge rst) if(!rst) a_r=0; else if(cnt==1) a_r=sw_ab; else a_r=a_r; parameter seg0=7'b1000000, seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010, seg6=7'b0000010, seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b00000 11,segc=7'b1000110, segd=7'b0100001,sege=7'b0000110,segf=7'b0001110; always (posedge clk_r) case(a_r[3:0]) 4'h0: HEX6[6:0]=seg0; 4'h1: HEX6[6:0]=seg1; 4'h2: HEX6[6:0]=seg2; 4'h3: HEX6[6:0]=seg3; 4'h4: HEX6[6:0]=seg4;

EDA技术与应用实验报告(四) 实验名称:ALU(算术逻辑运算单元)的设 计 姓名:陈丹 学号:100401202 班级:电信(2)班 时间:2012.12.11 南京理工大学紫金学院电光系

一、实验目的 1、学习包集和元件例化语句的使用。 2、学习ALU电路的设计。 二、实验原理 1、ALU原理 ALU的电路原理图如图1所示,主要由算术运算单元、逻辑单元、选择单元构成。 图1 ALU功能表如表1所示。 表1 2、元件、包集 在结构体的层次化设计中,采用结构描述方法就是通过调用库中的元件或者已经设计好

的模块来完成相应的设计。在这种结构体中,功能描述就像网表一样来表示模块和模块之间的互联。如ALU是由算术单元、逻辑单元、多路复用器互相连接而构成。而以上三个模块是由相应的VHDL代码产生的,在VHDL输入方式下,如果要将三个模块连接起来,就要用到元件例化语句。元件例化语句分为元件声明和元件例化。 1、元件声明 在VHDL代码中要引入设计好的模块,首先要在结构体的说明部分对要引入的模块进行说明。然后使用元件例化语句引入模块。 元件声明语句格式: component引入的元件(或模块)名 port(端口说明); end component; 注意:元件说明语句要放在“architecture”和“begin”之间。 2、元件例化语句 为将引入的元件正确地嵌入到高一层的结构体描述中,就必须将被引用的元件端口信号与结构体相应端口信号正确地连接起来,元件例化语句可以实现该功能。 元件例化语句格式: 标号名:元件名(模块名)port map(端口映射); 标号名是元件例化语句的唯一标识,且结构体中的标识必须是唯一的;端口映射分为:位置映射、 名称映射。 位置映射指port map中实际信号的书写顺序与component中端口说明中的信号书写顺序一致,位置映射对书写顺序要求很严格,不能颠倒;名称映射指port map中将引用的元件的端口信号名称赋予结构体中要使用元件的各个信号,名称映射的书写顺序要求不严格,顺序可以颠倒。 3包集 在实体及结构体中定义的对象、数据类型,对另外代码的实体是不能使用的。但是在同一工程的不同VHDL文件中,有些对象、数据类型、子程序等常常被重复使用。为方便VHDL 代码的编写,简化电路设计,故引入包集。包集也称为程序包。 包集主要由两部分组成:程序包说明和程序包体。其中,程序包体是可选的,一般程序包说明列出所有项的名称,而程序包体给出各项的细节。 程序包说明中包含的内容很多,只要是通用的全局量,都可以在程序包中加以说明。主要内容如下: ★对象(常量、变量、信号)的数据类型说明。 ★对象(常量、变量、信号)子类型的数值范围说明。 ★函数与过程说明。 ★元件语句说明。 程序包说明的书写格式如下: package程序包名is 说明语句; end程序包名; 程序包名:设计者自定义便于记忆的标识符。说明语句:包括各种类型的说明语句。 程序包体书写格式如下: package body程序包名is 52

实验一算数逻辑运算单元实验 2014.4.29 班级12级物联网工程(1)班学号姓名 【实验目的】 1.掌握简单运算器的数据传输方式。 2.掌握74LS181的功能和应用。 【实验要求】 完成不带进位位算术、逻辑运算实验。 按照实验步骤完成实验项目,了解算术逻辑运算单元的运行过程。 【实验过程】 实验1.1 不带进位位逻辑或运算实验 (1).把ALU-IN(8芯的盒型插座)与CPT-B板上的二进制开关单元中J01插座相连(对应二进制开关H16~H23),把ALU-OUT(8芯的盒型插座)与数据总线上的DJ2相连。 (2).把D1CK和D2CK用连线连到脉冲单元的PLS1上,把EDR1、EDR2、ALU-O、S0、S1、S2、S3、CN、M接入二进制开关(请按下表接线)。 (3).按启停单元中的运行按钮,使实验平台处于运行状态。 (4).二进制开关H16~H23作为数据输入,置33H(对应开关如下表)。 置各控制信号如下:

(5).按脉冲单元中的PLS1脉冲按键,在D1CK上产生一个上升沿,把33H打入DR1数据锁存器,通过逻辑笔或示波器来测量确定DR1寄存器(74LS374)的输出端,检验数据是否进入DR1中。 (6).二进制开关H16~H23作为数据输入,置55H(对应开关如下表)。 置各控制信号如下: (7).按脉冲单元中的PLS1脉冲按键,在D2CK上产生一个上升沿的脉冲,把55H 打入DR2数据锁存器。 (8).经过74LS181的计算,把运算结果(F=A或B)输出到数据总线上,数据总线上的LED显示灯IDB0~IDB7应该显示为77H。 实验1.2 不带进位位加法运算实验 (1)二进制开关H16~H23作为数据输入,置33H(对应开关如下表)。 置各控制信号如下: (2).按脉冲单元中的PLS1脉冲按键,在D1CK上产生一个上升沿,把33H打入DR1数据锁存器,通过逻辑笔或示波器来测量确定DR1寄存器(74LS374)的输出端,检验数据是否进入DR1中。 (3).二进制开关H16~H23作为数据输入,置55H(对应开关如下表)。 置各控制信号如下: (4).按脉冲单元中的PLS1脉冲按键,在D2CK上产生一个上升沿,把55H打入DR2数据锁存器。 (5).经过74LS181的算术,把运算结果(F=A加B)输出到数据总线上,数据总线上的LED显示灯IDB0~IDB7应该显示为88H。 【实验结果】 验证74LS181的算术运算和逻辑运算,在保持DR1=65H、DR2=A7H时,改变运算