K60(Rev6-Ch42-CMT)(中文)

第42章载波调制发射器(CMT)42.1 简介

载波调制发射器(CMT)模块为各种编码方案提供产生协议时序和载波信号的途径。CMT结合硬件处理重要的或者长时间的定时,结合来自CPU的信号产生,释放出更多的带宽处理其他的任务如代码数据生成,数据解压,或键盘扫描。CMT不包括特定协议的专用硬件配置,但是为了在功能上满足处理大多数协议的时序尽可能少的CPU干预的要求。当关闭调制器时,一些CMT寄存器可以直接用来改变红外输出信号的状态。这一特点致使下一代协议定时信号很难通过当前的架构而产生。

42.2 特点

这个模块的特点包括:

1.4种操作模式

(1)时序;带高和低时序的独立控制

(2)带宽

(3)频移键控(FSR)

(4)直接软件控制CMT_IRO信号

2.延长时间,带宽,FSK空间操作的模式

3.可选择的输入时钟分频器

4.周期结束中断

(1)能够关闭CMT_IRO信号并且作为定时器中断使用

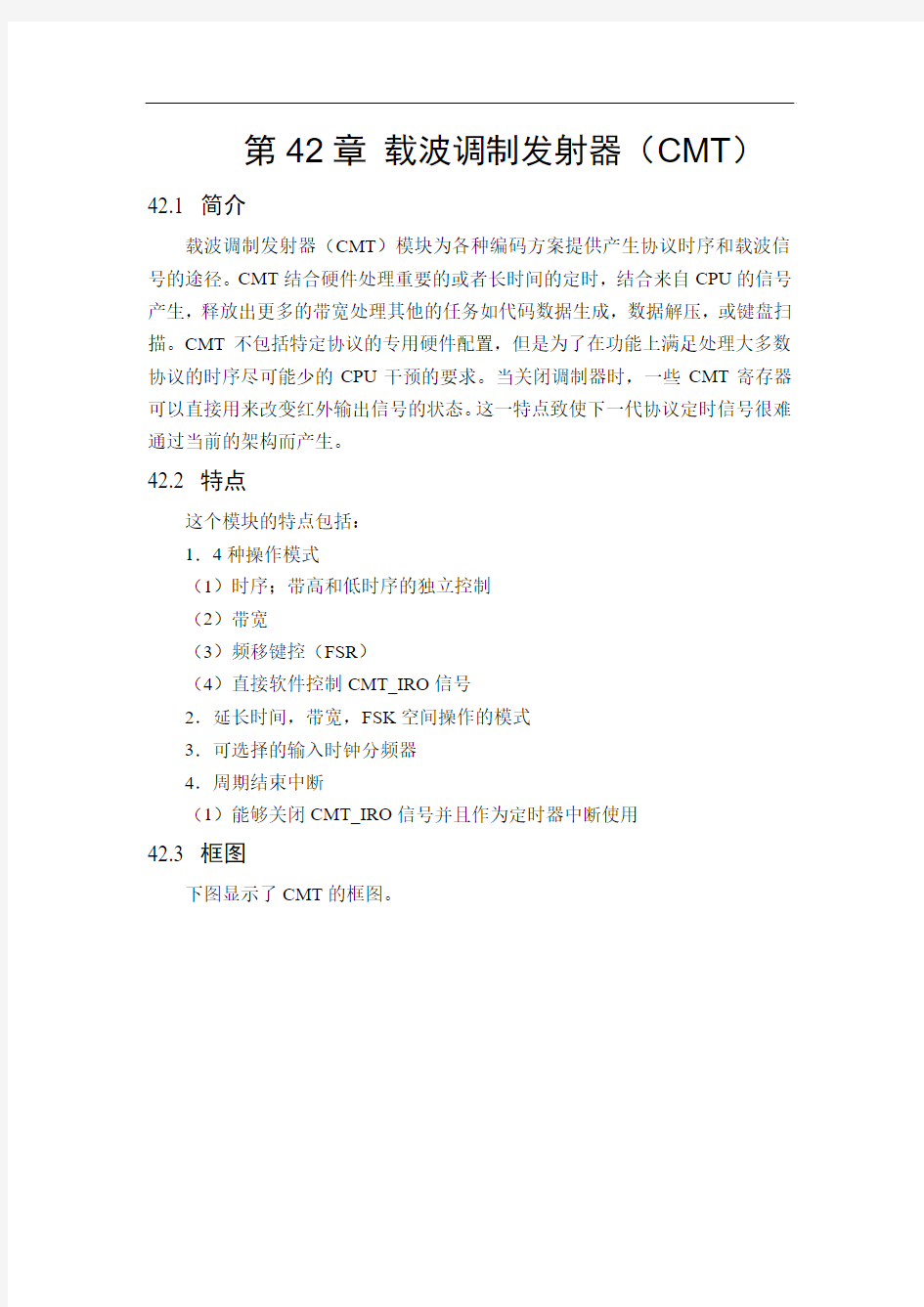

42.3 框图

下图显示了CMT的框图。

图42-1 CMT模块框图

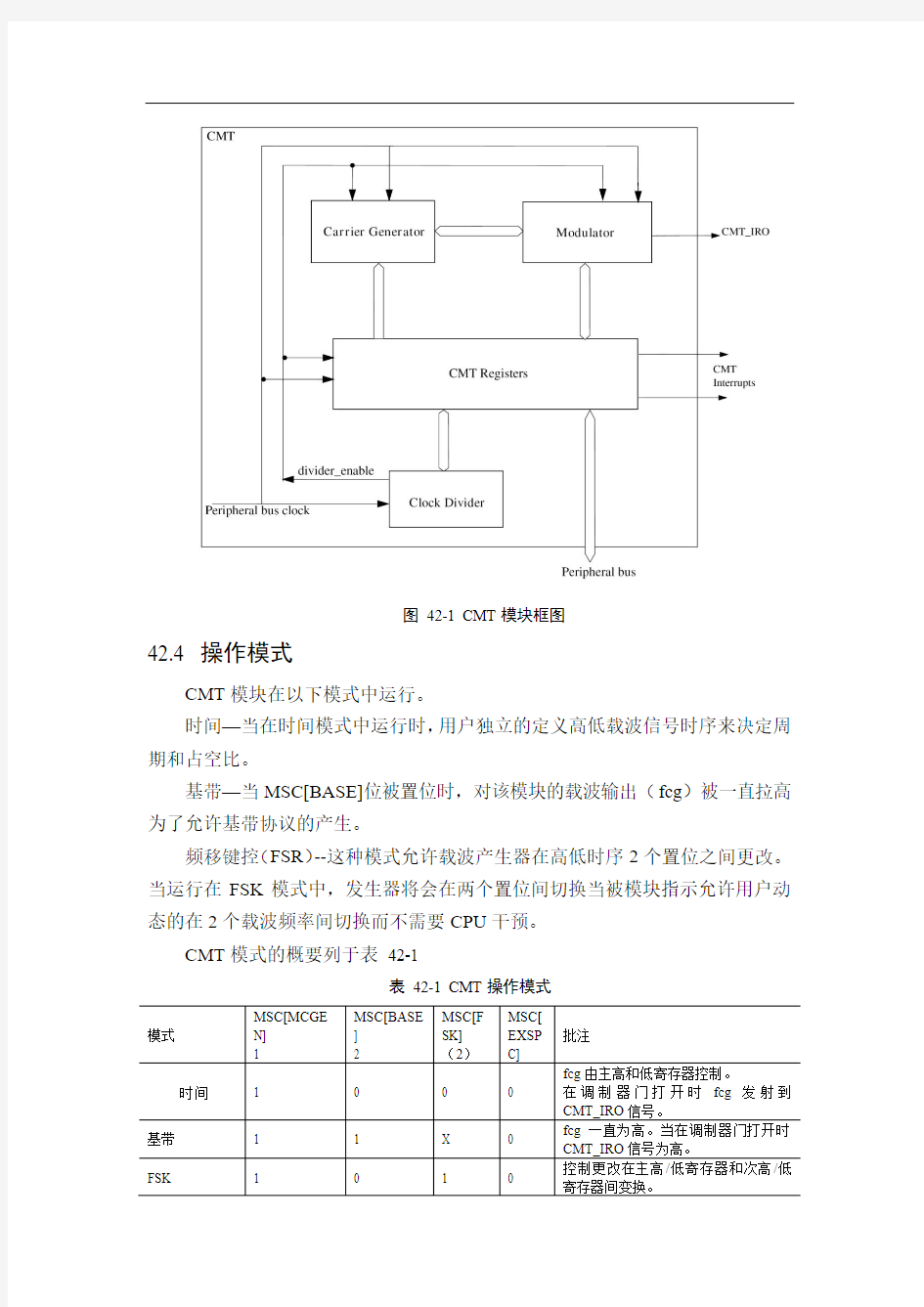

42.4 操作模式

CMT模块在以下模式中运行。

时间—当在时间模式中运行时,用户独立的定义高低载波信号时序来决定周期和占空比。

基带—当MSC[BASE]位被置位时,对该模块的载波输出(fcg)被一直拉高为了允许基带协议的产生。

频移键控(FSR)--这种模式允许载波产生器在高低时序2个置位之间更改。当运行在FSK模式中,发生器将会在两个置位间切换当被模块指示允许用户动态的在2个载波频率间切换而不需要CPU干预。

CMT模式的概要列于表42-1

表42-1 CMT操作模式

1.为了防止虚假操作,在开始传输之前初始化所有的数据和控制寄存器(MSC[MCGEN=1)。

2.这些位不是双缓冲的,在传输时不能更改(在MSC[MCGEN]=1时)。

注意

模块的方式到核心模式的任务是芯片特定的。对于模块到内核模式的任务,请参阅本章介绍如何配置模块。

42.4.1 等待模式操作

在等待模式中,如果CMT使能,将会继续正常运行。但是,当在等待模式中时,CMT的运行模式不会改变,因为CPU是不运行的。

42.4.2 停止模式操作

这节描述CMT停止模式操作。

42.4.2.1 正常停止模式操作

在正常停止模式里,CMT模块时钟停止。没有寄存器受到影响。

因为时钟停止了,CMT一旦从正常停止模式离开将会恢复。软件应当确保不能在调制器仍在操作时进入正常停止模式,防止在正常停止模式里阻止CMT_IRO信号不能被断言。这可能要求自MSC[MCGEN]位被清零起,要有一个超时时间来完成最近的调制器周期。

42.4.2.2 低功耗停止模式操作

在低功耗停止模式里,CMT模块内部完全断电,CMT_IRO信号状态在进入低功耗停止模式时被锁存并保持。为了防止CMT_IRO信号在低功耗停止模式里被断言,软件应当确保在进入低功耗停止模式时的信号是无效的。一旦从低功耗停止模式里唤醒,CMT模块将会处于复位状态。

42.5 CMT外部信号描述

这个表列出了外部信号的描述

表42-2 CMT信号描述

42.5.1 CMT_IRO—红外输出

当MSC[MCGEN]和OC[IROPEN] 被置位时,这个输出信号由调制器输出驱动。CMT_IRO信号开始一个有效的传输时有一定延迟,在MSC[MCGEN]位被断言为高时,可以通过两个寄存器位计算出来。表42-3给出了如何计算这个延时。

如果MSC[MCGEN]为被清零并且OC[IROPEN]位被置位,信号由OC[IROL]位驱动。这个使得用户软件可以直接通过写OC[IROL]位控制CMT_IRO的信号状态。如果OC[IROPEN]位被清零,信号被禁止并且不能被CMT模块驱动。因此,CMT可配置为一个定时器模块,用来生成周期性的中断,而不会造成信号有效

表42-3 CMT_IRO信号延迟计算

42.6 存储映像/寄存器定义

一下寄存器控制和监视CMT操作。

一个寄存器地址是基地址和偏移地址的和。基地址是芯片级定义的。偏移地址是模块级定义的。

CMT 存储映像

这个数据寄存器包括为产生载波输出的主高值。

地址:CMT_CGH1—4006_2000h 基址+0h 偏移=4006_2000h

注意:

X=在复位时未定义

CMT_CGH1域描述

42.6.2 CMT 载波发生器低数据寄存器1(CMT_CGL1)

这个数据寄存器包括产生载波输出的主要低值。

地址:CMT_CGL1—4006_2000h 基址+1h 偏移=4006_2001h 注意:

X=在复位时未定义

CMT_CGL1域描述

这个数据寄存器包括产生载波输出的次要高值。

地址:CMT_—4006_2000h 基址+2h 偏移=4006_2002h 注意:

X=在复位时未定义

CMT_CGH2域描述

42.6.4 CMT 载波发生器低数据寄存器2(CMT_CGL2)

这个数据寄存器包括产生载波输出的次要低值。

地址:CMT_CGL2—4006_2000h 基址+3h 偏移=4006_2003h 注意:

X=在复位时未定义

CMT_CGL2域描述

42.6.5 CMT 输出控制寄存器(CMT_OC )

这个寄存器被用于控制CMT 模块的IRO 信号。

地址:CMT_—4006_2000h 基址+4h 偏移=4006_2004h

注意:

X=在复位时未定义

CMT_OC 域描述

42.6.6 CMT 调制器状态和控制寄存器(CMT_MSC

)

MSC 寄存器包括调制器和载波发生器使能(MCGEN ),周期结束使能(EOCIE ),FSK 模式选择(FSK ),基带使能(BASE ),扩展空间(EXSPC ),预分频器(CMTDIV )位,和周期结束(EOCF )状态位。

地址:CMT_MSC —4006_2000h 基址+5h 偏移=4006_2005h

CMT_MSC 域描述

42.6.7 CMT调制器数据屏蔽高寄存器(CMT_CMD1)

这个寄存器的内容在一个调制周期完成之后传送到调制器向下计数器。

地址:CMT_CMD1—4006_2000h基址+6h偏移=4006_2006h

X=在复位时未定义

CMT_CMD1域描述

42.6.8 CMT调制器数据屏蔽低寄存器(CMT_CMD2)

这个寄存器的内容在一个调制周期完成之后传送到调制器向下计数器。

地址:CMT_CMD2—4006_2000h基址+7h偏移=4006_2007h

注意:

X=在复位时未定义

CMT_CMD2域描述

42.6.9 CMT调制器数据间隙高寄存器(CMT_CMD3)

这个寄存器的内容在一个调制周期完成之后传送到空间周期寄存器。

地址:CMT_CMD3—4006_2000h基址+8h偏移=4006_2008h

注意:

X=在复位时未定义

CMT_CMD3域描述

42.6.10 CMT调制器数据间隙低寄存器(CMT_CMD4)

地址:CMT_CMD4—4006_2000h基址+9h偏移=4006_2009h

注意:

X=在复位时未定义

CMT_CMD4域描述

42.6.11 CMT主预分频器寄存器(CMT_PPS)

这个寄存器用于置位主预分频器位(PPSDIV)。

地址:CMT_PPS—4006_2000h基址+Ah偏移=4006_200Ah

CMT_PPS域描述

42.6.12 CMT 直接存储访问(CMT_DMA )

这个寄存器用于使能/关闭直接内存访问(DMA )。

地址:CMT_DMA —4006_2000h 基址+Bh 偏移=4006_200Bh

CMT_DMA 域描述

42.7 功能描述

CMT 模块主要有时钟分频器,载波发生器和调制器组成。

42.7.1 时钟分频器

CMT 原本根据8MHz 总线时钟设计的,可以根据说明进行1,2,3,4或8分频。为了兼容更高的总线频率,主预分频器(PPS) 被开发为接收一个更高的频率并且产生一个叫中频(IF )的时钟使能信号。这个IF 应该大约等于8MHz ,而且成为使次预分频器时钟工作的一个时钟使能。下图给出了时钟分频器的框图。

图 42-14 时钟分频器框图

为了兼容CMT 的先前版本,当总线时钟=8MHz 时,PPS 应该配置成0。PPS 计数器根据总线时钟产生一个大约等于8MHz 的中频选择。

42.7.2 载波发生器

当运行在一

个

8MHz 中频型号并且次预分频器被置位为1分频(MSC[CMTDIV]=00)时,载波发生器的速度为125ns 。载波发生器可以产生周期在250ns (4MHz )和127.5μs (7.84kHz )之间间距为125ns 的信号。表 42-17给出了失踪分频位和载波发生器分辨率,最小载波周期和最小调制周期之间的关

系。

表42-17 时钟分频器

可能的占空比周期选项取决于要求完成的载波周期的计数值。例如,1.6MHz 信号是625ns的周期,因此要求5x125ns的计数去产生。这些计数值可能被分为高磁或者低次,所以占空比周期将会有20%(1份高,4份低),40%(2份高,3份低),60%(3份高,2份低),80%(4份高,1份低)有效。

为了低频信号占更大的比重,高分辨率的(总周期的百分比)占空比周期是可能的。

载波信号通过计数一个选择的寄存器的高载波时间和低载波时间的输入时钟数(8MHz总线125ns)产生。周期取决于总的时钟计数值。占空比取决于高时间时钟占总的计数时钟的比率。高时间和低时间的值是用户可编程的并且保存在两个寄存器中。

一个备用的高/低计数值的集合保存在另外的基础器中允许双频FSK(频移键控)协议的产生而不需要CPU的干预。

注意

只允许非零数据值。如果有计数值为0,那么载波发生器不会工作。

MSC[MCGEN]位必须被置位而且MSC[BASE]位必须清零来使能载波发生器时钟。当MSC[BASE]位被置位时,到调制器的载波输出一直保持高。下图为时钟发生器的框图。

图42-15 载波发生器框图

高/低时间计数器是一个8位的向上计数器。每次增加后,计数器中的内容会和合适的高或低计数值寄存器比较。当比较值相同时,计数器复位到0x01,并且比较重定向到其他的计数值寄存器。

假设高时间按计数比较寄存器当前活跃,一个有效的比较将会导致载波输出驱动低。计数器将继续增加(从复位值0X01开始)。当存储在选择的低计数值寄存器中的值相同时,计数器将会再次复位并且载波输出驱动高。

每个周期,会自动的产生直接给调制器的周期信号。最低频(最大周期)和最高频(最小周期)按照定义都可以产生。

fmax= fCMTCLK ÷(2x1)Hz fmin= fCMTCLK ÷(2x(28-1))Hz 通常情况下,载波发生器输出频率如下: fcg= fCMTCLK ÷(Highcount+Lowcount )Hz 1 载波信号占空比是通过改变高时间与低+高时间的比率来控制的。由于输入时钟周期是固定的,占空比分辨率将会正比于要产生的期望的载波周计数值。 占空比=低计数高计数高计数 42.7.3 调制器 调制器块控制红外输出信号(IRO )的状态。当调制器/载波发生器使能时,调制器输出被IRO 信号控制。当调制器/载波发生器关闭时,IRO 信号由IRO 锁存的状态控制。OC[CMTPOL]使能IRO 信号为高有效还是低有效。 在CMT 模式里,调制器功能如下: 在时间模式里,调制器可以控制载波到调制器输出上。 在基带模式里,调制器可以控制调制器的输出逻辑电平。 在FSK 模式里,调制器可以计数载波周期和指示载波发生器在两个载波频率间更换每当调制周期到期时。 调制器提供了一个简单的方法控制协议时序。调制器在8MHz 时有一个最小的响应为1.0μs 。它可以计数总线时钟(提供实时控制)或它可以计数载波时钟(为自计时协议)。 调制器包括一个17位的带检查溢出的向下计数器。计数器加载16位调制器空白周期缓冲寄存器中的值,CMD1和CMD2。最重要的位加载为0并且有一个符号位。当计数器是正值时,调制器们是开放的并且载波信号驱动发射器块。 当计数器溢出时,调制器门关闭并且使能16位比较器,来比较带调制器空 间周期寄存器内容的向下计数器值的逻辑完成,这已从CMD3和CMD4中加载。 当获得一个匹配时,通过打开调制器门,重载带CMD1和CMD2内容的计数器,重载调制器带CMD3和CMD4空周期寄存器来重复周期。 当载波信号为低禁止减少载波信号的高脉冲时,调制器空周期活动完成。如果载波信号时高,那么调制器延伸标志周期直到载波信号变为低。为了去断言空周期和断言标志周期,载波信号必须变为低确保空周期不会错误的减少。 如果调制器空周期寄存器的内容都为0,那么将会立即匹配并且没有空周期会产生(例如,FSK协议要求不同的频率连续发生)。 MSC[MCGEN]必须置位成开启调制器定时器。 图42-16 调制器框图 42.7.3.1 时间模式 当调制器运行在时间按模式里时(MSC[MCGEN]位被置位,MSC[BASE]和MSC[FSL]位被清零),调制器标志周期有CMTCLK÷8个时钟周期的整数值组成。8MHz IF和MSC[CMTDIV]=00时,调制器的响应时1μs,并且最大大约是65.535ms的标志和空周期。见下图时间模式和基带模式输出的示例。 时间和基带模式的标志和空时间方程如下: tmark=(CMD1:CMD2) ÷(fCMTCLK÷8) tspace=CMD3:CMD4÷(fCMTCLK÷8) 当CMD1:CMD2和CMD3:CMD4是级联寄存器的十进制值时。 图42-17 例:OC[CMTPOL]=0时时间和基带模式里的CMT输出 42.7.3.2 基带模式 基带模式(MSC[MCGEN]和MSC[BASE]位被置位)是时间模式的一个衍生,当标志和空周期是基于计数时(CMTCLK÷8)。标志和空计算和时间模式里是一样的。在这种模式里,调制器在标志周期的持续时间里会是逻辑1,在空周期的持续时间里是逻辑0。见图42-17中基带和时间模式里的输出例子。在例子中,载波输出频率产生一个0x01的高计数和0x02的一个低计数,这将会导致CMTCLK的3分频,一个33%的占空比。调制器向下计数器加载0x0003,空周期寄存器加载0x0002。 注意 图42-17和图42-18的波形是个概念图,并不是信号之间精确的时序关系。 42.7.3.3 FSK模式 当调制器运行在FSK模式里时(MSC[MCGEN]和MSC[FSK]位被置位,MSC[BASE]位被清零),调制器标志和空周期由载波时钟的一个整数数组成(空周期可以为0)。当标志周期到期时,空周期是透明启动的(就像在时间模式里)。每当调制器空周期到期时,载波发生器在主次数据寄存器值之间切换。 空周期提供一个脉冲间间隙(不载波)。如果CMD3:CMD4=0X0000,那么调制器和载波发生器将在无间隙的载波频率或任意载波毛刺(0空)之间改变。 CPU使用定时数据为计算载波周期和脉间间隙长度,FSK模式可以自动的 产生一个相位相干,带可编程周期和丛间间隙的双频FSK信号。 FSK模式的标志和空时间方程为: tmark=(CMD1:CMD2+1)÷fcg tspace=CMD3:CMD4÷fcg 当fcg事故载波发生器的输出频率时。下图中的例子显示了IRO信号以下列值在FSK模式中的样子:CMD1:CMD2=0x0003,CMD3:CMD4=0x0002,主载波高计数=0x01,主载波低计数=0x02,次载波高计数=0x03,次载波低计数=0x01。 图42-18 例:在FSK模式里的CMT输出 42.7.4 扩展的空间操作 在任意时间里,基带或FSK模式里,空间周期可以比空间周期寄存器的最大可能只在长些。置位MSC[EXSPC]位将强制调制器将下一个调制周期(以下一次计数器和空间周期寄存器的加载作为起始)作为空间周期相当于标志和空间计数的和。虽好的调制周期将全部由这些不带标志周期的扩展空间周期组成。清零MSC[EXSPC]将会使得调制器在下一次调制周期开始时返回到标准操作。42.7.4.1 时间模式里的EXSPC操作 为了计算时间模式或基带模式里的扩张空间的长度,当MSC[EXSPC]被置位时增加标志和空间时间和乘以调制器的周期数据。 texspace=(tmark+tspace)x(调制器周期数) 以扩展空间操作为例,参见下图。 注意 扩展空间使能功能可以用来仿真一个0标志事件。 图42-19 扩展的空间操作 42.7.4.2 FSK模式里的EXSPC操作 在FSK模式里,调制器继续计数载波输出时钟,在每个调制周期结束时在主次寄存器之间切换。 为了计算FSK模式里扩展空间的长度,一方需要知道主或次调制周期里的MSC[EXSPC]为是否已经置位,正如在MSC[EXSPC]位为高时主次调制周期完成的总数。当前调制器的一个状态位是不能被CPU访问的。如果需要,软件应当持续跟踪当期调制器周期(主或次)。在调制器周期的空间周期时间完成时扩展空间周期结束,此时MSC[EXSPC]为被清零。 如果MSC[EXSPC]位再一个主调制器周期被置位,使用下面等式: texspace=(tspace)p+(tmark+ tspace)s+( tmark+ tspace)p+… 当下标p和s参考主次调制周期的标志时间和空间时间。 如果MSC[EXSPC]位再次调制周期间被置位,那么使用这个等式: texspace=(tspace)s+(tmark+ tspace)p+( tmark+ tspace)s+… 42.8 CMT中断和DMA CMT根据MSC[EOCIE],MSC[EOCF],DMA[DMA]位产生一个中断请求或一个DMA传输请求。 表42-18 DMA传输请求xCMT中断请求 在下列情况下MSC[EOCF]被置位: 当前调制器不活动,并且MSC[MCGEN]位被置位成开始初始化CMT传输。 在MSC[MCGEN]位被置位时,每次调制周期结束时(此时计数器重新加载CMD1:CMD2)。 这种情况里MSC[MCGEN]位被清零,然后在调制周期结束之前被置位,在MSC[MCGEN]位被置位时MSC[EOCF]为将会被置位,但是在当前调制周期结束 时变为置位。 当MSC[MCGEN]变为关闭时,CMT模块在最后一个调制周期结束时不会置位EOC标志。 如果在MSC[EOCF]位被置位时,MSC[EOCIE]为为高,那么CMT模块将产生一个中断请求或一个DMA传输请求。 在退出服务程序之后,MSC[EOCF]为必须清楚以防产生另一个事件(中断或DMA请求)。 表42-19 如何清零MSC[EOCF]位 EOC中断的同时将CMD1:CMD2中的内容加载到向下计数器中,将CMD3:CMD4中的内容加载到空间周期寄存器中。EOC中断为用户提供了重新加载新的标志/空间之道调制器数据寄存器中的一种方法。调制器数据寄存器将会在当期调制周期结束时更新。注意:向下计数器和空间周期寄存器在每个调制周期结束时更新,不论是中断处理和EOCF标志状态。 /*----------------------------------------------------------------------------------------------------------------------------- 桂林电子科技大学 物联网工程 Editor:JaceLin Date:2014.2.5 -------------------------------------------------------------------------------------------------------------------------------- 一、DMA特性 1)k60有16个DMA通道 二、寄存器 1)控制寄存器:DMA_CR 31-18 reserved 17 CX 取消转移,0正常操作,1取消剩下数据转移 16 ECX 错误取消转移,0正常操作,1取消转移 15-8 reserved 14 EMLM 使能副循环映射 0 禁止,TCDn.word2 为32位 1 使能,TCDn.word被重新定义 6 CLM 持续连接模式,0当副循环结束后,再次激活DMA要通过裁决,1不用裁决 5 HALT 停止DMA操作,0正常模式,1停止DMA操作 4 HOE 错误时停止,0正常操作,1当有错误时HALT=1,也就是DMA停止 3 reserved 2 ERCA 使能循环通道裁决, 1 EDBG 使能调试,写0,调试也用DMA,写1,调试时DMA不可用 0 reserved 2)错误状态寄存器DMA_ES 31 VLD 所有错误状态位逻辑或,0没有错误,1表示至少有1个错误没有清除 30-17 保留 16 ECX 转移被取消0没有被取消的转移,1最后一次记录是被取消的转移 15 保留 14 CPE 通道优先错误,0没有通道优先错误,1有 13-12 保留 11-8 ERRXHN 错误通道位/被取消的位(最多16位) 7 SAE 源地址错误,0没有源地址配置错误,1有错误 6 SOE 源偏移错误,0没有源偏移配置错误,1有偏移配置错误 5 DAE 目标地址错误,0没有错,1有错误 4 DOE 目标偏移错误,0没有错误,1有 3 NCE NBYTES/CITER配置错误,0没有,1有 2 SGE Scatter/Gather配置错误,0没有,1有 1 SBE 源总线错误,0没有错误,1有 12 芯片配置模块 12.1 简介 注意:具体芯片有关该模块的具体实现细节请参考芯片配置章节有关内容。 系统集成模块(SIM)包括系统控制及系统配置寄存器。 12.1.1 特性 1)系统时钟的配置 (1)为SDHC、IIS、以太网时间戳、USB以及PLL/FLL等提供时钟源选择; (2)系统时钟分频值; (3)IIS和USB时钟分频值 2)架构的时钟门控制 3)Flash配置; 4)USB基准配置; 5)RAM大小配置; 6)可变化的外部时钟和错误时钟源选择; 7)UART0和UART1收/发源的选择/配置; 8)复位引脚滤波。 12.1.2 工作模式 (1)运行模式(2)休眠模式(3)深度休眠模式(4)VLLS模式 12.1.3 SIM引脚说明 12.2 存储器映射及寄存器定义 SIM模块包含很多位域用于为不同模块时钟选择时钟源和分频。包括时钟框图和时钟定义的详细信息参见时钟分配(Clock Distribution)一章。 注意:SIM_SOPT1寄存器同其他SIM寄存器有不同的基址。 SIM存储器映射: 12.2.1 系统选项寄存器1(SIM_SOPT1) SOPT1寄存器的复位值为如下:从POR和LVD退出:USBREGEN被置1,USBSTBY 被清0,OSC32KSEL被清0。 从VLLS或其它系统复位退出:USBREGEN,USBSTBY和OSC32KSEL不受影响。 地址:SIM_SOPT1-4004_7000h 基址+0h偏移量=4004_7000h 说明x表示在复位时未定义 12.2.2 系统选项寄存器2(SIM_SOPT2) SOPT2包含选择本设备上多个模块时钟源选项的控制。包括框图及设备时钟定义的详细信息参见Clock Distribution一章。 地址:SIM_SOPT2 –4004_7000h 基址+ 1004h 偏移量= 4004_8004h 第 5 章时钟分配 5.1 概要 MCG 模块主要控制用于产生系统时间的时钟源,时钟发生器将选择好的时钟源分成各种时钟域,包括系统主机时钟、系统从机时钟以及flash 存储器时钟。另外,时钟发生器可以为各个模块产生特定的时钟门,允许单独开关各个模块。 系统主时钟由MCGOUTCLK 时钟产生。时钟发生器电路提供多种分频因子,使设备的不同部分产生不同频率的时钟,这样以便做到功耗与性能之间的权衡。 各种模块(例如USB OTG 控制器),都有其特定的模块时钟,这些时钟由MCGPLLCLK 或MCGFLLCLK 时钟产生。除此之外,有些模块特定时钟的时钟源是可以更换的。SIM 模块的SOPT 寄存器可以控制大多数模块的时钟。 5.2 编程模型 时钟源的选择和混合是通过MCG模块来控制和编程的,而系统的时钟分频因子和模块时钟门是通过SIM模块来编程设置的。详细信息参见具体的寄存器和位描述。 5.3 高级设备时钟框图 系统振荡器模块、MCG 模块和SIM 模块的寄存器对信号混合,分频因子和时钟门的控制如下: 图5-1 时钟框图5.4 时钟定义 下表描述了上面框图的时钟。 5.4.1 设备时钟汇总 表5-1 是芯片时钟的详细信息。 表5-1 时钟汇总 5.5 内部时钟需求 时钟分频器可以通过SIM 模块的CLKDIV 寄存器设置。每个分频器的分频因子可编程设置,能选择一到十六。配置此设备的时钟必须满足下列要求: 1. 内核和系统时钟频率必须在100MHz 以内。 2. 总线时钟频率必须编程设置不大于50MHz,且是内核时钟的整数分频。 3. flash 模块时钟频率必须编程设置不大于25MHz,且是总线时钟的整数分频。 4. FlexBus 时钟频率必须编程设置成不大于总线时钟。 此设备的若干常用时钟配置如下: 选择1: 第二章 引言 2.1概述 本章概述了Kinetis系列以及其中的K60系列,还对设备所涵盖的模块进行了概括描述。 2.2K60系列引言 K60微控制器系列具有以下性能:IEEE1588以太网,全速和高速USB 2.0On-The-Go带设备充电探测,硬件加密和防窜改探测能力。丰富的模拟、通信、定时和控制外设从100LQFP 封装256KB闪存开始可扩展到256MAPBGA1MB闪存。大闪存的K60系列器件还可提供可选的单精度浮点单元、NAND闪存控制器和DRAM控制器 2.3功能模块分类 器件按照功能分为不同的模块,下面的章节对每个功能模块有着更详细的描述。 表格2-1功能模块分类 模块描述 ARM Crotex-M4内核32位ARM Crotex-M内核,具有DSP指令和单精度浮点运算单元,1.25 DMIPS/MHz,基于ARMv7结构,在某些系列中还包括16KB的数据/ 指令高速缓冲。 系统模块系统集成控制模块 电源管理和模式控制 多种电源模式可供选择:运行、等待、停止和掉电模式 低漏电流唤醒单元 杂项控制单元 交叉开关 内存保护单元 内部总线 直接内存访问(DMA)控制器与复用器,增加可用的DMA请求 外部看门狗 存储内部存储器包括 程序存储器 FlexNVM FlexRAM 可编程FLASH编程加速内存 SRAM Cache 外部存储和设备控制总线接口:FlexBus 串行可编程接口:EzPort NAND flash控制器 时钟可选的多个时钟源:包括内部时钟和外部时钟 为系统提供系统时钟的振荡器 为实时时钟提供时钟源的振荡器 加密CRC模块 硬件加密和随机数发生器 模拟集成可编程放大增益的高速AD转换器 模拟比较器 DA转换器 内部参考电压 定时器可编程延时模块 柔性定时器 周期性中断定时器 低功耗定时器 载波调制定时器 实时时钟 通信以太网MAC控制器支持IEEE1588协议 USB OTG内嵌全速/低速PHY USB支持设备充电检测功能 USB自带电压调节功能 高速USB控制器ULPI接口 CAN SPI I2C UART SD主机控制器 I2S 人机界面GPIO 硬件电容触摸屏接口 2.3.1Crotex-M4内核模块 器件内包含以下核心模块 表格2-2核心模块 14低功耗模式 14.1 简介 PMC包括内部电压调节器,上电复位(POR)以及低电压检测系统。 模式控制器控制PMC,本节主要的内容包含设备的所有复位。 14.2 特征 电源管理控制特征包括以下几个方面 (1)内部电压调节器; (2)在检测到低电压时的有效上电复位; (3)低电压检测保护,包括:多个可编程脱扣电压、警告和检测中断控制、在低电压检测时驱动复位。 14.3 低电压检测系统(LVD) 芯片包括一个防范低电压状态的系统,使芯片电压变化时能保护存储器内容并控制MCU的系统状态。该系统是由一个上电复位(POR)电路和一个电压LVD电路组成的。对于LVD电压,用户可选择脱扣电压有高(VLVDH)或低(VLVDL)两种。脱扣电压由LVDSC1[LVDV]位决定。进入VLPx,LLS和VLLSx模式时LVD被禁止。 有两个标志位可以用来指示低电压检测系统的状态: (1)低电压检测标志(low voltage detect flag ,LVDF)在电平敏感的方式工作。当内部供电低于选定的内部监控阈值(VLVD)时LVDF位被置1。只有当内部供电回复到阈值电压之上时,才能通过LVDACK位写1才可将LVDF位清0。否则,LVDF位保持为1。 (2)低电压警告标志(low voltage warning flag ,LVWF)在电平敏感的方式工作。当内部供电低于选定的内部监控阈值(LVWF)时LVDF位被置1。只有当内部供电回复到阈值电压之上时,才能通过LVDACK位写1才可将LVWF位清0。否则,LVWF位保持为1。 14.3.1低电压复位操作 通过设置LVDRE位,检测到一个低电压状态后LVD产生一个复位。低电压检测阈值取决于LVDV位。在LVD复位后,LVD系统保持MCU的复位状态直到供电升高超过此阈值。LVD或上电复位后SRS寄存器中的LVD位被置1。 14.3.2低电压中断操作 若需中断操作,则要配置LVD电路(LVDIE置1,LVDRE清0);LVDSC1[LVDF]置1并且当检测到一个低电压状态是就会产生一个LVD中断请求。通过LVDSC1[LVDACK]位写1才可将LVDF位清0。 14.3.3低电压警告中断操作(Low-Voltage Warning ,LVW) LVD系统包含一个低电压警告标志用以指示供电已经临近LVW电压但高于LVD电压。LVW也有一个中断,LVDSC2[LVWIE]位置1可以使能中断请求。若中断请求使能,则当LVWF置1时,一个LVW中断请求将产生。通过向LVDSC2[LVWACK]位写1将LVWF Addition of Final Test Site for Defense-grade XQ FPGA Products XCN16021 (v1.0) June 13, 2016 Product Change Notice - For Information Only Overview The purpose of this notification is to inform customers that Xilinx is adding a final test site, Silicon Turnkey Solutions (STS), in the United States for all defense-grade XQ FPGA products. There is no change to the form, fit, or function of the devices with this change. Description Xilinx is adding a final test site capability to our current Xilinx’s qualified test facility in Singapore for business continuity purposes. All Xilinx Defense-grade XQ FPGA products test programs and test platforms will be transferred to Silicon Turnkey Solutions (STS) facility. STS has been qualified many years back for other Defense-grade XQR Military (M, N) grade and Space XQR (V, R) grade products. The additional test site is also meant to consolidate all our Defense-grade products in same geography to optimize delivery support. Products Affected This change affects all packages, speed, and temperature grade variations of the Defense-grade XQ (I, M, N, Q) devices. Affected part numbers are included in the following table(s). All associated SCDs are also affected. Table 1:Virtex?-II and Virtex-II Pro FPGA Products Family Affected Part Number Part Number XQ2V1000-4BG575N XQ2VP40-5FF1152N XQ2V1000-4FG456N XQ2VP40-5FG676N XQ2V6000-5EF957I XQ2VP70-6EF1704I Note : Virtex-II family is included for Post Last Time Buy requirement. It has been discontinued per XCN12026. Table 2:Virtex-4 FPGA Products Family Affected Part Number Part Number Part Number XQ4VFX100-11FFG1152I4012 XQ4VLX25-10FF668M XQ4VLX60-10FF1148M XQ4VFX60-10EF672I XQ4VLX25-10SF363M XQ4VLX60-10FF668M XQ4VFX60-10EF672M XQ4VLX40-10FF668I XQ4VLX80-11FF1148I XQ4VFX60-10FFG1152I XQ4VLX40-10FF668M XQ4VSX55-10FF1148M XQ4VLX100-11FF1148I XQ4VLX60-10EF668M XCN16021 (v1.0) Jun 13, 2016 第2章简介 2.1 概要 本章提供了Kinetis组合和K60系列产品的概述。同时,本章提供了本文件所包涵设备的高水准的描述。 2.2 Kinetis组合 Kinetis是低功耗可扩展和在工业上使用混合信号ARM?Cortex?-M4系列MCU的最好的组合。第一部分介绍超过200引脚、外围设备和软件兼容性的5个MCU系列。每个系列提供了优良的性能,与普通外设内存,内存映射,并提供内部和系列之间轻松迁移包和功能可扩展性。 Kinetis MCUs使用了飞思卡尔的新的90nm带有独特FlexMemory的薄膜存储器(TFS)闪存技术。Kinetis系列MCU结合了最新的低功耗革新技术和高性能,高精密混合信号功能与连通,人机界面,安全及外设广泛。Kinetis MCUs使用了飞思卡尔和ARM第三方合作伙伴的市场领先的捆绑模式。 表示低功耗混合信号USB 段LCD 以太网加密和篡改检测DDR 所有Kinetis系列都包涵强大的逻辑、通信和时序阵列和带有伴随着闪存大小和I/O数量的集成度等级的控制外围部件。所有的kinetis系列包涵一下共同特征:· 内核: · ARM Cortex-M4内核提供1.25 DMIPS / MHz的DSP指令(浮点单元在kinetis系列可用)。 · 高达32位的DMA,同时尽可能减小CPU干预。 · 提供50MHz、72MHz和100MHz几种CPU频率(120MHz和150MHz在kinetis可用)。 · 超低功耗: · 10种低功耗操作模式通过优化外设执行和唤醒时间来延长电池寿命。 · 为了增加低功耗的灵活性,增加了低漏唤醒单元、低功耗定时器和低功耗RTC。 · 业界领先的快速换醒时间。 · 内存: · 从32 KB闪存/ 8 KB的RAM可扩展为1 MB闪存/128 KB的RAM。同时使空白的独立闪存执行代码和固件更新。 · 可选16 KB用于总线带宽优化执行性能和闪存高速缓冲存储器。关于K10的、K20和K60系列设备提供120 MHz CPU或更高的性能。 · FlexMemory支持高达512 KB的FlexNVM和高达16 KB的FlexRAM。FlexNVM可以进行分区,以支持其他程序快闪记忆体(例如:引导器),数据闪存(如大型表的存储),或EEPROM备份。FlexRAM支持EEPROM按字节写入和擦出操作,同时决定了最大的EEPROM 大小。 · EEPROM的擦写次数可以高达1000万次。 · EEPROM的擦写速度比传统的EEPROM快一个数量级。 · 混合模拟信号: · 快速,高精度16位ADC、12位DAC、可编程增益放大器、高速比较器和内部参考电压。降低降低系统成本同时具有强大的信号调节,转换和分析能力。 · 人机界面(HMI): · 电容式触摸传感器接口,支持全面低功耗和最小电流加法器。 · 连接与通信: · 支持ISO7816和IrDA协议的UARTs、I2S、CAN、I2C和DSPI · 可靠、安全和加密: · 硬件循环冗余校验内存的内容检查引擎/通讯数据和增加系统可靠性 · 独立时钟的COP,用于保护避免在错误的应用时的程序跑飞。 · 外部看门狗监控 · 时序和控制: · FlexTimers支持通用的、PWM和电机控制功能。 · 用于红外发射波形产生的载波调制器 · 用于RTOS任务调度、ADC转换源和可编程延时模块的可编程中断定时器。 · 扩展接口: · 多功能外部总线接口可以连接外部存储器,门阵列逻辑和液晶。 · 系统: · 具有中断功能的GPIO可以承受5V · 宽工作电压范围在1.71V至3.6V的闪存可编程下降至1.71 V的全功能闪存和模拟外设 · 环境工作温度范围从-40°C到105°C 除了这些通常的特征之外,逐渐增加的功能被加到特定的Kinetis系列,如下图2-2所示。 第49章SPI(DSPI) 49.1 导言 串行设备接口(serial peripheral interface ,SPI)模块提供一个在MCU和一个外部设备之间进行通信的同步串行总线。 49.1.1 框图 SPI(DSPI)的框图如下所示: 图49-1 DSPI框图 49.1.2 特性 DSPI支持三种SPI特性: ?全双工,四线同步传输 ?主机与从机模式 ?持续选择从机,使数据流工作在从机模式下 ?使用有4级TX FIFO缓冲进行传输操作 ?使用有4级RX FIFO缓冲进行接收操作 ?TX与RX的FIFO可以被分别地禁止,低延迟更新到SPI队列 ?TX和RX的FIFO在调试解除时是透明的 ?可对每一帧的传输属性进行编程: ?2个传输属性寄存器 ?可以对串行时钟的极性和相位进行编程 ?多种可编程的延迟 ?串行帧长度可被编程为4到16位,通过软件控制可以扩展 ?可以连续保持片选 ?6个外设片选,可以用复用器扩展到64个 ?通过复用器稳定地支持多达32个设备片选 ?DMA支持附加到TX FIFO的入口并且从RX FIFO中移除入口 ?TX FIFO未满(TFFF) ?RX FIFO未空(RFDF) ?6个中断条件: ?到达队列结尾(EOQF) ?TX FIFO未满(TFFF) ?当前帧传输完成(TCF) ?在发送FIFO为空时试图发送(TFUF) ?RX FIFO未空(RFDF) ?在接收FIFO满时接收帧(RFOF) ?全局中断请求线 ?在与低俗外设进行通信时使用变更的SPI传输格式 ?低功耗结构特性 ?支持停止模式 ?支持休眠模式 49.1.3 DSPI配置 DSPI模块始终工作在SPI配置下。 SPI配置允许DSPI发送和接收串行数据。此配置允许SDPI工作像基本SPI模块一样,使用内部FIFO,支持外部队列操作。发送数据和接收数据在不同的FIFO。主机CPU或一个DMA控制器从接收FIFO读取接收数据,并且写发送数据到发送FIFO。 对于队列操作,SPI队列可以驻留在系统RAM,并扩展到DSPI。队列与SDPI FIFO之间的数据传输由DMA控制器或主机CPU完成。下图中显示了一个系统的样例,其中包含了DMA,DSPI和系统RAM中的扩展队列。 图49-2 DSPI与DMA和RAM 第27章FLASH存储控制器(FMC)27.1 介绍 FLASH存储控制器(FMC)是一个存储加速单元,它提供下面的功能。 在设备和两块非易性存储器之间的一个接口,bank 0 由程序flash组成,bank 1由FlexNVM组成。 可以加速FLASH和FlexNVM数据传输的缓存。 27.1.1 概述 FLASH存储控制器管理设备和双Flash存储器之间的接口。FMC获取详细记录了存储器配置的状态信息,使用该信息可确保接口的正确。下表显示了支持 另外,对bank 0和bank 1来说,FMC提供了3个独立的机制,其作用是加速设备和Flash存储器之间的接口。利用一个64位预缓冲可以预先得到下一个64位flash存储器的位置,利用两个4路,8级缓存和一个单端64位缓冲可以预先存储要访问的flash存储器或者FlexMemory数据。 27.1.2 特征 FMC特征包括: ●设备与双flash存储器和FlexMemory之间的一个接口: ●当程序Flash和FlexNVM用作数据存储器时支持8位、16位、32 位读操作。 ●当FlexNVM和FlexRAM作为EEPROM时,支持8位,16位,32 位读/写操作。 ●对于bank 0和bank 1:读连续的32位空间返回第二个读的数据,没 有等待状态。存储器通过32位总线访问返回64位数据。 ●交叉通路访问功能为每个交叉通路主机设置禁止访问,只读访问, 只写访问,读/写访问功能。 ●加速从程序flash存储器和FlexMemory到设备的数据传输: ●带有主机和bank指令/数据访问控制的64位预测缓冲区 ●4路,8级,每行64位高速缓存,总共32个64位目录,带有替换 1. 硬件最小系统引脚 K60N512VM100芯片电源类引脚,BGA封装22个,LQFP封装27个,其中BGA封装的芯片有五个引脚未使用(A10、B10、C10、M5和L5)。芯片使用多组电源引脚分别为内部电压调节器、I/O引脚驱动、A/D转换电路等电路供电,内部电压调节器为内核和振荡器等供电。为了电源稳定,MCU内部包含多组电源电路,同时给出多处电源引出脚,便于外接滤波电容。为了电源平衡,MCU提供了内部相连的地的多处引出脚,供电路设计使用。 复位引脚RESET是一个专用引脚,内部含有上拉电阻。空闲状态为高电平,低电平迫使芯片复位。在写入器电路中,该引脚被连接到标准的10芯JTAG接口,以便写入器可以使MCU复位。 2.I/O端口资源类引脚 除去需要服务的引脚外,其它引脚可以为实际系统提供I/O服务。芯片提供服务的引脚也可称为I/O端口资源类引脚。MK60N512VMD100(144引脚BGA和LQFP封装)100个I/O引脚名、引脚号及功能描述。许多引脚具有复用功能。这些引脚在复位后,立即被配置为高阻状态,且为通用输入引脚,没有内部上拉电阻。需要注意的是,为了避免来自浮空输入引脚额外的漏电流,应用程序中的复位初始化例程需尽快使能上拉或下拉,也可改变不常用引脚的方向为输出,以使该引脚不再浮空。 ADC、DAC和USB引脚,以下引脚是MK60N512VMD100单独列出来的。 除去需要服务的引脚外,其它引脚可以为实际系统提供I/O服务。芯片提供服务的引脚也可称为I/O端口资源类引脚。MK60N512VMD100(144引脚LQFP封装)的有多达100个I/O引脚。其中A口26个,B口20个,C口20个,D口16个,E口18个,每个引脚均具有多个功能,详细情况请参见表2-表5。 表1 PTA口的26个引脚功能详述 表2 PTB口的20个引脚功能详述 K60核心开发板 快速使用说明 1、K60连接方式: K 60的JTAG的10pin线插接方式,miniUSB也是要插上去的,送的miniUSB是供电给K60的 转接板的插线方式,10pin是连接K60的,20pin是连接Jlink V8或者ulink2的标准JTAG接口 K60和JlinkV8连接后的图 K60和JlinkV8连接后的图 如果要查看串口的输出信息,可以使用TTL转串口的板子, 例程的串口使用的是K60的串口3,串口3可以输出很多调试信息和例程的相关信息。 K60板子上的插针C16和C17就是串口的RXD和TXD。 波特率是115200 K60核心板供电方式可以使用USB接口供电,也可以使用插针位置供电,请注意插针位置供电的选择: 2开发软件的安装: Kinetis_K60(客户资料)\开发软件 这个文件夹下有相关的开发软件,一般推荐IAR开发软件。 IAR-EWARM-EV-CD-6307 安装这个开发软件 IAR_Kegen_PartB,这个是注册机,用来生成IAR的注册码的,win7下使用的时候的,请使用管理员模式运行,否则无法生成正确的注册码。 例如图中已经生成了一个注册码 使用注册机的时候,第一步:先选择对应版本的IAR软件,第二步,点获取注册码,然后根据顺序,将生成的license number复制后,粘贴到IAR的安装要求输入对话框中,下一步将 生成的license key复制,贴到IAR的安装下一步要求输入对话框中,继续点下一步完成安装。注意:win7下使用的时候的,请使用管理员模式运行,否则无法生成正确的注册码。 我们的开发例程都是IAR的 请先安装IAR软件,IAR软件在光盘我们已经配备了 \Kinetis_K60-100(客户资料)\开发软件工具\IAR开发软件及注册机 在这里找到要安装IAR软件:IAR-EWARM-EV-CD-6307 启动后,选择如下图所示的目录,启动IAR软件的安装。 启动安装后,直接点“next”就行了。 第六章复位和启动 6.1 简介 MCU支持的复位源有: 表6-1 复位源 除了EzPort和MDM-AP复位之外,每个系统复位源在系统复位状态寄存器(SRSH和SRSL)都有相应的位。详见模式控制器一章。 EZP_引脚决定的功能模式下选择单片(默认)模式或串行flash编程MCU在CS (EzPort)模式而退出复位状态。详见启动选项。 6.2 复位 此部分讨论基本的复位机制和复位源。一些引发复位的模块可以配置为触发中断。参见各独立外设章节获取更多信息。 6.2.1 上电复位(POR) 当给MCU上电或提供的电压低于上电复位重置电压(V POR)时,POR电路会触发POR 复位。 当电压升高时,LVD电路保持MCU处于复位状态直到电压大于LVD低电压阈值(V LVDL)。POR复位后SRSL寄存器的POR和LVD位亦重设。 6.2.2 系统复位 MCU复位是一种可以使芯片回到初始状态的方法。系统复位起始于全面监管的片上调节器和来自于内部参考的系统时钟发生器。当芯片退出复位时,它按如下顺序操作:·从中断向量表0偏移开始读取开始SP(SP_main) ·从中断向量表4偏移开始读取PC ·LR设置为0xFFFF_FFFF 片上外设模块和非模拟IO引脚最初都被置为禁止。复位之后模拟引脚被默认为相应的模拟功能。 复位时,JTAG相应的输入引脚被配置为: ·TDI上拉(PU) ·TCK下拉(PD) ·TMS上拉 相应的输出引脚被配置为: TDO既不上拉也不下拉 注意到nTRST初始被配置为禁止的,然而一旦被配置为JTAG功能时,它的相应输入引脚被配置为: ·nTRST上拉 6.2.2.1 外部引脚复位(PIN) RESET是一个专用引脚。该引脚开漏和内部上拉。RESET将芯片从任何模式唤醒。在该引脚复位时,SRSL[PIN]被置位。 6.2.2.1.1复位引脚过滤 RESET引脚在所有的模式中都支持数字过滤。对于LLS和VLLSx模式,LLWU提供了一个可选的运行在LPO时钟为1kHz的数值过滤器。过滤操作详见LLWU章节。在非低漏操作中,用于RESET引脚过滤的有两个可选的时钟—1KHzLPO时钟和总线时钟。 RESET引脚过滤在SIM逻辑中实现,每个时钟源包含单独的过滤器。在Stop和VLPS 操作中,此逻辑由选择的的过滤模式决定切换到旁路操作或继续过滤操作。 这里有一些定义的模式—详见SIM模块的SOPT6寄存器描述。SOPT6[RSTFLTEN[2:0]]和SOPT6[RSTFLTSEL[4:0]]域控制所需的功能。每个过滤器复位成POR、LVD后,能从VLLS 唤醒。每个过滤器的复位值都是OFF。 LPO过滤器的过滤值计数固定是3。输入信号有一个2个周期的同步信号。这样,从高到低或从低到高的转换需要5个周期。当LPO过滤禁止时,LPO过滤器的初始化值是OFF (逻辑1)。 当总线过滤没有使能时,总线过滤器的初始化值是OFF(逻辑1)。当总线过滤使能时,总线过滤的过滤计数值由SOPT6[RSTFLTSEL[4:0]]控制。 6.2.2.2 低电平检测(LVD)复位 当给芯片提供可变电压,芯片的低电平检测系统可以保护内存和控制MCU系统状态的。系统由上电复位电路(POR)和低电压检测(LVD)电路组成。对于低电压检测(LVD)电路,用户可选检测电压(高电压(V LVDH)或低电压(VL VDL))。选择LVDSC1[LVDV]位即可选择不同的检查电压。LVD系统在正常运行、等待和停止模式下总是保持使能。LVD系统在VLPx、LLSx和VLLSx模式下总是保持禁止。详细信息参考电源管理控制器(PMC)章节。 通过设置LVDSC1[LVDRE],LVD可以在检测到低电压条件时产生复位。当产生LVD 复位时,LVD系统使MCU处于复位状态直到供应的电压大于LVD低电压阈值。 LVD复位或POR时SRSL[LVD]位被置位。 第24章多用途时钟信号生成器(MCG) 24.1 介绍 多用途多用途时钟信号生成器(MCG)模块为MCU提供多种时钟源选项。这个模块由一个频率环锁(FLL)和一个相位环锁(PLL)组成。FLL可由一个内部或外部参考时钟控制,而PLL可由一个外部参考时钟控制。这个模块要么在FLL或PLL输出时钟之间,要么在内部参考时钟或外部参考时钟之间选择一个时钟源以作为MCU系统时钟。MCG操作与晶体振荡器有关,其中晶体振荡器允许一个外部晶体、陶瓷共振器或外部时钟源产生外部参考时钟。 24.1.1 特性 MCG模块的关键特性: ◆频率环锁(FLL)。 ●数控石晶(DCO)。 ●DCO可设置时钟范围有四个。 ●低频率外部参考时钟源的编程选项和最大DCO输出频率。 ●内外参考时钟可以作为FLL源。 ●可以作为其他片上外设的时钟源。 ◆相位环锁(PLL) ●电压控制振荡器(VCO) ●外部参考时钟作为PLL时钟源。 ●VCO频分模块。 ●相位/频率检测器。 ●集成环过滤器。 ●可以作为其他片上外设的时钟源。 ◆内参考时钟生成器 ●9个微调位的精确慢时钟 ●4个微调位的快时钟 ●可以被用作FLL的时钟源。在FEI模式下,只有慢内参考时钟(IRC)可以被用作FLL源。 ●无论是快时钟还是慢时钟都不能用作MCU的时钟源 ●可以作为其他片上外设的时钟源。 ◆低功耗的石晶时钟发生器位MCG外部参考提供控制信号: ●HGO,RANGE,EREFS ◆从晶振获得外部时钟 ●可被用作FLL或PLL的时钟源 ●可被用作MCU的时钟源 ◆从RTC获得外部时钟 ●只能作为FLL的时钟源 ●只能选择MCU的时钟源 ◆带有重置请求能力的外部时钟监视器,可以在FBE,PEE,BLPE或者FEE模式下对外部时钟进行监测 ◆在PLL中使用的有中断请求能力的锁检测器 ◆外时钟参考的内参考时钟自动裁切功能(ATM)。 ◆FLL和PLL的参考分频。 ◆为其他片上设备提供时钟源的MCG PLL 时钟(MCGPLLCLK) ◆为其他片上设备提供时钟源的MCG FLL时钟(MCGPLLCLK) ◆为其他片上设备提供时钟源的MCG Fixed Frequency时钟(MCGPLLCLK) ◆为其他片上设备提供时钟源的MCG 内参考时钟(MCGPLLCLK) 图24-1 多用途时钟生成器(MCG)框图 第41章低功耗定时器(LPTMR) 41.1 简介 低功耗定时器(LPTMR)可以被配置成定时计数器(采用可选的预分频)或者是脉冲计数器(使用可选的干扰滤波器)在所有的模式中,包括低泄漏模式。它可以从大多数的系统复位事件中继续使用,可达1天的时间。 41.1.1 特点 LPTMR模块的特点包括: 带比较的16位定时计数器或者脉冲计数器 从任意低功耗模式中异步唤醒的可选择中断 硬件触发输出 计数器支持在自由运行模式或复位下比较 可配置预分频/干扰滤波器的时钟源 可配置脉冲计数器输入源 上升沿或下降沿 41.1.2 操作模式 41.1.2.1运行模式 在运行模式中,LPTMR正常运行。 41.1.2.2 等待模式 在等待模式中,LPTMR继续正常运行,可以配置成产生一个中断请求离开低功耗模式。 41.1.2.3 停止模式 在停止模式中,LPTMR继续正常运行,可以配置成产生一个中断请求离开低功耗模式。 41.1.2.4 低泄漏状态 在低泄漏模式中,LPTMR继续正常运行,可以配置成产生一个中断请求离开低功耗模式。 在低泄漏模式中,内部参考时钟是不可用的。 41.1.2.5 调试模式 在调试模式中,LPTMR正常运行。 41.2 LPTMR信号描述 表41-1 LPTMR信号描述 41.2.1 信号的详细描述 41-2 LPTMR接口信号描述 41.3 存储映像和寄存器定义 注意 LPTMR寄存器只有在POR或LVD事件时才会复位。 参照LPTMR功耗和复位详细描述。 LPTMRx存储映像 41.3.1低功耗定时器控制状态寄存器(LPTMRx_CSR) 地址:LPTMR0_CSR—4004_0000h 基址+0h偏移=4004_000 设计师常用尺寸及CMYK颜色表及中文名称 *名片成品:90*54mm,加4个毫米出血为:94*58mm。 *小三折页广告:210*285mm,加6个毫米出血为:216*291mm。 *祥云报纸:390*540mm,加出血为:396*546mm。 *金凤名苑小单页:210*285mm,加4个毫米出血为:214*289mm。 *新兴国际大三折页:420*285mm,加6个毫米出血:426*291mm. *新兴国际大单页:420*285mm,加6个毫米出血:426*291mm. *邯山商场小小单页:185*260,加4个毫米出血:189*264mm。 *江泉公司杂志(包括封面封底):420*285mm,加6个毫米出血:426*291mm. CMYK色谱设计应用 绿色CMYK:C100 M0 Y100 K0 霓虹灯红CMYK: C0 M100 Y60 K0 深蓝CMYK: C60 M80 Y0 K20 风景蓝CMYK: C40 M60 Y0 K40 深蔚蓝CMYK: C60 M80 Y0 K0 深河CMYK: C40 M80 Y0 K20 蓝紫色CMYK: C40 M100 Y0 K0 青紫色CMYK: C40 M60 Y0 K0 葡萄色CMYK:C20 M40 Y0 K40 深紫色CMYK: C20 M40 Y0 K60 复活节紫色CMYK: C20 M40 Y0 K0 黄昏紫CMYK:C20 M40 Y0 K20 淡紫色CMYK:C20 M60 Y0 K0 雄伟紫色CMYK:C20 M60 Y0 K20 淡白紫色CMYK:C0 M20 Y0 K20 紫色CMYK:C0 M40 Y0 K20 浅紫色CMYK:C0 M40 Y0 K0 深紫色CMYK:C0 M60 Y0 K40 紫红色CMYK:C0 M40 Y0 K60 灰土玫瑰CMYK:C0 M40 Y20 K20 粉红色CMYK:C0 M80 Y40 K0 深粉色CMYK:C0 M60 Y40 K0 高贵红色CMYK:C0 M60 Y40 K20 褪色的粉红色CMYK:C0 M40 Y40 K0 梦粉红色CMYK:C0 M60 Y60 K0 砖红色CMYK:C0 M60 Y80 K20 红宝石色CMYK:C0 M60 Y60 K40 胡桃木色CMYK:C0 M20 Y40 K60 沙土色CMYK:C0 M20 Y40 K0 深黄色CMYK:C0 M200 Y100 K0 桃红色CMYK:C0 M40 Y60 K0 浅橙色CMYK:C0 M40 Y80 K0 第54章通用输入输出(GPIO) 54.1 引言 处理器使用零等待方式,以最高性能访问通用输入输出(General Purpose Input and Output,GPIO)模块接口。GPIO寄存器支持任意长度的数据访问。 当引脚被配置为GPIO功能时,GPIO数据方向寄存器与输出数据寄存器控制每个引脚的方向及输出数据。当GPIO引脚被配置为任意数字功能时,GPIO 输入数据寄存器在每个引脚上显示逻辑值,提供相应的端口控制和对有效引脚的中断模块。 通过对于每个端口输出数据寄存器的额外设置、清除和触发写寄存器,通用输出的有效位被支持。 54.1.1 特点 ●快速的通用输入输出 ●在所有数字引脚重用模式中,输入数据寄存器引脚可见。 ●带有相应的设置/清除/触发寄存器的输入数据寄存器引脚 ●数据方向寄存器引脚 ●以零等待状态访问GPIO寄存器 54.1.2 操作模式 54.1.2.1 运行模式 在运行模式,GPIO正常运行。 54.1.2.2等待模式 在等待模式,GPIO正常运行。 54.1.2.3停止模式 在停止模式中,GPIO无效,尽管引脚仍然保持它们的状态。 54.1.2.4 调试模式 在调试模式中,GPIO正常运行。 54.1.3 GPIO引脚描述 表54-1 GPIO信号描述 注:并不是每个设备的每个端口上的所有引脚都是可用的。 54.1.3.1 详细的GPIO引脚说明 表54-2 GPIO详细的接口信号描述 54.2 内存映射与寄存器定义 任何对GPIO内存空间以外的合法空间地址的任意读写访问都将会导致总线错误。带有零等待状态的所有寄存器访问完成,除了带有一个等待状态的错误访问。 GPIOx 内存映射 第38章可编程延时模块(Programmable Delay Block,PDB) 注意:有关此模块的特定芯片的实现详细信息实例,请参阅芯片配置一章。 38.1 概述 PDB可以为内部或外部触发源提供可控制的延时,可以为ADC的硬件触发输入或为DAC的产生提供可编程的间隔。这样就可以为ADC转换和DAC输出的完成提供精确的时间。PDB模块还可以提供脉冲输出,就跟CMP模块中的采样窗口一样。 38.1.1 特性 1.多达15种输入触发中断源和软件触发中断源 2.多达8路的可配置PDB通道 一个PDB模块对应一个ADC 为每个PDB 通道ADC 触发器选择一个触发器输出的ADC 硬件触发器和多达8 个预输出 每个输出有一个16位的延时寄存器 可选的旁路电阻 运行模式有单次触发模式和连续模式 背靠背模式,可以使得ADC转换完成后触发下个PDB通道 可编程的延时中断 顺序错误中断 每个触发器有一个通道标志和一个顺序错误标志 支持DMA 3.高达8路的DAC内部触发源 每个DAC模块有一个内部触发输出 每个DAC触发输出有一个16位的内部延时寄存器 可选旁路延迟时间间隔触发寄存器 可选的外部触发源 4.高达8路的脉冲输出 脉冲输出可以独立的使能或禁止 脉宽可调 注意:PDB 的数量的输入和输出出发是与特定芯片有关的。详细信息请参阅芯片配置信息。 38.1.2 实现 下面的字母表示触发数量: 1.N-总的可用的PDB通道数 2.n-PDB通道号,范围0~N-1 3.M-每个PDB通道的总得可用的触发器 4.m-触发号,范围0~M-1 5.X-总的DAC内部触发数量 6.x-DAC内部触发号,范围0~X-1 7.Y-总的脉冲输出 8.y-脉冲输出号,范围0-Y-1 注意:模块输出的数量触发的核心是与特定芯片的。输出触发执行的核心模块,请参阅芯片配置信息。 38.1.3 背靠背的确认连接 PDB背靠背操作确认连接是与具体芯片有关的。关于实现,参考芯片配置说明。 38.1.4 DAC外部触发输入连接 DAC的外部触发输入连接的实现是与具体芯片有关的。详情参考芯片配置说。 【响应社区号召】野火新版K60代码与教程(2012年12月28日)GPIO 我们例程的特点是可以像51那样容易操作单个IO管脚,也提供函数接口来多个IO口操作。 为了让初学者更好地熟悉GPIO操作,我们提供了多个例程 51+编程风格的+GPIO+实验输入输出测试.rar 51编程风格的GPIO实验输出测试.rar GPIO+实验并行读写测试.rar GPIO+实验简单函数调用测试.rar GPIO+实验综合测试.rar LED 其实跟GPIO一致的,只不过更加熟悉GPIO操作。 LED实验简单测试.rar LED+综合测试例程.rar key 与常规的使用延时去抖的不同,野火的按键例程,使用定时扫描,更加稳定高效,而且还支持按键短按、长按、弹起动作,处理灵活。 一般大学生都是喜欢用延时去抖的,但那样消耗太多CPU时间,一般的项目开发都不会采用这种方案,而是采用定时扫描方案。 按键实验测试.rar EXTI 其实是PORT的功能,与GPIO也有关系,我们命名为EXTI,即外部中断的意思 EXTI外部中断实验综合测试.rar UART 串口查询接收例程.rar 串口发送例程.rar 串口中断接收例程.rar ADC&DAC 有了DAC后,产生方波,三角波、正弦波就简单了,就这样可以做成一个信号发生器 当然也可以做一个示波器啦,通过ADC来测量电压。 如果要做成录音功能,ADC只有16bit,与一般的MP3等真正产品的24bit 差距有点大了。 DAC播放音乐的话,12bit也只能做到能听清楚。 ADC如果要多路的话,就要DMA了…… ADC+综合测试例程.rar DAC+实验+ADC+测试.rar DAC+实验+LED+测试.rar DAC+实验万用表测试.rar FTM FTM 可实现输入捕捉、输出比较、PWM等功能。 我们的PWM例程是自动计算频率,不同系统频率下,初始化PWM后自动计算对应的频率。飞思卡尔K60 DMA 中文手册

K60(Rev6-Ch12-SIM)(Chinese)

K60时钟分配(中文)

K60P144M100SF2RM_CN_02

K60(Rev6-Ch14-Power Management Controller)(中文)

FPGA可编程逻辑器件芯片XQ4VK60-10FF1148M中文规格书

K60 介绍 (中文)

K60(Rev6-Ch49-SPI)(中文)

K60-flash-FMC(中文)

K60芯片详述

K60快速使用手册

Ch06-RstBoot(k60中文)

K60(Rev6-Ch24-MCG)(中文)

K60(Rev6-Ch41-LPTMR)(中文)(1)

CMYK颜色表及中文名称

K60(Rev6-Ch54-GPIO)(中文)

K60(Rev6-Ch38-PDB)(中文)

野火新版K60代码与教程