CD4017中文资料

4017中文资料

CD4017:十进制计数器/脉冲分配器CD4017 是5 位Johnson 计数器,具有10 个译码输出端,CP、CR、INH 输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH 为低电平时,计数器在时钟上升沿计数;反之,计数功能无效。

CR 为高电平时,计数器清零。

Johnson 计数器,提供了快速操作、2 输入译码选通和无毛刺译码输出。

防锁选通,保证了正确的计数顺序。

译码输出一般为低电平,只有在对应时钟周期内保持高电平。

在每10 个时钟输入周期CO 信号完成一次进位,并用作多级计数链的下级脉动时钟。

CD4017 提供了16 引线多层陶瓷双列直插(D)、熔封陶瓷双列直插(J)、塑料双列直插(P) 和陶瓷片状载体(C)4 种封装形式

推荐工作条件

电源电压范围:3V-15V 输入电压范围:0V-VDD 工作温度范围M 类:55℃-125℃ E 类:40℃-85℃

极限值

电源电压:-0.5V-18V 输入电压:-0.5V-VDD 十0.5V 输入电流:±10mA 贮存温度:-65℃-150℃

引出端功能符号

CO:进位脉冲输出CP:时钟输入端CR:清除端INH:禁止端Q0-Q9 计数脉冲输出端VDD:正电源VSS:地。

cd4017工作原理

cd4017工作原理

CD4017是一种常见的十进制计数器芯片,它可以将输入信号

按照顺序分配到10个输出引脚上。

该芯片是由一个主计数器

和一个辅助计数器组成的。

主计数器用于存储当前的计数值,辅助计数器则用于控制主计数器的计数顺序。

在CD4017工作时,首先要保证RESET引脚的电平为低电平,这样可以将主计数器复位为初始状态。

其次,时钟信号(CLOCK)被输入到CLOCK引脚上,当CLOCK信号的边沿触

发器工作时,主计数器就会根据时钟信号的变化进行计数。

当计数达到10时,主计数器会自动重置为0,并且辅助计数器

会自动加1。

辅助计数器的输出由十个输出引脚(Q0-Q9)表示。

对于每个输

入时钟脉冲,辅助计数器会使得相应的输出引脚(Q0-Q9)变为

高电平,而其他的输出引脚则保持低电平。

这样,我们可以通过检测Q0-Q9引脚的电平变化来实现对输入信号的分配。

需要注意的是,CD4017只能实现十进制的计数,而且它是一

个顺序计数器,即每次只能计数1个单位。

如果需要实现其他进制或者多单位的计数,就需要使用其他的计数器芯片。

通过这样的工作原理,CD4017计数器芯片能够在很多电子电

路中实现各种不同的功能,比如时序控制、信号分配等。

CD40174,CD40175中文资料

VDD=5V

230

400

NS

VDD=10V

90

150

VDD=15V

75

120

tSU

Time Prior to Clock Pulse that

Data must be Present

VDD=5V

45

100

NS

VDD=10V

15

40

VDD=15V

VDD=5V

1=10V

75

110

VDD=15V

60

90

tPHL

Propagation Delay Time to a

Logical “0” from Clear to Q

VDD=5V

180

300

NS

VDD=10V

70

110

VDD=15V

60

90

tPLH

Propagation Delay Time to a Logical

CD40174,CD40175中文资料

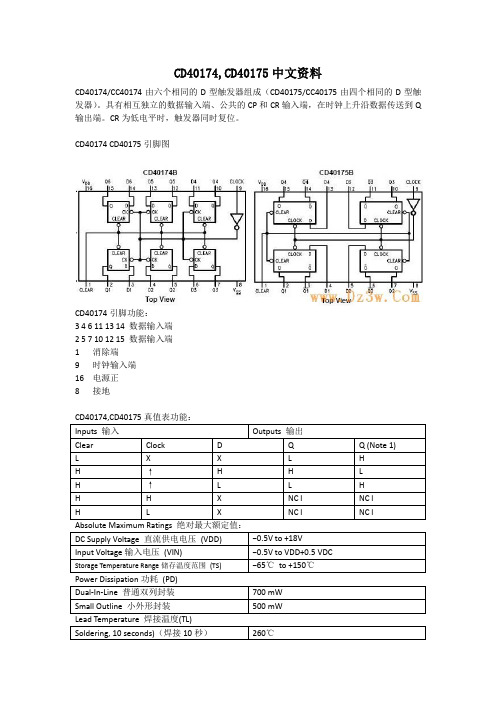

CD40174/CC40174由六个相同的D型触发器组成(CD40175/CC40175由四个相同的D型触发器)。具有相互独立的数据输入端、公共的CP和CR输入端,在时钟上升沿数据传送到Q输出端。CR为低电平时,触发器同时复位。

CD40174 CD40175引脚图

13

35

tH

Time after Clock Pulse that

Data Must be Held

VDD=5V

VDD=10V

-11

0

NS

-4

0

VDD=15V

CD4017中文资料内容说明及其运用

CD4017中文资料内容说明及其运用电子制作2009-11-14 20:09:21 阅读5119 评论1 字号:大中小订阅cd4017中文资料内容说明cd4017中文资料内容说明:CD4017 是5 位Johnson 计数器,具有10 个译码输出端,CP、CR、INH 输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH 为低电平时,计数器在时钟上升沿计数;反之,计数功能无效。

CR 为高电平时,计数器清零。

Johnson 计数器,提供了快速操作、2 输入译码选通和无毛刺译码输出。

防锁选通,保证了正确的计数顺序。

译码输出一般为低电平,只有在对应时钟周期内保持高电平。

在每10 个时钟输入周期CO 信号完成一次进位,并用作多级计数链的下级脉动时钟。

CD4017 提供了16 引线多层陶瓷双列直插(D)、熔封陶瓷双列直插(J)、塑料双列直插(P)和陶瓷片状载体(C)4 种封装形式。

引出端功能符号CO:进位脉冲输渊CP:时钟输入端CR:清除端INH:禁止端Q0-Q9 计数脉冲输出端VDD:正电源VSS:地CD4017组成的防抖动触摸开关电路这是一个实用点触发电路,可以方便的与各种电路组合使用,温度控制,光控,声控,射频遥控。

而只需把这些信号加到CD4017的CP端。

本电路使用一片十进制计数器CD4017,输出Y2和复位端RST相接,14脚每次到两个记数脉冲既复位。

其工作原理是220伏交流电经变压器降压、D1-D4整流、C1滤波后获得+9V直流电压。

C3、R2构成上电复位电路,CD4017复位后Y0输出高电平,Y1和Y2输出低电平,三极管V导通。

继电器吸合,其常开触点接通用电器。

K被按下后,C2迅速放电,14脚获得脉冲上升沿,触发CD4017记数,使Y0输出低电平,Y2仍保持低电平。

此时三极管V截止,继电器释放,用电器断电。

再次按下K时,C2再次放电,14脚又获得一个记数脉冲,CD4017的Y0和Y1输出低电平,Y2输出高电平,通过二极管D5将CD4017复位,Y0 输出高电平,Y1和Y2输出低电平,三极管V再次导通,继电器吸合。

CD4017中文资料_数据手册_参数

-55 to 125 -55 to 125

-55 to 125

Level-1-260C-UNLIM -55 to 125

Level-1-260C-UNLIM -55 to 125

Level-1-260C-UNLIM -55 to 125

Level-1-260C-UNLIM -55 to 125

Level-1-260C-UNLIM -55 to 125

Device Marking

(4/5)

CD4017BE CD4017BE CD4017BF CD4017BF3A

CD4017BM CD4017BM CD4017BM CD4017BM CD4017B CD4017B CM017B CM017B CM017B CM017B CD4022BE CD4022BE

(1)

Drawing

Qty

OBSOLETE

0

ACTIVE

PDIP

N

16

25

ACTIVE

PDIP

N

16

25

ACTIVE

CDIP

J

16

1

Eco Plan

(2)

TBD

Pb-Free (RoHS)

Pb-Free (RoHS)

TBD

ACTIVE

CDIP

J

16

1

TBD

OBSOLETE ACTIVE

CDIP SOIC

Samples

Addendum-Page 1

PACKAGE OPTION ADDENDUM

10-Jun-2014

Orderable Device CD4022BF

CD4022BF3A CD4022BNSR CD4022BNSRE4 CD4022BPW CD4022BPWE4 CD4022BPWR CD4022BPWRE4 CD4022BPWRG4 JM38510/05651BEA M38510/05651BEA

cd4017

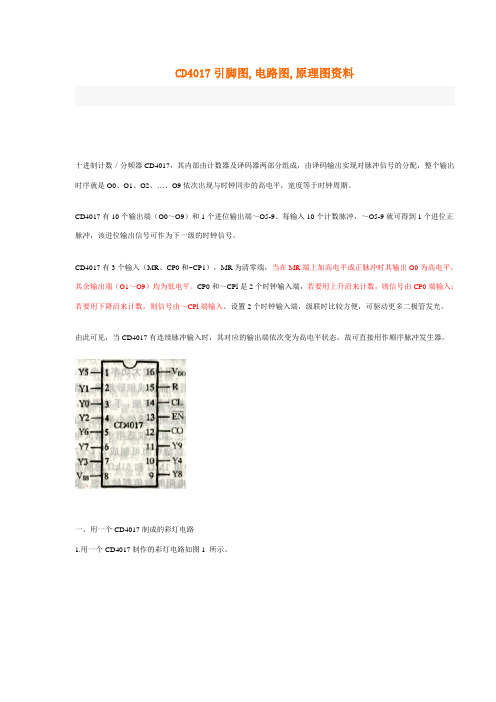

CD4017引脚图,电路图,原理图资料十进制计数/分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。

CD4017有10个输出端(O0~O9)和1个进位输出端~O5-9。

每输入10个计数脉冲,~O5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。

CD4017有3个输入(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出O0为高电平,其余输出端(O1~O9)均为低电平。

CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。

设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。

由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。

一、用一个CD4017制成的彩灯电路1.用一个CD4017制作的彩灯电路如图1 所示。

2.电路工作原理CD4017输出高电平的顺序分别是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚的高电平使6串彩灯向右顺序发光,⑤、⑥、③脚的高电平使6串彩灯由中心向两边散开发光。

各种发光方式可按自己的需要进行具体的组合,若要改变彩灯的闪光速度,可改变电容C1的大小。

二、用三个CD4O17彩灯电路图CD4017的级连,如图2所示。

2.CD4017级连后可以顺序输出24个高电平,同上理可组合出各种不同的发光方式,见图3,可使6串彩灯向右流水发光,再向左流水发光,中心向两边散开后再向中心靠拢发光,1、3、5、2、4、6串间隔发光等等CD4017 是5 位Johnson 计数器,具有10 个译码输出端,CP、CR、INH 输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

数字电路CD4017的原理及应用电路

数字电路CD4017得原理及应用电路数字电路CD4017就是十进制计数/分频器,它得内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号得分配,整个输出时序就就是Q0、Q1、Q2、…、Q9依次出现与时钟同步得高电平,宽度等于时钟周期。

CD4017有10个输出端(Q0~Q9)与1个进位输出端~Q5-9。

每输入10个计数脉冲,~Q5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级得时钟信号。

CD4017有3个输(MR、CP0与~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出Q0为高电平,其余输出端(Q1~Q9)均为低电平。

CP0与~CPl 就是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。

设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。

由此可见,当CD4017有连续脉冲输入时,其对应得输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。

CD4017有两个时钟端 CP 与 EN,若用时钟脉冲得上沿计数,则信号从 CP 端输入;若用下降沿计数,则信号从 EN 端输入。

设置两个时钟端就是为了级联方便。

CD4017 与 CD4022 就是一对姊妹产品,主要区别就是 CD4022 就是八进制得,所以译码输出仅有 Y0~Y7,每输入 8 个脉冲周期,就可得到一个进位输出,它们得管脚相同,不过 CD4022 得 6、9 脚就是空脚。

cd4017方框图cd4017引脚图一、用一个CD4017制成得彩灯电路1、用一个CD4017制作得彩灯电路如图1 所示。

cd4017电路图2、电路工作原理CD4017输出高电平得顺序分别就是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚得高电平使6串彩灯向右顺序发光,⑤、⑥、③脚得高电平使6串彩灯由中心向两边散开发光。

各种发光方式可按自己得需要进行具体得组合,若要改变彩灯得闪光速度,可改变电容C1得大小。

cd4017工作原理及应用电路图

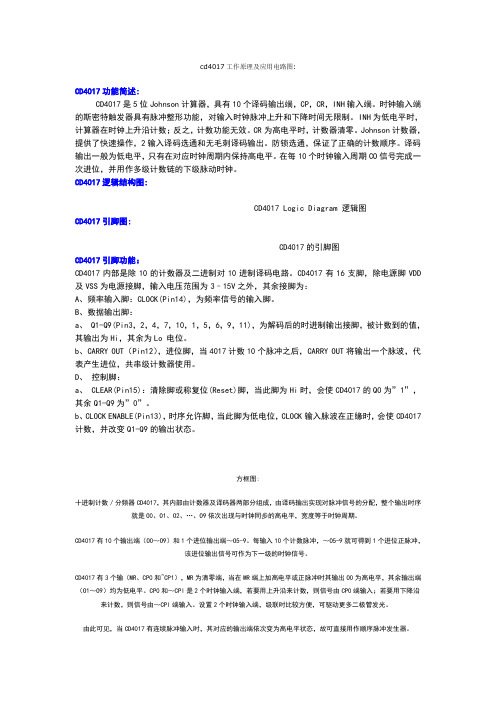

cd4017工作原理及应用电路图:CD4017功能简述:CD4017是5位Johnson计算器,具有10个译码输出端,CP,CR,INH输入端。

时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。

INH为低电平时,计算器在时钟上升沿计数;反之,计数功能无效。

CR为高电平时,计数器清零。

Johnson计数器,提供了快速操作,2输入译码选通和无毛刺译码输出。

防锁选通,保证了正确的计数顺序。

译码输出一般为低电平,只有在对应时钟周期内保持高电平。

在每10个时钟输入周期CO信号完成一次进位,并用作多级计数链的下级脉动时钟。

CD4017逻辑结构图:CD4017 Logic Diagram 逻辑图CD4017引脚图:CD4017的引脚图CD4017引脚功能:CD4017内部是除10的计数器及二进制对10进制译码电路。

CD4017有16支脚,除电源脚VDD 及VSS为电源接脚,输入电压范围为3–15V之外,其余接脚为:A、频率输入脚:CLOCK(Pin14),为频率信号的输入脚。

B、数据输出脚:a、 Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为解码后的时进制输出接脚,被计数到的值,其输出为Hi,其余为Lo 电位。

b、CARRY OUT(Pin12),进位脚,当4017计数10个脉冲之后,CARRY OUT将输出一个脉波,代表产生进位,共串级计数器使用。

D、控制脚:a、 CLEAR(Pin15):清除脚或称复位(Reset)脚,当此脚为Hi时,会使CD4017的Q0为”1”,其余Q1-Q9为”0”。

b、CLOCK ENABLE(Pin13),时序允许脚,当此脚为低电位,CLOCK输入脉波在正缘时,会使CD4017计数,并改变Q1-Q9的输出状态。

方框图:十进制计数/分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

10-5

0.3

1.0

AC Electrical Characteristics交流电气特性:

Symbol符号

Parameter参数

Conditions条件

最小

典型

最大

Units单位

CLOCK OPERATION运行时钟

tPHL, tPLH

Propagation Delay Time Carry Out Line

b、CARRY OUT(Pin12),进位脚,当4017计数10个脉冲之后,CARRY OUT将输出一个脉波,代表产生进位,共串级计数器使用。

D、控制脚:

a、CLEAR(Pin15):清除脚或称复位(Reset)脚,当此脚为Hi时,会使CD4017的Q0为”1”,其余Q1-Q9为”0”。

b、CLOCK ENABLE(Pin13),时序允许脚,当此脚为低电位,CLOCK输入脉波在正缘时,会使CD4017计数,并改变Q1-Q9的输出状态。

VDD = 5V

125

250

ns

VDD = 10V

45

90

VDD = 15V

35

70

trCL, tfCL

Clock Rise and Fall Time时钟上升和下降时间

VDD = 5V

20

ms

VDD = 10V

15

VDD = 15V

5

tSU

Minimum Clock Inhibit Data Setup Time最小时钟抑制数据设置时间

VOL

LOW Level Output Voltage输出低电平电压

|IO| < 1.0μA

VDD = 5V

0.05

0

0.05

0.05

V

VDD = 10V

0.05

0

0.05

0.05

VDD = 15V

0.05

0

0.05

0.05

VOH

HIGH Level Output Voltage输出高电平电压

|IO| < 1.0μA

0.44

0.88

0.36

mA

VDD = 10V, VO = 0.5V

1.3

1.1

2.25

0.9

VDD = 15V, VO = 1.5V

3.6

3.0

8.8

2.4

IOH

HIGH Level Output Current输出高电平电流(Note 3)

VDD = 5V, VO = 4.6V

-0.2

-0.16

CD4017引脚功能:

CD4017内部是除10的计数器及二进制对10进制译码电路。CD4017有16支脚,除电源脚VDD及VSS为电源接脚,输入电压范围为3–15V之外,其余接脚为:

A、频率输入脚:CLOCK(Pin14),为频率信号的输入脚。

B、数据输出脚:

a、Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为*后的时进制输出接脚,被计数到的值,其输出为Hi,其余为Lo电位。

-65℃to 150℃

Power Dissipation功耗(PD)

Dual-In-Line普通双列封装

700 mW

Small Outline小外形封装

500 mW

Lead Temperature焊接温度(TL)

Soldering, 10 seconds)(焊接10秒)

260℃

Recommended Operating Conditions建议操作条件:

200

400

VDD = 15V

160

320

tTLH, tTHL

Transition Time Carry Out and Decode Out Lines tTLH

VDD = 5V

200

360

ns

VDD = 10V

100

180

VDD = 15V

80

130

tTHL

VDD = 5V

100

200

VDD = 10V

Symbol符号

Parameter参数

Conditions条件

பைடு நூலகம்-40℃

25°

85℃

Units单位

最小

最大

最小

典型

最大

最小

最大

IDD

Quiescent Device Current静态电流

VDD = 5V

20

0.5

20

150

μA

VDD = 10V

40

1.0

40

300

VDD = 15V

80

5.0

80

600

VDD = 5V

4.95

4.95

5

4.95

V

VDD = 10V

9.95

9.95

10

9.95

VDD = 15V

14.95

14.95

15

14.95

VIL

LOW Level Input Voltage输入低电平电压

|IO| < 1.0μA

VDD = 5V, VO = 0.5V or 4.5V

1.5

1.5

1.5

DC Supply Voltage直流供电电压(VDD)

3 VDC to 15 VDC

Input Voltage输入电压(VIN)

0 to VDD VDC

Operating Temperature Range工作温度范围(TA)

-40℃to 85℃

DC Electrical Characteristics直流电气特性:

50

100

VDD = 15V

40

80

fCL

Maximum Clock Frequency最大时钟频率

VDD = 5V

Measured with

1.0

2

MHz

VDD = 10V

Respect to Carry

2.5

5

VDD = 15V

Output Line

3.0

6

tWL, tWH

Minimum Clock Pulse Width最小时钟脉冲宽度

-0.36

-0.12

mA

VDD = 10V, VO = 9.5V

-0.5

-0.4

-0.9

-0.3

VDD = 15V, VO = 13.5V

-1.4

-1.2

-3.5

-1.0

IIN

Input Current输入电流

VDD = 15V, VIN = 0V

-0.3

-10-5

-0.3

-1.0

μA

VDD = 15V, VIN = 15V

V

VDD = 10V, VO = 1.0V or 9.0V

3.0

3.0

3.0

VDD = 15V, VO = 1.5V or 13.5V

4.0

4.0

4.0

VIH

HIGH Level Input Voltage输入高电平电压

|IO| < 1.0μA

VDD = 5V, VO = 0.5V or 4.5V

3.5

VDD = 5V

415

800

ns

VDD = 10V

160

320

VDD = 15V

130

250

Carry Out Line

VDD = 5V

240

480

ns

VDD = 10V

CL=15pF

85

170

VDD = 15V

70

140

Decode Out Lines

VDD = 5V

500

1000

ns

VDD = 10V

CD4017电气参数:

Absolute Maximum Ratings绝对最大额定值:

DC Supply Voltage直流供电电压(VDD)

-0.5 VDC to 18 VDC

Input Voltage输入电压(VIN)

-0.5 VDC to VDD 0.5 VDC

Storage Temperature贮藏温度(TS)

VDD = 5V

120

240

ns

VDD = 10V

40

80

VDD = 15V

32

65

CIN

Average Input Capacitance平均输入电容

5

7.5

pF

CD4017中文资料

CD4017逻辑结构图:

CD4017引脚图:

CD4017功能简述:

CD4017是5位Johnson计算器,具有10个译码输出端,CP,CR,INH输入端。时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。INH为低电平时,计算器在时钟上升沿计数;反之,计数功能无效。CR为高电平时,计数器清零。Johnson计数器,提供了快速操作,2输入译码选通和无毛刺译码输出。防锁选通,保证了正确的计数顺序。译码输出一般为低电平,只有在对应时钟周期内保持高电平。在每10个时钟输入周期CO信号完成一次进位,并用作多级计数链的下级脉动时钟。

3.5

3.5

V

VDD = 10V, VO = 1.0V or 9.0V

7.0

7.0

7.0

VDD = 15V, VO = 1.5V or 13.5V

11.0

11.0

11.0

IOL

LOW Level Output Current输出低电平电流(Note 3)