6.2.8 时序逼近[共4页]

FPGA设计流程 ppt课件

第2章 FPGA设计流程

(3) 当系统存储器内容编辑器(In-System Memory Content Editor)允许运行时,独立于设计的系统时钟,来查看和修改RAM、 ROM或者寄存器内容。

(4) RTL Viewer及Technology Map Viewer也可以用于调试。 (5) 可以将芯片编辑器(Chip Editor)与SignalTapⅡ以及 SignalProbe调试工具一起使用,加快设计验证,并逐步修复在设 计验证期间未解决的错误。运行SignalTapⅡ逻辑分析仪或使用 SignalProbe功能验证信号之后,可以使用Chip Editor来查看编译后 布局布线的详细信息。还可以使用Resource Property Editor 对逻辑 单元、I/O单元或PLL的属性和参数进行编译后的编辑,而不需要 执行完整的重新编译。

第2章 FPGA设计流程

3) 综合(Synthesis) (1) 可以使用分析和综合(Analysis & Synthesis)模块分析设计 文件,建立工程数据库。Analysis & Synthesis 使用QuartusⅡ Integrated Synthesis 综合Verilog(.v)或者VHDL设计文件(.vhd)。根 据需要可以使用其他EDA综合工具综合Verilog HDL或VHDL设计 文件,然后生成QuartusⅡ软件使用的EDIF网表文件(.edf)或者 Verilog Quartus Mapping File (.vqm)。 (2) 设计助手(Design Assistant)依据设计规则,检查设计的可 靠性。 (3) 通过RTL Viewer可以查看设计的原理图,RTL Viewer包 括原理图视图,同时也包括层次结构列表,列出整个设计网表的 实例、基本单元、引脚和网络。

QuartusII操作指南

6.3 Quartus II操作指南6.3.1简介Altera技术领先的Quartus II设计软件配合一系列可供客户选择的IP核,可使设计人员在开发和推出FPGA、CPLD和结构化ASIC设计的同时,获得无与伦比的设计性能、一流的易用性以及最短的市场推出时间。

这是设计人员首次将FPGA移植到结构化ASIC 中,能够对移植以后的性能和功耗进行准确的估算。

Quartus II软件支持VHDL和Verilog硬件描述语言(HDL)的设计输入、基于图形的设计输入方式以及集成系统级设计工具。

Quartus II软件可以将设计、综合、布局和布线以及系统的验证全部都整合到一个无缝的环境之中,其中还包括和第三方EDA工具的接口。

Quartus II的主要特性有:<1>基于模块的设计方法提供工作效率<2>更快集成IP<3>在设计周期的早期对I/0引脚进行分配和确认<4>存储器编译器<5>支持CPLD、FPGA和基于HardCopy 的ASIC<6>使用全新的命令行和脚本功能自动化设计流程<7>高级教程帮助深入了解Quartus II的功能特性。

Altera公司的Quartus II软件提供了可编程片上系统(SOPC)设计的一个综合开发环境,是进行SOPC设计的基础。

Quartus II集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件(PLD)设计,综合,布局和布线,验证和仿真。

Quartus II设计软件根据设计者需要提供了一个完整的多平台开发环境,它包括整个FPGA和CPLD设计阶段的解决方案。

有关Quartus II的典型设计流程如图6-43所示。

1图6-43 Quartus II的典型设计流程此外,Quartus II软件为设计流程的每个阶段提供了Quartus II图形用户界面、EDA 工具界面和命令行界面。

FPGA官方学习网

-------------------------------------------------------------------------------

https:///etraining/webex/Verilog_CN/Verilog_CN.zip

-------------------------------------------------------------------------------

To run the course off line:

/customertraining/webex/Foundation_CN/CH_Foundation.zip

-------------------------------------------------------------------------------

https:///etraining/webex/ReadMeFirst_CN/ReadMeFirst_CN.zip

-------------------------------------------------------------------------------

https:///etraining/webex/STAP_CN/STAP_CN.zip

-------------------------------------------------------------------------------

/customertraining/webex/CycloneIV_CN/CycloneIV_CN.zip

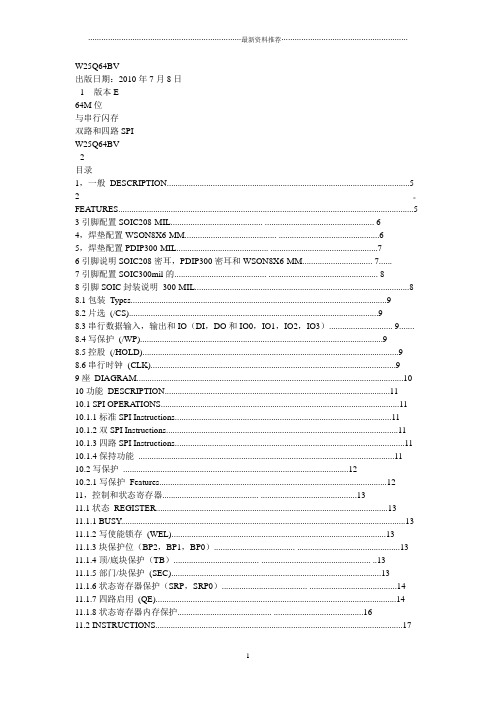

W25Q64中文资料精编版

W25Q64BV出版日期:2010年7月8日- 1 - 版本E64M位与串行闪存双路和四路SPIW25Q64BV- 2 -目录1,一般DESCRIPTION (5)2。

FEATURES (5)3引脚配置SOIC208-MIL.......................................... .. (6)4,焊垫配置WSON8X6-MM.......................................... . (6)5,焊垫配置PDIP300-MIL.......................................... . (7)6引脚说明SOIC208密耳,PDIP300密耳和WSON8X6-MM................................ 7......7引脚配置SOIC300mil的.......................................... .. (8)8引脚SOIC封装说明300-MIL (8)8.1包装Types (9)8.2片选(/CS) (9)8.3串行数据输入,输出和IO(DI,DO和IO0,IO1,IO2,IO3)............................. 9.......8.4写保护(/WP) (9)8.5控股(/HOLD) (9)8.6串行时钟(CLK) (9)9座DIAGRAM (10)10功能DESCRIPTION (11)10.1 SPI OPERATIONS (11)10.1.1标准SPI Instructions (11)10.1.2双SPI Instructions (11)10.1.3四路SPI Instructions (11)10.1.4保持功能 (11)10.2写保护 (12)10.2.1写保护Features (12)11,控制和状态寄存器............................................ .. (13)11.1状态REGISTER (13)11.1.1 BUSY (13)11.1.2写使能锁存(WEL) (13)11.1.3块保护位(BP2,BP1,BP0)..................................... .. (13)11.1.4顶/底块保护(TB)....................................... .................................................. ..1311.1.5部门/块保护(SEC) (13)11.1.6状态寄存器保护(SRP,SRP0)....................................... . (14)11.1.7四路启用(QE) (14)11.1.8状态寄存器内存保护........................................... .. (16)11.2 INSTRUCTIONS (17)11.2.1制造商和设备标识........................................... .. (17)11.2.2指令集表1 (18)W25Q64BV11.2.3指令表2(阅读说明书)....................................... (19)出版日期:2010年7月8日- 3 - 修订版E11.2.4写使能(06h) (20)11.2.5写禁止(04h) (20)11.2.6读状态寄存器1(05H)和读状态寄存器2(35H).............................. (21)11.2.7写状态寄存器(01H)......................................... .................................................. .. (22)11.2.8读取数据(03h) (23)11.2.9快速阅读(0Bh) (24)11.2.10快速读双输出(3BH)........................................ .................................................. 0.25 11.2.11快速读四路输出(6BH)........................................ .. (26)11.2.12快速读双I / O (BBh) (27)11.2.13快速读取四I/ O (EBh) (29)11.2.14八进制字读取四I/ O(E3H)..................................... (31)11.2.15页编程(02h) (33)11.2.16四路输入页编程(32H)........................................ . (34)11.2.17扇区擦除(20H) (35)11.2.1832KB的块擦除(52H) (36)11.2.1964KB的块擦除(D8h) (37)20年2月11日芯片擦除(C7H/ 60h) (38)21年2月11日擦除挂起(75h) (39)22年2月11日擦除恢复(7Ah) (40)23年11月2日掉电(B9h) (41)24年2月11日高性能模式(A3H)......................................... (42)25年2月11日发布掉电或高性能模式/设备ID(ABH) (42)26年2月11日读制造商/设备ID(90H)....................................... . (44)27年2月11日阅读唯一的ID号(4BH)........................................ . (45)28年2月11日读JEDEC的ID (9Fh) (46)29年2月11日连续读取模式复位(FFH或FFFFH)...................................... .. (47)12,电气特性.............................................. (48)12.1绝对最大Ratings (48)12.2操作范围 (48)12.3上电时序和写抑制阈值......................................... (49)12.4直流电气Characteristics (50)12.5 AC测量条件.............................................. .. (51)12.6 AC电气Characteristics (52)12.7 AC电气特性(续)......................................... . (53)12.8串行输出Timing (54)12.9输入Timing (54)12.10持有Timing (54)13包装SPECIFICATION (55)W25Q64BV13.18引脚SOIC208密耳(包装代号SS)..................................... .. (55)- 4 -13.28引脚PDIP300密耳(封装代码DA)..................................... (56)13.38触点WSON8x6毫米(封装代码ZE)....................................... (57)13.416引脚SOIC300密耳(封装代码SF)..................................... . (58)14订货INFORMA TION (59)14.1有效的部件号和顶端标记.......................................... (60)15版本HISTORY (61)W25Q64BV出版日期:2010年7月8日- 5 - 修订版E1概述该W25Q64BV(64M位)串行Flash存储器提供了有限的系统存储解决方案空间,引脚和电源。

计算机组成原理(十二条指令)

计算机学院计算机科学与技术专业《计算机组成原理课程设计》报告(2008/2009学年第一学期)学生姓名:闫全胜学生班级:计算机062202H学生学号: 200620030227指导教师:康葆荣2009年1月3日目录1 关于此次课程设计 (2)1.1 设计的目的: (2)1.2 设计内容及要求: (2)2 分析阶段 (3)2.1指令译码电路分析 (3)2.2 寄存器译码电路分析 (4)2.3 微指令格式分析 (5)2.4 时序分析 (6)3 初步设计阶段 (7)3.1 数据格式 (7)3.2指令描述 (7)3.3 存储器分区 (9)3.4 控制台微程序流程: (10)3.5 运行微程序 (11)4 详细设计阶段 (12)4.1控制台流程分解 (12)4.2 运行微程序子流程 (15)4.3 微程序总流程图 (24)5 实现阶段 (25)5.1 所用模型机数据通路的介绍 (25)5.2 微程序代码设计与编写 (26)微程序二进制代码表 (26)5.3 机器指令的输入及运行 (28)心得体会 (30)参考资料 (31)1 关于此次课程设计1.1 设计的目的:本课程设计是计算机科学与技术专业重要的实践性教学环节之一,是在学生学习完《计算机组成原理》课程后进行的一次全面的综合设计。

目的是通过一个完整的8位指令系统结构(ISA)的设计和实现,加深对计算机组成原理课程内容的理解,建立起整机系统的概念,掌握计算机设计的基本方法,培养学生科学的工作作风和分析、解决实际问题的工作能力。

1.2 设计内容及要求:基于TDN-CM++计算机组成原理实验教学系统,设计和实现一个8位指令系统结构(ISA),通过调试和运行,使设计的计算机系统能够完成指定的功能。

设计过程中要求考虑到以下各方面的问题:1、指令系统风格(寄存器-寄存器,寄存器-存储器,存储器-存储器);2、数据类型(无符号数,有符号数,整型,浮点型);3、存储器划分(指令,数据);4、寻址方式(立即数寻址,寄存器寻址,直接寻址等);5、指令格式(单字节,双字节,多字节);6、指令功能类别(算术/逻辑运算,存储器访问,寄存器操作,程序流控制,输入/输出);7、依据CPI值对指令系统进行性能分析。

采用一组RTL 以及综合 时序约束产生功能等价的FPGA 和ASIC

白皮书采用一组RTL以及综合/时序约束产生功能等价的FPGA和ASIC电子系统设计人员使用FPGA来实现他们的原型开发,利用器件的可编程能力验证硬件和软件。

一旦设计准备好进行量产时,设计人员寻找某类ASIC以达到功耗、性能和成本目标,特别是,能够提供硬件平台和工具包的ASIC,支持目前采用了FPGA的设计,可以使用相同的I/O、存储器资源和IP。

依据这些标准,设计人员降低了ASIC设计出现功能或者时序错误的风险。

本文讨论Altera HardCopy ASIC的发展、体系结构和功能,它作为封装和引脚兼容FPGA匹配器件,非常适合实现设计量产。

引言Altera于2001年率先推出具有“无缝原型开发”功能的180-nm CMOS技术HardCopy®系列ASIC。

设计第一代HardCopy ASIC产品的初衷是“加强”FPGA 的查找表(LUT)结构,使用少量定制互联层,通过直接连线(ASIC)互联来替代可编程交换架构。

FPGA 原型中经过“强化”的其他逻辑模块包括 I/O、锁相环(PLL)、存储器以及串化器/解串器(SERDES)通道等,这些都原封不动地应用在 HardCopy ASIC中。

自从推出第一代器件后,Altera又推出了基于130-nm、90-nm和40-nm CMOS技术的后续 HardCopy ASIC产品。

HardCopy ASIC与逻辑门阵列技术有相似的地方,预先作好了部分公共“基本”逻辑。

某一设计的投片会产生两种金属/两种转接层定制金属层模板,由此定义了某种器件。

然后,采用定制金属模板来处理基本晶片,进行测试,装配到与FPGA 原型百分之百引脚兼容、基于相同硅片工艺的封装中。

与可比的标准单元实现方法相比,新的HardCopy ASIC在定制互联晶片工艺步骤中预先处理基本晶片,降低了NRE成本,缩短了ASIC制造时间。

HardCopy ASIC与对应的Altera® Stratix®系列FPGA功能等价,提供与FPGA相当的资源,但是减小了管芯尺寸,降低了功耗。

XPT2406用户手册_cn

8.7

差分工作模式 ................................................................................................................................. 16

8.8

触摸屏应用建议 ............................................................................................................................. 17

9 数字接口 ......................................................................................................................................................... 19

8.9

温度测量 ......................................................................................................................................... 17

8.10

6.1 6.1.1 6.1.2 6.1.3

6.2

引脚分配图 ....................................................................................................................................... 8 QFN-16 封装 ..................................................................................................................................... 8 TSSOP-16 封装............................................................................................................................... 8 VFBGA-16 封装................................................................................................................................ 8 引脚功能描述 ................................................................................................................................... 9

RSP1 雷达信号处理器规格书

2014

Rቤተ መጻሕፍቲ ባይዱP1 雷达信号处理器规格书

BEYD 深圳市佰誉达科技有限公司 2014/12/11

目录

特点 .................................................................................................................................. 3 1.应用 ............................................................................................................................. 3 2.描述 ................................................................................

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

超大规模集成电路设计

(3)运行Quartus II生成的Tcl脚本文件(.tcl),用以设置PrimeTime环境。

(4)在PrimeTime软件中做时序分析。

2.使用BLAST和Tau软件

Quartus II软件生成Stamp模型文件,此文件可以被导入BLAST或Tau软件中,进行板级时序验证。

以下步骤描述生成Stamp模型文件的基本流程。

(1)通过Settings对话框(Assignments菜单)或在工程建立期间使用New Project Wizard (File菜单)指定EDA工具设置。

(2)在Quartus II软件中编译设计,生成Stamp模型文件。

Quartus II软件将该文件放置在特定工具的目录中。

(3)在BLAST或Tau软件中使用Stamp模型文件进行板级时序验证。

6.2.8 时序逼近

6.2.8.1 简介

Quartus® II软件提供完全集成的时序逼近流程,可以通过控制综合和设计的布局布线来达到时序目标。

使用时序逼近流程可以对复杂的设计进行更快的时序逼近,减少优化迭代次数并自动平衡多个设计约束。

时序逼近流程可以执行初始编译、查看设计结果以及有效地对设计进行进一步优化。

在综合之后以及在布局布线期间,可以在设计上使用网表优化,使用时序逼近布局图分析设计并执行分配,以及使用LogicLock™区域分配进一步优化设计。

6.2.8.2 使用时序逼近布局图

可以使用时序逼近布局图查看Fitter生成的逻辑布局,查看用户分配和LogicLock区域分配以及设计的布线信息。

可以使用此信息在设计中标识关键路径,并执行时序分配、位置分配和LogicLock区域分配,实现时序逼近。

可以使用View菜单中提供的选项自定义时序逼近布局图显示信息的方式。

可以按照封装引脚及其功能显示器件;可以按内部MegaLAB™结构、LAB和单元格显示器件;按芯片的区域显示器件;按所选信号的名称和位置显示器件;以及使用Field View命令(View菜单)显示器件。

Field View命令在Floorplan Editor的高级总体视图中显示器件资源的主要分类。

在Field 视图中用彩色区域表示分配,这些彩色区域显示已分配用户量、已布置的Fitter以及器件中每个结构未分配的逻辑。

可以使用Field视图中的信息进行分配,实现设计的时序逼近。

1.查看分配与布线

时序逼近布局图可以同时显示用户分配和Fitter位置分配。

用户分配是用户在设计中所做的所有位置与LogicLock区域分配。

Fitter分配是Quartus II软件在最后编译之后布置所有节点的位置。

可以使用Assignments命令(View菜单)显示用户分配和Fitter分配。

时序逼近布局图允许显示器件资源以及所有设计逻辑的相应布线信息。

使用Routing命令(View菜单),可以选择器件资源和查看以下布线信息类型。

(1)节点之间的路径:显示所选逻辑单元之间的路径、I/O单元、嵌入式单元和相互馈电的引脚。

232。