Altium Designer记录

清除Altium Designer的一些使用记录_win XP系统_

注意:请设置系统,使系统能够显示隐藏文件

清除Altium Designer的一些使用记录(win XP系统)

∙删除如下文件夹:C:\Documents and Settings\<windows_login_name>\Application Data\AltiumDesigner\

∙删除如下文件夹:C:\Documents and Settings\<windows_login_name>\Local Settings\Application Data\AltiumDesigner

∙删除如下文件夹:C:\Documents and Settings\All Users\Application Data\AltiumDesigner

∙删除如下文件夹:C:\Documents and Settings\All Users\Application Data\AltiumDesigner_Security

∙使用Regedit,删除HKEY_CURRENT_USER\Software\AltiumDesigner注册索引和所有的子索引。

(您需要到运行菜单运行regedit,再找出AltiumDesigner 。

当您对编辑您的注册表很熟悉时才能这么做,否则,请联系IT部门。

)

∙C:\Documents and Settings\<windows_login_name>\Local Settings\Temp 可能也包含一些已经被删除的文件。

∙清空回收站

Altium上海售后技术支持团队。

AltiumDesigner知识学习记录材料

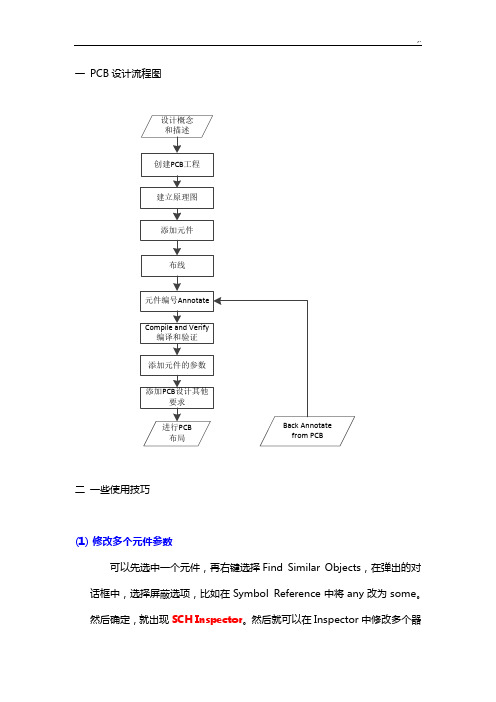

一PCB设计流程图二一些使用技巧(1)修改多个元件参数可以先选中一个元件,再右键选择Find Similar Objects,在弹出的对话框中,选择屏蔽选项,比如在Symbol Reference中将any改为some。

然后确定,就出现SCH Inspector。

然后就可以在Inspector中修改多个器件的参数或者封装。

(2)快速更改封装可以在Tools菜单栏中选择Footprint Manager,修改封装时候只要在封装上右键选择Set As Current, 更改完了以后点击Accept Changes。

另外,还可以右键选择Validate Footprint Paths来验证封装是否可用。

选择Accept后再点击Validate Changes可以查看更改是否可行,然后点击Execute Changes来执行更改。

另外,可以在Parameter Manager中修改参数。

(3)如何将别人的一个工程中用到的元件生成原理图库Tools中的Reset Schematic Designators来将器件复位成?状态。

或者在Annotate Schematics中选择Reset。

在Design中,选择Make Schematic Library来生成原理图库。

可以在Design中,选择Template,在其中选择模版来编辑原理图的一些信息,比如图名。

(4)如何将几个元件合并方法1,选中后右键,选择Unions方法2,选中元件,点击Tools菜单,然后选择Convert,再选择Creat Union(5)如何将某一部分经常使用的电路保存供以后使用选中后右键,选择Snippet,然后可以创建自己的Snipp et文件夹。

使用的时候,在右下角System菜单选择Snippet即可弹出窗口(6)如何得到元件报表选择Report,然后选择Bill of materials(7)自上而下的设计先使用Place Sheet Symbol再用Place Sheet Entry(注意按Tab键设置输入输出等属性),另外电源具有全局属性,不需另外设计。

Altium Designer Summer 9 学习笔记

Altium Designer Summer 9 学习笔记本软件与快播播放器不兼容,使用本软件时不允许打开快播,否则会提示exception access violation in module dxp.exe at 001b0d7f. 类似的错误1、Tab--查看属性2、空格键--调整正在绘制的图形的方向3、Ctrl+滚轮--缩放试图4、L--打开层设置5、Shift+m--放大镜6、Ctrl+m--测量距离,100mil=2.54mm;这个单位长度比较常用;7、从外部向AD内导入元件库或者封装库:通过view---workplace panels--system----library 打开库对话框(在界面右上角边上也可以打开),然后点击其上侧按钮libraries弹出加载对话框,点击下方的add按钮,弹出选择库文件的对话框,选择一个或者多个.lib文件,点击打开按钮,等待片刻,点击close按钮,这时候便可以从库对话框中查看是否添加成功。

8、从零开始工作的步骤(1)首先建立一个工程:file--new--new project---pcb project;(2)然后给工程建立原理图文件或者pcb文件,即在左侧projects对话框中右键点击刚才建立的工程名称,点击add new to project-----schematic;(3)与第二个步骤同样的办法建立pcb文件:右键点击工程名称----add new to project-----pcb;(4)保存工程:右键工程名称,点击save project,弹出保存对话框,选择保存目录,输入工程名称,保存,然后系统让保存原理图和pcb文件,依次输入相关名称,点击保存;(5)这时候可以画原理图和pcb板了;(6)如果需要绘制原理图的元件,那么首先要建立一个元件库(文件)(schematic libraries),则操作步骤与建立pcb文件或schematic文件一样;然后就可以再打开的页面里使用菜单里place、tools等自由绘制我们想要的元件,然后保存;(7)如果想在同一个元件库的库文件里绘制多个库元件,那么打开元件库,然后点击菜单里的tools---new component,弹出新的绘制窗口,在这里可以绘制下一个库元件;(8)打开原理图文件,在元件库对话框中选择要使用的元件,双击选中,然后在原理图文件绘制界面点击即可添加一个元件;(9)再次添加一个元件;与上一个元件形成连接关系;(10)添加封装:在原理图文件绘制界面里,选中某一个元件,右键,点击properties,弹出component properties 对话框,然后在右下角models for XXX(元件名称)小对话框下方,点击add,弹出add new model 对话框,这里选中footprint,点击ok,弹出pcb model对话框,在name里输入要加入的封装的名称,比如dip8,系统会自动浏览并给出所选pcb模式的预览图,如果系统中不含有该名称的pcb model或者不知道封装的名称,可以点击name 后面的browse;(11)很多时候需要自己画封装,画封装前需要先知道各个元件的尺寸大小,然后我们需要建立一个pcb library,方法与建立元件库一样;(12)绘制封装前首先设置吸附点会有助于绘制图形,吸附点的距离需要根据原理图文件界面的吸附点的距离来定;(13)设置吸附点可以用工具栏中的下拉工具set snap grid或者ctrl+g,设置吸附点前我们可以先修改一下显示的单位,使用快捷键Q就可以实现mil与mm之间的自由转换;(14)比如添加一个焊孔,可以使用工具栏中place pad工具,点击一下该工具图标,然后点tab键,出现属性对话框,在这里可以设置封装的多层或者单层,然后必须设置properties 中designator的标号,也就是封装脚的编号或者顺序,否则自动生成pcb板时会出错;(15)添加好焊孔之后,一般还需要加一个框,可以清晰的显示出元件的位置和大小;这种线一般加在top overlay(字符)层上;使用place line工具画出焊孔外围方框;绘制之前有时我们需要重新设置吸附点;(16)绘制好之后我们需要给封装设置一个基准参考点,点击菜单栏中edit----set reference,从中我们可以选择pin1或者center、location其中一个;这一步十分关键;若在后面发现这一步忘记做了,需要打开这个封装文件然后设置一个基准点,保存,然后在系统中找到pcb library,然后在这个封装的名称上右键点击update PCB with XXX(封装的名称);(17)一切绘制好之后,保存封装库文件并输入名称,然后给刚才绘制的封装命名并保存,最后还要在界面左上角点击保存按钮将封装保存;(18)然后就可以使用刚才建立的封装了;(19)安装电路原理图绘制好图后点击保存;(20)然后点击菜单栏project----compile documentXXX(文件名)开始编译原理图,编译的结果会在右下角system---message里显示;(21)确认绘制没有问题之后,点击菜单栏中design----update PCB XXX(文件名称),弹出engineering change order对话框,然后点击对话框左下角validate changes 来检测哪些可以正确生成pcb,确认都可以正常生成后,点击旁边的execute changes按钮生成pcb文件;然后点击右下角close按钮;(22)这时候需要查看生成的pcb,缩小pcb界面或者使用工具栏中小放大镜fit document 或者使用快捷ctrl+Pgup;如果位置不合适,可以单击一下然后移动一个合适的位置,然后再点击一下后用delete键删除上层;(23)如果觉着pcb界面过大或者过小,可以点击菜单栏中design---board shape-----redefine board shape,然后就可以自定义画出一个方框来作为pcb界面;(24)调整并确认无误后,我们可以在keep-out layer层定制板子的大小:点击keep-out layer,然后点击菜单栏中place--line,用线来确认板子的大小;(25)然后可以在需要的角添加过孔,使用工具栏中的按钮,添加过孔前还可以根据需要来修改单位和孔径的大小;(26)修改所有元件名称的字体格式:先随意选择一个元件名称点击右键,选择find similar objects,然后选择一项或多项需要修改的参数,然后把后面的any修改成same,点击apply,然后弹出一个小的对话框,在这里我们可以把想要的值输入进去,然后关闭该对话框,最后在当前.pcbdoc界面右下角点击clear,所有类似或者参数值接近的参数都被修改完毕;(27)统一改封装:方法和上面的一样;(28)接着我们需要修改几个参数,打开design---rules,然后第一个参数是间隙clearance,点击后可以在最下方示意图的上方修改最小间隙的大小,一般这个参数根据不同pcb生产厂家机器的规格不同设置成不同的参数大小;参数值越小,规格越高。

清除Altium Designer的一些使用记录_win XP系统_

注意:请设置系统,使系统能够显示隐藏文件

清除Altium Designer的一些使用记录(win XP系统)

∙删除如下文件夹:C:\Documents and Settings\<windows_login_name>\Application Data\AltiumDesigner\

∙删除如下文件夹:C:\Documents and Settings\<windows_login_name>\Local Settings\Application Data\AltiumDesigner

∙删除如下文件夹:C:\Documents and Settings\All Users\Application Data\AltiumDesigner

∙删除如下文件夹:C:\Documents and Settings\All Users\Application Data\AltiumDesigner_Security

∙使用Regedit,删除HKEY_CURRENT_USER\Software\AltiumDesigner注册索引和所有的子索引。

(您需要到运行菜单运行regedit,再找出AltiumDesigner 。

当您对编辑您的注册表很熟悉时才能这么做,否则,请联系IT部门。

)

∙C:\Documents and Settings\<windows_login_name>\Local Settings\Temp 可能也包含一些已经被删除的文件。

∙清空回收站

Altium上海售后技术支持团队。

altium_designer笔记

Altium designer原理图的设计2、3、屏障:compile mask(编译时被屏障的不显示信息)。

4、消除编译警告:place→divectives→NO ERC。

5、6、放置总线BUS:总线名[0:n],然后place Bus Entry, 放置网络代码:place→ Net Label。

例如: 总线格式:databus[0:9],在Bus Entry命名:databus0、databus2… databus9,另一端命名databus0、databus2…databus9则建立了一一对应的关系,及databus0对应databus0。

7、查找替换:Edit→Find and Replace Text 说明:替换名字而已。

8、9、10、SCH→SCH Inspector 显示信息和修改被选对象参数等。

11、12、原理图设计完成后生成报表:reports→bill of materials,按键Export则导出元件清单/也可以使用模版“Template”点击浏览“*…+”选择模版再导出元件清单。

原理图分等级式的设计1、由顶层到底层设计:先设计顶层建立连接关系,然后创建子图再进行部分原理的设计并保存。

Place→sheet symbol命名编辑后,放置端口:place→add sheet entry,在弹出的窗口设置properties下的name 格式:名[0..n]。

多根线端口用总线连接。

子图的生成:左键单击选中sheet symbol,右击在弹出的菜单中选择create symbol actions→create sheet from sheet symbol。

设计完成之后进行检测确定是否匹配:Design→synchronize sheet entries and ports,如不匹配则修改之。

2、由底层到顶层设计:先设计原理图再由原理图创建sheet symbol再建立连接关系子图设计完成→创建原理图(可命名为top)→在工作区间单击右键→sheet actions→create sheet symbol from sheet or HDL→在弹出的对话框中选择子图→确定。

Altium_Designer6.9软件操作实用笔记 自己也修改

Altium Designer 6.91、一个项目里可以有多张分立的原理图。

2、一项目里多张分立的原理图不能单独分开分别导入不同的PCB,导入一个PCB时同一项目所有原理图一定是个集体,并一定会一起同时导入这个PCB,也就是一个PCB一定包含这个项目所有原理图。

但可以画多张PCB。

3、当原理图张数或电路改变时,重新导入PCB后,会使PCB更新至和已有原理图一致,当在PCB改变了位号时更新原理图,在原理图重新编译下会在原理图已有位号旁显示更改后的位号。

但不改变已有位号。

4、多张分立的原理图导入到PCB电源是连接的。

5、多张分立的原理图如需信号连接,需建立层次原理图,否则导入到PCB板互不连接。

6、默认设置—TOOL---Preferences---defauts7、按住CTRL+SHIFT滚动鼠标滑轮切换层(在PCB操作界面)8、选中按住SHIFT再拖动元件为复制功能(在原理图的操作下,可以使用,这种操作复制出来的元器件的标号自动增加)★★★★★9、选中一个元件,CTRL+R连续放置,CTRL+D相当于CTRL+C和CTRL+V 复制再粘贴,或对着元件按E再选(区别于上面的操作,复制出来的元器件的标号和母体是一样的)10、选中,按住CTRL拖动元件为DRAG功能,即链接导线会跟随延长,与MOVE功能移动不一样,按M键出现DRAG和MOVE,DRAG可以方便两个芯片引脚对应连接,再拖动,避免一根一根线连(原理图操作界面,实用功能)★★★★★11、EDIT-----BREAK WIRE 断线(原理图界面)12、PLACE---DIRECTIVE(directive)---NO ERC 不进行ERC电气规则检查(原理图界面红色叉叉具有同样的功能 Place No ERC)13、PLACE---DIRECTIVE---compile mask 编译屏蔽罩14、原理图编译:Project---compile document sheet (编译功能是什么作用?)15、原理图标号排序:Tools---Annotate Schematics (未尝试)16、原理图右下角的模板添加,Design—template—set templatefile name打开自带的模板路径找到Templates文件夹进入打开即可,更改模板内容Design—Document options—parameters 更改Value即可(何功能?)17、CTRL+F 查找(原理图界面,可用)18、CTRL+H 查找并替换(原理图接界面,Text to Find选择需要修改的原件,Replace With要改成的原件编号)19、层次原理图从顶层到子层绘制,先绘制顶层,再单击一个原理图模块symbol右键选择sheet symbol actions---create sheet from symbol 创建子原理图。

Altiumdesignersummer08学习笔记

Altiumdesignersummer08学习笔记本人来自于重庆邮电大学,花了一个月时间学习altiumdesigner,学习过程中做了些简单的操作笔记,笔记是根据郭天祥的讲课视频来记录的,希望能对大家有所帮助,如果有什么想和我交流,可以加我的QQ:375240364开始启动ALTIUM DESIGNER时,其实运行的是DXP。

EXE文件,pcb画图要测量元件的大小,按ctrl+g能设置两个点之间的距离,选中弹出来工俱第二个图标为焊盘,画点,尺子测量ctrl+m,SHIFT+M是打开或取消放大镜功能,放大某一个部分画电路元件:1。

place下选要画的元件的形状,2,tool下选择PIN要添加的引脚,按TAB键可以修改引脚属性,(内部标号和外部号),确定后可按空格键翻转两个标号,3,按住CTRL键滚轮可以放大或缩小,4,在做原理图时,每个字母后面加上"\",就会显示上划线,这一条只适用于在画原理图库时,在原理图中添加元器件时修改其名字时是行不通的。

5,元件之间能自动连接,不过连接时的线是很短的,如何加长?按左键选中元件,然后按住CTRL键拖动元件。

6,添加封装,双击元件,再点击右下脚ADD,选择FOOTPRINT,7,2.54mm,在PCB中非常重要,即是100mil,单片机中大部分都是这样的距离,8。

画PCB封装图,元件都齐,再测量9,画PCB时设置两个引脚之间的距离:点工具栏#字网状图形,选set snap..默认的是mil单位,按Q后会转换成MM为单位,点焊盘画圆圈,按TAB键打开属性,designator中要填写与对应引脚相同的序号,画完后最好加一个框架。

加框要加在TOP OVERLAY层,用LINE画线工具画线,可以通过设置间距,使方框细一些,10.VSS是代表要接地的意思11,画好原理图后,选PROJECT下的compile编译,然后点designer下生成PCB图,然后点工具栏上的放大镜会弹出PCB图来,designer下bord shap下选redfine board shap来确定黑色格子的大小,最好和PCB图宽度相当12,画好一个PCB封装库时要设置一个参考点,以免到时移动时找不到元件,在封装库文件下点EDIT找到set reference,如果是在生成PCB之后才设置参考点,那么这时要重新导入封装,或是把库升级(找到工程里文件点右键升级),如果还是找不着位置,可以重置其坐标,找一个与它相差不远的元件的坐标,以它为参考设置。

Altium Designer Winter 09 面板笔记

Altium Designer Winter 09 面板笔记原理图设计初步A,笔记open打开hidden隐藏open/modified打开后修正modified修正compile编辑、编译design workspace工作空间compile all projects所有工程进行编译add new project添加新的工程create project from创建工程open design workspace打开已有的工作空间close systom system configuration- configuration清屏open a document最近打开文档open a project打开工程new新的new from existing file从已有文件新建文件new from template从模板新建文件file文件 edit编辑 view察看 project工程(项目) place放置 design设计tools工具 reports报告 window窗口 help帮助open workspace documents打开工作空间下的文档open design workspace 打开已有的工作空间explore浏览romove from project从工程中移除customize用户定义(个性化定制) preferences优先选项(个性化爱好定制) system info系统信息 run process运行进程 check for updates检查更新 licensing(my account) run script运行脚本library库script files建立脚本文件mixed-signal sinulation混合信号模拟other其他的文档import导入 close关闭 save保存(正常文件保存) save as另存为save copy as拷贝出来再另存为save all保存所有import wizard输入向导(其他软件文件快速转入该软件方法)knowledge center支持中心 cut剪切 copy复制 paste粘贴 smart paste智能粘贴 align对正 move移动fit document适合当前文件的察看fit all objects适合所有文件的察看area适合区域文件的察看around point适合点文件的察看cancel取消 back(退回) next前进(下一步) finish 完成refresh刷新 full screem全屏toolbars拖把 navigation导航 wiring布线 custonize定制 design conpiler工作空间控制面板 default默认 startup开始 devices view器件察看 home page 主页 status bar状态栏 command status命令状态 grids栅格 toggle units单位切换project documents项目文档 show比较view channels多通道(可以察看原件参数)local history历史project packager工程打包bus总线bus entry总线进口part器件manual junction手工接点power port电源端口wire线net label网络标号port端口off sheet connector离图连接sheet symbol图表符add sheet entry添加图纸入口device sheet symbol器件图表符harness线束directives指示text string文本字符串text frane文本框drawing tools绘图工具notes注释update pcb document portswitcher1d.pcbdoc(生成pcb)brovse library浏览库add/remove library添加/移除库make schematic library生成原理图库make integrated library生成集成库template模板netlist for project工程的网络表netlist for document文件的网络表simulste仿真create sheet from symbol产生图纸create hdl file from symbol从图表符产生HDL文件create sheet symbol from sheet or hdl(hdl文件或图纸产生图表符) create component from sheet图纸生成器件renane child sheet子图重新命名synchronize sheetentries and ports(同步图纸人口和端口)document options 文档选项find component发现器件up/down hierarchy上/下层次paraneter manager参数管理器footprint manager封装管理器update from libraries从器件库更新update parametars from database从数据库更新参数annotate schematics (harness definition problem finder)reset schematic designators注解reset duplicate schematics designators复位标号annotate schematics quietly复位重复force annotate all schematics静态注释back annotate schematics标注所有器件number schematic sheets反向标注board level annotate图纸编号annotate compiled sheets(未知)sigal integrity(未知)import fpga pin file导入fpga pin 文件fpga sigal manager(fpga信号管理器)pcb to fpga project wizard(pcb到fpga工程向导)convert转换cross probe交叉探针cross select node交叉选择模式select pcb components选择pcb器件configgure pin svapping配置管脚交换schenatic preferences设置原理图参数bill of materials(未知)measure distance测量距离port cross reference端口交叉参考。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SCH & SCH Lib 繪製1.图纸大小的设臵 Design/Document OptionsStandard Style Protel所提供的图纸样式有以下几种:●美制: A0 、 A1 、 A2 、 A3 、 A4 ,其中 A4 最小。

●英制: A 、 B 、 C 、 D 、 E ,其中 A 型最小。

●其它: Protel 还支持其它类型的图纸,如 Orcad A 、Letter 、 Legal 等。

自定义图纸大小可以在 Custom Style 选项2.格点设臵2.1格点形状和颜色的设臵原理图-右键-option-GridsProtel DXP 提供了两种格点,即 Lines (线状格点)和 Dots (点状格点)2.2Grid属性在 Document Options (图纸属性设臵)设有 Grid 选项区域,和 Electrical Grid 选项区域。

( 1 ) Grid 区域设臵选项区域Grid 选项区域中包括 Snap 和 Visible 两个属性设臵:● Visible :用于设臵格点是否可见。

在右边的设臵框中键入数值可改变图纸格点间的距离。

默认的设臵为 10 ,表示格点间的距离为 10 个像素点。

● Snap :用于设臵游标移动时的间距。

选中此项表示游标移动时以 Snap 右边设臵值为基本单位移动,系统的默认设臵是 10 。

例如移动原理图上的组件时,则组件的移动以 10 个像素点为单位移动。

未选中此项,则组件的移动以一个像素点为基为单位移动,一般采用默认设臵便于在原理图中对齐组件。

3.自己画:原理图组件、封装组件Display Name-管脚在IC中的作用名,因IC而异Designator-管脚号 Length-管脚长度,为格点距离的两倍为204.批量修改原理圖元件封裝:Protel中掌握批量修改元件方法是必须的,在原理图中及PCB中修改的方法一样。

a.点击选中其中任意一个要修改的元件。

b.右键点击该元件---Find Similar Objects 此时跳到筛选页面,看看你要改动的所有元件是不是有共同的地方而异于其它元件,比如名称,封装,管脚。

相同的就把那个“Any”改为“same”,一般改一处即可。

Apply是预览你筛选的结果,被选中的元件都变亮。

如果有其它元件也被选中了,重新筛选,全部选上要修改的元件后,点击OK。

c.此时回到了原理图页面,看到选中的元件都变亮了。

点击“Inspect”(在页面的下部)。

出现修改页面。

d.把要修改的参数修改即可。

(修改封装要自己输入封装名称,没有选择)e.关闭修改页面。

点击原理图页面右下角的“Clear”,完成。

5.自動,批量元件編號:TOOLS->ANNOTATE SCHPCB & PCB Lib繪製1.TopLayer、BottomLayer、MidLayerx,这几层是用来画导线或覆铜的(当然还有TopLayer、BottomLayer的SMT贴片器件的焊盘PAD2.Top Solder、Bottom Solder:Solder表面意思是指阻焊层,就是用它来涂敷绿油等阻焊材料,从而防止不需要焊接的地方沾染焊锡的,这层会露出所有需要焊接的焊盘,TOP solder和BOTTOM solder 设臵之后表示印制板上的绿油不会覆上,直接露铜,如果你在一根导线上又画了一条线在solder层的时候做出来的印制板那条导线画solder 的地方都是露铜的,如果在没有铜线的地方画solder则此部分不会有绿油覆盖。

要想将过孔加阻焊的话则在过孔的属性中将force complete tenting on top和force complete tenting on bottom 两个选项打勾即可3.Top Overlay、Bottom Overlay,丝印层,PCB表面的文字或电阻电容符号或器件边框等,一般为白色;4.Keepout,画边框,确定电气边界5.Multi Layer,贯穿各层的,像过孔(到底层或顶层的过孔VIA也有Solder和Paste)6.via称为过孔,有通孔、盲孔和埋孔之分,主要用于同一网络在不同层的导线的连接,一般不用作焊接元件;pad称为焊盘,有插脚焊盘和表贴焊盘之分;插脚焊盘有焊孔,主要用于焊接插脚元件;而表贴焊盘没有焊孔,主要用于焊接表贴元件。

via主要起到电气连接的作用,via的孔径一般较小,通常只要制板加工工艺能做到就足够了,而且via表面既可涂上阻焊油墨,也可不涂;而pad不仅起到电气连接的作用,而且还起机械固定的作用,pad的孔径(当然是指插脚焊盘)则必须要足够大到能穿过元件的引脚,否则会导致生产问题;另外,pad表面一定不能有阻焊油墨,因为这会影响焊接,并且一般在制板时还要在pad表面涂上助焊剂;还有pad的孔径(当是指插脚焊盘)的盘径和孔径之间还必须符合一定的标准,否则不仅影响焊接,而且还会导致安装不牢固。

7.Pcb LIB:TOOL-》COMPONENT WIZARD8.Board option------>Snap Grid設臵鼠標每移動一格的距離,一般設臵成最小1mi(0.025mm)精度最高Visable Grid 設臵可視網格距離,Grid 1和Grid 2設臵成1mm方便知道元件之間的距離或線的長度,不用再去測量9.畫封裝的時候一定要在頁面的中心畫,否則在PCB布局的時候會出現這樣的狀況,點擊這個元件封裝,鼠標就偏移都其他地方去了,解決方式是放臵一個焊盤,并CTRL+END讓焊盤定位在頁面中心,然後以這個中心話封裝就可以了10.Electrional Grid:电气网格,当手动布线时,鼠标靠近具有电气的导线或者焊盘的时候,自动跳到焊盘的中心处,设臵的值越大,电气“吸引”更远。

Snap Grid:移动鼠标的步进距离,需要精度高的尺寸时,就把这个值设臵小一点。

Component Grid:元件步进网格,在进行元件布局的时候,移动元件步进的距离大小设臵。

設臵小一點Visible Grid:可视网格,设臵背景中看见的格子的大小設臵為1mm 11 .電氣安全間距(最小間距)、元件間安全間距(最小間距)設臵電氣Clearance(安全间距规则)Protel的(Electrical)电气规则中的Clearance(安全间距规则)用于限制图件间距的最小值,使图件之间不会因为过近而产生相互干扰。

所谓安全间距,也就是具有导电性质的图件之间的最小间距,通常包括导线与导线(Track to Track)、导线与过孔(Track To Via)、过孔与过孔(Via to Via)、导线与焊盘(Track to Pad)、焊盘与焊盘(Pab to Pab)、焊盘与过孔(Pab to Via)等之间的最小间距。

元件間安全間距Design--->Rule分別設臵Clearance和Component Clearance12电气规则:包括Clearance(安全间距规则)、Short-curcit (短路规则)、Un-Route net(未布线网络规则)、Un-connected Pins(未连线引脚规则)。

short-circuit短路规则Protel DXP中的(Electrical)电气规则中的short-circuit短路规则用于设定是否允许某两个图件短路。

在实际电路板设计过程中,我们避免两个图件短路情况的发生,但有时需要将不同的网络短接在一起,比如有几个地网络之间需要短接到一点。

如果设计中有这种网络短接的需要,必须为此添加一个新的规则,在该规则中允许短路,即在如图5-9所示的Constraints(规则限制)下勾选Allow Short Circuit,并在Where the first object maches中指明这一规则适用于哪个网络、板层或者其他特殊元件。

Unrouted Net未布线网络规则Protel DXP中的(Electrical)电气规则中的Unrouted Net未布线网络规则用于设定检查网络布线是否完整。

设定该规则后,设计者可根据它检查设定范围内的网络是否布线完整。

Unconnected Pin(未连线引脚规则)Protel DXP中的(Electrical)电气规则中的Unconnected Pin(未连线引脚规则)用于设定检查元件的引脚是否存在没有连线的情况(引脚悬空),13. interactively route connections是交互式布线,用于画有电气连接的线place line是放臵线条,用于画没有电气连接关系的线,如元件的外框或PCB的外形等如果有相同网络(电气属性)的焊盘,用互交式布线是不会变颜色的。

用普通布线就不一样了,普通布线布出的线是没有网络(电气属性)的,双击这走线,在属性对话框里定义这走线的网络与连接的焊盘一致,绿色消除。

(一般不建议使用普通布线)14線間距必須遵守2W和3W原則.15信號線儘量不使用過孔16.shift + s查看當前層的布線17布線網絡分門別類PCB布线软件的书籍和资料大家应该都看得不少了,网上有很多布线技巧的文章,大都是教人如何避免干扰,如何走地线等等,其实这些软件里面还有一个功能,也很好用的,只是绝大部分的书籍都没有介绍。

这就是Net Class功能。

Pcb文件首次加载网络表的时候,没有对其进行分类。

这个功能可以人工将无数的网络连接分门别类,比如分成Power、data_bus、Address_bus、Hi_volta等类别。

这样分类后可以分别对不同的类别施加不同的布线策略。

好了,现在让我们尝试一下这个功能(以protel为例):首先打开一个PCB图;选择菜单“Design-->Classes..”跳出图 1的画面。

这里我已经预先定好了几个C ,其中“All Nets”是protel 默认的类别,这个类别包含了所有的网络。

如果定义了布线规则,默认就是针对这个类别的。

现在我要为这个pcb增加一个表示CPU地址总线的类别“Address_bus”,按下图 1画面中的“Add”按键,在图 2的画面中输选择“A0~A19”,然后选择“>”把这些网络放臵到右边的子窗口中。

如图 3。

这样就建立好了一个新的pcb 网络类别。

用同样的办法,再建立“power”、“data_bus”等网络类别。

好了,我们为这些网络类别分别指定布线策略吧,首先我们为电源类指定布线策略。

按下图 4画面中的“Add”按键,增加一个策略。

如图 5所示,“Filter Kind”选择“Net Class”, “Net Class”选择“POWER”,然后可以分别设定它的线宽等参数,你还可以为POWER类增加一个靠近限制的规则(由于我这个电路板是4层板,我这个工程就不设臵靠近规则了)。