BGA焊接状况Intel分析报告(Rev6-SitkaFA)

BGA焊接及植球

BGA焊接及植球BGA(Bump Grid Array)一种新型IC封裝方式,其物理特性較QFP方式更堅固,所以是目前多腳IC較為流行的封裝方式之一,由于其引腳改為錫球,焊接后不能直接檢測其焊接情況,所以給焊接及檢查都帶來了新的課題.BGA在焊接失敗后,其上引腳已被破坏,只有重新植球方可利用,下面就以BGA焊接;檢查及植球予以概述.\一.BGA焊接條件及要求:1.何為空洞(VOID)?空洞是指在BGA焊接完畢后,用X-RAY照射,發現焊點內有明顯的白點.這种現象就稱為空洞.因X-RAY不能穿透較厚金屬,所以看到白點說明焊點含這樣會影響其可靠性.在BGA的焊接中嚴禁有空洞出現(如附圖)2.圍牆/屋頂:回焊過程中由于外界原因如:机械沖擊等引起焊點輕微移動而形成類似圍牆或屋頂狀之現象.3.形成空洞:圍牆屋頂之主要原因:熱沖擊或机械沖擊影響BGA焊接之四要素:(1)方法:*印刷方法:生產焊過程中,BGA焊盤上都要刷上一層0.13MM的焊錫膏(其清洁劑.活化劑及錫.鉛等組成)印刷過程中要求涂刷均勻,厚度在0.13MM左右,且印刷膏應在開封后12小時內用完.返修過程中,在焊盤上涂上一層松香膏,其厚度在0.3MM左右,要求涂刷均勻.*回焊爐:生產過程中,回焊爐溫度設置CH1:.235℃;CH2:340℃CH3:200℃;CH4:340℃;CH5:180℃;CH6: 270℃;CH7:210℃;CH8:260℃.這樣使PCB板逐漸受熱后逐漸泠卻,防止PCB變形,同時也杜絕焊點不光滑出現圍牆/屋頂之現象,返修過程要求加熱儀器模擬回焊爐,一般有四個階階段:底面加熱.預熱回焊.降溫.返修時要求BGA焊點溫度在200℃~220℃之間,其周圍最近之元件溫度不超過160℃,且BGA焊點溫度在183℃之上.至少保留60秒.(2)物料:*錫膏(在3~10℃下保存):由活化劑.清洁劑等組成.且有低沸點,少气泡之特性.其水份越少,活化劑含量及金屬越高,空洞越少.在焊接過程中,清洁劑對PCB 板進行清洁,活化劑則在預熱階段將板PCB板及BGA上已氧化部分進行還原并防止加熱過程中氧化.*PC板:焊接內要求PCB板清洁,干燥.焊點無氧化現象,避免有綠油.异物等PC板生產過程進行表面處理,其中NI/AU處理最好,其次采用水平噴錫方法,防止焊盤氧化VI/AU*錫球:要求大小均勻,氧化程度低.(3)人為因素:*FIFO:先處理過的板先進行焊接,避免PCB板或BGA在空气中長期放置,以致水份含量增加及焊點或錫球氧化.*清洁:BGA焊接過程必須保持清洁,否則易造成開路,清洁時不宜使用含氧化劑之物品用手摸焊盤.*過時:BGA從干燥柜口放出后.在空气中放置不超過12小時,否則應重新烘烤26小時(在125℃下).PCB板在空气中放置不超過12小時.否則應在110℃烤4小時(4)環境:*擺放時間:指從印好到入爐時間,應越短越好.*水气含量.*氮气濃度500PPM由BGA焊接四要素我們可以得知形成空洞之原因亦有:(1)周圍空气進入;(2)FLUX和綠漆的作用;(3)FLUX受熱分解;(4)FLUX內清洁劑作用;(5)PC板內水份;(6)除銹過程中產生的气泡.5.FLUX活化:*溫度:130℃~170℃;*時間:MIN:50’S;*最高溫度:215℃(+-)10℃;*熔錫時間:MIN 60’S;*熔錫溫度:183℃以上.綜上所述,可知BGA焊接條件有:(1)PCB板清洁干燥無氧化;(2)BGA錫球均勻,清洁干燥無氧化;(3)松香膏無分份涂刷适宜;(4)預熱溫度大于130℃,時間大于50’S又利于FLUX活化;(5)BGA 焊點溫度大于183℃.且至少保留時間在60’S以上;(6)BGA最近之元件溫度不超過160℃;(7)操作穩定,防上机械沖擊;(8)加熱均勻,溫度上升徐緩,防上熱沖止.BGA焊接要求:(1)焊點光滑,無圍牆/屋頂之現象;(2)無空洞虛焊;(3)無連錫;(4)不傷其周圍元件及PCB板.二;BGA返修方法及過程:1,焊接設備使用及調整:目前我公司BGA返修焊接設備使用德國FINETECH公司的BGA焊接設備來取代老式喜瑪設備.其主要由視訊系統,控制系統及加熱系統.,,視訊系統由CAMERAI;CAMERAII.臨視器放大鏡組等組成,用來定位控制系統由電腦及HOT AIR BOTTOM HEATING CONTROLLER REFLOW CONTROLPLACECONTROL組成.加熱系統由底座,底板.吸嘴.加熱懸臂,加熱底网姐成.(1)對准方法:從監視器上觀察需對准兩部分圖像重合即可使用時間腳踏開關,此時會有紅色LASTER 作為對准點.底板可自由移動,位置調正后,可用底板兩微調旋鈕進行X.Y向微調,其精度可達0.1MM.(2)COMISS軟件使用方法:COMISS內有兩個程式:A. PROTOC OL (設定模式)B MODIFOCATION (建立模式)使用第一种方法時,其參數為可修改,但不存盤.使用第二种方法時其參數可任意修改后存盤.這种模式輸:”FINETECH” PASSWORD.*COMISS運行步驟:(1)雙擊COMISS;(2)選擇MODE;(3)進入選定MODE;(4)選擇所用文件;(5)點擊START (點FRNISH為退出.*參數設定方法:(1)進入MODE FICATION 模式;(2)點擊要修改項,彈出修改框后修改(灰色框內參數不可調)三:BGA焊接:步驟: (1) 將PCBA板拆BGA后殘留錫吸淨;(2)將PCBA板上待焊BGA位置用吸錫線粘平;(3)清洗PCAB板(用無水酒精)(4)涂松香膏,要求涂刷均勻,厚度在0.08MM左右(注意周圍元件避免沾松香膏,以利清洗)(5)放置BGA芯片,其邊緣与PCBA板目白框對齊,也可用視訊系統對位,方法為:將PCBA板置与底板目.BGA吸附在對應NOZZLE 上,踩動腳踏開關,移動底板,使底板PCBA板上焊盤与BGA腳重合即合;(6)放下懸避,NOZZLE,距PCBA 板約0.8MM;(7)選擇正确文件,點擊START;(8)加熱完畢,待綠色曲線降低140℃時抬起懸臂,取下PCBA板;(9)清洗PCBA 板殘留松香膏.FINETECH 之軟件COMISS 和項參數之含義:50S:底面預熱時間;20S:底面加熱時間;5K/S:溫度上升速度為每秒外5K;10.0S:上升時間(微机自動運算)PRE-HEAT:預熱;210℃:預熱最啟溫度;90S:預熱時間;REFLOW:回焊;270℃:回焊溫度;30S:回焊時間:COLLING:冷卻;53.0S:冷卻時間;SB:140℃指焊接時底面保持最低溫度.COMISS 曲線及各段含義:各段含義及作用:A:底板溫度由開机升至預定下限溫度時間;B:其斜率与溫度上升速率設置有關(1 RH些MP);C:BGA預熱時間,此時松香膏活化劑作用,還原氧化物,并防止焊接過程中,錫被氧化; D:由預熱到回焊,其斜率与溫度上升速率設置有關(2 RHMP);E:回焊時間,此過程中焊錫完全熔化;F:冷卻,其与溫度下降速率有關.COMISS 各參數設置方法及依据:1設置方法:參數設置方法比較簡單,在MODIFICTION模式下,點擊參數框內需設置項,出現該項設置兩框,修改參數,點OK即可,參數修改完畢,點擊左方.2.設置依据:由于儀器上各溫度傳感器測得之溫度并非BGA真正受熱溫度,所以在進行首次焊接時應測試BGA及其周邊真正受熱溫度,以附合BGA焊接溫度要求.測試進PCBA板如圖示三個位置分別埋入傳感線,其得曲線最高溫度,符合下列范圍方為正常: (1)(2)最高溫度低于220℃,183℃以上至少保留60S;(3)最高溫度不超過140℃.直接影響溫度曲線的參數有:FLOW及加熱時間和溫度設置,在FLOW一定下,溫度与加熱時間成正比.在加熱時間一定的情況下,溫度与FLOW成正比(附圖2為BGA首片焊接時所測溫度曲線及各項參數設置.四.BGA 植錫球:1.方法及步驟:(1)准備合适的模具;(2)將BGA上殘留錫吸淨,并清洗;將已(3)清洗之BGA上涂刷松香膏,然后用刮刀刮下,BGA 上殘留一層极薄之松香膏;(4)將已涂松香膏之BGA置于模具公模上;(5)將母模罩上;(6)倒入适量錫球,并用刷子刷,保証每個孔內都有一顆錫球;(7)取下母模,檢查有無錫球多或漏;(8)置于PCB板上,用手輕彈PCB板,看是否有錫球滾動,若有則說明該點未涂上松香膏,可用IC針涂少許;(9)加熱;(10)清洗2.注意事項:(1)粘錫必須干淨,平整,不能有凸錫現象;(2)涂刷松香膏不能太厚,以免加熱時沸騰,使錫球滾動,涂刷時必須均勻;(3)加熱時,風量不易過大,以免把球吹跑;(4)模具每次使用后是易清洗,以免松香膏粘眷錫球.總結:BGA 焊接設備之參數并非一成不變,在外界環境變化下,(如气壓,設備老化等),相同的參數所得到的實際溫度并非一致,所以在BGA 焊接過程中要經常檢驗所焊之效果,但無論外界條件怎么變化,所設備的參數之結果必須符合:(1)芯片溫度不超過220℃;(2)183℃以上至少保留60S;(3)最近元件之溫度不超過140℃;只要符合此三個條件,保証BGA的焊接質量不會有問題.所以此條件為BGA焊接之基本指導思想,也是基本之要求.。

bga的良好焊接方法

现BGA 的良好焊接随着电子技术的发展,电子元件朝着小型化和高密集成化的方向发展。

随着电子技术的发展,电子元件朝着小型化和高密集成化的方向发展。

BGA BGA 元件已越来越广泛地应用到SMT 装配技中来,并且随着u BGA 和CSP 的出现,SMT 装配的难度是愈来愈大,装配的难度是愈来愈大,工艺要求也愈来愈高。

工艺要求也愈来愈高。

工艺要求也愈来愈高。

由于由于BGA 的返修的难度颇大,的返修的难度颇大,故故实现BGA 的良好焊接是放在所有SMT 工程人员的一个课题。

这里就BGA 的保存和使用环境以及焊接工艺等两大方面同大家讨论。

使用环境以及焊接工艺等两大方面同大家讨论。

BGA 的保存及使用BGA 元件是一种高度的温度敏感元件,元件是一种高度的温度敏感元件,所以所以BGA 必须在恒温干燥的条件下保存,操作人员应该严格遵守操作工艺流程,操作人员应该严格遵守操作工艺流程,避免元器件在装配前受到影响。

避免元器件在装配前受到影响。

避免元器件在装配前受到影响。

一般一般来说,BGA 的较理想的保存环境为200C-250C,200C-250C,湿度小于湿度小于10%RH (有氮气保护更佳)。

大多数情况下,我们在元器件的包装未打开前会注意到BGA 的防潮处理,同时我们也应该注意到元器件包装被打后用于安装和焊接的过程中不可以暴露的时间,以防止元器件受到影响而导致焊接质量的下降或元器件的电气性能的改变。

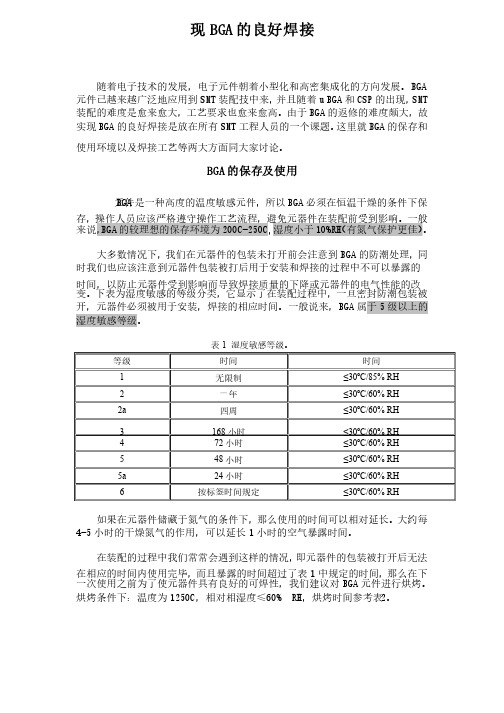

下表为湿度敏感的等级分类,下表为湿度敏感的等级分类,它显示了在装配过程中,它显示了在装配过程中,它显示了在装配过程中,一旦密封防潮包装被一旦密封防潮包装被开,元器件必须被用于安装,焊接的相应时间。

一般说来,开,元器件必须被用于安装,焊接的相应时间。

一般说来,BGA BGA 属于5级以上的湿度敏感等级。

湿度敏感等级。

表1 湿度敏感等级。

湿度敏感等级。

等级 时间 时间 1 无限制 ≤30ºC/85% RH 2 一年 ≤30ºC/60% RH 2a 四周 ≤30ºC/60% RH 3168小时 ≤30ºC/60% RH 4 72小时 ≤30ºC/60% RH 5 48小时 ≤30ºC/60% RH 5a 24小时 ≤30ºC/60% RH 6按标签时间规定≤30ºC/60% RH如果在元器件储藏于氮气的条件下,那么使用的时间可以相对延长。

浅析SMT工艺中BGA焊接不良原因

浅析SMT工艺中BGA焊接不良原因摘要:随着科学技术的不断发展,现代社会与电子产品密切相关。

随着电子产品向便利/小型化、网络化和多媒体的方向快速发展,对电子装配技术提出了严格的要求。

为了实现这一目标,必须对生产技术和组件进行深入的研究。

表面贴装技术(SMT)符合这一趋势,为电子产品的轻巧、微妙、简洁和小巧奠定了基础。

SMT是现代电子装配最流行的技术。

该技术最大的优点是,传统组件的体积被压缩到微型设备上,而体积只有原来的十分之一,因此可以解决传统电子组件的某些缺陷,如低密度、低可靠性、大容量和高成本。

新的高密度组装技术不断出现,其中球栅阵列(BGA)是进入实际阶段的高密度组装技术。

本文分析了BGA器件的组装特性和焊不良的原因。

关键词:SMT工艺;BGA焊接不良;原因分析引言SMT(Surface Mount Technology,表面贴片技术)是一种在电路板上安装表面安装元件的方法。

它是现代装配技术的核心,是一种复杂且不断发展的技术。

通过掌握制造过程的质量要求,了解各种零部件的焊接问题、原因和解决方案,我们可以不断地防止它们发生。

1BGA技术的发展BGA技术自1960年代的美国开始研究,但直到90年代初,BGA才进入实际应用阶段。

虽然SMT可以组装出轻、薄、短、小的电路,但随着人们对小型化电子电路和I/O引线数提出了更高的要求,继而对具有高引线数的精细间距器件的引线间距以及共面性提出了更为严格的要求。

由于QFP器件受到加工精度、可生产性、成本和组装工艺的制约,管脚的最小间距为0.3mm,这就大大限制了高密度组装的发展。

另外,由于精细间距QFP器件细引线易弯曲、质脆、易断,对引线间的共面性和贴装精度的要求严格,其应用受到了很大的限制,为此美国一些公司就把重点放在开发和应用比QFP器件更优越的BGA器件上。

2 BGA技术的特点BGA技术使用一种引线间距大、长度短的全新的设计方式,采用将圆型或柱状点隐藏在封装下面的结构,这样就消除了精细间距器件中由于引线问题而引起的共面性和翘曲的问题。

解析SMT回流焊接BGA锡球脱落及界面剥离的焊接不良原因及对策

解析SMT回流焊接BGA锡球脱落及界面剥离的焊接不良原因及对策随着IC 封装技术的发展,I/O 数量增多、布线密度增大、基板层数增多,使得传统的四边引角扁平封装(Quad Flat Package,QFP)等封装形式在其发展上有所限制,20 世纪90年代中期以球栅阵列封装(Ball Grid Array,BGA)、芯片级封装(Chip Scale Package,CSP)为代表的新型IC 封装形式问世,解决了封装引脚共面度、脚距过细和面积过大等问题。

传统引脚型芯片 BGA芯片(同样大小芯片 IO可多几倍)现在采用BGA封装的产品有很多种,如常见的电脑显卡、南北桥、CPU,在手机、投影仪、电视等产品中也有BGA元器件。

SMT贴片BGA芯片应用已经越来越多,但是,对BGA芯片SMT中的各项焊接工艺,作为工程师的你真的了解“透”了吗?BGA:即Ball Grid Array(球栅阵列封装)正常的BGA焊接1、BGA锡球脱落问题1、SMT接合工法・回流式自动机・锡膏・SMT基板概要・锡球脱落2、SMT接合工法・不良发生原因比率・锡球脱落注目3.锡球狭缢现象、脱落现象、界面剥离现象4.CSP、BGA接合部工程别不良发生要因:接合及接合后锡球形状変化(狭缢现象或锡球脱落要因)5.锡球脱落及变形现象分类及问题点整理6.CSP实装不良:锡球脱落及変形现象解说(事例1)7.CSP实装不良:锡球脱落及変形现象(事例2)CSP实装不良:锡球脱落及変形现象(事例3)8.CSP、BGA实装不良:锡球脱落及変形现象解说9.CSP、BGA実装不良:金属间化合物相界面剥离(1)10.CSP、BGA実装不良:金属间化合物相界面剥离(2)11.CSP、BGA実装不良:金属间化合物相界面剥离(3)12.锡球脱落及变形现象、对策方法13.锡球接合界面破坏现象、对策方法2、电镀问题1.锡球接合界面破壊现象、Ni电镀问题锡球接合界面破壊现象、Ni电镀Cl污染问题(污染组成构造)3.锡球接合界面破坏现象、Ni电镀污染ー接合力低下现象4.錫球接合界面破壊現象、Au/Ni-P電鍍諸条件影響問題5.Au/Ni-P電鍍諸条件影響問題-無電解電鍍条件6.Au/Ni-P電鍍諸条件影響問題-置換金電鍍浴浸漬時間影響7.錫球接合界面破壊現象、Sn-Cu接合界面合金厚ー接合強度3、CSP (BGA)气泡问题1.气泡发生原因2.CSP(BGA)实装时发生气泡分析~錫球組成錫膏組成変化・・・回流接合挙動相違点~3.CSP(BGA)实装时发生气泡分析~錫球組成錫膏組成変化・・・回流接合挙動相違点~4.錫球組成錫膏組成変化4、相关连技术1.CSP(BGA)錫球脱落問題参考資料錫ー金溶食速度(1)2.CSP(BGA)錫球脱落問題参考資料錫ー金溶融温度变化(2)3.CSP(BGA)錫球脱落問題参考資料金浓度ー強度関係4.CSP(BGA)錫球脱落問題参考資料金濃度ー伸長関係5.CSP(BGA)錫球脱落問題参考資料錫膏印刷厚ー金濃度的関係CSP(BGA)錫球脱落問題参考資料金属間化合物(1)6.CSP(BGA)錫球脱落問題参考資料金属間化合物7.SMT不良事例.混載実装界面剥離現象及対策8.SMT不良事例 ex:脚部界面剥离原因・对策9.SMT不良事例.銅箔剥離現象及对策5、SMT接合工法・回流温度曲线SMT回流焊就是通过大量加热,使锡膏受热融化从而让表面贴装元器件和PCB焊盘通过焊锡膏合金可靠地结合在一起的制程。

面向完整传输路径的BGA焊点信号完整性分析及优化

面向完整传输路径的BGA焊点信号完整性分析及优化0 序言随着电子产品的不断更新换代,微电子封装技术也在随之逐渐发展,多芯片组件(multi-chip module,MCM)技术应运而生. 多芯片组件作为一种新型的集成电路封装形式,与常规封装形式相比具有信号传输快、信号带宽大、信号噪声小、互连效率高、功耗小、组装效率高、成本低、重量轻、体积小等一系列的优点.然而多芯片组件在具备众多优势的同时,不可忽略在芯片密集度不断加大、信号工作频率不断升高所带来的问题,尤其是芯片之间高速互连结构(完整传输路径)所产生的问题. 而且对于传输速率达几百Mbps 甚至数Gbps 的高速信号,其有效频谱已延伸到微波甚至毫米波频段,在复杂互连系统中传输时已表现出极为明显的波特性,将对互连结构中信号传输产生极大的影响. 因此,要确保 MCM 中各芯片间保持良好的信号传输、不出现导致系统故障的信号完整性问题已经成为一项新的挑战.信号完整性指的是在高速产品中由互连线引起的所有问题,是数据进行高速传输中必须解决的一个重要问题,信号完整性问题出现将导致数据传输的丢失和传输错误,是决定系统性能的关键因素[1-2]. 关于完整传输路径的信号完整性研究,国内外相关的文献报道尚不多见,仅有少量的相关文献报道. 在国内,熊华清[3]采用互连结构分段的方法研究分析了MCM中Chip to Chip双条完整传输路径的传输性能. 该方法通过将完整传输路径分割成独立的互连结构模型,单独对互连结构进行分析和处理,最后得到完整传输路径的传输性能;在国外,Ndip等人[4-6]提出将BGA封装中完整的信号传输路径分解成相互连接的独立结构,对每个结构进行等效电路建模,把各互连结构的等效电路模型串联成一个整体来代替完整的电路模型,以该模型进行了相应的分析. 从现有文献报道极少的情况上看,完整传输路径研究刚开始起步,尚未能系统化的针对BGA焊点形态对完整传输路径的影响展开深入研究,对于完整传输路径的BGA焊点形态参数的优化更是极为少见. 因此,为了减少高频信号在MCM完整传输路径内信号完整性问题的影响,进一步提高高频信号在MCM完整传输路径中的传输性能,有必要展开BGA焊点形态对完整传输路径的影响相应研究及BGA焊点形态参数的优化设计. 对此,文中以高频条件下的MCM中Chip to Chip的一条完整传输路径中BGA为研究对象,通过建立基于BGA焊点的完整传输路径的HFSS仿真模型,分析焊点高度、焊点最大径向尺寸、焊盘直径对完整传输路径信号完整性的影响. 并以上述焊点形态参数为设计因素,以完整传输路径回波损耗作为目标值,设计17组仿真计算,采用响应曲面法对17组仿真所得完整传输路径回波损耗与BGA 焊点形态参数间关系进行拟合,结合遗传算法对拟合函数进行优化,得到完整传输路径回波损耗最小的组合参数,并对最优组合参数仿真验证,为减小高频条件下完整传输路径信号完整性提供理论指导.目前,很多科学杂志报道过绝缘体器件上部分和完全耗尽的硅中构建的逻辑单元或组合电路和单晶体管的单事件瞬态(SET)响应[3-8]。

BGA虚焊不良问题分析

BGA虚焊不良问题分析发表时间:2020-12-21T14:50:06.553Z 来源:《科学与技术》2020年8月22期作者:牛毅姬娇[导读] 随着封装技术的不断发展和用户需求的不断提高,牛毅姬娇陕西黄河集团有限公司陕西省西安市710043摘要:随着封装技术的不断发展和用户需求的不断提高,BGA封装器件正朝着近距离、小型化的方向发展。

目前常用的BGA间距已达到0.4pith,最小间距已达到0.3pith。

芯片管脚越来越多,给电子安装工艺带来了新的挑战,BGA元器件在回流焊过程中控制难度越来越高,容易出现虚焊问题,给产品带来了严重的质量问题。

本文在此背景下,分析了回流焊中BGA虚焊的几种主要原因,并提出了相应的控制方法。

关键词:BGA;虚焊;质量1前言球栅阵列封装(BGA)技术是一种应用于集成电路中的表面粘附封装技术,由于其占用空间小、输入输出管脚多等特点,在电子产品中得到了广泛的应用。

但由于焊盘位于设备的底部,在焊接和测试方面存在一些困难。

因此,BGA芯片的焊接一直是电子产品生产中的一个难题。

在BGA芯片的焊接故障中,最常见的故障是虚焊和桥接。

相比之下,桥接容易通过X射线检测,而且不需要破坏器件。

而虚焊问题的检测难度更大,原因也比较复杂。

因此,为了解决BGA器件虚焊问题,必须对其形成机理进行分析。

2.常见的BGA虚焊不良问题2.1虚焊原因分析目前,虚焊实际上是焊盘失效的一种表现形式,表现为焊盘导电性差或焊盘强度差导致器件管脚与焊盘之间呈现一种开路现象。

其根本原因在连接界面上未形成合适厚度(1.5~3.5)um的IMC层。

实际上,造成虚焊的原因很多,包括热不足引起的冷焊、共面性差导致的脱焊、应力引起的焊盘裂纹等。

在目前的电子产品生产中,BGA芯片主要采用回流焊的方式安装在PCB板上。

因此,在锡膏印刷和安装良好的前提下,造成BGA焊盘虚焊的主要原因可分为三类:设计不良(DFM设计不良)、可焊性差(焊料质量不佳、器件引脚可焊性差、PCB 焊盘可焊性差)和热利用不合理(热量过高、热量过低、炉温曲线控制不佳)。

BGA元件引起的不良分析

BGA元件引起的电子产品功能不良分析改善一般的BGA元件导致产品功能不良或性能不稳定主要原因有三点:一是制造不良(虚焊、假焊、连锡、烧坏芯片),二是原材料不良(来料不良或储存不当),其次是设计。

具体问题要具体分析,根据根本原因采取对应措施,以下内容仅做参考分析的方向。

第一部分------原因分析一、原材料不良1.原材料供货时是否本身有一定比例的性能不良。

2.是否是二手物料或呆滞旧料(重新植球锡球大小不均匀或存放很久的库存呆滞料)。

3.BGA是否存放太久(半年以上),供货时已存在锡球表面氧化现象(颜色变暗、发黑、浅灰色)。

二、包装方式1.BGA散料、尾数包装方式是否合理,是否由于包装方式不恰当导致BGA锡球压扁或掉球,是否长期将BGA元件放置在非真空环境中,导致锡球氧化。

2.原包装物料在运输和储存过程能否保证真空包装无破损漏气现象,存放的环境是否符合这类元件要求。

三、贴装前的准备工作1.BGA包装漏气或非真空包装时间超过72小时,是否经过烘烤后贴装。

2.BGA上线前是否经过基本抽检(目视锡球大小是否均匀,锡球表面是否变色,银白色为正常,锡球发黑,颜色变暗或变成浅灰色,证明锡球已经发生不同程度的氧化,有可能导致焊接不良)四、锡膏印刷质量控制1.SMT印刷时是否针对BGA元件焊盘的印刷质量做了100%检查,然后再投入贴片。

2.SMT钢网是否有堵孔现象,导致漏印或少锡;印刷机刮刀压力是否适中,保证锡膏厚度均匀(目测印刷后PCB焊盘上的锡膏无明显拉尖或锡膏厚度不均匀现象)3.印刷前目检BGA焊盘的焊接点大小是否一致,油墨覆盖是否均匀,油墨过后会导致印刷拉尖,锡膏厚度不均匀(目视焊盘大小无明显区别,油墨无明显凸起或目视焊盘明显呈凹下去状态, PCB的油墨厚度在实际操作中可测性不大,目前最实用的非标准检查方式就是目测,可操作性比较强)。

4.PCB表面是否有异物或灰尘,PCB油墨共面性是否有保证。

(目视PCB焊盘与油墨几乎处于同一平面,或用手刮油墨无明显阻力,油墨覆盖不可过厚且厚度要均匀)五、贴装设备(贴片机)贴装BGA元件的设备,是否有激光识别矫正装置,能否识别锡球不大小规则或变形的BGA,能否进行激光图像识别,区别锡球表面是否氧化或少球。

BGA焊接问题分析

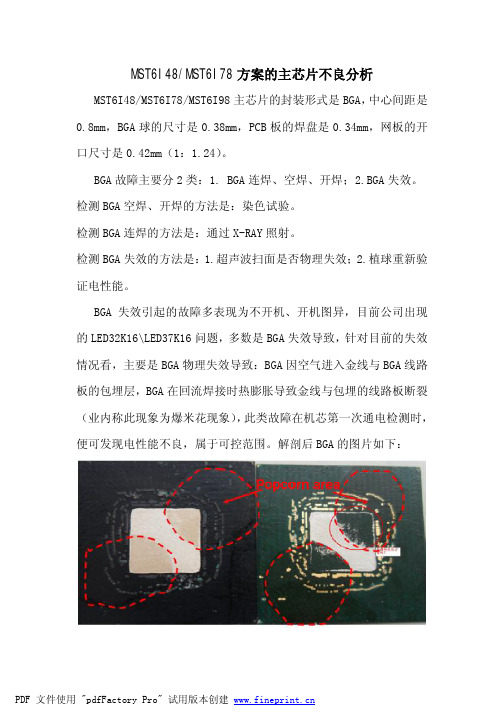

MST6I48/MST6I78方案的主芯片不良分析MST6I48/MST6I78/MST6I98主芯片的封装形式是BGA,中心间距是0.8mm,BGA球的尺寸是0.38mm,PCB板的焊盘是0.34mm,网板的开口尺寸是0.42mm(1:1.24)。

BGA故障主要分2类:1. BGA连焊、空焊、开焊;2.BGA失效。

检测BGA空焊、开焊的方法是:染色试验。

检测BGA连焊的方法是:通过X-RAY照射。

检测BGA失效的方法是:1.超声波扫面是否物理失效;2.植球重新验证电性能。

BGA失效引起的故障多表现为不开机、开机图异,目前公司出现的LED32K16\LED37K16问题,多数是BGA失效导致,针对目前的失效情况看,主要是BGA物理失效导致:BGA因空气进入金线与BGA线路板的包埋层,BGA在回流焊接时热膨胀导致金线与包埋的线路板断裂(业内称此现象为爆米花现象),此类故障在机芯第一次通电检测时,便可发现电性能不良,属于可控范围。

解剖后BGA的图片如下:BGA空焊、开焊引起的电性能故障,生产过程比较难发现,因为我公司第一次通电检测多为直接插屏调试,PCB机芯没有发生变形,开焊、空焊的BGA焊球与PCB仍接触良好,如果发生变形时,电性能故障才可能发生,如前期LED46K11P(0002)出现的花屏、图异现象。

PCB经过螺丝固定后,不可避免会发生轻微变形,通孔安装允许的弓曲和扭曲的程度为1.5%,有表面贴装的板,其弓曲和扭曲允许程度0.75%.LED46K11P(0002)经过老化线后,容易出现故障,原因为:PCB 为FR4的玻纤板,温度升高时在螺丝扭力的作用下变形度会增加,导致BGA焊球与PCB无法接触导致开路,从而出现花屏故障。

空焊通过染色试验可以发现,如果确定了空焊的具体位置,再通过Xray可以把控故障板,如下图:出现故障的焊球明显偏小,原因是PCB焊盘由于网板堵孔没有印上锡膏,没有锡膏与焊球熔融,球偏小,从而出现只接触不焊接现象。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

At 5kv, 150x magnification

At 5kv, 1000x magnification

Solder ball pull down to PCB pad. No separation between BGA ball and pad.

5. METHOD OF ANALYSIS 5.1 Microscope for 500X 5.2 EDX Analysis. Test conditions follow Intel’s: a. At 5kv, 150x magnification, SE image b. At 5kv, 600x magnification, SE image c. At 5kv, 3000x magnification, SE image d. Select the dark side to do EDX Analysis at 15kev. 6. TEST RESULTS 6.1 Ti and Mg did found from the returned coupon after analysis. 6.2 Put solder ball on Pad 4 and Pad 5 and also compare each others, no separation problem. 7. SUMMARY OF ANALYSIS 7.1 20% contamination area and more will cause solder joint problem but 10 % perform well solder contact between solder ball and pad. 7.2 After review all BGA pads, it can be hardly detects the minor Mg and Ti elements at very small area on the two pads only. 8. FUTURE PLANS 8.1 Supplier would like to perform ball shear test for the suspicious pad.

No separation phenomenon found.

The EDX’s analysis for 10% contamination

4. DEFECT MAP 4.1 X-section for Pad 4 (Suspect contamination pad and both Mg and Ti compositions are more than pad 3 ) : No solder joint problem and separation found between solder ball and pad like returned photo from Intel. Pls see below.

At 5kv, 3000x magnification

At 15 Kev C, O, N, Mg, Al, Si, Pb, Sn, Ti

Pad 3 Analysis

At 5kv, 150x magnification

At 5kv, 600x magnification

Hale Waihona Puke At 5kv, 3000x magnification

Pad 3 Pad 4

Pad 3 Pad 4

Returned Coupon

Diagram 1.

2. SAMPLES SUBMITTED For RTV`s x-section (Follow Intel's indicated location: Pad 3 and 4): After EDX analysis, Supplier did find the element Mg、Ti on both pads. The SEM photo & EDX analysis as follows: At 5kv, 150x magnification At 5kv, 600x magnification

SITKA 689998-004 (CHTJD8A) U4G1 (PID) FA Update (Rev:06)

Date: 6/02/01

1. PROBLEM DESCRIPTION 1.1 Perform EDX again for returned the SITKA 689998-004 with U4G1 BGA pad because Intel indicated the error location. 1.2 Follow Intel's indication for pad 3 and pad 4. 1.3 Supplier also chooses pad 5, it is very close pad 3 and pad 4, to put solder ball on these pads and check if any separation between solder ball and BGA pad. The detail location as follows, Pad 5 Pad 5

At 5kv, 150x magnification

At 5kv, 1000x magnification

Solder ball pull down to PCB pad.

No separation between BGA ball and pad.

4.2 X-section for Pad 5 (No contamination) : No solder joint problem and separation found between solder ball and pad. Pls see below.

At 15 Kev C, O, Mg , Si, Pb, Sn, Ti

Pad 4 Analysis

3. PROCESSING CONDITIONS AT FAILURE 3.1 Ti and Mg are found on the legend ink only. Refer to Rev2_Sitka FA on May. 24. 3.2 Per report with the Rev5_Sitka FA on June. 01, the result shows 20 % contamination area and more % with the legend ink on BGA pad will cause solder joint problem. 3.3 But 10 % contamination area with both composition Ti 16.76 % and Mg 1.27 % do not cause solder joint problem. Pls refer to the photos and “ EDX`s analysis for 10% contamination area “ chart. As follows. Pad No. Ink area(%) 1 10% 2 20% 3 30% 4 50% 5 80% 6 90%