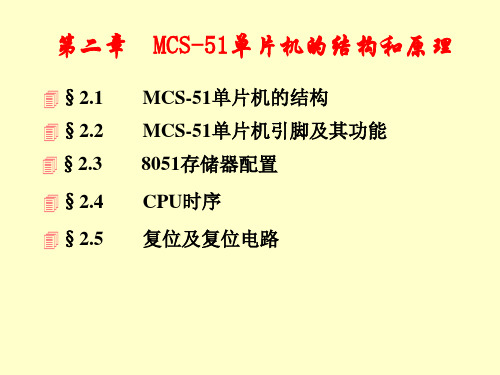

第二章%20MCS-51单片机的结构和原理

合集下载

第02章 MCS-51单片机的结构

CY

AC

F0

RS1 RS0

OV

/

P

PSW位地址

D7H D6H D5H D4H CY AC F0 RS1

D3H RS0

D2H D1H OV

D0H P

CY:进位标志。用于表示Acc.7有否向更高位进位。 加减运算时,保存最高位进位、借位状态。 AC:半进位标志。用于表示Acc.3有否向Acc.4进位。 例:78H+97H 0111 1000 +1001 0111 1 0000 1111

ALU

定时与控制 程序地址寄存器AR

CPU

。

2.2.2 控制器

控制器由程序计数器PC、指令

寄存器和指令译码器、定时和控

制逻辑电路。

相对控制器而言,运算器接受控 制器的命令而进行动作。

1).程序计数器PC

※ PC不属于特殊功能寄存器,不可访问,在物理结构 上是独立的。 ※ 16位的地址寄存器,用于存放下一字节指令的地址, 可寻址64KB的程序存储器空间。 ※ PC的基本工作方式有:

⑴ 自动加1。CPU从ROM中每读一个字节,自动执行 PC+1→PC; ⑵ 执行转移指令时,PC会根据要求修改地址; ⑶ 执行调用子程序或发生中断时,CPU会自动将当前 PC值压入堆栈,将子程序入口地址或中断入口地址装入 PC;子程序返回或中断返回时,恢复原有被压入堆栈的 PC值,继续执行原顺序程序指令。

用示波器检测该引脚来判断单片机是否损坏。

② PROG功能:片内有EPROM的芯片,在EPROM编程 期间,此引脚输入编程脉冲。

⑵ PSEN:片外程序存储器读选通信号输出端。 在向片外程序存储器读取指令或常数期间,每个机

器周期该信号两次有效(低电平)作为片外ROM的

单片机2

图2-1 MCS-51的外部引脚

8

单片机原理与应用

EA /VPP:片外ROM访问允许信号输 出引脚/片内 EPROM编程电压输入引脚。 它的功能是: (1)当 EA =0时,允许单片机访问片外 ROM(不允许使用片内ROM)。所以, 对于无片内ROM的单片机(如8031)此 引脚应接地。 (2)当 EA =1时,允许单片机使用片内 ROM。对于具有片内ROM的单片机, 若该引脚为高电平,则CPU在访问片内 ROM时,当访问地址超过所配置容量的 最大值时,会自动转向访问片外ROM。 (3)在对片内EPROM进行编程时,用 于输入编程电压。

23

单片机原理与应用

7.其他主要部件

暂存寄存器TMP1、TMP2:用于暂时存放从 数据总线或ACC送来的操作数。 程序地址寄存器:用于存放当前指令的地址, 具体数据由程序计数器送入。 指令寄存器:用于存放当前正在执行的指令操 作码(指令的构成在下一章中介绍)。 指令译码器:用于对指令寄存器中的指令操作 码进行分析,并把译码结果送给定时与控制部件, 作为产生微操作控制信号的依据。 内部总线:包括地址总线、数据总线和控制总 线,分别用于传递与它们的名称相对应的信号, 内部总线是各部件间进行信息传递的公共通道, 信号传递过程由CPU全盘控制,分时操作,不会 发生冲突。

1.电源引脚

VCC:+5V电源。 Vss:地线。

图2-1 MCS-51的外部引脚

4

单片机原理与应用

2.外接晶振引脚

XTAL1、2: 用于连接晶体振荡器 和微调电容,以便与 单片机内部的振荡器 构成内部时钟电路, 当采用外部时钟时, 作为外部振荡信号的 输入端。

图2-1 MCS-51的外部引脚

20

第2章MCS-51单片机基本结构

令和四周期指令。

2.1.4

复位和复位电路

单片机在重新启动时都需要复位,MCS-51 系列单片机有一个复位引脚输入端RST。 1. MCS-51系列的单片机复位方法为:在RST上加

一个维持两个机器周期(24个时钟周期)以上

的高电平,则单片机被复位。 2. 复位时单片机各部分将处于一个固定的状态。

复位后单片机各单元的初始状态

R2 2 00

2 2u F

R S T/VP D

R1 1K

V ss

GND

未稳压电源

WDI R1 PFI MR R2 MAX813L P1.0

RESET

WDO

﹠

RST MCS-51

“看门狗”复位电路

2.1.5 MCS-51单片机的引脚功能

MCS-51单片机采用40脚双列直插式封装形式,主要包括以 下几个部分: 1. 电源引脚Vcc和Vss Vcc(40脚):电源端,为十5V; Vss(20脚):接地端 ,GND。 2. 时钟电路引脚XTAL1和XTAL2 XTAL1为内部振荡电路反相放大器的输入端 。 XTAL2为内部振荡电路反相放大器的输出端 。 3. 控制信号引脚RST、ALE、PSEN和EA 4. I/O(输入/输出)端口P0、P1、P2和P3 5. MCS-51单片机P3口的第二功能

单片机各种周期的关系图

机器周期 S1 S2 S3 S4 S5 S6 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2

时钟周期 状态周期

1个机器周期=6个状态周期=12个时钟周期

4、指令周期: 它是指CPU完成一条操作所需的全部

时间。 每条指令执行时间都是有一个或几个机器周

期组成。MCS - 51 系统中, 有单周期指令、双周期指

2.1.4

复位和复位电路

单片机在重新启动时都需要复位,MCS-51 系列单片机有一个复位引脚输入端RST。 1. MCS-51系列的单片机复位方法为:在RST上加

一个维持两个机器周期(24个时钟周期)以上

的高电平,则单片机被复位。 2. 复位时单片机各部分将处于一个固定的状态。

复位后单片机各单元的初始状态

R2 2 00

2 2u F

R S T/VP D

R1 1K

V ss

GND

未稳压电源

WDI R1 PFI MR R2 MAX813L P1.0

RESET

WDO

﹠

RST MCS-51

“看门狗”复位电路

2.1.5 MCS-51单片机的引脚功能

MCS-51单片机采用40脚双列直插式封装形式,主要包括以 下几个部分: 1. 电源引脚Vcc和Vss Vcc(40脚):电源端,为十5V; Vss(20脚):接地端 ,GND。 2. 时钟电路引脚XTAL1和XTAL2 XTAL1为内部振荡电路反相放大器的输入端 。 XTAL2为内部振荡电路反相放大器的输出端 。 3. 控制信号引脚RST、ALE、PSEN和EA 4. I/O(输入/输出)端口P0、P1、P2和P3 5. MCS-51单片机P3口的第二功能

单片机各种周期的关系图

机器周期 S1 S2 S3 S4 S5 S6 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2 P1 P2

时钟周期 状态周期

1个机器周期=6个状态周期=12个时钟周期

4、指令周期: 它是指CPU完成一条操作所需的全部

时间。 每条指令执行时间都是有一个或几个机器周

期组成。MCS - 51 系统中, 有单周期指令、双周期指

第二章--MCS-51单片机的结构

基 本 组 成

5)布尔处理器 MCS-51的CPU是8位微处理器,它还具有1位微处理器的 功能。布尔处理器具有较强的布尔变量处理能力,以位 (bit)为单位进行运算和操作。它以进位标志(Cy)作为累 加位,以内部RAM中所有可位寻址的位作为操作位或存储 位,以P0~P3的各位作为I/O位,同时布尔处理器也有自 己的指令系统。

FFFFH 片外ROM 1000H 0FFFH 0FFFFH

片外RAM或 I/O口

片内ROM

EA =1

片外ROM

EA =0

0000H

0000H

基 本 组 成

图2-2 8051存储器配置图

从用户使用的角度看,8051存储空间分为三类:片内、 片外统一编址0000H~0FFFFH的64KB的程序存储器地址 空间;256字节数据存储器地址空间,地址从00H~0FFH; 64KB片外数据存储器或I/O口地址空间,地址也从 0000H~0FFFFH。上述三个空间地址是重叠的,即程序 存储器中片内外低4KB地址重叠,数据存储器与程序存储 器64KB地址全部重叠,虽然地址重叠,但由于采用了不 同的操作指令及控制信号EA、PSEN的选择,因此不会发生 混乱。

基 本 组 成

在任一时刻,CPU只能使用其中的一组寄存器,并且 把正在使用的那组寄存器称为当前寄存器组。当前寄存器 组由程序状态寄存器PSW中RS1、RS0位的状态组合决定。 非当前寄存器组可作为一般的数据缓冲器使用。

基 本 组 成

图2-3 8051内部数据寄存器配置图

位寻址区(20H~2FH) 内部RAM的20H~2FH单元为位寻址区 ,这16个单元 (共计128位)的每一位都有一个8位表示的位地址,位寻址 范围为00H~7FH。位寻址区的每一个单元既可作为一般 RAM单元使用,进行字节操作,也可以对单元中的每一 位进行位操作。

第2章8051单片机硬件结构和原理

指令寄存器IR及指令译码器ID

• 由PC中的内容指定ROM地址,取出来的指令经IR送至ID, 由ID对指令译码产生一定序列的控制信号,以执行指令所 规定的操作。

振荡器和定时电路

• 8051单片机片内有振荡电路,只需外接石英晶体 和频率微调电容(2个30pF左右),其频率范围为 1.2MHz~12MHz。该信号作为8051工作的基本节拍

片外程序存储器

从程序员角度看存储器

程序存储器保留地址

(1)0000H~0002H三个单元:

• 用作上电复位后引导程序的存放单元。因

为复位后PC的内容为0000H,CPU总是从

0000H开始执行程序。将转移指令存放到 这三个单元,程序就被引导到指定的程序 存储器空间去执行。

程序存储器保留地址

(2)0003H~002AH单元:

使用。

SFR之 程序状态寄存器PSW(D0H)

• PSW是一个8位特殊功能寄存器,它的各位包含

了程序执行后的状态信息,供程序查询或判别之

用。各位的含义及其格式如表2-6所列。

• PSW除有确定的字节地址(D0H)外,每一位均有

位地址

Psw中的位

• CY(PSW.7): 进位标志位。在执行加法(或减法)运算 指令时,如果运算结果最高位(位7)向前有进位(或借 位),则CY位由硬件自动置1;如果运算结果最高位无 进位(或借位),则CY清0。CY也是89C51在进行位操作 (布尔操作)时的位累加器,在指令中用C代替CY。 • AC(PSW.6): 半进位标志位,也称辅助进位标志。当 执行加法(或减法)操作时,如果运算结果(和或差)的 低半字节(位3)向高半字节有半进位(或借位),则AC位 将被硬件自动置1;否则AC被自动清0。 • F0(PSW.5): 用户标志位。用户可以根据自己的需要 对F0位赋予一定的含义,由用户置位或复位,以作为 软件标志。

第2章MCS--51系列单片机的结构及原理

(3)软件标志FO(PSW.5):这是可由用户定义的一个 状态标志,可由用户置位或复位。F1的定义与F0相同。

(4)工作寄存器组选择位RS1、RS0(PSW.4,

PSW.3): RS1、RS0与工作寄存器组的对应关系

如下:

RS1 RS0 工作寄存器组 片内RAM地址

00

第0组

00H~07H

01

第1组

指令执行后,A=D1H最高位无进位,故C=0;低半字节有进位,AC=1; OV=0 1=1,发生溢出;A中1的个数为偶数,故P=0。

CPU时序

一.振荡器

CPU执行指令的一系列动作是在时序电路的控制下一拍一拍进行的。 其节拍信号由振荡器产生,MCS--51系列单片机的内部有一个高增益的反 相放大器。外接晶体后可构成自激振荡器产生节拍信号,接法见图2-1, 也可使用片外振荡器,采用不同工艺制造的单片机芯片接法不同:

RST/VPO:双功能引脚,在单片机工作期间, 当此引脚上出现连接2个机器周期的高电平时可 实现复位操作,详见2.4节。

在Vcc掉电期间,若该引脚接备用电源 (+5v),可向片内RAM供电,以保存片内RAM中 的信息。

2.2 MCS—51系列单片机的微处理器与CPU时序

运算器由算逻运算单元ALU、累加器A、B寄存器、暂存器1、 暂存器2、及程序状态字PSW构成。程序状态字PSW是1个8位 的专用寄存器,用于存放程序运行中的各种状态信息,可 进行位寻址,

P

图2—3 程序状态字各位的含义

(1)进位标志C(PSW.7);很多算术逻辑运算指令执行 后都会影响进位标志C。例如加减运算,若运算结果有进 位或借位,则C=1,若无,则C=0。可用专门的指令或硬件 将C置位或清零,在进行位操作时,C又起着位累加器的作 用,类似于累加器A。

(4)工作寄存器组选择位RS1、RS0(PSW.4,

PSW.3): RS1、RS0与工作寄存器组的对应关系

如下:

RS1 RS0 工作寄存器组 片内RAM地址

00

第0组

00H~07H

01

第1组

指令执行后,A=D1H最高位无进位,故C=0;低半字节有进位,AC=1; OV=0 1=1,发生溢出;A中1的个数为偶数,故P=0。

CPU时序

一.振荡器

CPU执行指令的一系列动作是在时序电路的控制下一拍一拍进行的。 其节拍信号由振荡器产生,MCS--51系列单片机的内部有一个高增益的反 相放大器。外接晶体后可构成自激振荡器产生节拍信号,接法见图2-1, 也可使用片外振荡器,采用不同工艺制造的单片机芯片接法不同:

RST/VPO:双功能引脚,在单片机工作期间, 当此引脚上出现连接2个机器周期的高电平时可 实现复位操作,详见2.4节。

在Vcc掉电期间,若该引脚接备用电源 (+5v),可向片内RAM供电,以保存片内RAM中 的信息。

2.2 MCS—51系列单片机的微处理器与CPU时序

运算器由算逻运算单元ALU、累加器A、B寄存器、暂存器1、 暂存器2、及程序状态字PSW构成。程序状态字PSW是1个8位 的专用寄存器,用于存放程序运行中的各种状态信息,可 进行位寻址,

P

图2—3 程序状态字各位的含义

(1)进位标志C(PSW.7);很多算术逻辑运算指令执行 后都会影响进位标志C。例如加减运算,若运算结果有进 位或借位,则C=1,若无,则C=0。可用专门的指令或硬件 将C置位或清零,在进行位操作时,C又起着位累加器的作 用,类似于累加器A。

第2章 MCS-51单片机

(4)可寻址外部程序存储器和数据存储器,各64KB;

(5)两个16位定时器/计数器; (6)32位可编程并行I/O口; (7)一个可编程全双工串行I/O口; (8)二十多个特殊功能寄存器; (9)5个中断源,两个优先级嵌套中断结构。

2. 微处理器 8051微处理器的组成如下所示:

累 加 器 ACC( Accumulator) 程 序 状 态 字 寄 存 器 PSW( Program Status Word) 运算器 暂存寄存器 CPU 寄存器B 指 令 寄 存 器 IR 控制器 指 令 译 码 器 ID 程 序 计 数 器 PC

(2)位寻址区

内部RAM的0x20~0x2F为位寻址区,这16个字节的每

一位都对应一个8位地址,位地址范围为0x00~0x7F。该区 域可按字节读写,也可按位读写,位地址从0x20单元最低位 开始,共有16×8位,即128个位地址。 如果系统需要位操作,最好保留0x20~0x2F单元的部分

或全部,作为位存储区,以支持位处理操作。位寻址区的每

一位都可以直接进行位操作。通常把各种程序状态标志位控 制变量,设在位寻址区内,同时,位寻址区的RAM单元也 可以作一般的数据缓冲器使用。RAM寻址区位地址映象如 表2-5所示。

位 寻 址 区 地 址 映 象

(3)缓冲器区

内部RAM的0x30~0x7F的地址区,可作为数据缓冲器 使用,存放数据,由于该区有丰富的操作指令,使用十分 方便。 2.外部数据存储器 在51系列中,允许用户扩展外部数据存储器和I/O接口, 用户可以通过P0、P2口最多扩展连接64K个外部单元(每

片机系统。

MCS-51的典型产品是8051、8031、8751。8051是ROM型单片 机,内部有 4KB 掩膜 ROM ; 8031 无片内 ROM , 8751 片内有

第2章 MCS-51单片机的硬件结构

CPU访问片外存储器时,模拟开关打向右边。P2 口上送出PC高8位地址或DPTR高8位地址信息。再不作 I/O口使用。

(2)通用I/O接口功能

P2口作准双向口使用,与P1口相同,也有输入、 输出、端口操作三种工作方式。

3.P2口负载能力

4个LSTTL负载,输出电流≥ 400uA

三、P3口

1. P3口1位结构原理图如图所示

P 奇偶标志

A中1的个数若为奇数P=1,否则P=0

例如:MOV A, #7FH ADD A, #4FH 0111,1111B + 0100,1111B 1100,0110B

结果:(A)=C6H, C=0,AC=1,OV=1,P=0

2.控制器 3.片内存储器

4.4个I/O接口

5.串行接口

6.定时/计数器

先片内、后片外,片内片外连续,二者 一般不作重叠。 EA=0,只访问片外程序存储器 EA=1,先访问片内程序存储器。当PC >0FFFH(51子系统)或PC>1FFFH(52子系统) ,再去访问片外程序存储器。

存储器编址图如下图所示

0000H

片内ROM /EA=1 0FFFH 0FFFH 1000H 片外ROM 0000H 片外ROM /EA=0 00H 7FH 80H FFH 片外RAM 片内RAM 0000H

有5个中断源

11.111条指令,含乘、除法,有很强

的位处理能力 12.片内采用单总线结构,单一+5V

电源

52系列主要有8032、8052两种机型。 与51系列不同在于:片内数据存储器增 至256个字节,3个16位定时/计数器,6 个中断源。

二、内部结构

MCS-51系列单片机的内部结构如 下图所示:

1 2 . . .

(2)通用I/O接口功能

P2口作准双向口使用,与P1口相同,也有输入、 输出、端口操作三种工作方式。

3.P2口负载能力

4个LSTTL负载,输出电流≥ 400uA

三、P3口

1. P3口1位结构原理图如图所示

P 奇偶标志

A中1的个数若为奇数P=1,否则P=0

例如:MOV A, #7FH ADD A, #4FH 0111,1111B + 0100,1111B 1100,0110B

结果:(A)=C6H, C=0,AC=1,OV=1,P=0

2.控制器 3.片内存储器

4.4个I/O接口

5.串行接口

6.定时/计数器

先片内、后片外,片内片外连续,二者 一般不作重叠。 EA=0,只访问片外程序存储器 EA=1,先访问片内程序存储器。当PC >0FFFH(51子系统)或PC>1FFFH(52子系统) ,再去访问片外程序存储器。

存储器编址图如下图所示

0000H

片内ROM /EA=1 0FFFH 0FFFH 1000H 片外ROM 0000H 片外ROM /EA=0 00H 7FH 80H FFH 片外RAM 片内RAM 0000H

有5个中断源

11.111条指令,含乘、除法,有很强

的位处理能力 12.片内采用单总线结构,单一+5V

电源

52系列主要有8032、8052两种机型。 与51系列不同在于:片内数据存储器增 至256个字节,3个16位定时/计数器,6 个中断源。

二、内部结构

MCS-51系列单片机的内部结构如 下图所示:

1 2 . . .

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

16位程序计数器16位程序计数器-PC 位程序计数器

由两个8位的计数器 组成, 存储将要 由两个 位的计数器(PCL,PCH)组成 , PC存储将要 位的计数器 组成 执行的下一条指令的地址, 位可容纳的最大数值为 执行的下一条指令的地址 , 16位可容纳的最大数值为 65535,为 64KB, 因此 , MCS-51可寻址 可寻址64KB的程序存 为 , 因此, 可寻址 的程序存 储器。改变PC内的值 就可改变程序执行的方向。 内的值, 储器。改变 内的值,就可改变程序执行的方向。

VPD:

备用电源。 备用电源。

+5V10uF REST控制管脚 PSENPSEN: :

程序存储器允许输出信号端。在访问片外程序存储器时, 程序存储器允许输出信号端。在访问片外程序存储器时,CPU 控制该端输出负脉冲作为外部存储器的选通信号, 允许CPU读出 控制该端输出负脉冲作为外部存储器的选通信号 , 允许 读出 EPROM中被选中单元中的指令码。该管脚一般连程序存储器的选 中被选中单元中的指令码。 中被选中单元中的指令码 通信号端(OE)。 通信号端 。

§2-2 MCS-51单片机的引脚及其功能 单片机的引脚及其功能

p 1.0

1、电源管脚: 、电源管脚: Vcc,Vss 2、时钟电路管脚: 、时钟电路管脚: XTAL1,XTAL2 3、控制信号脚: 、控制信号脚: RST/VPD, ALE/PROG PSEN及Vpp/EA 及 4、I/O管脚 、 管脚 P0,P1,P2,P3

30

29

p 3 .5 / T 1

p 3 .6 / WR

PSEN

28

p 2 .7

p 3 .7 / RD XTAL 2 XTAL 1

VSS

21

p 2 .0

电源管脚

Vcc:电源端,为5V,允许电源有偏差; :电源端, ,允许电源有偏差; GND(VSS):地。 地

注:为了防止电源脉冲对单片机的影响,一般在 为了防止电源脉冲对单片机的影响, VCC和GND之间接上一个 之间接上一个1uF的电容。 的电容。 和 之间接上一个 的电容

MCS-51单片机结构原理 第二章 MCS-51单片机结构原理

教学目的:掌握MCS-51单片机内部的结构及其组成,了解 单片机内部的结构及其组成, ●教学目的:掌握 单片机内部的结构及其组成 了解CPU、存储器组 、 织结构、并行输入输出口结构,以及51单片机的引脚信号及 单片机的引脚信号及CPU时序。通过 时序。 织结构 、并行输入输出口结构,以及 单片机的引脚信号及 时序 学习,应对MCS-51单片机的硬件结构以及各部分的组成原理有基本了解,建 单片机的硬件结构以及各部分的组成原理有基本了解, 学习,应对 单片机的硬件结构以及各部分的组成原理有基本了解 立起单片机的整体印象,为后续学习打下基础。 立起单片机的整体印象,为后续学习打下基础。

1、中央处理单元CPU(8位) 中央处理单元CPU( CPU 用于数据处理、位操作(位测试、置位、复位) 用于数据处理、位操作(位测试、置位、复位) 2、只读存储器ROM(4KB或8KB) 只读存储器ROM(4KB或8KB) ROM 用于永久性存储应用程序,掩膜 用于永久性存储应用程序,掩膜ROM、EPROM、EEPROM 、 、 3、随机存取存取器RAM(128B/256B) 随机存取存取器RAM(128B/256B) RAM 用于程序运行中存储工作变量和数据 4、并行输入/输出口I/O(32线) 、并行输入/输出口I/O(32线 I/O 用作系统总线、扩展外存、 O接口芯片 用作系统总线、扩展外存、I / O接口芯片

控制管脚 RST/VPD

RST: :

复位信号输入端,高电平有效。保持两个机器周期以上, 复位信号输入端,高电平有效。保持两个机器周期以上,并变 为低电平,单片机开始从0000地址执行,即可完成单片机复位。单 地址执行, 为低电平,单片机开始从 地址执行 即可完成单片机复位。 片机复位不改变片内RAM的值。 的值 片机复位不改变片内

§2-3 MCS-51单片机的存储器配置 单片机的存储器配置

计算机存储结构: 计算机存储结构:

哈佛结构:程序存储与数据存储分开 哈佛结构:程序存储与数据存储分开——单片机 单片机 诺依曼结构: 冯.诺依曼结构:程序与数据存储在一起 诺依曼结构 程序与数据存储在一起——通用计算机 通用计算机 单片机的存储器结构(ROM+RAM) 单片机的存储器结构(ROM+RAM): ROM:常用于存放程序和需要长时间存放的数据,掉电不丢失; :常用于存放程序和需要长时间存放的数据,掉电不丢失 RAM:随时可读可写的存储器,掉电后数据立即丢失。 :随时可读可写的存储器,掉电后数据立即丢失。

ACC

SP 缓冲器

ALU 定 时 控 制 指 令 译 码 器

OSC

PC增1 增 中断、 中断、串行口和定时器 PSW PC

DPTR

PSEN ALE EA RESET

控制器

指 令 寄 存 器

P1锁存器 锁存器 P1驱动器 驱动器

P3锁存器 锁存器 P3驱动器 驱动器 P3.0-P3.7

XTAL1

XTAL2

1、单片机的存储器结构

采用哈佛结构,存在 个物理上相互独立的存储器空间 个物理上相互独立的存储器空间: 采用哈佛结构,存在4个物理上相互独立的存储器空间: 片内程序存储器 片内数据存储器

FFFFH

片外程序存储器 片外数据存储器

FFFFH

片外 64K ROM

0FFFH 片内4K 片内4K ROM 0000H 0FFFH

片外 64K RAM (I/O)

访问片内与片外 RAM靠指令区分 靠指令区分 MOV与MOVX 与

FFH SFR 80H 7FH 00H

EA=1

0000H

EA=0

0000H

片内RAM 片内RAM

2、单片机的程序存储器

常用单片机的程序存储器容量: 常用单片机的程序存储器容量:

型号

8031/32 8051/52 8751/52 89X51/52 W51

返回

P1.0-P1.7

可对4 可对4位(半字节), 半字节), 单字节) 16位 8位(单字节)和16位 累加器,它是最繁忙的8 累加器数据进行操作, 双字节)数据进行操作, (双字节),它是最繁忙的8 位特殊功能寄存器, 位特殊功能寄存器 中央处理器(CPU) 中央处理器(CPU) 数据来自两个暂存器。 数据来自两个暂存器。,用A 表示,ALU的运算结果存 表示,ALU的运算结果存 在此处。 在此处。 包含运算器 控制器两部分 运算器和 包含运算器和控制器两部分 位寄存器, 8位寄存器,在乘除运算 位的ALU ALU: (1)8位的ALU: 时,用来存放另一个操作 并存放一部分结果。 数,并存放一部分结果 位程序状态字寄存器, 8位程序状态字寄存器, 。 位累加器ACC ACC( ): (2)8位累加器ACC(A用于存放指令执行后的状 态信息, 态信息,供程序查询和判 位寄存器B: (3)8位寄存器 : 别。 位寄存器 运算器 布尔操作器

8051单片机 8051单片机 内部结构图

RAM地址 地址 寄存器

存储器

P0.0-P0.7 P0驱动器 驱动器

P2.0-P2.7 I/O接口 接口

P2驱动器 驱动器

128B RAM

P0锁存器 锁存器

P2锁存器 锁存器

4KBROM

程序地址 寄存器

B寄存器 寄存器 运算器

暂存器1 暂存器

暂存器2 暂存器

振荡器及定时控制电路

MCS-51 片 内 有 振 荡 器 OSC , 通 过 单 片 机 的 XTAL1,XTAL2连接片外的石英晶体及两个频率微调电容, 连接片外的石英晶体及两个频率微调电容, 连接片外的石英晶体及两个频率微调电容 产生单片机工作所需要的基本时钟—节拍 节拍。 产生单片机工作所需要的基本时钟 节拍。

5、串行输入/输出口UART(二线) 串行输入/输出口UART(二线) UART 串行通信、扩展I O接口芯片 串行通信、扩展I / O接口芯片 6、定时/计数器T/C(16位增量可编程) 定时/计数器T/C(16位增量可编程) T/C(16位增量可编程 它与CPU之间各自独立工作,当它计数满时向CPU中断 它与CPU之间各自独立工作,当它计数满时向CPU中断 CPU之间各自独立工作 CPU 7、时钟电路 fosc 分为内部振荡器、 分为内部振荡器、外接振荡电路 8、中断系统 五源中断、两级优先,可编程进行控制。 五源中断、两级优先,可编程进行控制。

时钟电路管脚

XTAL1:芯片内部反相放大器输入端,使用外部振荡器时需接地。 :芯片内部反相放大器输入端,使用外部振荡器时需接地。 XTAL2: 芯片内部反相放大器输出端,使用外部振荡时接振荡器输 芯片内部反相放大器输出端, 入的信号。 入的信号。

XTAL2

外部振荡器

XTAL2

XTAL1

XTAL1

内部振荡方式

(4)8位程序状态寄存器PSW: 位程序状态寄存器PSW: PSW (5)布尔处理器: 布尔处理器: (6)2个8位暂存器: 位暂存器:

中央处理器(CPU) 控制器 中央处理器(CPU)—控制器 (CPU)

(1)程序计数器(PC) 程序计数器(PC) (2)指令寄存器(IR) 指令寄存器(IR) 控制器 (3)指令译码器(ID) 指令译码器(ID) (4)振荡器及定时与控制电路

p 1.7

RST

p 3 .0 / RXD

1

40 39

VCC

p 0 .0

8

9 10 11

12

32

31

p 0 .7

p 3 .1 / TXD

p 3 .2 / INT 0

p 3 .3 / INT 1 p 3 .4 / T 0

Vpp / EA

ALE / PROG