一种新型线阵CCD驱动电路的设计方法

基于CPLD的线阵CCD的驱动电路设计与实现

ห้องสมุดไป่ตู้

摘 要: C C D驱动时序 电路 的设计实现是其应用 的关键 问题。该 文在分析 T C D 1 2 0 9 D线阵 C C D的工作原 理和驱动时序等特性的基础上 , 提 出了一种基 于 C P L D的线阵 C C D驱动电路的设计方法 , 其 中选用 MA X I l 系歹 4 C P L D作为硬件设计平台 , 运用 V H D L 语 言设计 驱动时序电路 。该设计 使用 Q u a r t u s I I 软件对所设

l o g i c d e v i c e( C P L D ) i n t h i s p a p e r . I n o r d e r t o r e a l i z e t h e t i me s e q u e n c e d r i v i n g , t h e MA X I I d e v i c e s W a S u s e d

计的驱动程序进行 了仿真 , 仿真与实验结果表 明该方案设计可行 , 电路结构简单 , 集成度较 高 , 实用性强 ,

并具有一定通用性 。 关键词 : 线阵 C C D ; 驱动时序 电路 ; 复杂可编程逻辑器件 ; V H D L

中图分类号 : T N3 8 6 . 5 文献标识码 : A 文章 编号 : 1 0 0 3 - 0 1 0 7 ( 2 0 1 3 ) 1 0 — 0 0 1 3 - 0 5

线阵CCD驱动电路的设计

线阵CCD驱动电路的设计摘要本文论述了线阵CCD驱动电路的工作原理和现状,选择了基于CPLD驱动线阵CCD工作的方案。

采用MAXⅡ器件的EPM240T100C5N为控制核心,JTAG 端口向CPLD中下载程序,以TCD1500C为例,设计了基于CPLD的线阵CCD 驱动电路,完成了硬件电路的原理图的设计,编写了SH、φ、RS脉冲的程序,为CCD工作提供了驱动脉冲,并实现了软件调试。

通过QUARTUSⅡ软件平台对程序的模拟仿真,表明本文研究的基于CPLD的线阵CCD驱动电路能够满足CCD工作所需的驱动脉冲,达到了课题要求。

关键词:线阵CCD,复杂可编程逻辑器件,驱动时序,硬件描述语言The Design of Linear CCD Driving CircuitABSTRACTIn t his paper, working principle and current application status of the linear CCD driving circuit is introduced. After comparition, CPLD is selected as the driving methodology. EPM240T100C5N of MAXⅡdevices is selected as the control center and JTAG is used as the download program port. With TCD1500C for example, linear CCD driving circuit based on CPLD is designed, the hardware design is finished. The software procedures for the SH, φ,RS pulses, which provides driving pulses for the operation of CCD and realizes the regulation is developed and debugging. Software simulation based on the QUARTUSⅡplatform prooved that this linear CCD driving circuit can meet the driving pulses needed for CCD activities and satisfy the requirements for the subject.KEY WORDS:linear CCD, complex programmable logic device, driving time, hardware description language目录第一章绪论 (1)1.1课题的背景、意义 (1)1.2课题的研究内容 (1)1.3国内外的研究状况及发展趋势 (1)第二章总体方案设计 (3)第三章硬件设计 (5)3.1线阵CCD驱动电路的工作原理 (5)3.1.1 线阵CCD的工作原理 (5)3.1.2 TCD1500C的主要特性参数 (7)3.1.3 驱动电路的工作原理 (9)3.2CPLD器件的选择 (10)3.2.1 可编程逻辑器件的发展历程............................ 错误!未定义书签。

CCD驱动电路及处理电路设计

线阵CCD系统设计童列树驱动电路设计:TCD1209D采用双向时钟驱动,要正常驱动此CCD工作,除了要提供电源外,还需提供6个驱动的信号:SH转移脉冲信号、RS复位脉冲信号、CP缓冲控制脉冲信号、Ф1和Ф2(Ф2b)模拟移位寄存器的驱动双相脉冲信号。

其中Ф2和Ф2b都是Ф2转移电极的驱动信号,只是Ф2b在模拟移位寄存器上所处的位置最靠近输出端,信号电荷将从Ф2b电极下的势阱通过输出栅转移到输出端。

但是Ф2b和Ф2的时序是一样的,可以合为一路信号,所以CCD实际上只要5路信号。

转移脉冲SH的高电平期间,驱动脉冲Ф1必须为高电平,而且保证SH的下降沿落在Ф1的高电平上,这样才能保证光敏区的信号电荷并行地向模拟移位寄存器的Ф1电极转移。

完成信号电荷的并行转移后,SH变为低电平,光敏区与模拟位移寄存器被隔离。

在光敏区进行光积累的同时,模拟位移寄存器在驱动时钟中Ф1和Ф2的作用下,将转移到模拟移位寄存器的Ф1电极里的信号电荷向输出方向移动,在输出端得到被光强调制的序列脉冲输出。

ADC的选择:对于驱动电路来说,还要对ADC进行控制,系统所用的数模转换芯片是AD9224。

AD9224是一款12位,40MSPS的高性能的模数转换器,它具有高性能采样保持放大器和参考电压参考。

因为AD9224使用的时候受ADC 时钟的控制,图3所示是其工作的采样时序图。

AD9224 概述:AD9224是一款单芯片、12位、40 MSPS 模数转换器(ADC ),采用单电源供电,内置一个片内高性能采样保持放大器和基准电压源。

AD9224采用多级差分流水线架构,内置输出纠错逻辑,在40 MSPS 数据速率时可提供12位精度,并保证在整个工作温度范围内无失码。

AD9224 特性∙ 低功耗:415 mW ∙ +5 V 单电源 ∙ 保证无失码∙ 微分非线性(DNL )误差:±0.33 LSB ∙ 片内采样保持放大器和基准电压源 ∙ 信噪比(SNR ):68.3 dB∙无杂散动态范围(SFDR ):81 dB ∙ 超量程指示∙ 数据输出格式:标准二进制 ∙ 28引脚SSOP 封装 ∙与3 V 逻辑兼容AD9224 参数AD9224 基本参数分辨率(Bits) 12吞吐率 40 MSPS AD9224 其他特性 工作电压(V) 4.75-5.25 输入通道数 1AD9224 封装与引脚SSOP28信号的调理:在带有模拟电路的设计中,信号的调理成为不可缺少部分。

积分可调的线阵CCD驱动设计与实现

技 术前 沿 ・

积分 可调的线阵 C D驱动设计与实现 C

田 庄

( 汉 理 工 大 学 理 学 院 湖 北 武 汉 武

40 7 ) 3 0 0

【 摘 要 】 彩 色线 阵 图 像 传感 器 TCD2 5 D 为例 ,分 析 了 电荷 耦 合 器件 的 工 作 原 理及 驱 动 要 求 ,针 对 改 变 光积 分 时 间 的 问题 ,提 以 22 出 r两种 解 决 方 案 ,并 进 行 仿 真 测试 , 结 果 证 明 没计 方 案 可 进 行 光 积 分 调 节 。 [ 键词】 关 CCD 积 分 可 调 TCD2 5 D 22 【 图分类号】 中 TM [ 献标 识码】 文 A 【 章 编 号 ]0 7 4 6 ( 0 0)0 —0 6 —0 文 l 0 —9 1 2 1 3 07 2

改 变 以 适 应 测 量 要 求 。 CCD 的 光 积 分 时 间 太 短 , 光 敏 元 内 积 累 的 电 荷 少 , 输 出 信

i r s n f ii g

—

e g (lc t e d eco k) n h i(o n e <c n tt e f u tr o s)h n c

c oun e < = c unt r 1 tr o e+ :

的 读取 l 3 】

l

cnt o s<=2 2 5 ( d +1; 2 5 *Na d ) p p o e sco k a: r cs(lc )

b g e m

荷 耦 合 器 件 , 作 为 一 种 新 型 的 光 电 传 感 器

件 ,具 有 分 辨 率 高 、性 能稳 定 、 寿命 长等 特 点 , 在 现 代 光 电 子 学 和 非 接 触 测 量 等 方 面有广泛的应用 。 CCD 的 正 常 ] 作 对 驱 动 时 序 要 求 严 二 格 , 在 不 同 的 工 作 环 境 , 光 积 分 时 间 也 应

线阵CCD驱动电路的可编程设计与实现

1 冼 进. Verilog HDL数字控制系统设计实例. 北京 : 中国水利水 电出版社 , 2007: 232—235

2 元华明. 高分辨率全帧 CCD 驱动电路技术研究. 西安 :中国科学 院研究生院 , 2006: 7—10

3 求是科技. CPLD / FPGA 应用开发技术. 北京 : 人民邮电出版社 , 2005: 23—35

END;

2. 3 驱动电路时序仿真与实验测试 采 用 EPM7064STC44210 作 为 目 标 器 件 , 用

VHDL 语言描述整个设计 ,并在 QuartusⅡ5. 1 集成 环境下完成整个设计的输入 、编译 、仿真 ,最终生成 编程烧录文件 。在仿真过程中 ,将 CP的周期设为 250 ns,即 CP的频率为 4 MHz。仿真波形图如图 3 所示 。

4106

科 学 技 术 与 工 程

8卷

从仿真图中可知 , sh高电平脉冲宽度为 4个 CP 周期即 1 μs, fm、fccd频率分别为 2 M、0. 5 M ,恰好 是 TCD132D 手册中的典型驱动频率要求 ,可见符合 设计要求 。

由于 sh 的 时 间 比 较 长 (在 本 设 计 中 设 定 为 10000个 CP周期 ) ,在仿真图中不能完全表现出来 , 然后 对 实 际 电 路 使 用 示 波 器 (型 号 为 R IGOL DS5152M )进行测量 ,实测波形图如图 4、图 5所示 , 对比可得出仿真结果和实测结果吻合 。电路可稳 定输出 1M 的像元同步脉冲 (它与 CCD 驱动脉冲同 频率 ) , 此处行同步脉冲周期即 CCD 积分时间为 1. 156 m s,实际应用时由于考虑到光照强度的问题 , 积分时间没有设为 2. 5 m s,而是 1. 156 m s(编程时 r 最大值取为 4 624) ,这里即体现了积分时间可调的 可编程设计思想 。

基于CPLD技术的新型线阵CCDTCD1501的驱动时序设计与实现

第26卷第3期2007年9月武 汉 工 业 学 院 学 报Journal of W uhan Polytechnic University Vol 126No 13Sep 12007 收稿日期:2007204217作者简介:李强(19802),男,河南省驻马店市人,助教。

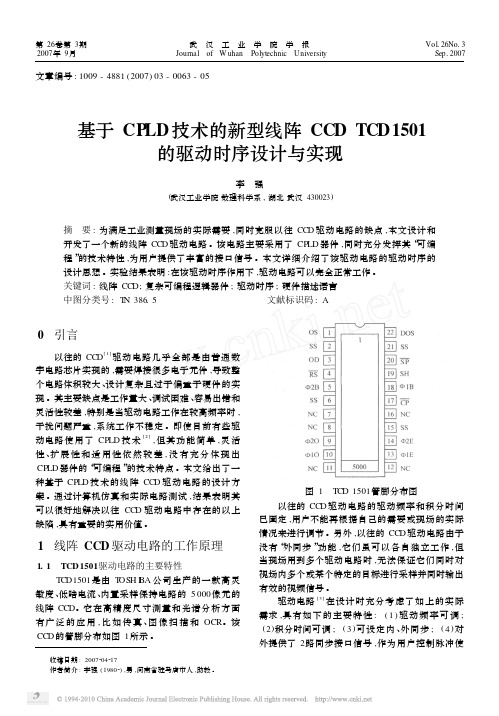

文章编号:1009-4881(2007)03-0063-05基于CP LD 技术的新型线阵CCD TCD1501的驱动时序设计与实现李 强(武汉工业学院数理科学系,湖北武汉430023)摘 要:为满足工业测量现场的实际需要,同时克服以往CCD 驱动电路的缺点,本文设计和开发了一个新的线阵CCD 驱动电路。

该电路主要采用了CP LD 器件,同时充分发挥其“可编程”的技术特性,为用户提供了丰富的接口信号。

本文详细介绍了该驱动电路的驱动时序的设计思想。

实验结果表明:在该驱动时序作用下,驱动电路可以完全正常工作。

关键词:线阵CCD;复杂可编程逻辑器件;驱动时序;硬件描述语言中图分类号:T N 386.5 文献标识码:A0 引言以往的CCD [1]驱动电路几乎全部是由普通数字电路芯片实现的,需要焊接很多电子元件,导致整个电路体积较大、设计复杂且过于偏重于硬件的实现。

其主要缺点是工作量大、调试困难、容易出错和灵活性较差,特别是当驱动电路工作在较高频率时,干扰问题严重,系统工作不稳定。

即使目前有些驱动电路使用了CP LD 技术[2],但其功能简单,灵活性、扩展性和适用性依然较差,没有充分体现出CP LD 器件的“可编程”的技术特点。

本文给出了一种基于CP LD 技术的线阵CCD 驱动电路的设计方案。

通过计算机仿真和实际电路测试,结果表明其可以很好地解决以往CCD 驱动电路中存在的以上缺陷,具有重要的实用价值。

1 线阵CCD 驱动电路的工作原理1.1 TCD 1501驱动电路的主要特性T CD1501是由T OSH I B A 公司生产的一款高灵敏度、低暗电流、内置采样保持电路的5000像元的线阵CCD 。

基于CPLD 的线阵CCD 的驱动电路

1 总体方案设计线阵CCD 一般不能直接在测量装置中使用,因此CCD 驱动信号的产生及输出信号的处理是设计高精度、高可靠性和高性价比线阵CCD 驱动模块的关键。

传统驱动CCD 的设计方法使CCD 的工作频率较慢,信号输出噪声增大,不利于提高信噪比,不能应用于要求快速测量的场合。

而用器件CPLD 进行驱动,则可提高脉冲信号相位关系的精度,以及提供给CCD 驱动脉冲信号的频率,而且调试容易、灵活性高。

目前,在工业技术中,多采用基于CPLD 的实现线阵CCD 的驱动。

系统框图如图1 所示。

图1 基于CPLD 的线阵CCD 的驱动电路2 硬件设计2. 1 CPLD 的硬件电路的设计以CPLD(Complex Programmable Logic Device)器件为核心,设计线阵CCD 的驱动电路。

然后在其基础上扩展,选择其他元器件,设计出与其相配套的电路部分,经调试后组成硬件系统。

CPLD 的电路由5 部分组成,有源晶振向EPM240T100C5N 的U1A 的IO/GCLK0 口输入时钟脉冲CLK0,提供了CPLD 工作的时钟脉冲,因为时序逻辑的需要。

U1C 从JTAG 端口中下载程序,U1B 的52、54、56、58 口输出脉冲信号。

U1D 管脚接3. 3 V 电压,U1E 管脚接地。

电路原理如图2 所示。

图2 CPLD 的电路原理图2. 2 DC /DC 模块的设计为得到CPLD 所需的电压,外接电源需要经过DC /DC 模块进行转换。

为进一步减少输出纹波,可在输入输出端连接一个LC 滤波网络,电路原理如图3所示。

图3 DC/DC 模块的电路原理图设计2. 3 稳压模块的由DC /DC 模块转换的直流电压,经过一个R11电阻和一个发光二极管接地,发光二极管指示灯,然后从AMS 芯片的Vin端输入,进入到芯片的内部,经过一系列的计算,从Vout输出3. 3 V 电压,GND 端端口接地。

为消除交流电的纹波,电路采用电容滤波,分别用0. 1 μF 的极性电容和10 μF 的非极性电容组成一个电容滤波网络。

线阵CCD图像传感器驱动电路的设计

线阵CCD图像传感器驱动电路的设计1 引言电荷耦合器件(CCD.Charge(Couple DevICe)是20世纪60年代末期出现的新型半导体器件。

目前随着CCD器件性能不断提高.在图像传感、尺寸测量及定位测控等领域的应用日益广泛.CCD应用的前端驱动电路成本价格昂贵,而且性能指标受到生产厂家技术和工艺水平的制约.给用户带来很大的不便。

CCD驱动器有两种:一种是在脉冲作用下CCD器件输出模拟信号,经后端增益调整电路进行电压或功率放大再送给用户:另一种是在此基础上还包含将其模拟量按一定的输出格式进行数字化的部分,然后将数字信息传输给用户,通常的线阵CCD摄像机就指后者,外加机械扫描装置即可成像。

所以根据不同应用领域和技术指标要求.选择不同型号的线阵CCD器件,设计方便灵活的驱动电路与之匹配是CCD应用中的关键技术之一。

本文以TCD1501C型CCD图像传感器为例.介绍了其性能参数及外围驱动电路的设计.驱动时序参数可以通过VHDL程序灵活设置.该电路已成功开发并应用于某型非接触式位置测量产品中。

2 CCD工作原理CCD是以电荷作为信号,而不同于其他大多数器件是以电流或者电压为信号,其基本功能是信号电荷的产生、存储、传输和检测。

当光入射到CCD的光敏面时.CCD首先完成光电转换.即产生与入射光辐射量成线性关系的光电荷。

CCD的工作原理是被摄物体反射光线到CCD器件上.CCD根据光的强弱积聚相应的电荷.产生与光电荷量成正比的弱电压信号,经过滤波、放大处理,通过驱动电路输出一个能表示敏感物体光强弱的电信号或标准的视频信号。

基于上述将一维光学信息转变为电信息输出的原理,线阵CCD可以实现图像传感和尺寸测量的功能。

图1为CCD光谱响应曲线。

3 驱动电路的实现线阵CCD TCD1501C的主要技术指标如下:像敏单元数为5 000;像元尺寸为7μm×7μm;像元中心距为7μm;像元总长为35 mm;光谱响应范围为400 nm-1000 nm.光谱响应峰值波长为550 nm,灵敏度为10.4 V/lx.s~15.6 V/lx.s。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一种新型线阵CCD 驱动电路的设计方法[作者:丁忠林 刘尧猛 张建民 转贴自:微计算机信息 点击数:328 更新时间:2008-10-20【字体: A 】 design and application of dynamic CCD Driving Circuit Abstract: in this paper a new way to design linear array CCD driving circuit is presented 。

in the desi gn ,PLD is used to control the CCD optical-integral-time dynamically without changing the primary fre quency of the system .so the CCD optical-integral-time can be changed with the intensity of the backgr ound lamp-house so as to improve the system precision and avoid the saturation distortion problem of t he CCD output signal.This method has been applied in the stripple steels vertical cutting centering-system and been proved to be highly effective.Key word :linear array CCD;dynamic control; CCD optical-integral-time;driving signals;摘要:本文提出了一种新型线阵CCD 驱动电路的设计方法。

采用该方法,不改变系统工作主频就可以动态控制CCD 光积分时间随着光源强度变化而变化,从而提高了系统精度,解决了CCD 输出信号因环境影响引起的饱和失真和背景与物体无法分开的问题。

此电路用可编程逻辑器件EPM7032C44实现,已将该方法应用于带钢纵切机组自动对中系统中,获得良好的效果。

关键词:线阵CCD ;动态控制;光积分时间;驱动信号1 前言线阵CCD 具有体积小、分辨率高、稳定性好、抗干扰性强、测量误差小等特点[1],被广泛应用于非接触工件尺寸的测量中。

线阵CCD 应用的关键是驱动信号的产生及输出信号的处理[2]。

驱动信号由驱动电路产生,因而在线阵CCD 应用中需要着重考虑驱动电路设计。

目前常用的有以下三种CCD 驱动电路设计方法:(1) 直接数字电路驱动法该方法电路的实现复杂,调试困难,使用不便[2]。

(2)单片机驱动法该方法单片机输出的驱动信号频率低,速度慢,不适合应用在高速数据采集中[3]。

(3)记数分频法该方法是通过改变系统主频或者计数器的初始预置值实现积分时间的改变,灵活性差。

系统主频的改变将影响模拟通道的处理,而计数初值的改变会影响驱动波形[3]。

以上三种方法均属于静态驱动方法,CCD光积分时间不受背景光强的控制。

而在实际应用中,CCD是工作在复杂恶劣的环境中,CCD的输出信号与光的强度和CCD单元的光积分时间成正比。

在CCD光积分时间一定的情况下,光的强度过高时,CCD输出信号会出现饱和失真;光的强度过低时,输出信号过低,使得景物与背景模糊,无法分开。

本文提出了一种采用动态控制CCD光积分时间的新型线阵CCD驱动电路设计方法,即背景光强时使CCD光积分时间短;背景光弱时,使其积分时间长些,从而使CCD输出信号在正常工作范围内。

此外,在基于DSP带钢纵切机组自动对中系统中,采用本方法,利用可编程逻辑器件通过控制CCD的光转移脉冲周期改变光积分时间,从而在系统主频不变的情况下,使CCD驱动信号和输出信号在恶劣的环境中正常工作。

2 CCD的结构、工作原理及驱动波形2.1 CCD的结构电荷耦合器件(Charge Couple Device,简称CCD)是一种新型光电传感器件。

它的基本单元是MOS结构,它能存储由光产生的电荷信号,当对它施加特定时序脉冲时,其存储电荷能在CCD内作定向移动而实现自扫描,输出电压信号的大小与CCD单元存储的电荷多少成正比[4],CCD单元存储电荷多少与光的强度和CCD单元光积分时间成正比。

TCD1206UD型线阵CCD结构框如图1所示。

它由2236个pn结光电二极管构成光敏元阵列,其中前64个和后12个是用作暗电流检测而被遮蔽的,用符号Dn表示;中间的2 160个光电二极管是曝光像敏单元,每个光敏单元的尺寸为14μm长、14μm高、中心距为14μm,用Sn 表示。

光敏元的两侧是存储其电荷的MOS电容列——存储栅。

MOS电容列两侧是转移栅电极SH。

转移栅的两侧为CCD模拟移位寄存器,其输出部分由信号输出单元和补偿输出单元构成[4]。

2.2 CCD工作原理及驱动信号波形CCD只有在一定的驱动脉冲作用下才能正常工作。

下面以TCD1206UD为例说明CCD的工作原理,其驱动脉冲波形如图2所示。

ФSH是转移脉冲,其作用是将CCD单元存储电荷转移到模拟移位寄存器中。

φ1、φ2脉冲的作用是使模拟移位寄存器的电荷信号移动,通过OS输出。

ΦR是复位脉冲,复位一次OS输出一个信号。

当光照在TCD1206UD上,第一个ФSH脉冲由高变低时,CCD单元存储栅势阱进入光积分状态并产生存储电荷。

当第二个ФSH脉冲由低变高时,将CCD单元存储点荷转移到模拟移位寄存器中。

CCD的光积分时间是两个ФSH脉冲间隔,存储电荷转移时间是ФSH的脉宽时间。

模拟移位寄存器在Φ1与Φ2脉冲的作用下将上次转移到电极下势阱中的电荷信号向左转移,并经过输出电路由OS电极输出。

按照其结构的安排,OS端首先输出13个虚设单元信号,再输出51个暗电流信号,然后连续输出S1到S 2160有效像素单元信号。

第S2160信号输出后,又输出9个暗信号,再输出2个奇偶检测信号,以后便时空驱动。

空驱动数目可以是人意的,可利用它来延长光积分时间。

由于该器件是两列并行,分奇、偶传输的,所以在一个ФSH周期中至少要有1118个φ1脉冲,即TSH>1118T0。

如果TSH小于1118T0,那么上次数据没有读完就开始下一次读数,使输出信号产生失真。

如果积分时间长,CCD的输出电压幅度就高,会产生输出饱和失真[4]。

为了提高系统的检测灵敏度,使CCD的积分时间增长但又不使输出信号失真,有两种方法:(1)利用空驱动数量来增加TSH内的时钟脉冲数[5]。

(2)降低输出速率,但这样会影响信号处理电路的参数、频带、信噪比[6]。

所以选择第一种方法来增加光积分时间比较好,这样可以动态调节光积分时间。

因此,本文采用了在系统时钟频率不变的情况下,光积分时间根据CCD工作环境的背景光源强度的变化通过改变空驱动脉冲数量达到动态控制CCD的目的。

3 动态控制CCD光积分时间电路的设计由于CCD的镜头会受到灰尘和背景光的强度影响,会使CCD输出信号失真,增大检测误差,为了解决此问题采用动态控制CCD光积分时间的新型线阵CCD驱动电路,即背景光强时,使其积分时间短;背景光弱时,使其积分时间长,从而使输出信号在正常工作范围内。

其逻辑电路如图3所示。

该电路设计了CC D正常工作脉冲ФSH、φ1、φ2 、φR ,并可动态地调整光积分时间。

为了保证各个脉冲同步工作,采用统一主频时钟T0。

φ1、φ2是由主频时钟二分频和一个非门得到。

φR是通过主频时钟经逻辑电路产生。

而转移脉冲φSH则通过计数器产生,其工作原理是当基本计数器计到2236后,产生计数满信号,使光积分延时预置计数器计数,预置初值确定空驱动数目,其取值范围为1~4095。

当光积分延时预置计数器计满时,清除基本计数器进行下一次计数,并产生转移脉冲φSH。

光积分延时预置计数器计数预置初值是由微处理器根据采集电荷信号来检测光的强弱通过接口电路自动设置。

该电路可以通过微处理器动态控制CCD光积分时间,以提高检测精度。

此电路能够达到的最小光积分时间为2236T0,最大光积分时间为2236T0 +4096T0。

动态控制CCD光积分时间电路用可编程逻辑器件EPM 7032C44实现的,以下是用Verilog DHL设计此驱动电路的程序module Drive(φSH, φ1, φ2, φR,Data,T0);input T0;input[11:0] Data;outputφSH, φ1, φ2, φR;reg φ1, φ2, φR;regφSH,Clr,Start_signal,Signal_del;reg[11:0] Data_reg,Base_count;reg[8:0] Sh_count;parameter n= 2236 ;always@(posedge T0)beginφ1=~φ1;φ2=~φ1;endalways@(T0) φR =T0;always@(posedge T0)beginif(Base_count==n)beginsignal_del=1;Base_count= Base_count +1;Start_signal =1;endelseif(Base_count >n+2) Base_count =n+3;elsebeginsignal_del=0;Base_count = Base_count +1;endif(Clr)beginBase_count =0;Start_signal =0;endendalways@(posedge T0)beginif(signal_del)Data_reg = Data;if(Start_signal)beginif(Data_reg ==4095)beginClr =1;endelse Data_reg = Data_reg +1;endif(Clr)beginif(Sh_count ==500)beginSh_count =0;Clr =0;endelse Sh_count = Sh_count +1;endendalways@( Clr)beginif(Clr)φSH=1;elseφSH=0;endendmodule4 动态CCD驱动电路的应用线阵CCD常常工作在恶劣的环境中,背景光源的变化会产生CCD的检测误差加大,降低了系统的检测精度,系统采用动态控制CCD光积分时间驱动电路可解决此问题,提高系统的精度。

动态CCD驱动电路应用系统框图如图-4所示,系统的工作原理:线阵CCD采集的信号通过抗干扰电路和A/D转换、存储并送给微处理器,微处理器对这些数据进行处理,确定光积分延时计数预值并传输给动态CCD驱动电路,动态CCD驱动电路产生CCD驱动信号来驱动CCD工作。