数字电子技术第三章

北京航空航天大学:数字电子技术基础 教学课件第三章 组合数字电路

X2=–0.1011011

[X1]反=0.1001010 [X2]反=1.0100100

X3=–1101001 [X3]反=10010110

小数反码定义为 [X]反=

【例如】

X

2–2–n+X

当0≤X<1

当–1 < X≤0

n—二进制小 数数值的位数

[X]反=2–2–6+(–0.101101)

②二进制、 八进制、十六进制转换成十进制 二进制、八进制或十六进制转换成等值的十进 制数时,可按权相加的方法进行。 【例如】 (1011.01)2=1×23十0×22十1×21十1×20十0×2-1十1×2-2 =8+0+2+1+0+0.25=(11.25)10 (167)8=1×82十6×81+7×80=64+48+7=(119)10

2.二进制

在 二进制数中,每一位仅有0、1两个数码。计数规 律:逢二进一。任意一个二进制数可以表示为 (S)2=kn-12n-1+kn-22n-2+...+k020+k-12-1+k-22-2+...+k-m2-m = Ki 2 i

i=n–1 –m

其中,ki:只能取0或1 m、n:正整数,n为整数位数,m为小数位数 2:二进制的基数 2i: 称为第i位的权 【例如】 (101.101)2=1×22十0×21十1×20十1×2-1十0×2-2十1×2-3

一、数制

1.十进制 在 十进制数中,每一位有0—9十个数码。计数规 律:逢十进一。 任意一个十进制数(S)10可以表示为

(S)10=kn-110n-1+kn-210n-2+...+k0100+k-110-1+...+k-m10-m

数字电子技术课件 第3章_集成逻辑门电路

释放的过程,如同电容器的充、放

电一样,表现出一定的电容效应,

称其为结电容。因结电容的存在,

当外加电压由出反向跳变为正向时,

PN结内部要建立起足够的电荷梯度

才开始形成正向扩散电流,因而正

向导通电流的建立要滞后于输入电

压正跳变的时刻。二极管由反向截

止转换为正向导通所需的时间,一

般称为开启时间。

图3.2. 4 二极管的开关时间

表3.2.2 三极管工作状态的特点

工作状态

截止

放大

条件

偏置情况 工 作 集电极电流 特 管压降 点

c.e间等效内阻

iB 0

发射结和集电 结均为反偏

iC 0

VCEO ≈Vcc 约数百千欧 相当于关断

0<iB<Ics/β 发射结正偏 集电结反偏

iC≈βiB VCE= Vcc-ICRC

可变

饱和

iB> Ics/β 发射结和集电 结均为正偏

MOS管作开关使用时,通常是工作在截止区和可 变电阻区。在数字电路中,用得最多的是N沟道增强型 MOS管和P沟道增强型MOS管,它们是构成CMOS数 字集成电路的基本开关元件。由于P沟道增强型MOS 管和N沟道增强型MOS管在结构上是对称的,两者工 作原理和特点也无本质区别,只是在PMOS管中,栅 源电压VGS、漏源电压VDS、开启电压VTP均为负值。

第3章 集成逻辑门电路

3.1 概述 3.2 基本逻辑门电路 3.3 TTL集成逻辑门电路 3.4 CMOS集成逻辑门电路 3.5 TTL电路与CMOS电路的接口

本章学习目的和要求

1. 熟悉半导体器件的开关特性,了解分立元件基 本门电路、TTL门、ECL门、CMOS门电路的结 构 特点、工作原理和电气特性;

数字电子技术基础第三章

二、交流噪声容限

反相器对窄脉冲 的噪声容限—交 流噪声容限远高 于直流噪声容限。

交流噪声容限受 电源电压和负载 电容的影响。

图3.3.23 CMOS反相器的交流噪声容限

三、动态功耗

动态功耗:当CMOS 反相器从一种稳定工 作状态突然转变到另 一种稳定的过程中, 将产生附加的功耗。

PD=PC+PT PD为总动态功耗 PC为对负载电容充放

图3.3.xx CMOS三态门电路结构之三 可连接成总线结构。还能实现数据的双向传输。

3.3.6 CMOS电路的正确使用

一、输入电路的静电防护

1、在存储和运输CMOS器件时最好采用金属屏蔽层 作包装材料,避免产生静电。

2、组装、调试时,应使电烙铁和其他工具、仪表、 工作台面等良好接地。操作人员的服装、手套等选用 无静电的原料制作。

图3.5.34 OC门输出并联的接法及逻辑图

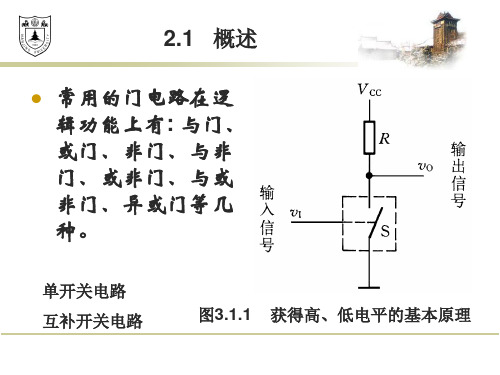

2.1 概述

常用的门电路在逻 辑功能上有: 与门、 或门、非门、与非 门、或非门、与或 非门、异或门等几 种。

单开关电路 互补开关电路

图3.1.1 获得高、低电平的基本原理

图3.1.2 正逻辑与负逻辑

一些概念

1、片上系统(SoC) 2、双极型TTL电路 3、CMOS

1961年美国TI公司,第一片数字集成电路 (Integrated Circuits, IC)。

C=1时 Vo=RL*Vi/(RL+RTG) RTG越小越好,并且希望不 受输入电压变化。

图3.3.39 CMOS模拟开关接 负载电阻的情况

四、三态输出的CMOS门电路

高阻态。 此电路结构 总是接在集 成电路的输 出端。

图3.3.40 CMOS三态门电路结构之一

数字电子技术第三章逻辑门电路

(2)基本应用

模拟开关作为数据选择器 1)C=0时,TN管截止,TP 导通,A点为1,TG1开通, TG2关断,L=X;

2)C=1时,TN管导通,TP 截止,A点为0,TG2开通, TG1 关断,L=Y。

4051模拟开关芯片内部结构

8个模拟开关

4052模拟开关芯片内部结构

双4路模拟开关

3.1.9、 CMOS电路的优点

1. 集成度高,静态功耗小。 2. 允许电源电压范围宽(118V)。 3. 扇出系数大,抗噪容限大。

3.2 TTL逻辑门电路

1、三极管的开关特性

①当Vi=-V时,发射结反偏截止 Ic≈ 0,Vce≈Vcc。 开关断开

②当Vi=+V时,通常调节Rb使得Ib>Ics/β

T饱和,此时Ic=Ics,Vce≈0.3V, 三极管饱和导通。 开关闭合

第三章 逻辑门电路

3.1、 MOS门电路 3.1.1 NMOS 开关 负载线

ID

vi=“1”

0 vo=“0”

vi=“0”

UDS

vo=“1”

3.1.2 NMOS 开关特性:

(1) Vi=0(Vi<VT ) ,MOS管截止,类似开关断开,Vo =1(高电平);

(2) Vi=1(Vi>VT ) ,MOS管饱和导通,开关接通呈现一个 小的接通电阻,若Ron<<RL , Vo =0(低电平); (3) MOS管开关具有延迟

=1

=0

C

C

Ron<<RL

3.1.3 NMOS 非门

(1)电阻RL实际用MOS管替代;

(2)T1为工作管(增强型),T2为负载管(耗尽型)始终 导通,但导通电阻Ron2>>Ron1。 (3) Vi=0(Vi<VT ) ,T1截止, T2导通,Vo =1(高电平);

数字电子技术第三章-2

根据全加器的逻辑功能可知 (CO)i=AiBi+(Ai+Bi)(CI)i 设:AiBi=Gi, Ai+Bi=Pi 得 (CO)i=Gi+Pi(CI)i =Gi+Pi[Gi-1+Pi-1(CI)i-1] = Gi+PiGi-1+ Pi Pi-1[Gi-2+Pi-2(CI)i-2] …… =Gi+PiGi-1+ Pi Pi-1Gi-2+……Pi Pi-1……P1G0 +Pi Pi-1……P0C0 因为CO=0,所以当A和B输入时即可计算出各位的CI, 使运算速度大大提高。

以三位为例

CO3 G3 P3 CI 3 G3 P3 (G2 P2CI 2 ) G3 P3 [G2 P2 (G1 P CI1 )] 1

MSI 四位超前进位加法器74LS283的逻辑 图见P167、逻辑框图如下

3.用加法器设计组合逻辑电路: 逻辑函数能化成变量相加的可用。

( A A ) D

1 0

4

( A1 A0 ) D5 ( A1 A0 ) D6 ( A1 A0 ) D7 A2

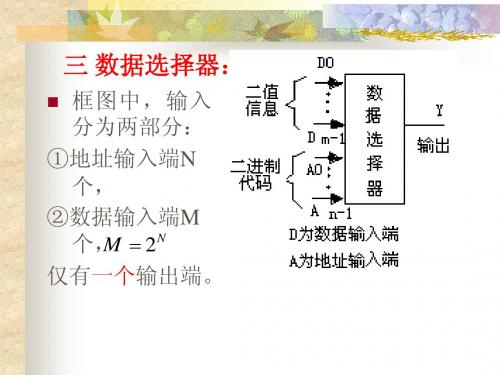

2. 用数据选择器设计组合逻辑电路:

数据选择器 ①只可实现单输出的逻辑函数; ②地址输入端的个数可等于逻辑函数的 变量数,也可比逻辑函数的变量数少1个 例:分别用四选一和八选一数据选择器 设计交通灯监视电路。

74LS153的逻辑结构 图如右图 S1 0 时

Y1 D10 A1 A0 D11 A1 A0

12 1 0 13 1 0 1

D A A D A A S

Y2的表达式类似。

万里学院-数字电子技术基础-第三章习题及参考答案

第三章锁存器与触发器一、选择题1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.33.对于D触发器,欲使Q n+1=Q n,应使输入D= 。

A.0B.1C.QD.Q4.存储8位二进制信息要个触发器。

A.2B.3C.4D.85.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD.Q6.对于T触发器,若原态Q n=1,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD.Q7.在下列触发器中,有约束条件的是。

A.主从JK F/FB.主从D F/FC.同步RS F/FD.边沿D F/F8.对于JK触发器,若J=K,则可完成触发器的逻辑功能。

A.RSB.DC.TD.Tˊ9.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=0B.J=Q,K=QC.J=Q,K=QD.J=Q,K=0E.J=0,K=Q10.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=QD.J=Q,K=1E.J=1,K=Q11.欲使JK触发器按Q n+1=0工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=1D.J=0,K=1E.J=K=112.欲使JK触发器按Q n+1=1工作,可使JK触发器的输入端。

A.J=K=1B.J=1,K=0C.J=K=QD.J=K=0E.J=Q,K=0 13.欲使D触发器按Q n+1=Q n工作,应使输入D= 。

A.0B.1C.QD.Q14.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从RS触发器C.同步RS触发器D.主从JK触发器15.下列触发器中,没有约束条件的是。

A.基本RS触发器B.主从RS触发器C.同步RS触发器D.边沿D触发器16.为实现将JK触发器转换为D触发器,应使。

数字电子技术基础 第3章

三极管 截止状态 等效电路

Uth为门限电压

第 3 章 集成逻辑门电路

返回首页

一、三极管的静态开关特性

iC u S 为放大和饱和的交界点,这时的临界饱和线I 增大使 iB 增大, 放大区 从而工作点上移, iC 增 iB 称临界饱和基极电流,用 IB(sat) 表示; M T 相应值:IC(sat) 为临界饱和集电极电流; S 大,uCEI减小。 IC(sat) B(sat) UBE(sat) 为饱和基极电压; 饱 Q UCE(sat) 为饱和集电极电压。对硅管, 和 截止区 UBE(sat) 0.7V, UCE(sat) 0.3V。三极 A 区 管在临界饱和点仍然具有放大作用。 U O N u

输入级

中间级

输出级

CT74H系列TTL与非门

第 3 章 集成逻辑门电路

返回首页

3.3.1 TTL 与非门

一、 TTL 与非门的工作原理

R1 R4 VCC +5V

2.8 k

B1

760

C2 C1

R2

58

V3 V2 R5 V4

A B

V1

4 k

VD1 VD2

470

R3

中间级由V2和R2、R3 逻辑符号 组成。V2 集电极和发射极 Y 分别输出两个不同逻辑电 V5 平的信号,分别驱动 V3和 V5。

第 3 章 集成逻辑门电路

返回首页

一、门电路的作用和常用类型

门电路 (Gate Circuit) 指用以实现基本逻辑关系和常用复合逻辑关系的 电子电路。

常用的逻辑门电路:

与门 或门 非门 异或门 与非门 或非门 与或非门

数字电子技术第三章1.pdf

G3 G2 G1 G0 0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

自然二进制码至格雷码的转换

G3 = B3

GG12

= =

B3 B2

⊕ B2 ⊕ B1

G0 = B1 ⊕ B0

推广到一般,将n位自然二进制码转换成n位格

输出

Si Ci+1 00 10 10 01 10 01 01 11

全加器逻辑符号

Ci CI ∑

Si

Ai

Bi

CO

Ci+1

学生自己完成逻辑电路

例5:试将8421BCD码转换成余三BCD码。

(1)真值表

(2)卡诺图

B3BB12B0 00 01 11 10

00 0 0 0 0

01 0 1 1 1

11 ☓ ☓ ☓ ☓

BC A

00

01

11

10

00 0 0 1

10 1 1 1

BC A

00

01

11

10

00 0 0 1

10 1 1 1

两圈相切有险象

增加冗余圈克服险象

三、冒险现象的消除

1.增加冗余项

2. 增加选通信号

增加选通信号的方法比较简单,一 般无需增加电路元件,但选通信号必须 与输入信号维持严格的时间关系,因此 选通信号的产生并不容易。

6 0 110 1 001

7 0 111 1 010

8 1 000 1 011

9 1 001 1 100

10 1 0 1 0 ☓ ☓ ☓ ☓

11 1 0 1 1 ☓ ☓ ☓ ☓