封装中修改PAD

Cadence17.2 PadEditor入门指南

Cadence 17.2 Pad Editor 入门指南(2)创建自定义焊盘及封装Pad Editor 与Allegro PCB Designer 相互配合,可以做出各种类型的封装。

当我们需要制作相对简单的封装时,可以用Pad Editor图形库中现成的图形制作封装,但当我们接触到一个新的元器件时,封装的焊盘就需要自己动手进行制作。

本章,我就带大家制作一个SOIC 封装的自定义焊盘以及封装。

自定义焊盘的制作主要分为两步,第一步就是使用Allegro PCB Designer 建立一个图形文件,第二步就是用Pad Editor 利用这个图形文件建立焊盘。

一、焊盘图形文件的制作1.1 、新建一个Shape Symbol 符号:打开PCB Dedigner-->File-->New-->shape symbol首先给自己的图形起一个名字,选择好路径,类型选择Shape Symbol ,点击o k。

Allegro 的symbol类型有一下几个:Board symbol :板Board(wizard) :板向导Module :模块符号Package symbol :一般封装符号Package symbol(wizard) :一般封装符号向导Mechanical symbol :机械符号Shape symbol :形状符号Flash symbol :导通符号但我们常用的有一下五中,它们分别是Package Symbol 、Mechanical Symbol 、Format Symbol 、Shape Symbol 、Flash Symbol 。

每种Symbol 均有一个Symbol Drawing File( 符号绘图文件), 后缀名均为*.dra 。

此绘图文件只供编辑用, 不能给A llegro 数据库调用。

Allegro 能调用的Symbol 如下:1.1.1 、Package Symbol一般元件的封装符号, 后缀名为*.psm 。

pads元件封装制作教程

PowerPCB元件制作在PowerPCB的元件库来说,很多人都会混淆一个问题,就是Part type和Part Decal 这两个概念。

简单地说,放在PCB上面大家看得到的就是Part Decal,Part Type表示元件类型,是供导入网络表时对应的,这个和allegro中的symbol和drawing是一个意思。

举个简单的例子,我在原理图中放了一颗电解电容假设名叫CE1,我就定它的footprint为CE1。

而我在PCB中对这个电解电容做了两个对应的封装,一个叫CE1H11,这个是立式安装形式,另一个叫CE1L11,代表卧式封装。

如果没有一个Part Type的东西也许我们会很困难去对应,但在PowerPCB中有了这个,我就定义一个Part Type叫做CE1type指向立式和卧式两个封装,设一个优先,这样在导入网表的时候会抓到这个Type,两个封装就同时调用,PCB 布局的时候我们就可以根据需要自由地选择封装了。

具体的作法在后面会讲到,我们先理解一下这个概念就可以了。

对于PowerPCB中元件的制作,主要有以下一些方面的东西要注意1. PAD的制作;2. 丝印的制作;3. 元件高度的定义;4. Part type的对应;其中前面三项都是制作Part Decal,现在我们具体地讲一下元件制作的详细步骤。

一.元件Decal的制作元件Decal的制作可以用手动的,对于一些标准件可以用系统提供的wizard来做。

我们可以有两种方式进入元件Decal编辑窗口。

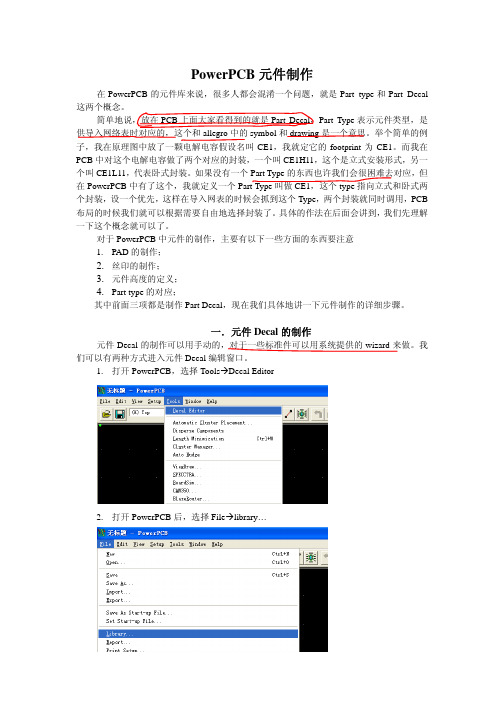

1. 打开PowerPCB,选择ToolsÆDecal Editor2. 打开PowerPCB后,选择FileÆlibrary…在这个图中,不论我们点击Decals,Parts等都看不到任何东西,因为我们还没有元件库在里面,这里,如果我们要新建一个元件库,须点击New Lib…,如要加载一个已有的元件库进来,则点击Lib. List…。

allegro 遇到的问题汇总 避免忘记

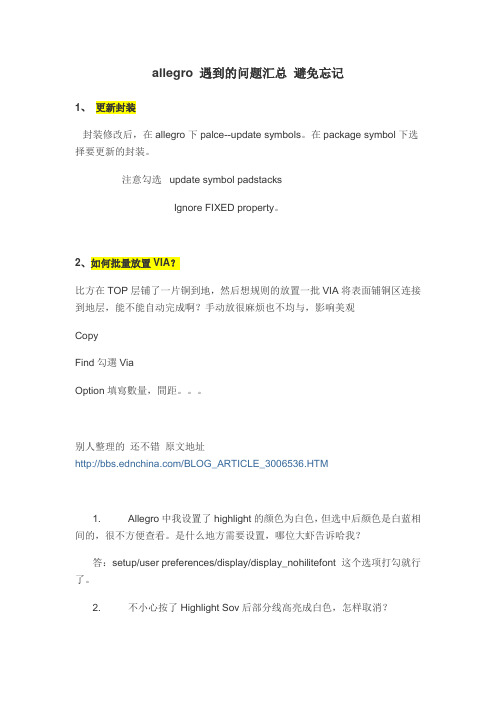

allegro 遇到的问题汇总避免忘记1、更新封装封装修改后,在allegro下palce--update symbols。

在package symbol下选择要更新的封装。

注意勾选update symbol padstacksIgnore FIXED property。

2、如何批量放置VIA?比方在TOP层铺了一片铜到地,然后想规则的放置一批VIA将表面铺铜区连接到地层,能不能自动完成啊?手动放很麻烦也不均与,影响美观CopyFind勾選ViaOption填寫數量,間距。

别人整理的还不错原文地址/BLOG_ARTICLE_3006536.HTM1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->Temporary Highlight里修改即可,临时修改颜色可以点Display->Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer 那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer即可。

5. 快速切换层快捷键答:可以按数字区里的“-”或“+”来换层。

芯片叠封技术 pad电容

芯片叠封技术 pad电容

芯片叠封技术是一种将多个芯片堆叠在一起,形成一个整体的封装结构的技术。

在芯片叠封技术中,PAD电容是指在芯片堆叠过程中,通过在芯片之间添加电容器来增加芯片之间的电容。

PAD电容的作用主要有以下几个方面:

1. 降低电源噪声:在芯片堆叠过程中,由于芯片之间的电源共享,会产生一些电源噪声。

通过在芯片之间添加PAD电容,可以提供更低的电源噪声,提高芯片的性能和可靠性。

2. 提高信号完整性:芯片之间的电容器可以提供更好的信号隔离,减少信号干扰,提高信号完整性。

3. 优化功耗和性能:通过在芯片堆叠过程中添加PAD电容,可以优化芯片的功耗和性能。

在高性能芯片中,PAD电容可以提供更好的电源稳定性和信号完整性,从而提高芯片的工作效率和性能。

4. 提高散热效果:PAD电容可以作为散热器的一部分,在芯片堆叠过程中有效地散热,提高芯片的散热效果。

PAD电容在芯片叠封技术中起到了重要的作用,可以提高芯片的电源稳定性、信号完整性、功耗和性能,并提供散热效果。

ALLEGRO封装教程

一、手工制作封装1、打开“PAD Designer”如下界面按实际需求填好后保存,如保存为cd160X30注:阻焊层比助焊层大约1MM即可2,启动Allegro PCB Ediror 选择“File”-“New”弹出对话框3、点击OK进入编辑界面,选择“SETUP”-“Design Parameters”弹出窗口4、选择“SETUP”-“Grids”打开以下窗口设置5.选择“SETUP”-“User Preference”打开以下界面6,添加管脚焊盘。

选择“LAYOUT”---“PINS”或者图标,然后设置控制面板”options”标签页中的相关选项7,设置好后,在命令窗口中输入放置的坐标如( x 0 0)按回车键确定添加。

注意,输入坐标时x要用小字母加空格8焊盘放置完成后添加Place_Bound_Top(放置约束)。

选择”SETUP”—“Areas-“—“Package Boundary”选项。

设置控制面板的”Options”然后用坐标输入放置9、设置封装限制高度,选择”SETUP”—“Areas-“—“Package Height”选项。

然后选择该封装。

设置控制面板的”Options”10、添加丝印外框。

选择“Add”—“Line”选项,设置控制面板中“Options”然后按封装要求画出丝印框11.添加标签,选择“LAYOUT”--“LABELS”—“RefDes”选择。

设置控制面板中“Options”单击屏幕区域出现文本输入框,输入标签如U* j* REF 右键单击选择“DONE ”12,选择“File”---“Save”选项,保存元件封装二、O RCAD和ALLEGRO交互式布局1,打开原理图,选中文件,然后选择“options”-----“Preferences”出现下界面三、更改坐标原点的方式1、打开文件,选择“SETUP”--“Design Parameter Editor”弹出以下界面2,第2种方式,选择“SETUP”—“Change Drawing Origin”然后单击需要设置成为坐标原点的地方四、O r CAD导出网络表打开原理图文件,选择设计文件,选择“Tloos”--“Create Netlst”弹出以下界面五、ALLEGRO导入网络表1,设置路径:选择“SETUP”-“User Preference”打开以下界面2、选择“File”--“Import”---“Logic”弹出以下界面。

allegro 封装更新到PCB中,不通过网络表实现

allegro更新封装封装修改后,在allegro下palce--update symbols。

在package symbol下选择要更新的封装。

注意勾选(建议全勾上)(1)update symbol padstacks(2)Reset customizable drill data--重置自定义钻孔数据。

如果要更新焊点的钻孔误差值, 钻孔符号, 钻孔符号字元, 及钻孔大小。

可勾选此项就会全部更新钻孔(3)Reset symbol text location and size--重置符号文本的位置和尺寸(4)Ignore FIXED property--忽略固定属性则表示在设计元件输入时,忽略元件的固定属性。

当满足替换条件或者其它更改删除时是否忽略有FIXED属性的元件、走线、网络等等。

Allegro brd文件更新封装及焊盘方法对于allegro软件,很多时候需要在其brd文件中更新元件的封装或是焊盘,本文主要介绍其更新元件封装及焊盘方法及操作步骤。

一、allegro 更新封装方法及操作步骤a) 在allegro中更改需要更新的元件封装,并保存,记住其封装名称;b) 打开brd文件,选择菜单中的Place->Update Symbols,即出现下图所示画面:c) 选择需要更新封装的元件,点击Refresh即完成封装更新。

二、allegro 更新焊盘方法及操作步骤a) 在Pad Designer中修改对应的焊盘,并保存,记住其焊盘名称;b) 用allegro软件打开brd文件;c) 选择Tools->Padstack->Replace,右侧的Option菜单即出现如下图所示的画面:d) 在此菜单中,选择需要更新的焊盘,点击Replace即完成元件焊盘封装更新。

pcb建封装pad的标准

pcb建封装pad的标准

PCB建封装PAD的标准因不同的封装类型和应用需求而异,以下是几种常

见的标准:

1. 欧规(European Standard):通常以公制(mm)表示,尺寸包括

14mm、10mm、7mm、5mm等。

2. 美规(American Standard):通常以英制(inch)表示,尺寸包括、、等。

3. JEDEC标准:是一种常见的电子封装标准,主要应用于集成电路封装。

常见的JEDEC标准包括SOIC、DIP、SIP等,尺寸范围也较广。

4. IPC标准:是一种电子互连行业标准,主要应用于PCB和电子组件之间

的互连。

IPC标准包括IPC-7351、IPC-7352等,对封装尺寸、间距、焊盘尺寸等都有详细的规定。

需要注意的是,不同的封装类型和应用需求会有不同的标准,因此在选择封装类型和尺寸时,需要根据具体的应用场景和要求进行选择。

同时,还需要考虑到PCB板的设计和制造工艺,以确保良好的电气性能和可靠性。

Allegro PCB封装库的设计与规范

这种管理方式的优点是占用的资源比较少,当要批量更新焊盘的时候只要更新PAD库里 的焊盘,再刷新一下电路板就ok,这就是为什么用Allegro打开PCB会比用Protel快的原因,资 源是一点点省下来的。

1 Allegro封装库基本介绍

与Protel封装的区别

Allegro 封装库的 PAD number是唯一的, Protel PCB封装库PAD number可以不唯一。 这就要求我们在设计原理图库的时候Pin number也要和Allegro封装库对应起来,否 则设计的电路图没法导入Allegro里作PCB设计。

例如:bga484_1r00_23x23 表示484 管脚,球间距为1mm,Body size 为23mm 乘以23mm 的BGA 封装。

qfp100_0r50_16x16 表示100 管脚,脚间距为0.5mm,最大外型尺寸为16mm 乘以 16mm 的QFP 封装。 3)SOP、SO、SSOP、TSOP、TSSOP 类封装元件: sop/tsop/ssop/tssop+管脚数_Pitch_Full size 宽度 例如: tssop8_0r65_4r90 表示管脚数为8,管脚间距为0.65mm,Full size 宽度为4.9mm 的 TSSOP封装。

2 Allegro封装库设计规范

PCB 封装名称的命名方法。

1)标准两管脚分立器件: 阻容感等贴装分立器件,根据国际标准命名法则0402、0603、1206、1210、1805…等,以 其实体英制大小进行标准命名。 2)集成芯片类封装元件: 比如:BGA、 QFP、QFN、PLCC、 DFN、SON等等类型芯片,命名规则为: 芯片类型+管脚数_Pitch_Full size

2 Allegro封装库设计规范