基于FPGA的微波炉定时系统设计

微波炉eda

elsif min10'event and min10 = '1' then -- 设置十分位时间

if time3 < 9 then

time3 := time3 + 1;

else

time3 := "0000"; -- 十分位最大为9,超过置0

end if;

if timeTotal <= "1001100101011001" then-- 在 5999 秒内

if time0 = "0000" then

if time1 /= "0000" then-- 向十秒位借位

time1 := time1-1;

time0 := "1001";-- 借位后一秒位为 "1001"

time1 := "1111";

time0 := "1111";

end if;

elsif timeTotal > 0 then

time0 := time0 - 1;-- 不需要借位则直接用一秒位减一

end if;

end if;

减计数模块的设计中,采用了if 嵌套的模式,处理各位的借位。当clock时钟上升沿到来即执行一次判断。程序中并没有采用直接对信号进行赋值,而是重新再进程中重新定义了四个临时的信号。处理完成后再赋值给中间信号 tSec1,tSec10,tMin1,tMin10。 由于变量赋值的即时性,程序也方便将信号赋给测试信号测试。

( 4 )当十分位不为零,如果borrow位为1则减一后清零借位信号borrow,置位一分位和一秒位为"1001 "即为9,置位十秒位为"0101"。为零则减计数完毕。置位tSec1、tSec10、tMin1、tMin10为"1111"。结束减计数程序。

微波炉智能控制系统设置毕业论文

微波炉智能控制系统设置毕业论文目录绪论第一章课题的设计1.1 任务的提出1.2 课题的内容和要求1.3 设计的目的和意义第二章关键技术简介2.1 FPGA简介2.2 VHDL语言概述2.3 Quartus II 开发系统简介开发系统简介第三章系统总体设计3.1 系统总体设计方案3.2 系统功能模块描述3.2.1 输入模块3.2.2 控制模块3.2.3 显示模块3.3 系统的工作流程第四章硬件系统设计4.1 输入模块设计4.1.1 键盘扫描4.1.2 键盘译码4.1.3 输入模块的实现4.2 控制模块的设计4.2.1 状态转换控制4.2.2 数据装载4.2.3 烹饪计时4.2.4 温度控制4.2.5 控制模块的实现4.3 显示模块的实现第五章软件系统设计5.1 输入模块仿真5.2 状态转换器仿真5.3 数据装载器仿真5.4 烹饪计时器仿真5.5 显示译码器仿真第六章总结致谢参考文献附录1 绪论随着人民生活水平的提高,微波炉开始进人越来越多的家庭,它给人们的生活带来了极大的方便。

微波炉由2450MHz 的超高频来加热食物。

它省时、省电、方便和卫生。

方便和卫生。

作为现代的烹饪工具,作为现代的烹饪工具,作为现代的烹饪工具,微波炉的控制器体现着它的重要性能指微波炉的控制器体现着它的重要性能指标。

目前大部分微波炉控制器采用单片机进行设计,目前大部分微波炉控制器采用单片机进行设计,电路比较复杂,电路比较复杂,电路比较复杂,性能不够灵性能不够灵活。

本文采用先进的EDA 技术,利用Quartus Quartus IIII 工作平台和VHDL 设计语言,设计了一种新型的微波炉控制器系统。

设计了一种新型的微波炉控制器系统。

该系统具有系统复位、该系统具有系统复位、该系统具有系统复位、时间设定、时间设定、时间设定、烹饪计烹饪计时、温度控制和音效提示等功能,在FPGA 上实现。

上实现。

第一章 课题的设计1.1. 任务的提出在现代人快节奏生活中,微波炉已成为便捷生活的一部分。

基于FPGA的微波炉控制器的设计

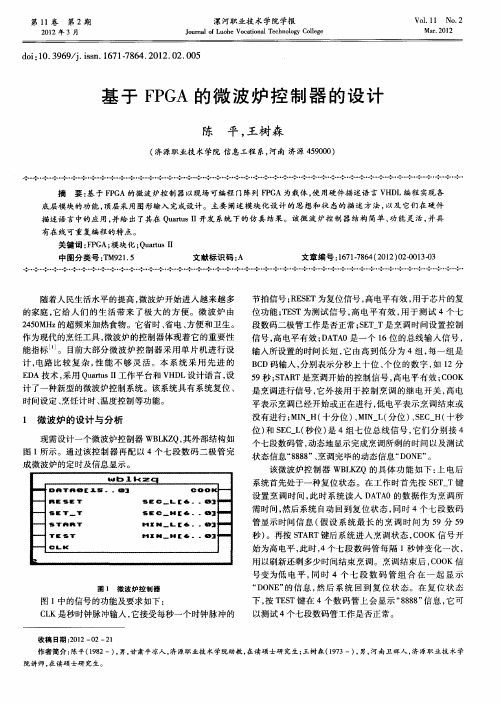

1 微波 炉的 设计 与分析

现需设 计一 个微波 炉控 制器 WB K Q, L Z 其外部 结构 如

图1 所示 。通过该 控 制 器再 配 以 4 七 段 数 码 二极 管 完 个 成 微波 炉的定 时及信 息显示 。

trb 1 k 2 a t

^ T — o £墓 嚣 -

R 慧 霉 慧 t 臀 蕾 T — T 尊 _ T 一 糍

基 于 F G 的 微 波 炉 控 制 器 的 设 计 PA

陈 平, 王树 森

( 济源职业技 术学院 信息工程 系, 河南 济源 49 0 ) 5 00

摘

要: 于FG 基 P A的 微 波 炉 控 制 器 以现 场 可 编 程 门 阵 列 F G 为载 体 , 用硬 件描 述 语 言 V D PA 使 H L编 程 实现 各

需 时问 , 系统 自动 回到 复位 状 态 , 然后 同时 4个七 段 数 码

管 显示 时间 信 息 ( 设 系统 最 长 的 烹 调 时 间 为 5 假 9分 5 9

秒) 。再 按 S A T键后 系统 进 入 烹调状 态 ,O K信 号 开 TR CO 始 为高 电平 , 此时 , 个七 段 数 码管 每 隔 1 钟变 化一 次 , 4 秒 用 以刷新 还剩 多少 时间结 束 烹调 。烹 调结 束 后 , O K信 CO

中图分类号 :M9 15 T 2 .

文献标识码 : A

文章编号 :6 17 6 (0 2 0 - 1-3 17 -84 2 1 ) 20 30 0

孛 . . . . . . ・ ・ ,夺 . . . ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ 夺 夺 夺 夺 争 争 夺 { ・ 幸 幸 幸 夺 夺 夺 夺 夺 争 夺 夺 孛 夺 夺 夺 夺 夺 夺 孛 孛 牵 夺 孛 夺 孛 夺 夺 幸 夺 争 夺 夺 夺 夺 ÷ 夺

基于Verilog的微波炉控制器的设计

基于FPGA 的微波炉控制器的设计一、设计任务及要求该实验主要完成微波炉控制器的设计。

主要功能有复位开关、模式选择、烹调时间设置、LED 指示烹调状态及数码管显示烹调剩余时间。

上电后,系统处于复位状态。

工作时首先进行烹调时间设置,并使用数码管显示时间信息,设要求最长的烹调时间为59分59秒,时间设置完毕后系统处于等待状态状态;选择开始烹调模式时系统进入烹调状态,时间显示数码管按每秒减1的倒计时方式显示剩余烹调时间;烹调结束后,系统回到复位状态。

二、设计方案及流程微波炉控制器系统主要有一下五个电路模块组成:分频模块、模式选择电路、时间设置电路、倒计时模块、显示模块。

分频模块完成系统50MHz 的时钟向1Hz 的分频,使计时器能够按照1S 的频率倒计时。

模式选择电路,其功能是控制微波炉工作过程中模式的切换,选择不同的模式系统计入不同的工作状态。

时间设置模块,该模块主要是可根据用户需求输入烹调时间;倒计时电路会根据用户所设置的时间进行倒计时,由数码管显示电路显示目前烹调状态,同时由LED 灯指示系统反正在烹调。

系统总体框图如下:系统的输入输出信号如下:输入clk ,key0,key1,key2,key3,key4五个信号,输出hex0,hex1,hex2,hex3,sec_flag ,cook 六个信号。

时间设置模块50MHz 分1Hz 的 分频模块数码管显示电路倒计时电路模式选择模块图1 系统总体框图clk作为50MHz分频模块的输入,时钟上升沿有效。

Key3作为模式选择信号,mode0表示系统进入分设置模块,mode1表示系统进入秒设置模块,mode2表示系统设置时间完成,进入烹调状态。

key2的作用是在mode0及mode1模式下对分、秒设置进行加操作,按一下分、秒加1。

key1的作用是在mode0及mode1模式下对分、秒设置进行减操作,按一下分、秒信号减1。

key0作为系统的复位信号,在不同模式下按下key0系统都会进入复位状态,数码管显示”0000”,cook标志的LED灯处于灭状态。

微波炉可编程逻辑控制系统设计

微波炉可编程逻辑控制系统设计微波炉可编程逻辑控制系统设计随着人们生活水平的提高,微波炉已经成为广大家庭不可或缺的电器,相信大家对微波炉已经非常熟悉了。

它能够以独特的方式加热食物,既快捷又方便。

但是,目前市场上的微波炉普遍存在着定时不准确、温度控制不稳定、操作复杂等问题,给用户的使用带来了不便。

为此,设计一种微波炉可编程逻辑控制系统,是非常有必要的。

需求分析:我们的系统需要满足以下几个主要功能:1.定时功能:以最短的时间精确地加热食物,避免加热过头。

2.温度控制:通过精确测量微波的温度,避免加热不均匀。

3.操作简单:用户操作界面应该简单直观,方便不同用户的使用。

基于以上需求分析,我们可以开始系统的设计。

硬件方案1.温度传感器:我们需要一种能够准确测量微波温度的传感器,在市面上有很多种温度传感器,常用的有热电偶、热敏电阻、热电阻等。

我们考虑使用一种精度高、反应速度快、稳定性好的热敏电阻。

2.触控屏:使用触控屏可以简化用户的操作,让用户界面更加直观,可触控的屏幕也可以避免误操作和按键损坏等问题。

3.微波开关:微波加热的过程中,需要让微波源开关控制微波闸门的开关,以达到加热的目的。

4.微波管:微波的加热核心是微波管。

我们需要选购高品质的微波管,以确保加热效果稳定并且寿命长。

5.逻辑控制板:所有硬件的控制需要一个逻辑控制板来负责。

我们可以使用单片机或者嵌入式芯片。

软件方案1.程序设计:我们需要编写运行在逻辑控制板上的程序。

程序需要实现用户控制界面、温度传感器数据采集、微波开关控制等功能。

程序同时需要确保稳定高效,以此保证系统的性能。

2.内存管理:部分程序需要保存在逻辑控制板的内存中,因此我们需要实现程序的内存管理。

其中,存储程序的部分,需要保证读写速度快、容量足够。

3.硬件驱动:逻辑控制板需要控制各种硬件,如温度传感器、微波管等。

因此,我们需要考虑如何写好各种硬件的驱动程序以及如何控制硬件的状态。

总结本文介绍了微波炉可编程逻辑控制系统的设计方案,包括硬件方案和软件方案。

基于某FPGA技术地微波炉控制器

**大学**学院现代电子系统设计**系(院)**专业题目:基于FPGA技术的微波炉控制器学生姓名:班级:学号:指导教师:完成日期:年月摘要本文介绍了应用FPGA芯片和硬件描述语言(VHDL)设计微波炉控制器系统的方法。

系统使用VHDL编程实现各底层模块的功能,顶层的设计采用图形输入完成。

本文主要阐述模块化设计的思想和状态图的描述方法,以及它们在硬件描述语言中的应用,并展示了其在QuartusⅡ开发系统下的仿真结果和烧写到EPM570T100C5后的现象。

主要有以下几个模块:状态控制器KZQ、数据装载器ZZQ、烹调计时器JSQ、显示译码器YMQ47以及分频器和动态显示电路。

该控制器具有系统复位、状态控制、时间设定、烹饪计时、动态显示译码等功能。

关键字:FPGA;VHDL;微波炉;控制器;状态图;定时器目录1.绪论 (1)1.1任务的提出 (1)1.2设计的基本要求 (1)1.3设计的目的和意义 (1)2.系统总体设计 (2)2.1系统总体方案设计 (2)2.2系统功能模块描述(具体的电路图和VHDL设计文件将在附件中给出)23.系统详细设计 (2)3.1 状态控制器KZQ的设计 (2)3.2 数据装载器ZZQ的设计 (5)3.3 烹调计时器JSQ的设计 (5)3.4 显示译码器YMQ47的设计 (5)4系统仿真 (6)4.1状态转换控制器KZQ仿真图 (6)4.2数据装载器ZZQ仿真图 (6)4.3计时器JSQ仿真 (7)4.4显示译码器YMQ47仿真图 (8)5.设计总结 (8)6.参考文献 (8)7.附件 (9)7.1整体的原理图 (9)7.2各个基本模块的VHDL语言 (9)7.2.1分频器 (9)7.2.2控制器KZQ (10)7.2.3装载器ZZQ (11)7.2.4计时器JSQ,和其中需用到的DCNT6和DCNT10 (12)7.2.5译码器YMQ47 (15)7.2.6动态显示电路需要用到的DCNT4和decoder (15)1.绪论随着人民生活水平的提高,微波炉开始进入越来越多的家庭,它给人们的生活带来了极大的方便。

基于FPGA的微波炉定时系统设计

基于FPGA的微波炉定时系统设计作者:梁丽来源:《中国教育技术装备》2016年第20期摘要介绍基于FPGA的微波炉定时系统的设计思想、开发过程和仿真结果。

用EDA技术设计电子系统,具有设计效率高、修改快捷、易于升级和性能稳定等一系列优点。

关键字 FPGA;EDA技术;微波炉;定时系统中图分类号:G642 文献标识码:B文章编号:1671-489X(2016)20-0047-031 前言以EDA工具为开发环境,以硬件描述语言VHDL为编程语言,以可编程逻辑器件FPGA 为设计载体,采用EDA技术自顶向下的电子系统设计,改进传统的电子系统设计观念。

这种方法从系统级设计入手,在顶层、方框图级、功能级、门级等分别进行系统描述、功能设计、逻辑设计、电路设计等,由于设计的主要仿真和调试过程是在高层次上完成的,极大地提高了电子系统的设计效率、可靠性和灵活性。

下面以微波炉定时系统的设计为例,介绍在MAX+PLUSⅡ软件环境下进行设计、测试,基于FPGA芯片进行硬件实现的设计过程。

2 设计要求设计一种基于FPGA的微波炉定时系统。

要求:系统通电后处于复位状态。

首先,系统读入烹调时间,并显示在数码管上;然后按START键,系统进入烹调状态,剩余烹调时间在数码管上实时刷新;烹调结束后,数码管显示烹调结束信息,系统回到复位状态。

在烹调过程中,按PAUSE键或RESET键,可使系统暂停工作或使系统回到复位状态;在复位状态下,按TEST键可测试数码管工作是否正常[1]。

3 总体设计方案从系统设计要求出发,自顶向下地将设计细化,使功能具体化、模块化。

微波炉定时系统由状态控制器、数据装载器、烹调计时器和动态显示电路等模块构成。

将各模块连接起来,用图形输入法形成顶层模块,微波炉定时系统顶层模块连接如图1所示。

4 设计实现首先进行系统设计,划分各个功能模块,然后借助于EDA工具进行具体的模块设计。

采用VHDL语言对各模块进行编程,在MAX+PLUSⅡ环境下对各程序进行编译和仿真验证,创建各模块的器件符号,待建立整体系统顶层文件时调用。

基于FPGA的微波炉控制器设计开题

1选题的目的和意义1.1选题的背景随着生活水平的不断提高, 人们对家用电器的功能和质量的要求越来越高。

而现有市售的微波炉其主要弊端为: 不能按既有程序进行烹调, 需要使用者根据食物的类型、数量、温度等因素去设定微波炉的工作时间, 若设定的工作时间过长, 含水分较多的食物可能会产生过热碳化的现象, 若时间过短则达不到预期的烹调效果。

不仅在节能方面未做过多考虑,使用者还需要经常翻看使用说明书才能完成操作过程。

针对这些问题, 笔者认为有必要研制一种操作简单且烹调效果好的微波炉,根据一些家常菜按固定程序烹调的现象,可采取分时、分档火力加热,节时又节能。

1.2设计的目的和意义目前大部分微波炉控制器采用单片机进行设计,电路比较复杂,性能不够灵活。

本设计采用先进的EDA 技术,利用VHDL 设计语言,设计一种新型的微波炉控制器,该控制器具有系统复位、状态控制、时间设定、火力档位、烹饪计时、温度控制、显示译码和音响效应等功能,基于FPGA 芯片实现。

1.3选题的技术现状应用FPGA 芯片和硬件描述语言(VHDL)设计该微波炉控制器系统,该系统用VHDL 编程实现各底层模块的功能,顶层设计用图形输入完成。

设计依据如下:1)技术可行性:采用EDA作为开发方法,VHDL语言为开发工具,通过设计和实验,对开发的程序进行调试运行和波形仿真测试验证,实现设计目标;2)经济可行性:合理利用实验室已有软件、实验箱、开发板,对该微波炉控制器设计进行开发、调试运行、仿真测试,以及结果验证等;3)以现有网络资源为依据,以辅导老师的指导为参考,根据已学知识,综合该控制器设计要求,具体细化设计;2题目的主要内容本设计是基于FPGA的微波炉控制器设计。

2.1设计的总体结构描述该微波炉控制器系统可由以下几个模块组成:(1)状态控制器KZQ;(2)数据装载器ZZQ;(3)烹调计时器JSQ;(4)温度控制器KTQ;(5)显示译码器YMQ;(6)音响效应控制ALARM;系统功能模块如下:图2.1 系统功能模块图系统各模块之间的关系示意图如下所示:图2.2 模块关系图2.1.1设计的各个功能模块描述(1)状态控制器KZQ的功能是控制微波炉工作过程中的状态转换,并发出有关控制信息。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的微波炉定时系统设计

发表时间:2018-10-26T10:19:02.383Z 来源:《建筑学研究前沿》2018年第15期作者:朱太梅

[导读] 以EDA工具为开发环境,以硬件描述语言VHDL为编程语言,以可编程逻辑器件FPGA为设计载体。

广东美的厨房电器制造有限公司

摘要:本文介绍了应用FPGA芯片和硬件描述语言(VHDL)设计微波炉控制器系统的方法。

系统使用VHDL编程实现各底层模块的功能,顶层的设计采用图形输入完成。

关键词:FPGA;微波炉;定时系统;设计

引言

以EDA工具为开发环境,以硬件描述语言VHDL为编程语言,以可编程逻辑器件FPGA为设计载体,采用EDA技术自顶向下的电子系统设计,改进传统的电子系统设计观念。

1、微波炉控制器系统

微波炉控制器系统是一个实用型的系统系统,它不仅操作简单,而且烹调效果好,可以按固定程序加热一些家常菜,加热系统采取分时分火力加热,系统有以下几个模块:显示模块、输入模块、按键扫描和键盘译码控制模块,同时还包括状态转换控制数据装载烹饪计时温度控制及音效提示等显示模块,涉及到显示译码和指示灯的闪烁时,要经过需求分析设计并利用FPGA实现相应的功能,同时经过波形仿真调试验证设计方案,还要对方案的可行性进行有效的实现。

2、微波炉定时器工作流程

微波炉定时器和功率调节器结构和原理普通微波炉一般都采用定时器和功率调节(控制)器由同一电机驱动的组合体形式,简称定时功调器。

定时器主要由微型同步电机、降速齿轮组件和定时联动开关等组成。

由于其有联动开关串接在微波炉电源电路中,因此定时器大都兼作电源启动开关,当然另设启动开关的微波炉除外。

当操作人员拨动定时钮,设定定时时间时,定时开关被接通,微波炉得电而开始工作,同时定时器电机转动。

图1 微波炉定时器工作流程图

3、微波炉定时设计要求

设计一种基于FPGA的微波炉定时系统。

要求:系统通电后处于复位状态。

首先,系统读入烹调时间,并显示在数码管上;然后按START键,系统进入烹调状态,剩余烹调时间在数码管上实时刷新;烹调结束后,数码管显示烹调结束信息,系统回到复位状态。

在烹调过程中,按PAUSE键或RESET键,可使系统暂停工作或使系统回到复位状态;在复位状态下,按TEST键可测试数码管工作是否正常。

图2 微波炉定时系统顶层模块连接图

4、微波炉定时设计方案

从系统设计要求出发,自顶向下地将设计细化,使功能具体化、模块化。

微波炉定时系统由状态控制器、数据装载器、烹调计时器和动态显示电路等模块构成。

将各模块连接起来,用图形输入法形成顶层模块,微波炉定时系统顶层模块连接如图2所示。

5、微波炉定时系统设计实现

首先进行系统设计,划分各个功能模块,然后借助于EDA工具进行具体的模块设计。

采用VHDL语言对各模块进行编程,在

MAX+PLUSⅡ环境下对各程序进行编译和仿真验证,创建各模块的器件符号,待建立整体系统顶层文件时调用。

状态控制器状态控制器的功能是根据输入信号和微波炉所处的状态控制自身工作状态的转换,并输出相应的控制信号。

测试信号TEST=‘1’时,则LD_8888=‘1’,指示数据装载器装入用于测试的数据“8888”;置位端SET_T=‘1’时,则LD_CLK=‘1’,指示数据装载器装入设置的烹调时间数据;启动信号START=‘1’时,则COOK=‘1’,指示烹调正在进行之中,并提示计时器进行减计数;直到DONE=‘1’时,则LD_DONE=‘1’,指示数据装载器装入烹调完毕的状态信息“donE”,才使COOK=‘0’。

中间信号量CURR_STATE指示出状态控制器的5种状态,分别用0、1、2、3、4来代表。

数据装载器数据装载器的功能是在状态控制器输出信号的控制下选择定时时间、测试数据或烹调完成等信息的装载。

利用3个装载信号的组合LD_8888&LD_DONE&LD_CLK赋给变量TEMP,巧妙地解决装载数据的选择问题。

当LD_8888=‘1’时,输出测试数据,

DATA2=“8888”;当LD_CLK=‘1’时,输出设置的烹调时间数据,DATA2=“2453”;当LD_DONE=‘1’时,输出烹调完毕的状态信息数据,

DATA2=“ABCD”,将其转化为数码管显示,应为“donE”;当LOAD=‘1’时,表示烹调计时器正处于数据装入状态。

烹调计时器烹调计时器的功能是实现烹调过程中的时间递减计数,且当计时结束时向状态控制器提供状态信号,以便状态控制器产生烹调完成信号。

烹调计时器的内部组成原理是利用两个减法十进制和两个减法六进制计数器的级联,可实现59′59″数之间的计时和初始数据的装载。

LOAD=‘1’时完成装入功能,COOK=‘1’时执行逆计数功能,DATA3为来自于数据装载器的输出数据;MIN_H、MIN_L、SEC_H

和SEC_L为完成烹调所剩时间,PLUS和MINUS为控制MIN_L进行加‘1’和减‘1’的信号输入端;当数码管显示信息为DONE时,指示烹调完成。

动态显示电路动态显示电路的功能是以动态扫描的方式将各种显示信息显示在4个LED数码管上,4个数码管的8个数据端是分别并联的,由片选信号控制各数码管轮流显示。

该模块由片选、扫描、显示译码子模块整合实现。

结束语

综上所述,以VHDL硬件描述语言进行设计,将微波炉定时系统的核心部分集成在一片FPGA芯片内,可以通过软件编程的方法对其硬件结构和工作方式进行重构,使得硬件的设计可以如同软件设计那样方便快捷,为电子系统的设计带来极大的灵活性和通用性。

参考文献

[1]梁丽.基于FPGA的微波炉定时系统设计[J].中国教育技术装备,2016.

[2]肖银.基于WIFI技术的微波炉控制电路设计[D].电子科技大学,2016.

[3]韩团军.基于FPGA微波炉控制器设计[J].国外电子测量技术,2010.。