Global Bus Design of a Bus-Based COMA Multiprocessor DICE

BUS208-2.5.6-Globalization-and-The-Coca-Cola-Company-FINAL

Globalization and the Coca-Cola CompanyIntroductionToday, Coca-Cola is one of most well-known brands in the world. This company hascontinued to gain momentum and growth, capitalizing on the rapidly expandingbeverage industry and ranking as the largest beverage company in the world. With its push for global market share, Coca-Cola now operates in over 200 countries with over 84,000 suppliers. Currently, over 70% of Coca Co la’s business i ncome is generatedfrom non-US sources (Coca-Cola Company, 2012). In over a century, Coca-Cola hasgrown the company into a multi-million dollar business.However, the road to success has not always been easy for Coca-Cola. Many countries have banned the use of Coca-Cola products, claiming that these products are“threatening public health” and “encouraging obesity.” Many labor practice suits havebeen filed against the mega beverage company with accusations of “child laborsweatshops” and “discrimination in providing health care benefits to workers.” Inaddition, the beverage industry has been flooded with competitors introducing new soft drink products, such as Pepsi, along with soft drink alternatives, such as Gatorade,bottled water, fruit juice, and energy drinks. Coca-Cola has faced the challenge byintroducing new beverage brands including Sprite, Fanta, Minute Maid, Simply Orange, Fresca, Vitamin Water, Smart Water, Odwalla, and Powerade.In light of the obstacles Coca-Cola has overcome, the company has remained true to its commitment to provide quality, refreshing, and satisfying products to consumers. Inorder to ensure each product tastes the same across the globe, Coca-Cola continues to keep the beverage recipes secret with tightly controlled manufacturing facilities. Coca-Cola has never lost sight of its goal to be the best beverage company in the world. Now, let us take a closer look at Coca Cola’s journey to globalization.Coca-Cola’s Journey to GlobalizationFounded back in the 1880’s, Coca-Cola was developed by John Pemberton as anAmerican iconic brand known for high quality and consistency. During this period inhistory, storekeepers demanded pre-packaged products with brand name recognition.Coca-Cola met these demands with its iconic red and white logo and brand marketing to instill confidence in the consumer that the Coca-Cola product would taste the sameeverywhere it was purchased. These strategies soon became the foundation for Coca- Cola’s plan to e xpand globally.In the early 1900’s, C oca-Cola started to globalize. Bottling plants were initially built in Cuba and Panama as the US military spread to these regions, causing a rise in demand for the Coca-Cola brand. These plants proved to be successful, reducing shipping and delivery costs typical in these regions. Soon after, additional bottling plants opened inHawaii, Puerto Rico, and the Philippines. These efforts launched Coca-Cola’sSaylor URL: /bus208#2.5.6investment in testing foreign markets for future expansion opportunities. By 1926, Coca-Cola had established foreign relationships and plants around the world in support of its newly created center of global operations.Coca-Cola continued on its path of mass production and rapid expansion for the nextseveral decades. Local branches along with local partnerships to produce and distribute the signature Coca-Cola products were established throughout the world. The ending of World War II and the Cold War marked the signature period in which Coca-Cola hadestablished itself as a true global corporation known for its efficiency and worldwidecapabilities.Next, let us take a look at three key strategies employed by Coca-Cola to support rapid growth and expansion across the globe: global marketing strategies, productdifferentiation, and technology.Global Marketing StrategiesCoca-Cola’s marketing strategies played a significant role in success fully globalizing the company. The company’s popular advertising slogans and catchy jingles played into the hearts and minds of people around the world. Some of the most rememberedadvertising slogans include:∙“Drink Coca-Cola.”∙“Things go better with Coke.”∙“Good ‘til the last drop.”∙“It’s the real thing.”∙“Always Coca-Cola.”∙“Enjoy.”∙“Life tastes goo d.”Coupled with these slogans, songs were used to have consumers remember the brand.One of the company’s most popular jingles wa s known as “I want to buy the world acoke,” produced in 1971 by Billy Davis. The commercial featuring this song portrayed a world of hope and love produced by a group of multicultural teenagers on top of a hill.This commercial went down in history as one of the most well-known commercials of all time.In addition to Coca-Cola’s advertising efforts, Coca-Cola became the first commercial sponsor of the Olympic Games in Amsterdam in 1928. Coca-Cola continues to be anOlympic Games sponsor today. Coca-Cola has also sponsored many other sportingevents such as the International Federation of Association Football (FIFA), NationalHockey League (NHL), National Basketball Association (NBA), National FootballAssociation (NFL), Major League Baseball (MLB), NASCAR, and Cricket World Cup. Saylor URL: /bus208#2.5.6Product DifferentiationAnother key factor that has supported Coc a Cola’s globalization vision is the company’s ability to customize the product to meet the needs and wants of individual markets. For example, Coca-Cola has been able to tailor its product line to meet the needs of theyounger consumer by offering Powerade and flavored Coke products, such as Cherry Coke and Vanilla Coke. Additionally, the company is meeting the needs of the healthconscious, older consumer with Diet Coke, Vitamin Water, and Odwalla products. Coca-Cola has invested significant time and money into researching and understandingdifferent marketing segments based on lifestyle, age, and income in order to accurately develop and market its products.Packaging differentiation has also played a key role in how adaptable the Coca-Colaproduct is to various market segments. Functional packaging has been used to make the products available in different sizes and forms, including glass and plastic bottles, aluminum cans, and fountain drink dispensers. The company considers various shapes and sizes of the bottles and cans to ensure easy stacking and vending machinedispensing. To promote the company’s commitment to environmental sustainability, all packaging materials are designed to be recyclable and labeled accordingly for easyconsumer identification.TechnologyTechnology advances contributed to Coca-Cola’s ability to globalize rapidly throughout the 20th century. Product transportation became more efficient and cost effective withthe development of bigger and faster semi-trucks, cargo ships, jet aircraft, and trains.Coca-Cola was able to manufacture and ship products quicker and farther to marketsegments that were unreachable before these transportation improvements. In addition, technology advances became the driving force behind the ease and speed at whichinformation was available. Distributors and warehouses were able to more accuratelytrack inventory levels and fill order shipments, resulting in lower overall operating costs.Computerization also led to slashed product costs and improved efficiencies.Computerized and automated manufacturing equipment increased the speed andvolume in which products were produced. These technological advances enabled Coca Cola to compete on a global scale, selling the well-known brand of products across the world at competitive prices.Summary:∙Coca-Cola is one of the most well-known brands in the world, operating in over 200 countries.∙While the global marketplace has presented numerous opportunities for Coca-Cola, the company has also encountered global attacks on the nutritional valueof its products, along with unfair labor practice accusations.Saylor URL: /bus208#2.5.6∙Founded in 1880, Coca-Co la began its journey toward becoming the world’s best and largest beverage company.∙Coca-Cola’s American iconic logo, brand recognition, convenient packaging, and consistent product manufacturing became the foundation for the company’s planto expand globally.∙ A pioneer in globalization, Coca-Cola began expanding bottling andmanufacturing facilities back in the early 1900’s, establishing key foreignpartnerships.∙Coca-Cola’s marketing strategies, including memorable advertising slogans, catchy jingles, and sporting event sponsorships, played a significant role inwinning the hearts and minds of consumers globally.∙Product differentiation, such as offering different beverages in flexible packaging options, allowed Coca-Cola to customize the product for different marketsegments.∙Technology advances, including product transportation, telecommunication, and computerization, became the driving force behind Coca-Cola’s ability to capitalizeon the rapidly expanding marketplace across the globe.References:Coca-Cola Company (2012). Wikinvest. Retrieved December 11, 2012./stock/Coca-Cola_Company_(KO)Saylor URL: /bus208#2.5.6。

16节点COMA型

十六节点的阶层构造COMA 协议设计计算机应用技术COMA 简介【1】:COMA 是并行机结构体系中的一种,它的全称是Cache Only Memory Architecture ,它是NUMA 模型的一种特例,它利用各节点的高速缓存构成全局地址空间。

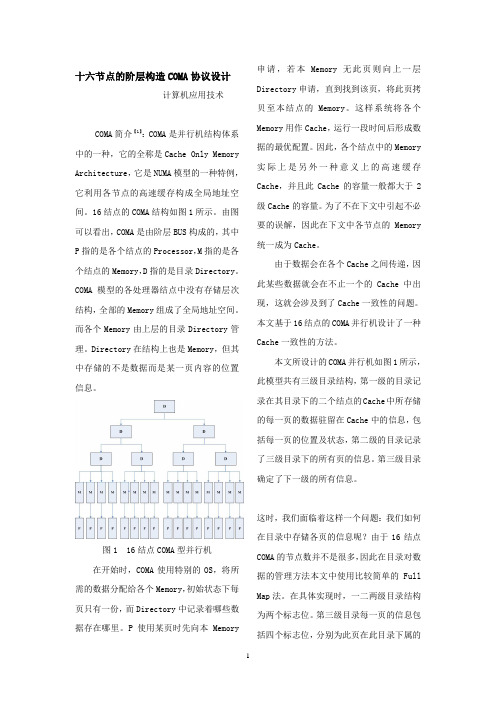

16结点的COMA 结构如图1所示。

由图可以看出,COMA 是由阶层BUS 构成的,其中P 指的是各个结点的Processor ,M 指的是各个结点的Memory ,D 指的是目录Directory 。

COMA 模型的各处理器结点中没有存储层次结构,全部的Memory 组成了全局地址空间。

而各个Memory 由上层的目录Directory 管理。

Directory 在结构上也是Memory ,但其中存储的不是数据而是某一页内容的位置信息。

图1 16结点COMA 型并行机 在开始时,COMA 使用特别的OS ,将所需的数据分配给各个Memory ,初始状态下每页只有一份,而Directory 中记录着哪些数据存在哪里。

P 使用某页时先向本Memory申请,若本Memory 无此页则向上一层Directory 申请,直到找到该页,将此页拷贝至本结点的Memory 。

这样系统将各个Memory 用作Cache ,运行一段时间后形成数据的最优配置。

因此,各个结点中的Memory 实际上是另外一种意义上的高速缓存Cache ,并且此Cache 的容量一般都大于2级Cache 的容量。

为了不在下文中引起不必要的误解,因此在下文中各节点的Memory 统一成为Cache 。

由于数据会在各个Cache 之间传递,因此某些数据就会在不止一个的Cache 中出现,这就会涉及到了Cache 一致性的问题。

本文基于16结点的COMA 并行机设计了一种Cache 一致性的方法。

本文所设计的COMA 并行机如图1所示,此模型共有三级目录结构,第一级的目录记录在其目录下的二个结点的Cache 中所存储的每一页的数据驻留在Cache 中的信息,包括每一页的位置及状态,第二级的目录记录了三级目录下的所有页的信息。

跨座式单轨交通高架换乘车站方案设计

收稿日期:20201215基金项目:中铁工程设计咨询集团有限公司科技开发课题(单轨-研2020-3-11)㊂作者简介:岳文豪(1991 ),男,2014年毕业于英国曼彻斯特大学建筑与城市化专业,文学硕士,工程师㊂文章编号:16727479(2021)03012806跨座式单轨交通高架换乘车站方案设计岳文豪(中铁工程设计咨询集团有限公司,北京㊀100055)㊀㊀摘㊀要:跨座式单轨是一种以高架敷设为主的中运量轨道交通制式,其换乘车站多采用高架形式设置在公共空间之中,对城市景观影响较大㊂为优化跨座式高架换乘车站的功能流线布置,减小车站体量,实现标准化㊁轻量化设计目标,从跨座式单轨制式独有的灵活度高㊁适应性强的特点出发,采用总结归纳法和案例分析法进行深入研究㊂首先,对跨座式高架换乘车站设计的影响因素进行分析,并对常用的高架车站换乘方式进行归纳;再结合近期项目实例,对同车站换乘车站及通道换乘车站的方案演变㊁优劣比选㊁适用范围进行研究,并对跨座式高架换乘车站的设计原则进行总结归纳㊂在统一设计原则的指导下,通过合理的车站站型选取以及因地制宜的周边分析,最大程度地实现了跨座式高架换乘车站的设计目标㊂关键词:跨座式单轨;高架换乘车站;同车站换乘;通道式换乘;方案研究中图分类号:TU248.1;U232㊀㊀文献标识码:ADOI:10.19630/ki.tdkc.202012150001开放科学(资源服务)标识码(OSID):Design of Elevated Transfer Station of Straddle MonorailYue Wenhao(China Railway Engineering Design and Consulting Group Co.,Ltd.,Beijing 100055,China)Abstract :The straddle monorail system is a medium volume rail transit system which mainly laid overhead.Its transfer stations are mostly set in the urban public space with an elevated mode,which has a great impact on the urban landscape.In order to optimize functional streamline,reduce station volume and achieve standardization and lightweight,the method of summary induction and case analysis were adopted based on thecharacteristics of straddle monorail system including high flexibility and strong adaptability.Firstly,theinfluence factors of straddle elevated transfer station were analyzed,and the commonly used transfer methods were summarized.Moreover,combined with project cases,the evolution,quality comparison,scopeapplication of the one-station transfer mode and channel transfer mode were studied,and the design principles of straddle elevated transfer station were summarized.Under the guidance of unified design principle,thedesign goal of straddle elevated transfer station can be achieved to the greatest extent through reasonableselection of station type and peripheral analysis according to local conditions.Key words :straddle monorail;elevated transfer station;one-station transfer;channel transfer;schematicdesign㊀1㊀研究背景及方法1.1㊀研究背景及意义换乘车站作为轨道交通线网各条线路的交汇节点,是轨道交通系统的重要组成部分㊂随着城市轨道交通的逐步发展,换乘站发挥的中转换乘作用愈发重要,目前各大轨道交通成网的城市,换乘站客流占全网的50%以上[1]㊂换乘车站往往位于城市重要节点位置,周边环境复杂,人流量大,控制因素多㊂尤其对于高架设置的换乘车站,其庞大的建筑体量会对城市空间和道路景观造成较大影响㊂如何在满足车站日常使用功能的同时,体现人性化设计理念[2],提升旅客换乘体验,并优化车站景观效果,是高架换乘车站设计中需要解决的主要矛盾㊂目前,关于轨道交通换乘车站的研究成果主要集中在传统钢轮钢轨制式领域,张丙昌对地下车站之间的换乘方案进行研究[3];陈小飞探讨了高架车站与地下车站之间的换乘关系[4];罗景华对高架车站与周边的建筑和环境的有效融合进行研究[5],刘宝对岛式与侧式车站换乘设计进行探讨[6]㊂然而,对于高架式换乘车站设计方案的系统性研究相对较少,亟待进行系统性总结㊂1.2㊀研究方法及目标在既有研究成果的基础上,从跨座式单轨制式的独有特点出发,结合近期的众多设计实践,以总结归纳和案例分析作为主要研究方法,对换乘车站的设置原则㊁制约因素㊁换乘方案㊁车站布局进行系统性研究,并对车站与城市空间的结合方式进行探索,以期达到跨座式换乘车站使用功能便捷化㊁车站体量轻量化㊁周边结合紧密化的设计目标[7-10]㊂2㊀高架换乘车站影响因素分析高架换乘车站设置于地面以上城市空间之中,其影响因素也有别于传统制式地下换乘车站,主要体现在如下几个方面㊂2.1㊀线位方案在工程设计中,轨道线路和换乘车站为 线 和点 的关系㊂根据线路交汇方案不同,车站可分为平行式和垂直式两种,具体布置形式如图1㊁图2所示㊂图1㊀双线平行式布置㊀图2㊀双线垂直式布置㊀当两线平行敷设时,两车站可在相同高度贴临或结合一体;当两线呈垂直交叉时,若线路存在高度跨越关系,两车站可分别独立设置于路口一侧,再通过换乘通道㊁连桥等形式连接㊂2.2㊀建设时序轨道交通工程建设投资大㊁周期长,普遍存在规划㊁建设分期实施的情况㊂对于建设时序不同的项目,应采取不同设计策略㊂同期建设的换乘车站,应优先考虑双线车站的一体化设计实施,从而最大程度方便旅客乘降及换乘㊂对于不能同期实施的换乘车站,在考虑换乘便捷性的基础上,需要结合分期建设的建设时序㊁投资分匹㊁接口预留等因素综合考虑,因地制宜地选择换乘方案㊂2.3㊀客流组织换乘车站多位于城市重要节点,周边客流规模较大,容易造成拥堵㊂在车站内,对旅客通行影响较大的站台宽度㊁换乘通道宽度㊁进出站闸机数量㊁扶梯数量等指标,应按照远期高峰小时最大客流量进行测算,以满足旅客使用需求㊂换乘车站内部各类人群相互汇集,在设计中应充分考虑不同类型人流走行路线的独立性,确保进出站流线,换乘流线,商业开发㊁工作人员流线均相互独立,以减少干扰㊂2.4㊀周边环境及规划换乘车站多数设置在城市核心区域,此类车站周边环境复杂,建筑密集,人流量大㊂车站设置应符合城市规划对周边地块的相关上位条件及指标,并满足车站与周边建筑的消防㊁节能㊁日照等相关距离要求㊂换乘车站设站方案应与市政道路和周边环境统一考虑,并着重考虑车站及天桥与人行道㊁车行道㊁周边建构筑物的相对关系,出入口应尽量靠近周边主要客流集散点,以减少旅客进出站走行距离㊂条件允许时,车站主体及出入口应与周边地块综合开发有机结合,为旅客带来便捷乘降体验,以及为周边区域注入活力㊂3㊀高架换乘车站的设计分类结合上文所述,高架换乘车站的受控因素存在多样性㊂在设计过程中,对于不同的及边界条件,也应采取相应的换乘方案设计策略[11-13]㊂根据划分标准不同,高架换乘车站的换乘方案主要分为如下几类㊂3.1㊀按照换乘部位分类按换乘部位分类,换乘方案分为非付费区换乘和付费区换乘两种㊂非付费区换乘多用于不同制式及票制的轨道交通之间换乘,在同制式轨道交通中,多采用付费区换乘的形式㊂付费区换乘又细分为站台换乘㊁站厅换乘和通道换乘㊂站台换乘最为便捷,站厅换乘次之,在两线同期实施并满足其他外部条件的情况下,应优先考虑站台㊁站厅相结合的换乘方式㊂通道式换乘设置灵活,适用于两线车站站位距离较远或分期建设的情况,当采用通道换乘时,应合理布置换乘线路,避免流线过长引起旅客通行不便㊂3.2㊀按照车站类型分类根据车站相对关系不同,高架换乘可分为同车站换乘和通道式换乘两大类㊂根据线路高差关系㊁换乘方式㊁车站布置的差异,又可细分为如图3所示多种类型㊂图3㊀换乘车站站型分类4㊀同车站换乘方案比选在两线同步实施,且周边环境及线路走向条件允许的情况下,应优先考虑双线并站的同车站换乘方案㊂车站合二为一能够最大程度方便乘客换乘,便于日常运营维护管理[14-15]㊂根据线路关系不同,该类车站又细分为一岛两侧车站㊁双岛车站和叠岛车站3种㊂4.1㊀一岛两侧车站当两条线路在同一高程,平行且不交叉敷设时,可采用一岛两侧车站形式㊂该站型设置1座岛式站台和2座侧式站台,站台下方设置共用站厅层㊂该站型换乘部位属于站厅与站台结合式,其中一个方向可实现同站台换乘,其他方向需通过站厅层进行换乘,剖面布置如图4所示㊂该站型多见于传统钢轮钢轨制式换乘车站设计中㊂主要优点为换乘流线较短,站厅集中设置,便于换乘㊁乘降和运营管理㊂车站两侧区间线路平顺无交叉,墩柱布置较为规整,景观效果较好,车站及两侧区间布置如图5所示㊂该方案不足之处在于车站宽度较大,需占用较多道路及路侧空间,且需根据市政道路宽度及线路敷设位置综合确定车站布局和柱位布置㊂图4㊀一岛两侧车站剖面示意㊀图5㊀一岛两侧车站鸟瞰示意㊀4.2㊀双岛车站当两条线路在同一高程,平行且局部交叉敷设时,可采用双岛车站形式㊂该站型同高程设置2座岛式站台,站台下设置共用站厅层㊂该站型换乘部位属于站厅与站台结合式,其中2个方向可实现同站台换乘,其他方向需通过站厅层进行换乘,剖面布置如图6所示㊂图6㊀双岛车站剖面示意㊀该站型换乘流线最短,乘客换乘与乘降最为便捷㊂然而,车站两侧区间线路存在交叉跨越,墩柱布置不规则,景观效果不佳;车站宽度相对较大且需占用较多道路及路侧空间(见图7)㊂4.3㊀叠岛车站当道路宽度条件受限时,可充分利用跨座式单轨爬坡性能优良的特点,将两条线路在不同高程敷设,此图7㊀双岛车站鸟瞰㊀时换乘车站采用叠岛车站形式㊂该站型上下设置2座岛式站台,站台下设置共用站厅层㊂该站型换乘部位属于站厅与站台结合式,其中2个方向可实现同站台换乘,其他方向需楼扶梯及站厅层进行换乘,其剖面布置如图8所示㊂图8㊀叠岛车站剖面示意㊀该站型能够有效减少车站宽度,占地面积较小,且换乘流线较短便于旅客乘降及换乘㊂然而由于站台上下布置,换乘流线与进出站流线相互交叉,容易造成楼扶梯处人流拥堵;且车站两侧区间在两个不同高程敷设,墩柱设置复杂,实施难度大,车站及区间效果如图9所示㊂图9㊀叠岛车站鸟瞰㊀5㊀通道式换乘车站方案比选虽然同车站换乘方案有诸多优点,但其受到外部条件制约因素较多,存在车站体量大,用地要求高㊁车站需同期实施等问题㊂当要求无法满足时,应考虑选择通道式换乘车站方案㊂通道式换乘车站的优点是两换乘车站相互独立,互不干扰,车站通过付费区换乘天桥进行连接,从而实现换乘功能㊂在建设过程中,可先期实施近期车站,并预留换乘通道接入条件,可有效减少工程投资和建设规模㊂根据线路关系不同,通道换乘车站分为双线平行通道换乘和双线垂直通道换乘两种类型,具体站型分类如下㊂5.1㊀双线平行式通道换乘双线平行式通道换乘车站主要适用于两条线路平行敷设的情况,根据两车站相对位置关系的差异,又分平行交错式通道换乘和平行并列式通道换乘㊂(1)平行交错式通道换乘车站该站型双线车站交错布置,通过端部换乘通道连接两车站付费区,从而实现站厅层换乘㊂平行交错式通道换乘车站常用于线路平行设置且道路条件较为狭窄的情况,可最大程度减少换乘站所占用的用地宽度㊂图10为淮南轨道交通淮南站,为1号线/4号线换乘站㊂该站所在位置市政道路狭窄,红线宽度仅35m,周边建筑拆迁困难㊂为最大程度压缩所占道路宽度,车站采用平行交错式通道换乘方案,在两站站厅层端部的付费区通过换乘通道相互连接,从而实现换乘功能,换乘距离仅为15m,平面布置如图11所示㊂图10㊀平行交错式通道换乘车站鸟瞰㊀图11㊀平行交错式通道换乘车站平面示意㊀(2)平行并列式通道换乘车站平行并列式通道换乘车站常用于线路平行设置且两线间距较大的情况㊂该站型两线车站并列布置,通过换乘通道将两车站站厅层付费区相连,从而实现站厅换乘㊂此种布置方式在保证两车站的相互独立性同时,又将换乘距离压缩至较短的范围内,如图12㊁图13所示㊂图12㊀平行并列式通道换乘车站鸟瞰㊀图13㊀平行并列式通道换乘车站平面示意5.2㊀双线垂直式通道换乘当线路交叉布置时,可采用双线垂直式通道换乘㊂为满足线路互相跨越时的高差要求,需将2个车站的轨道梁和站台设置在不同的高度上,根据车站相对位置及轨道梁高度不同,可细分为三㊁四层车站通道换乘;站厅站台上下交错式通道换乘;二㊁三层车站通道换乘等三种形式㊂(1)路中三㊁四层车站通道换乘跨座式单轨路中高架车站一般为三层布局,即架空层㊁站厅层及站台层,当两线路交叉时,可通过增加换乘层的方法抬升其中一座车站,从而满足线路的高差要求,形成三㊁四层车站通道换乘㊂以淮南轨道交通洞山路换乘站为例,2号线车站为路中高架三层站,由下至上为架空层㊁站厅层㊁站台层,1号线车站为路中高架四层站,由下至上分别为架空层㊁换乘层㊁站厅层㊁站台层㊂付费区换乘通道连接1号线换乘层和2号线站厅层,1号线换乘乘客需经站台下至换乘层后再经由换乘通道行至2号线站厅层,如图14㊁图15所示㊂图14㊀路中三㊁四层站通道换乘方案剖面㊀图15㊀三㊁四层站通道换乘方案㊀此换乘方案的换乘通道可实现无高差设置,换乘相对便捷,然而,换乘层的设置会导致车站体量增大,高度提高,投资也相应增加㊂(2)路中厅台交错式车站通道换乘当换乘车站设置在路中时,为避免车站高度过高,也可通过站厅层与站台层倒置的方法来满足线路高差要求,即站厅站台上下交错式通道换乘㊂仍以洞山路换乘站为例,1号线/2号线洞山路站均为路中高架三层车站,其中,1号线车站站厅层位于二层,站台层位于三层;2号线车站站台层位于二层,站厅层位于三层㊂两车站站厅层通过付费区换乘通道连接,通道高差为7m,具体布置如图16所示㊂图16㊀站厅站台上下交错式通道换乘方案剖面㊀该换乘方案两个车站建筑体量与标准站一致,建筑高度统一㊂但2号线车站站厅站台倒置,容易造成旅客流线迂回曲折,不利于日常使用及紧急疏散㊂且换乘通道存在高差需额外加设楼扶梯,会对乘客换乘带来不便㊂(3)二㊁三层车站通道换乘当通道换乘车站的其中一座有条件设置于路侧空地时,可采用二㊁三层通道换乘方案,并考虑与周边地块综合开发进行结合,在缩短换乘距离的同时为路侧地块引入活力㊂以德州轨道交通恒大站为例,1号线为路中高架三层站,3号车站为路侧高架二层站㊂两车站站厅层通过付费区换乘通道相连,从而实现换乘,剖面布置如图17所示㊂其中3号线车站与地块内的商业综合体结合设计,并设置连桥相连接,从而最大程度地提升地块的经济价值,周边开发效果如图18所示㊂图17㊀二㊁三层车站通道换乘方案剖面图18㊀二㊁三层车站通道换乘方案鸟瞰㊀6㊀结论跨座式单轨具有爬坡能力强,转弯半径小,车站体量小等特点,故跨座式高架换乘车站布置方案相较于传统钢轮钢轨制式有更高的灵活性和适应性㊂当换乘车站并站统一设置时,可结合周边城市空间和道路条件,灵活地选择一岛两侧㊁双岛或叠岛换乘方案㊂当换乘车站分站设置或分期实施时,应综合考虑上文所述限制因素及工程实际条件,选择最匹配的通道换乘方案㊂在跨座式高架换乘车站深化设计过程中,应遵循如下原则㊂(1)车站方案设计应着重考虑缩短旅客换乘走行距离,减少换乘高差,条件允许时应优先采用同车站换乘方式㊂(2)换乘旅客流线应与进㊁出站旅客流线分开设置,避免相互交叉干扰㊂(3)车站需分期实施时,应在满足近期车站使用需求及远期加建可实施性的基础上,尽量缩小近期建设规模和投资㊂(4)车站方案设计应与周边规划㊁市政道路紧密结合,合理确定出入口及换乘通道的布置㊂(5)条件允许情况下,应优先考虑将换乘车站与周边综合开发结合设置,为周边城市空间注入活力㊂参考文献[1]㊀罗小峰.枢纽型高架车站设计方案研究[J].智能建筑与智慧城市,2020(1):68-70.[2]㊀李玉书,孙越,万衡,等.城市轨道交通车站换乘通道客流压力的评估方法[J].城市轨道交通研究,2020,23(1):106-109,144.[3]㊀张丙昌.地铁车站换乘形式的设计研究[J].建材与装饰,2019(2):247-248.[4]㊀陈小飞.谈换乘方式之高架站与地下站换乘[J].设备管理与维修,2019(3):119-120.[5]㊀罗景华.高架车站建筑设计思路的研究[J].建筑技术开发,2020,47(9):15-16.[6]㊀刘宝,张小燕.岛式与侧式车站换乘建筑设计探讨[J].低碳世界,2018(2):272-273.[7]㊀赵薇.城市密集区多线换乘车站设计探索 轨道交通16号线龙阳路站设计回顾[J].建材与装饰,2019(18):219-220.[8]㊀于海.城轨高架换乘站建筑防火设计实例研究 以上海罗山路站为例[J].中外建筑,2018(10):167-168.[9]㊀苏珊山.建筑学设计审美在城市高架轨道交通建设中的应用[J].浙江建筑,2018,35(8):12-16,34.[10]余群涛.对轨道交通路中高架车站方案布置形式探索[J].建筑技术开发,2018,45(8):63-64.[11]许乙弘,李晓况.地铁车站换乘空间体验优化设计研究[J].城市轨道交通研究,2018,21(7):10-14.[12]皮雁南,郭建媛,马骁,等.城市轨道交通换乘车站多方式客流控制模型[J].都市快轨交通,2020,33(3):72-76,84.[13]张浩,尤建新.基于数据包络分析和托宾模型的城市轨道交通运输效率[J].同济大学学报(自然科学版),2018,46(9):1306-1311.[14]沈晓阳.重庆市跨坐式单轨交通的建设和运营[J].城市轨道交通研究,2006(10):8-13.[15]杨宏伟.铁路客运枢纽站各种交通方式的衔接研究[D].北京:北京交通大学,2005.。

交通工程定制公交翻译修正版

Collaborative Research: Cyber-Enabled Demand-Interactive Transit (CREDIT) for SustainableTransportation合作研究:基于互联网的已知需求的可持续定制公交1 IntroductionThe auto-dependent surface transportation system in the U.S. has not only created chronic traffic congestion that costs over $ 100 billion per year [109], but also severely limited mobility options, especially for those who have no access to private autos. Such a system also exacerbates the environment impacts of travel. In the US, transportation consumes 27.8% ofall energy, of which 92.8% come from petroleum use; it also contributes 32.7% of greenhouse gas (GHG) emissions[47].在美国路面上对于汽车的过度依赖的交通系统不仅造成了每年耗费1000亿美元的交通拥挤,而且严重的限制了群众出行的选择,尤其是对于那些还没有私家车的群众。

这样的系统也恶化了交通的环境影响。

在美国,交通耗费了总能源的27.8%,其中92.8%来源于石油的使用,同时32.7%的温室气体的排放也由此产生。

Promoting transit, or public transportation, is widely regarded an important measure in the transition to be more efficient, equitable and sustainable transportation [121].振兴交通,或者公共交通,被广泛的视为是实现有效、平等和可持续交通的重要措施。

English_Version_of_A_History_of_Literature_in_the_

74 | China Book International"It has been three or four decades since I had the dream of compiling a history of literature from the Ming Dynasty at the age of 40." In 1999, Mr. Xu Shuofang (1923-- 2007), who was nearly eighty years old, recalled his memories like this in the preface to of Literature in the Ming Dynasty . Seven years later, History of Literature in the Ming Dynasty Mr. Xu and his student Sun Qiuke, was fi However, Mr. Xu had never expected that the writings condensing his lifelong efforts would remain popular today and be widely spread overseas.These days, the English version of A History of Literature in the Ming Dynasty was jointly published by Zhejiang University Press and Springer Nature Group and released to the world on the Springer Link platform. The export of this book also means that more overseas readers will be introduced to the literature of Ming Dynasty China.Xu Shuofang, a scholar of ancient Chinese literature and senior professor at the School of Humanities, Zhejiang UniversityThe English Version of A History of Literature in the Ming Dynasty A “Window”Zhejiang is a window that shows us China and Chinese characteristics. With its rich cultural heritage and time-honored history, Zhejiang acts as an important platform for international academic and cultural exchanges. The Implementation Plan of Zhejiang's High-qualityLatest English version of A History of Literature in the Ming DynastyCopyright ©博看网News Reportsabout Publishinghistory more deeply in more aspects.It is reported that A History of Literature in the Ming Dynasty is one of the works published by Zhejiang University in response to the "Academic Classics Going Abroad" program within the Chinese-English translation project and one of the outcomes in its first phase.The "Academic Classics Going Abroad" program, launched in 2019, was set up by Zhejiang Universityto promote the research results of humanities and social sciences of the university to the world. It aims to publish a number of academic classics that can represent Chinese academic standards, reflect the essence of Chinese culture, and show Chinese academic frontiers. This program falls into the Chinese-English translation program for Chinese academic classics and the funding program for English academic publications.At present, 16 kinds of works on the research of humanities and social sciences authored by well-known scholars at Zhejiang University have been selected by the Chinese-English translation program. Besides A History of Literature in the Ming Dynasty (English version), General Theory of Dunhuang Studies (English version) and General Theory of Ancient Chinese (English version) will soon be released. In the next three years, sixteen categories of books will be translated and published under this program.Translation of Classical Literary WorksA "Barrier"Translation comes across as a barrier when academic classics, especially literary works, are "going global".In translatology, there is a saying: There are always untranslatable things in literary works. That's because literature is the art of language, in which lie the individual wills of works and the differences in cultural context.Mo Yan, the famous Nobel Prize winner, said, "Translation is tougher than creation." It took him only 43 days to finish the first draft of Life and Death are Wearing Me Out, while it took Anna Gustafsson Chen, a Swedish sinologist, a good six years to translate this book.Then, what are the difficulties in translating Chinese classics? "It was difficult, at multiple levels," said Ma Li, the translator of A History of Literature in the Ming Dynasty and a professor at East China University of Political Science and Law, to the journalist on the phone. As a 30-year experienced translator, she was outspoken about the difficulties of translating A History of Literature in the Ming Dynasty.In this book, a study is made by three genres: novels, operas, and poems. It contains not only the author's views, but also citations of expressions in many literary works from the Ming Dynasty. In the translation process, all these contents need to be represented as "intact" as possible.There are many difficulties in this process. For example, it is difficult to find the corresponding pronunciationsin English for some onomatopoeia words in ancient Chinese poetry. As some dramas are uncommon, no one has translated them yet. The first translator is sureto face many challenges. In the translation of ancient Chinese works, compared with vernacular works, cultural differences should be considered. In addition, the "rhyme" unique in traditional Chinese culture should be conveyed to overseas readers as much as possible.In the translation process, Ma Li used to peruse the original work repeatedly, combining the author's pointof view, language features, and the differences between Chinese and foreign cultures. "There is neither shortcut nor end to translation," said Ma Li. She believed that good translation was cultivated day after day.The translation and publication of literary works carry the heavy responsibility of bringing Chinese culture abroad. For more overseas readers, the launch of the English version of A History of Literature in the Ming Dynasty means that the study of literature of the Ming Dynasty becomes more accessible. Ma Li is very proud of it. "It is much more difficult and rewarding than translating best sellers."Copyright©博看网. All Rights Reserved.76 | China Book International。

中考英语交通工具改进单选题50题

中考英语交通工具改进单选题50题1. We need to improve the ____ of our cars to reduce fuel consumption.A. speedB. performanceC. sizeD. color答案:B。

本题考查交通工具性能相关词汇。

选项A“speed”指速度;选项B“performance”有性能的意思,符合语境,强调汽车整体性能的提升以降低油耗;选项C“size”指尺寸;选项D“color”指颜色,均与降低油耗的性能改进无关。

2. The new technology can greatly enhance the ____ of the buses.A. safetyB. comfortC. beautyD. cost答案:A。

本题围绕交通工具性能改进。

选项A“safety”意为安全,新技术能提升公交车的安全性;选项B“comfort”指舒适;选项C“beauty”指美观;选项D“cost”指成本,而题干说的是新技术对公交车性能的提升,安全性能更符合。

3. To make the trains more efficient, we should focus on improving their ____.A. enginesC. seatsD. lights答案:A。

本题考查火车性能改进的重点。

选项A“engines”指引擎,改进引擎能使火车更高效;选项B“windows”指窗户;选项C“seats”指座位;选项D“lights”指灯光,这三个选项都不是影响火车效率的关键因素。

4. The improvement of the ____ can make the planes fly longer distances.A. wingsB. cabinsC. enginesD. pilots答案:C。

本题关于飞机性能改进。

选项A“wings”指机翼;选项B“cabin”指机舱;选项C“engines”指引擎,改进引擎能使飞机飞得更远;选项D“pilots”指飞行员,飞行员不是飞机能飞更远的直接改进因素。

综合英语PPT课件

Strategies • Comprehensive English Assessment and

Feedback

Introduction to

01 Comprehensive English

The Definition of Comprehensive English

要点三

Authentic Materials

Textbooks often include authentic materials, such as articles, dialogues, and readings, to provide students with exposure to natural language use in real world contexts

• Communicative teaching method: student-centered, emphasizing the practical use of language, emphasizing the practice of listening and speaking, and encouraging students to actively participate in classroom activities.

Learner centered

The current design is learner centered, focusing on the needs and interests of learners and providing opportunities for active participation and self directed learning

多网融合下的都市圈客运系统发展思路

规划思路多网融合下的都市圈客运系统发展思路周予婷$,戴新鎏2,孙洪涛3,马波涛((1中国铁路经济规划研究院有限公司研究实习员,北京100038;2中国铁路经济规划研究院有限公司处长、研究员,北京100038;3中国铁路经济规划研究院有限公司副研究员,北京100038;4中国铁路经济规划研究院有限公司研究员,北京100038)摘要:随着国家区域协调发展等重大战略的推进,以特大城市、大城市为核心的都市圈发展的新格局逐渐形成。

都市圈这一新的空间概念以及人民对美好出行的向往对交通基础设施的互联互通提出了新的要求,不同交通方式之间应进一步有效衔接,构建以四网融合轨道交通为主骨架,地面公交为补充,与民航、私家车、慢行交通充分衔接的多网融合都市圈客运系统,从而适应不同层次的旅客出行需求。

同时,也应注意在尚未成熟、客运需求小的中西部都市圈中把控都市圈客运基础设施的建设节奏。

文章介绍了多网融合下都市圈客运系统的发展背景,以日本东京都市圈为例介绍了成熟都市圈多网融合下的客运系统的结构特点和运营模式,明晰了都市圈客运系统的层次结构,提出了我国都市圈客运系统的发展思路。

关键词:多网融合;都市圈;客运系统;轨道交通文献标识码:A文章编号:1004-9746(2021)02-0042-05Development of Metropolitan Area Passenger Transportation System with Multi-network IntegrationZHOU Yuting1,DAI Xinliu2,SUN Hongtao3,MA Botao4(1China Railway Economic and Planning Research Institute Co.,Ltd.,Research Intern,Beijing100038,China;2China Railway Economic and Planning Research Institute Co.,Ltd.,Division Chief and Researcher,Beijing100038,China;3China Railway Economic and Planning Research Institute Co.,Ltd.,Associate Researcher,Beijing100038,China;4China Railway Economic and Planning Research Institute Co.,Ltd.,Researcher,Beijing100038,China)Abstract:With the conduction of major strategies such as Regional Coordinated Development,a new pattern of metropolitan area development centering on mega-cities has gradually formed.The new spatial concept of metropolitan area and the people's yearning for better travel have put forward new requirements for the interconnection of transportation infrastructure.Different transports should be further effectively connected.A multi-network integrated metropolitan area passenger transportation system with the four-network integrated rail transit as the main framework,supplemented with bus system,and fully connected with civil aviation,private cars,and non-motorized traffic should be constructed,so as to meet the demand of passengers at different levels.At the same time,attention should also be paid to controlling the pace of passenger transportation infrastructure construction in the central and western metropolitan areas that are not yet developed and with low traffic demand.This article introduces the background of the passenger transportation system in the metropolitan area under multi-network integration.Taking Tokyo as an example,it introduces the structural characteristics and operation mode of the passenger transportation system under the multi-network integration in the mature metropolitan area, clarifies the hierarchical structure of the metropolitan passenger transportation system,and finally puts forward the development method of the passenger transportation system in Chinese metropolitan area.Key words:multi-network integration;metropolitan area;passenger transportation system;rail transit1多网融合下的都市圈客运系统发展背景随着经济社会的快速发展,城市、城镇之间人口、商品、资源的流动进一步加强,逐步形成了一体化发展的新格局#以北京、上海、杭州等特大城市、大城市为核心的都市圈结构日渐成熟,这些都市圈中人们的出行需求越来越多元,尤其是都市圈内部通学、通勤、就医的短途出行需求快速攀升,在都市圈核心城市就业,周边节点城市居住的“双城生活”现象越来越多,传统的铁路、城轨、公交各自发展的国铁集团科研开发计划课题:"四网融合"背景下的市域(郊)铁路发展研究(J2020Z403)多网融合下的都市圈容运系统发展思路周予婷.戴新鎏.孙洪涛.马波涛格局已经不再能适应今后一体化发展趋势。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Global Bus Design ofa Bus-Based COMA Multiprocessor DICEGyungho Lee,Bland Quattlebaum,Sangyeun Cho ,and Larry KinneyDept.of Electrical EngineeringDept.of Computer Science University of Minnesota Minneapolis,MN 55455E-mail:ghlee@To appear in Proceedings of International Conference on Com-puter Design,Austin,Texas,October 1996.AbstractDICE is a shared-bus multiprocessor based on a dis-tributed shared-memory architecture,known as Cache-Only Memory Architecture (COMA).Unlike previous COMA pro-posals for large-scale multiprocessing,DICE utilizes the COMA to effectively decrease the gap between modern high-performance microprocessors and the bus.As micro-processors become faster and demand more bandwidth,the already limited scalability of a shared bus decreases even further.DICE tries to optimize the COMA for a shared-bus medium,in particular to reduce detrimental effects of the cache coherence and the “last memory block”problem on replacement.In this paper,we present a global bus design for a bus-based COMA multiprocessor using the IEEE Fu-turebus+standard backplane bus and the Texas Instruments chip-set.Our design demonstrates that necessary bus trans-actions for DICE can be done efficiently with existing stan-dard bus signals.Considering the benefits of the COMA and the little design complexity it adds to the conventional shared-bus multiprocessor design,a bus-based COMA mul-tiprocessor such as DICE can become a viable candidate for future shared-bus multiprocessor designs.1IntroductionShared-bus SMPs (Symmetric Multi-Processors)such as the Sequent Symmetry [14]or the SGI Challenge [3]rep-resent the mainstream of accepted and commercially vi-able computer systems.However,as microprocessors be-come faster and demand more bandwidth,the already lim-ited scalability of the shared bus decreases even further,andthe ill-effect of a cache miss penalty becomes even worse.Even with clustering of having several processors per a pro-cessor board,the effective machine size for shared-bus mul-tiprocessors is fairly limited.Further,a cache miss can cost up to a few hundred processor cycles for recent high-performance microprocessors.To bridge the gap between high-performance microprocessors and a backplane bus,it is important to reduce global bus traffic and to increase lo-cal memory utilization,together with efforts to develop a high-speed wide data-path backplane bus.The DICE (Direct Interconnection of Computing Ele-ments)project at the University of Minnesota utilizes the Cache-Only Memory Architecture (COMA)to bridge the gap.The COMA improves the utilization of local mem-ory by decoupling the address of a datum from its phys-ical location,allowing the data to move dynamically be-yond the level provided by traditional caches.This decou-pling is achieved by treating the memory local to each node,called attraction memory (AM),as a cache to the shared address space without providing traditional physical main memory [5].Unlike the previous examples of scalable COMA ma-chines,including the DDM of the Swedish Institute of Com-puter Science [5]and the KSR-1of the Kendall Square Re-search [23],DICE focuses on the efficient realization of the COMA as a shared-bus SMP with little provision for scal-ability for larger-scale multiprocessing.While we expect many problems associated with scalable COMA machines to become less serious with a shared-bus medium,shared-bus multiprocessors benefit from the COMA in three ways:(i)less bus contention due to lower global traffic;(ii)shorter average memory latency due to higher local memory utiliza-tion;and (iii)more processors in the machine due to less bandwidth requirement on the bus.This paper presents a global bus design of DICE.TheFigure1:A bus-based COMA multiprocessor main contribution of this paper is in demonstrating the feasi-bility of an efficient implementation of a bus-based COMA multiprocessor.Especially,we focus on how the imple-mentation handles the coherence enforcement and the re-placement problem,which can cause significant overheads in scalable COMA machines[7,9].Our design employs the IEEE Futurebus+standard backplane bus[22]and the Texas Instruments chip-set[21].The rest of this paper is organized in the following man-ner.Section2gives a brief background necessary for our discussions.Section3describes the coherence and replace-ment protocol of the DICE multiprocessor.A global bus implementation is given in Section4,and Section5will summarize the paper.2Background2.1Why bus-based COMA?Shared bus design has been popular in small-scale com-mercial SMPs.A commercial SMP typically runs a single instance of an operating system with a shared real address main memory,and supports hardware cache coherence con-trol.Among recent machines are the SGI Challenge[3]and the Sun Microsystems Ultra X000Servers[24].Although the shared-bus SMP is a widely accepted architecture,its scalability is severely hurt due to the limited bandwidth of the bus.As microprocessors become faster and demand more bandwidth,the shared bus becomes an even more se-rious bottleneck in such systems.If the last ten-year history is any indication for future,then one should expect that the bottleneck will become even worse.For example as noted in [6],with16processors,a block size of64Bytes,and a64-KB data cache,the total bandwidth demand for some par-allel benchmark programs ranges from almost500MB/sec (for Barnes in SPLASH-2[20])to over9400MB/sec(for Ocean),assuming a processor that issues a data referenceFigure2:Block diagram of a DICE nodeevery5ns.In comparison,the Gigaplane bus of the Ultra X000Servers,one of the highest bandwidth bus systems, provides2500MB of bandwidth[24].Handling the problem of the shared-bus bottleneck can be done in three complementary approaches.Firstly,a faster and wider bus needs to be developed.This can be achieved by developing low voltage-swing bus transceivers, high density packaging,effective grounding to reduce noise interference,and more effective line termination.Secondly, smart bus protocols such as more aggressive pipelining are needed.Thirdly,memory requests should be serviced lo-cally.This end can be met by having larger caches(of multi-level structure)or large shared caches together with“clus-tering”[16].Taking this to an extreme,a DSM(Distributed Shared Memory)architecture,especially the COMA,be-comes attractive.The COMA improves the utilization of local memory by decoupling the address of a datum from its physical loca-tion,allowing the data to move dynamically beyond the level provided by traditional caches.With dynamic repli-cation and migration of data through the AMs,a COMA machine seems to be able to provide higher utilization of local memory than is otherwise possible,which may result in low average memory access latency and low network traf-fic.As the processor technology is progressing much faster than the bus or interconnection network technology,this po-tential reduction in latency and bandwidth requirement can be a crucial advantage.2.2Bus-based COMA multiprocessorsFigure1shows a high-level structure of a bus-based COMA multiprocessor.A processor node(dashed box)is composed of a high-performance microprocessor,two lev-els of cache memory,and the local memory managed as the AM.The local memory tag,which includes‘state’informa-tion and uses fast SRAMs,is duplicated so that local tag access and global bus snooping will not conflict too often(b) 16-processorsADM ARC2D DYFESM FLO52Q MDG OCEAN QCD2TRACK TRFDADM ARC2D DYFESMFLO52QMDGOCEANQCD2TRACK TRFDFigure 3:Global bus utilization (memory pressure =60%)Data Traffic Rate Replacement Traffic Rate Coherence Traffic Rate (b) 16-processors(a) 8-processorsA D MR C 2DF E S MO 52QM D GC E A NQ C D 2R A C KT R F DA D MR C 2DF E S MO 52QM D GE A NQ C D 2A C KT R F DA D MA R C 2DD Y FE S MF L O 52QM D GO C E A NQ C D 2T R A C KT R F DA D MR C 2DF E S ML O 52QM D GC E A NQ C D 2R A C K T R F DD MC 2DS M52QD GA NC D 2C K R FD A D MA R C 2DD Y FE S MF L O 52QM D GO C E A NQ C D 2T R A C KT R F DFigure 4:Bus traf fic rate per reference (memory pressure =60%)at the tag.The inclusion property [1]is maintained in thememory hierarchy.Figure 2gives a block diagram for a DICE node.As in a traditional shared-bus machine,every node snoops all global bus traf fic.In dealing with large AM,it can be challenging to have a snoop control logic that can keep up with a modern backplane bus with a high clock fre-quency,especially if the memory access model is based on the sequential consistency [10].For example,with the SGI POWERpath-2[3],each bus transaction takes five clock cy-cles of the 47.6MHz clock,and the snooper has about 35ns (less than two cycles)to search the state and tag for its AM and then update the state if necessary.With the fast SRAMs currently available,the snooper has little dif ficulty in keeping the AMs of the COMA coherent.However,if the snooper cannot keep up with the fast clock of the back-plane bus,one can adopt relaxed memory models such as the release consistency [4]in order to perform the snoop-ing asynchronously and delay the coherence actions.Note that recent high-performance microprocessors support the relaxed memory models [6].A major overhead involved in the COMA is additional extra memory.One source of this need for extra memory isthe state and tag memory for the AM.While it is not sig-ni ficant in terms of the amount of space,the state and tag memory can be a signi ficant overhead in terms of cost.Ex-tra memory is also needed for the unallocated space,which has been reported to be essential for good performance of the COMA.Since the unallocated space is necessary mostly for shared variables,its amount can be kept reasonably small [7,8,9],especially when the set-associativity for the AM is four or higher.2.3Potential performanceTo gauge the potential performance advantage of a bus-based COMA multiprocessor over the traditional bus-based SMPs,we have simulated a “scaled-down ”DICE machine labeled DICE in Figure 3and a traditional shared-bus mul-tiprocessor modeled after the SGI Challenge [3]labeled SMP .The effects of contention at the processor cache,at the local memory,and at the shared bus are re flected in our simulation results.A detailed description of our simulation environment and results are found in [13].Figure 3and 4show the bus utilization and traf fic rate per reference for the studied architectures respectively.ForLocal EventBus-Induced EventReplace-Related Event Figure5:DICE write-invalidate coherence protocol(PR: Processor Read,PW:Processor Write,NR:Network Read, NW:Network Write,NI:Network Invalidation,NTO:Net-work Transfer of Ownership,NNOC:Network No Other Copy)the nine programs from the Perfect Club Benchmark[2], our simulation results show significant bus traffic reduc-tion.DICE generated slightly more traffic for replacement and coherence for some programs.The results are consis-tent with the results of our previous study[12].A recent study[11]on a bus-based COMA multiprocessor reports a similarly significant reduction in bus traffic:a traffic re-duction of up to70%,with an average of46%,for the six SPLASH benchmark[19]programs.3Coherence and ReplacementIn this section,we outline the coherence and replace-ment protocol for the DICE multiprocessor.More details of our coherence and replacement protocol are found in[13]. We discuss major aspects of the protocol,which is different from the one for traditional SMPs.Figure5shows the four-state write-invalidate coherence protocol for DICE.An AM block can be in any one of the four states:Invalid(INV),Shared Non-owner(SHN), Shared Owner(SHO),and Exclusive(EXL).The SHN state is a non-owner state and guarantees that the block in this state is not the only copy in the system.The SHO state is an owner state and carries an ambiguity–there may or may not be other copies.The EXL state guarantees that the block is the only copy in the system,and ownership is implicit.The SHO and EXL states indicate the responsibility of supply-ing data when a read or write request for the block is seen on the bus.Ownership removes the ambiguity in responding to bus transactions(e.g.,on an AM miss)and reduces the traffic re-lated to memory block replacement,which poses a unique problem in COMA multiprocessors.A falling-off block due to replacement,if it has ownership,needs to transfer its ownership to a shared copy if any,or relocate to a remote node if it is the“last copy”of the memory block.Although the cache-like local memory can be backed up by system disk(s)on replacement,its tremendous overhead prohibits such operations.On a reference miss,a(victim)block in the set to which the reference maps has to be selected to receive the incom-ing data.Unlike LRU or random selection in traditional caches,the states of the blocks are used to choose the vic-tim prioritized in the following order:INV,SHN,SHO, EXL.The INV and SHN states do not incur the relocation process.Figure6shows the results of this priority-based selection for several cases assuming4-way set-associative AMs.Victim candidates after the priority-based selection are marked with a darker block,and the victim is selected randomly should there be more than one candidate.If the selected victim is in the SHO or EXL state,it needs to be re-located.A priority scheme is used in choosing which node to accommodate the block to be relocated.Figure7briefly demonstrates our priority scheme.A node with a shared copy of the replaced block is given the highest priority.It is clear that this case is possible only when a block in the SHO state is replaced.Ownership transfer without an AM update suffices in this case.The second priority is given to the node with a block in the INV state and no shared copy of the replaced block.The data will be stored in the block frame,and the resulting state is EXL regardless of the state that the original replaced block had.Next priority is given to a node with a SHN block which is not identical to the replaced block.The lowest priority is given to a node with blocks all having ownership.To avoid the chain of relo-cation,a processor node which originates relocation can ac-quire ownership of the incoming data,so that the block to be relocated may not go down to the lowest priority case[13]. It may seem that relocation to the node with a block in the INV state is preferable to the node having a shared copy of the replaced block.However,our scheme favors a node with a shared copy because(i)relocation incurs ownership transfer only,and(ii)better performance can be achieved from the efficient use of memory space[7].4A Global Bus DesignWe present in this section a global bus design for DICE based on our previous discussions.A complete description of this section can be found in[17]and[18].Our design uses the IEEE Futurebus+standard bus.The implemen-tation presented here is one of many possible implemen-tations.Although the design described in[17,18]usesState Block BxBxFigure 6:Victim block selection (B x :incoming block to satisfy a miss)a write-update policy,our discussion is limited to the one with a write-invalidate policy.4.1FB+backgroundWe chose the Futurebus+(FB+)[22]for our global bus implementation.In the discussions which follow,the imple-mentation uses the B-pro file speci fication detailed in IEEE 896.2for a couple of reasons.The pro file B supports a dis-tributed arbitration protocol,which is desirable not only to remove the poor system scaling associated with a central arbitration but also for the replacement and relocation al-gorithm.Moreover,several companies including Mupac,Schroff,and Texas Instruments (TI)[21],offer pro file B compliant chip-sets,backplanes,and Eurocard enclosures.This greatly simpli fies the bus interface design by providing a proven implementation of the pro file.Table 1shows the transaction mapping between those proposed to support the DICE multiprocessor and those pro-vided by the FB+.To enhance the capabilities of the ba-sic bus transactions,the IEEE 896.1speci fication provides eight user-de fined signal lines,TAG[7:0].In addition,two modes of data transfer are provided on the bus,namely packet mode and compelled mode .The first allows up to a 64-contiguous-byte transfer using only the address of the first word.The compelled mode on the other hand requires a handshake for each data transfer.The Read/Write Un-locked transactions may be used in the packet or compelled mode for any transactions which are 8,16,32,or 64bytes in length.The Read/Write Partial transactions are to transfer 7bytes or less and are restricted to the compelled mode.The FB+is basically comprised of two individual global buses.The AD[63:0]bus is a multiplexed address/data 64-bit path that is responsible for all address and data trans-fers.The second bus is thearbitration bus.Arbitration mes-Figure 7:Selecting a remote AM for relocationsages are interrupts and general system information that can be transferred throughout the system in parallel with data bus activity.In addition,this bus can provide arbitration for a bus master-elect while another bus device is the current bus master.This provides the ability to hide some of the latency associated with a distributed arbitration protocol for gaining global bus access.Basic read or write transactions are conducted in three separate phases.The first phase is called connection phase and is initiated by the bus master.During this phase the master drives the AD[63:0]bus with the address to read from or write to.In addition,signal lines are driven to indi-cate the phase of the transaction,the transaction type and the style of transfer,packet or compelled.In data phase ,which is the second phase,data is transferred via packet or com-pelled mode over the AD[63:0]bus.The last phase in the transaction is disconnection phase and is used to terminate the FB+transaction.The master can issue another transac-tion (bus park ),or release the bus tenure to the master-elect waiting to carry out a transaction.Arbitration in FB+can be initiated any time,regardless of the state of an ongoing bus transaction.The only de-pendence on the address bus is AS*(Address Sync)which indicates to the system that the bus master is terminating its tenure and the bus will be available.Depending on bus traf fic,the arbitration latency can be completely hidden.We use the TI chip-set [21]for our design,which is comprised of three chips,the TFB2010arbiter,the SN54-FB/SN74FB 2032competition transceiver,and the SN54FB/SN74FB 2040TTL-BTL transceiver.The TFB2010design greatly simpli fies the task of system mes-Read Unlocked+-M Miss (B)-I Invalidate (B)-C Copy NoneRead Unlocked 0000100Write Unlocked 0100000Write PartialRead Partial or Read Unlocked Write Partial or Write Unlocked Write Unlocked -M Miss (B)COMA TransactionsBasicTag[7:0]TransactionsVariationB: Block Transfer P: Partial TransferFuturebus+ B-Profile-H Hit (P, B)Write Partial or Write Unlocked 0001000TASREP WRRD0010000-U Uncached(P, B)-U Uncached(P, B)-R Relocate -Rp Relocate Read Unlocked 000000100000000000010000000000100001000000Read Unlocked Read Unlocked Table 1:Transaction mappingsages and FB+arbitration.Programming and normal con-trol of the arbitration process is accomplished through the CSR (Command and Status Register)bus.CS registers in-side the TFB2010may be written to or read from in order to set arbitration priorities,con figure operations,send mes-sages,obtain interrupts,and observe the TFB2010status.The CS registers together with the distributed arbitration are important features that make our implementation ef ficient.Some backplane buses without such features may necessi-tate a certain COMA transaction such as replacement to be implemented in more than one bus transactions.In the remainder of this section,we summarize the im-plementation of each transaction.Also,we describe how re-placement in local memory can be handled with little over-head.4.2RD -M,-U,and -I:Read RequestThe RD (ReaD request)transaction is made up of three distinct modes of operation.Two of the modes,-M (Miss)and -I (Invalidate),support the DICE architecture while the -U (Uncached)mode helps to maintain 896.2Pro file B com-pliance,which is necessary to incorporate ‘third-vendor ’I/O boards.4.2.1RD -MWhen a read request issued by a processor misses in the local memory,an RD -M transaction will be issued on the global bus.The transaction will always operate on a com-plete memory block and use the packet mode of data trans-fer.4.2.2RD -UThe RD -U is a read transaction that will not be cached by the recipient of the data.In addition,the slave node sup-plying data will not alter the coherence state in the local memory.Unlike the RD -M transaction,RD -U can transfer a byte,word,double word,or even multiple blocks of data using the compelled mode or packet mode of data trans-fer.An uncacheable read transaction helps to meet two of the implementation goals for the DICE project,archi-tecture support and speci fication adherence.By providing an uncached transaction,a node can conduct transactions to I/O devices and other resources that are not included in the cacheable shared memory space of the system.Also,RD -U provides direct support for memory references signaled as non-cacheable by the CPU.The second goal of adhering to a speci fication will allow the design to take advantage of industry standard system support devices such as DMA,bus bridges,and networking support.4.2.3RD -IRD -I is one of the transactions unique to a bus-based COMA.In traditional systems,memory recovery and page write-backs to disk are an ongoing process.With respect to main memory storage,these actions are governed solely by the operating system.In the DICE multiprocessor main memory is not only distributed but also of a cache structure.Consequently,sim-ply altering a page table entry and writing back a “copy ”of a page to disk is insuf ficient to provide data integrity and co-herence.For example,if a page is written back to disk and copies are left in the local memories of processing nodes,regardless of what occurs in the L1and L2caches,when the page frame is re-allocated by the operating system there will be two different sets of data available.When the RD -I transaction is used to write a page back to disk,the actual page transfer is most commonly handled by a DMA device,independent of the processor(s).During the connection phase of the transaction all nodes snoop the address.Those with SHN coherence state invalidate their copies.The sole node in EXL or SHO state will complete the transaction by first sourcing the RD -I transaction with the requested block then invalidate its own copy.In addition,each node with a valid copy will also invalidate the L2cache which will in turn invalidate the L1cache.Although this problem hap-pens also in a traditional SMP with copy-back cache,the problem is more extended in the COMA and fairly compli-cated due to the relocation process to handle the last mem-ory block problem.4.3WR-M,-H,and-U:Write RequestThe WR(Write Request)transaction is also comprised of three modes of operation.An uncached(WR-U)opera-tion is again defined to support the B-profile.4.3.1WR-MThe DICE architecture assumes a write-allocate policy, however,revising this to no-allocate or allocate-on-demand should not be difficult.To allocate a block to the local memory,WR-M transaction turns to a RD-M transaction with a different TAG[7:0],which signals invalidation of other copies,if they exist in the system.To support write-invalidate policy for coherence,any write reference to a block in the SHN or SHO state will also incur a WR-M transaction.A WR-M transaction is similar to RD-I trans-action,but potential initiating source can be different.By implementing WR-M as a simple transaction the latency seen by the initiating CPU and the length of the global bus tenure can be minimized.4.3.2WR-HWR-H is a write partial transaction used to update remote copies for processor write memory references which hit in local memory on the SHN or SHO states.The TAG[7:0]set-ting separates it from the partial write of the WR-U transac-tion.In addition,TAG[0]is used to indicate to the mastering node the presence of any remote copies.If the transaction completes and TAG[0]is asserted then there exists at least a shared copy in the system.However,if the transaction com-pletes with TAG[0]unasserted then the mastering node is able to update a SHN copy to EXL.With a write-invalidate policy,the WR-H transaction is not necessary.However, the WR-H transaction can be useful to optimize DICE fur-ther than presented here,which is beyond the scope of this paper.4.3.3WR-UThe WR-U is a write transaction that will not be cached by any recipient of the data.Similar to RD-U,WR-U can transfer a byte,word,double word,or even multiple blocks of data using the compelled or packet mode of data transfer.4.4REP-C,-R,and-Rp:Replacement and Relo-cationREP(Replacement)-C(Copy),REP-R(Relocate),and REP-Rp(Relocate page)are related with the replacement protocol described in Section3.Figure8:Block relocation mechanism4.4.1Relocation mechanismFigure8conceptually demonstrates how this replacement and relocation is handled in a processor node.On a ref-erence miss,the node decides whether relocation is neces-sary(1a).It sends a data request on the bus while fetching the replaced data from the local memory(2a).It puts the fetched data into the relocation buffer along with the state (3a).Upon the arrival of missing data,it begins the relocate transaction,and the processor now can resume its execution (4a).From the viewpoint of a remote node,when a relocate transaction is seen on the bus,the node buffers the data with its address and state(1r).The node looks up the AM state and tag memory to decide its priority in accepting the block it has just received(2r).Based on the result of the state and tag look-up,it generates and sends to the arbiter a priority vector,which is the2-bit priority concatenated with its node ID(3r).In case of a tie in the2-bit priority,the node ID,the lower bits in the vector,will help decide the winner.After arbitration,the result will be passed back to the controller, which will either update the AM and the tag,or discard the buffered data(4r).The distributed arbitration determines the unique winner which will accommodate the block,and all other nodes will discard the block,thereby achieving our goal.4.4.2REP-CThe REP-C transaction is always performed on non-page fault generated replacements.It is responsible for obtaining a copy of the block that contains the reference missed in the local memory.Although the-C transaction is an unlocked block read as RD-M,following every REP-C,without loss of tenure,is an REP-R transaction.REP-C is very similar to the transfer mechanism of the RD-M transaction.A global request is issued and the nodewith ownership responds by supplying the data.In addition to the data requested,the mastering node also takes over the ownership attribute for the block.This is done to ensure that a location will exist for the relocation transaction following the REP-C.A more complete description and an example of the ownership transfer(and ownership relinquish)is given in[13].4.4.3REP-RWhen REP-C completes the CPU request can be satisfied and allowed to execute the next instruction.However,the issue of relocating the block which initially occupied the local memory,causing the collision,still remains.The REP -R transaction utilizes the arbitration protocol of the FB+ previously described to accomplish relocation.Without loss of the bus tenure,the REP-R transaction is initiated imme-diately after a REP-C completes.The transaction is com-pletely controlled by the GBTC(Global Bus Transaction Controller,in Figure2)and does not involve the LBTC. This allows the LBTC(Local Bus Transaction Controller) to service the CPU for accesses to the local memory.The GBTC controls the HOST bus and places a block transfer write request to the address of the block needed to be relocated.The global bus interface views this as a packet mode transfer of the number of bytes equal to a block size. Each remote node will search their local memory tags as in previous transactions,however,the response of each node depends on the state of all the blocks in the set to which the address maps.In addition,remote nodes do not simply handshake with the FB+communication protocol but par-ticipate in an arbitration for the block being relocated.Once nodes have determined their priorities using the scheme outlined in Section3,each arbitrates using the FB+ arbitration protocol.The arbitration priority of the relo-cation algorithm is such that master-elect preemption will take place and that only nodes participating in the arbitra-tion have the opportunity to win.When the arbitration completes,the winner will be the node which takes the block being relocated.The priority of the node winning the arbitration determines what state the block will be placed in.If an INV block or an SHN block not of the same address wins,then the block can be placed in local memory in the EXL state.As in the WR -H transaction,TAG[0]is used to remove the ambiguity of relocation.When a SHN state node of the same address wins the arbitration,TAG[0]is used to determine if the state should be EXL or SHO.4.4.4REP-RpIn a bus-based COMA multiprocessor,page faults must be managed differently from conventional SMPs.The primary reason is that the local memories of the system are caches to the entire shared address space.Local memories are-way set-associative and therefore have locations per node where a page may be located.Also,a page fault in a tradi-tional system generally has no need to alter the location of data already in the system unless memory is full.However, a page fault in a COMA system can result in a significant redistribution of data due to a collision with the incoming page.This can occur if the incoming page maps to a loca-tion in local memory which is occupied by block(s)of data in the EXL or SHO state.When a page fault occurs in DICE,a page frame of mem-ory must be guaranteed to exist which maps to the incoming page.With sufficient unallocated memory,there exists such a page frame[8].However,guaranteeing available space somewhere in the system does not guarantee available space in a specific node,nor does it guarantee that the available space is contiguous.Since the concept of locality suggests that it would be highly beneficial if the node originating the page fault should also be the recipient of the incom-ing page[15],clearing specific locations for the incoming page may become necessary.Clearing a page of data in the local memory may only require reserving space if no EXL or SHO attributes currently exist.In the case where all the blocks are not in the INV or SHN state,a relocation trans-action becomes necessary for each of those blocks.When a page fault occurs,the GBTC on the node will begin processing contiguous range of memory associated with the page.The GBTC will go through each block ad-dress in the page range and mark INV and SHN copies with the Occupied tag status.Blocks in the EXL or SHO state must be relocated as described in Section4.4.3with the ex-ception of the relocation buffer,it is not necessary in this case since there is currently not a collision.Once an EXL or SHO block has been relocated the block frame is marked with the Occupied state.When the last block address in the page range reached,the page fault support by the GBTC is complete.Note that blocks coming in from disk and block relocation due to the REP-Rp can be intermixed because of the priority assigned to the REP-Rp transaction and the lower priority of the DMA device when performing the WR -U transaction to move the page into memory.This is fully supported by the FB+arbitration protocol and the round robin fairness mechanism.4.5Synchronization,I/O transactions,and inter-rupt supportThe TAS transaction is defined(in Table1)as a read block followed by a write partial to implement synchro-nization instructions such as test-and-set.The memory lo-cation being accessed must remain under the control of a single processor for the duration of the read-modify-write cycle.In order to implement this on the TI chip-set two。