基于Verilog HDL语言的ISE设计流程

ISE开发环境使用指南[FPGA开发教程

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

基于Verilog 的有限状态机设计

基于Verilog 的有限状态机设计与优化1 引言在集成电路的设计过程中, 不论是使用FPGA还是ASIC 来实现, 有限状态机经常是作为一个电路设计的关键部分而出现的. 状态机的功能是否完善( 是否强壮型) 对整个电路会产生重大的影响.有限状态机主要有两种类型: Moore 型状态机和M ealy 型状态机. Moore 型状态机是指输出只与当前状态有关, 与输入信号无直接关系. 而Mealy 型状态机的输出不只与当前状态有关, 还与输入信号有关.文中以目前常用的硬件描述语言Verilog HDL 为基础, 对不同的状态机编码类型和状态机描述风格对状态机性能的影响进行了深入的分析. 分别使用Xilinx ISE 和Design Compiler 对实例进行了综合,分析了面积、速度与功耗的信息, 给出了对于不同类型状态机的最佳编码风格.2 状态机编码状态的编码方式最常用的有二进制码、格雷码和独热码三种, 不同的状态机编码方式对状态机的影响非常大. 如表1 所示.二进制的编码从第一个状态到最后一个状态是按二进制码的顺序排列的, 是一种最普通的编码方式.表1 不同的编码比较十进制码Binary code Gray code One- hot code0 000 000 00011 001 001 00102 010 011 01003 011 010 1000用格雷码进行状态的变换时, 相邻状态转换只有一个状态位发生翻转. 这样就可以消除转换时由多条状态信号线的传输延迟所造成的毛刺, 大大地减少了由一个状态到下一个状态时逻辑的混淆可以降低功耗.one- hot 状态译码简单, 只有1 位是1 其他位为0, 易于修改, 可以减少组合逻辑, 但会使用更多的触发, 增加电路面积.Binary- code、Gray- code 编码使用最少的触发器, 较多的组合逻辑, 而One- hot 编码反之.因此, Binary 和Gray- code 适用于触发器资源较少, 组合电路资源丰富的情况( CPLD) , 对于FP GA 则更适用One- hot code, 因为这样可以充分利用FPGA 丰富的触发器资源. 另外, 小型设计通常使用Binary- code 和Gray- code, 对于大型的设计使用One- hot code 效果更佳.3 状态机的描述方法状态机的描述方法通常有三种: 一段式( one al ways) 、二段式( two always) 和三段式( three always) .3. 1 一段式一段式的状态机描述方法是指将整个状态机写到一个alw ays 模块里, 该模块描述当前状态转移, 又描述状态的输入和输出.由于一段式的描述方法是给STATE 自身赋值, 所以本身就会引入一个周期的延时, 需要在设计中通过预计算考虑进去.一段式的描述方法所有输出都是寄存器输出的, 因此不会产生毛刺, 但是这种组合逻辑和时序逻辑都写到一起的方法是不可取的, 而且在描述当前状态的时候还要考虑到下一状态的输出. 这种描述方法可读性差、难于理解和维护, 不利于时许约束、功能更改及调试, 对于Mealy 型的状态机来说, 容易出现Latches.3. 2 二段式二段式的状态机描述方法是指使用两个always模块, 其中一个always 模块采用同步时序的方式描述当前状态和下一状态的转移, 另一个alw ays 模块采用组合逻辑来描述下一状态和输出向量的赋值.二段式的描述方法比一段式的更合理, 它更易于阅读、理解和维护, 更利于综合并优化代码. 但是它的缺点是第二个alw ays 块组合逻辑的输出会出现毛刺, 影响电路性能.3. 3 三段式三段式的状态机描述方法是由二段式发展而来的, 在二段式两个alw ays 的基础上又增加了一个alw ays 块来描述每个状态的输出, 用寄存器寄存了一拍, 达到同步输出的目的.需要注意的是, 增加的一级寄存器会引入一个周期的延时, 需要在设计中通过预计算考虑进去, 避免逻辑发生错误. 这样一级寄存器的引入, 也就形成了FSMs 输入逻辑的一级流水.引入了组合逻辑寄存, 输出同步不仅会带来运行性能的提升, 还会增加系统的稳定性, 防止输出信号出现毛刺, 防止组合回路的产生.4 实例分析下面以一个简单红绿灯状态转移为例进行分析, 当RESET 信号给出以后进入IDEL 状态, 之后状态机的描述方法通常有三种: 一段式( one al 进入RED 状态, 之后进入GREEN 状态, 之后进入YELLOW 状态, 最后回到RED 状态. Default 时进入IDEL 状态.一4. 1 使用Xilinx ISE 进行分析在使用Xilinx ISE 对例子进行综合的时候, 右键点中综合软件, 选属性选型, 在HDL Options 中有一个优化选项为FSM Encoding Algorithm, 在其下拉菜单中选中AUTO( 默认项) , 工具就可以自动修改设计中的状态机的状态编码, 使其成为对FPGA 来说最优的编码风格.对于本设计来说, 由于只有4 个状态, 所以状态编码被优化成了Gray- code. 但是经过验证, 在状态较多的状态机设计中, 状态编码一般都被优化成One- hot code.通过表2, 对Xilinx ISE 的综合后报表进行分析可以看到, 由于one always 的状态机全部为时序电路,所以最大频率会比two alw ays 和three always 大.在面积方面, two always 型的状态机所占面积最小, three alw ays 稍大, 而one alw ays 型的状态机所用门数最多, 所占面积也最大.对于功耗来说, 使用Xilinx ISE 集成的Xpower进行功耗分析, 所得到的三种状态机编码风格的功耗并不存在明显差异.表2 Xilinx ISE 的综合结果使用门数最大频率one alw ays 8 313. 283MHztwo always 43 312. 891MHzthree alw ays 67 312. 891MHz4. 2 使用Design Compiler 进行分析在使用Design Complier 对所举实例进行分析话时, 分别选取了1always& binary、1always& one - hot、2always& binary、2alw ays& one - hot 、3alw ays& binary、3always& one- hot 等6 种设计, 每个设计分别设定了2 个时钟周期( . ns 和7ns) 进行分析. 综合得到的面积和延时的结果按顺序标在图2、图3 中. 表3、表4 给出了详细的数据.由图2 可见, 2alw ays 在面积上具有明显优势,其次是3alw ays. 由图3 对时序的分析可见, 2alw ays也是具有一定的优势.比较使用Design Compiler 和Xilinx ISE 的综合结果可以发现, 不论是使用FPGA 还是ASIC, tw oalw ays 所占面积总是最小的, 其次是three alw ays,而one alw ays 所占面积最大. 这主要是由于one alw ays 的状态机全部为时序电路, 所以花费的面积最大, three alw ays 由于多采用一级寄存器同步, 所以所花费的面积比two always 的要大一些.5 比较分析通过以上分别使用Xilinx ISE 和Design Compiler 对实例进行的分析, 可见two alw ays 的编码风格存在巨大的优势. 因为Moore 型的状态机输出只有状态寄存器驱动, 状态机所受影响差异不会很大,所以建议对Moore 型状态机采用two alw ays 的编码风格.而Mealy 型状态机, 输出不只与当前状态有关,还与输入信号有关, 输出是组合逻辑的输出, 这样在每个STATE 中产生的信号复杂而且有不同的timeskew , 如果信号直接输出而不引用寄存器同步的话, 在高频的电路中很可能会导致时序上的错误. 所以建议使用three alw ays 风格, 将输出同步一拍.对于one alw ays 的风格, 虽然在一些开源的IP盒中经常见到, 但是通过以上的分析, 可以发现这种状态及描述风格存在着巨大的缺陷.至于状态编码的使用, 对于FPGA 来说建议使用工具自动优化状态机的状态编码, 而对于ASIC 来说, 建议在小型设计中使用Binary- code 和Gray code, 而对于大型的设计则使用One- hot code.6 结束语文中结合了一个Verilog HDL 的实例, 对三种不同的状态机编码和状态机描述方式进行了深入的研究, 分析了其各自的优缺点. 并分别使用Xilinx ISE 和Design Compiler 对一个实例进行了综合, 对面积、速度与功耗进行了分析. 结果表明one alw ays的写法需要被摒弃, two alw ays 的编码风格适合Moore 型状态机, 而three always 的编码风格适合Mealy 型状态机. 文中同时也给出了适合不同设计的最优状态编码。

ISE使用指导

-3-

ISE 使用说明

下一步,进行可编程器件型号的选择以及设计流程的设置。在器件型号栏有 Device family , Device (型号) ,封装,speed grade,可以根据实验平台所用的可编程逻辑器件分别设置相 应选项。对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了 New Project Information 的设置。如图所示:

-9-

ISE 使用说明

count<="000000"; end if; elsif flag='1' and flag1='1' then if count<59 then count<=count+1; elsif count>=59 then count<="000000"; end if; end if; end if; end process; end Behavioral; -- flag='1' , 则进行 60 进制计数

然后单击工程 counter 下的子目录 count-Behavioral(count.vhd) , 接着在界面的 Processes for Source 一栏选择 Implement Design,进行布局布线的综合:

-15-

ISE 使用说明

然后工程名 counter 上单击右键,弹出对话框,选择新建 Test Bench Waveform,在 file 命名 为 test_counter。

在界面的 Processes for Source 一栏,是一系列综合工具。 Synthesize XST 工具一般可以分析 代码的语法错误,查看错误报告和 RTL 级的电路设计图。 单击 View Synthesis,出现如图所示对话框:

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

Verilog_HDL复杂数字系统设计-2_[1]...

![Verilog_HDL复杂数字系统设计-2_[1]...](https://img.taocdn.com/s3/m/3f4f2f7ba26925c52cc5bff2.png)

2013-8-4

南通大学电子信息学院

7

1.3复杂数字系统的设计方法

1.3.1 复杂数字逻辑系统

• 嵌入式微处理机系统

• 数字信号处理系统 • 高速并行计算逻辑

• 高速通信协议电路

• 高速编码/解码、加密/解密电路 • 复杂的多功能智能接口

• 门逻辑总数超过几万门达到几百甚至达几千万门的数

字系统

2013-8-4 南通大学电子信息学院 8

1990 Verilog HDL 公开发表

1995 Verilog IEEE1364 标准公开发表

1990有关Verilog HDL的 全部权利都移交给OVI(Open Verilog International)组织

2013-8-4 南通大学电子信息学院 6

1.2.3 Verilog HDL的优点

2013-8-4

南通大学电子信息学院

24

例2-2b 4选1多路选择器

module mux4_to_1 (out, i0, i1, i2, i3, s1, s0); output out; input i0, i1, i2, i3; input s1, s0; wire s1n, s0n; wire y0, y1, y2, y3; not not0(s1n, s1); not not1(s0n, s0); and and0(y0, i0, s1n, s0n); and and1(y1, i1, s1n, s0); and and2(y2, i2, s1, s0n); and and3(y3, i3, s1, s0); or or0(out, y0, y1, y2, y3); endmodule

2013-8-4 南通大学电子信息学院 3

Verilog HDL数字设计教程(贺敬凯)第1章

路网表。

第1章 Verilog HDL数字设计综述

波形图输入方法则是将待设计的电路看成是一个黑盒子,

只需告诉EDA工具该黑盒子电路的输入和输出时序波形图,

EDA工具就可以完成黑盒子电路的设计。 原理图输入方法是一种类似于传统电子设计方法的原理 图编辑输入方式,即在EDA软件的图形编辑界面上绘制能完 成特定功能的电路原理图。原理图由逻辑器件(符号)和连接

理图和信号的连接表,如果是一个大的系统,将是一大摞图

纸,以后系统若出现问题,查找、修改起来都很麻烦。

第1章 Verilog HDL数字设计综述

上述过程是从底层开始,或在已有的功能模块的基础上 来搭建高层次的模块直至整个系统的。因此这种传统的电子 系统的设计过程是一种自底向上(Bottom-Up)的设计,设计 过程必须从存在的基本单元模块出发,基本单元模块必须是 已经设计成熟的标准单元模块或其他项目已开发好的单元模 块。

第1章 Verilog HDL数字设计综述

本书所有设计最终的实现目标主要定位于FPGA,因此下

面重点介绍FPGA的开发流程。FPGA的EDA开发流程如图1-3

所示。

第1章 Verilog HDL数字设计综述

图1-3 FPGA的EDA开发流程

第1章 Verilog HDL数字设计综述

从图1-3可以看出,FPGA的开发流程与图1-2所示的用 EDA工具设计数字系统的流程基本相同,都需要设计输入、 功能仿真、逻辑综合、布局布线(适配)、时序仿真、物理实 现等几个步骤。下面将分别介绍主要设计模块的功能特点。

第1章 Verilog HDL数字设计综述

1. 设计输入 在EDA软件平台上开发FPGA/CPLD时,首先要将电路系 统以一定的表达方式输入计算机。通常,EDA工具的设计输 入可分为以下两种类型:

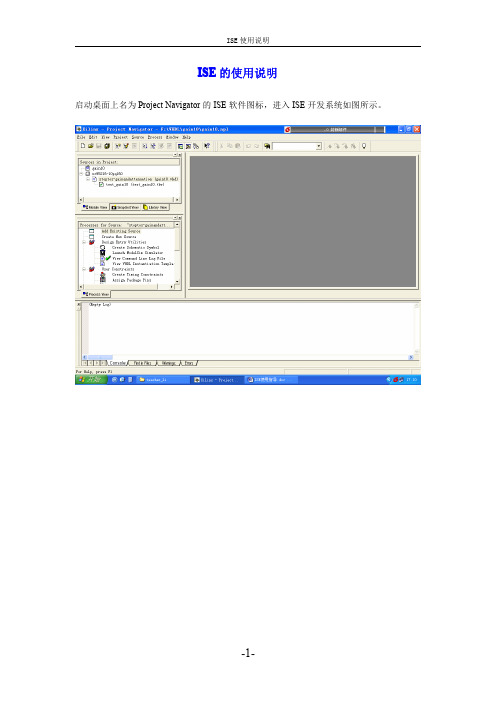

ISE的使用说明

ISE的使用说明建立工程 (2)综合 (12)管脚约束 (14)布局布线的综合 (18)添加波形 (19)仿真 (21)下载 (25)启动桌面上名为Project Navigator的ISE软件图标,进入ISE开发系统如图所示。

在上拉菜单file栏打开,单击New project选项,开始新建一项工程。

如果想打开已有的ISE工程文件(文件格式为*.npl),则单击open project选项。

下面我们将以一个包括了24进制和60进制计数器的复合计数器的VHDL程序为例,来说明ISE的具体使用。

首先单击New project选项,出现如图所示对话框:在Project name一栏填上工程文件名,我们在此工程名命名为counter,放在目录F:\teacher_li 下。

下一步,进行可编程器件型号的选择以及设计流程的设置。

在器件型号栏有Device family ,Device (型号),封装,speed grade,可以根据实验平台所用的可编程逻辑器件分别设置相应选项。

对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了New Project Information的设置。

如图所示:单击“完成”按钮,进入到如下对话框:在Source in Project一栏,选择菜单Module View选项,在工程名counter的图标位置单击右键,出现如下对话框。

New Project :新建一项文件,单击ew Project图标,出现的对话框包括了以下选项:新建IP核,电路设计,状态机,新建测试波形,用户文档,Verilog编写文件,Verilog测试文件,VHDL库,VHDL编写文件,VHDL包,VHDL测试平台。

Add Source :添加一项已经存在的文件。

本例中,首先选择VHDL Module项,我们file name命名为count。

下一步,进行管脚信号名称,位数和方向的设置。

verilog hdl应用程序设计实例精讲

verilog hdl应用程序设计实例精讲网上现在有很多关于verilog hdl应用程序设计的资料,但是并没有一个很系统和全面的教程来帮助初学者快速入门。

本文就verilog hdl应用程序设计实例进行了精讲,从基本概念到应用实例一步一步地回答了初学者的问题,帮助大家理解verilog hdl的设计和应用。

一、verilog hdl的基本概念Verilog HDL是一种硬件描述语言,用于描述数字系统,包括逻辑电路、集成电路等等。

它既可以进行仿真验证,也可以直接生成硬件电路。

简单来说,verilog hdl就是一种用来描述数字系统的语言。

1.1 模块与实例化在verilog hdl中,模块是最基本的设计单元,每个模块包含一个或多个端口和内部逻辑电路。

模块可以包含其他模块,这被称为实例化。

实例化可以理解为创建一个模块的实例,并根据实例进行连接。

1.2 端口和内部信号模块的端口是与其他模块或外部电路连接的接口,可以是输入、输出或双向。

内部信号是模块内部产生和使用的信号,只在模块内部可见。

1.3 组合逻辑与时序逻辑组合逻辑是指只有输入信号改变时才会改变输出信号的逻辑电路,而时序逻辑是指输出信号的改变还受到时钟信号的控制。

在verilog hdl中,可以使用逻辑门、逻辑运算符和条件语句来实现组合逻辑和时序逻辑。

二、verilog hdl应用程序设计实例接下来,我们通过一些实例来展示verilog hdl的应用程序设计。

2.1 4位全加器我们首先来实现一个4位全加器。

全加器是用来实现两个二进制数的加法的电路,它能够实现两个输入和一个进位的相加操作,输出结果和进位。

在verilog hdl 中,可以使用逻辑运算符和条件语句来实现全加器。

2.2 4位加法器我们可以使用四个全加器来实现一个4位加法器。

加法器是用来实现两个二进制数的加法的电路,它能够实现多位的相加操作,输出结果和进位。

2.3 4位计数器计数器是一种能够实现计数功能的电路,它能够根据时钟信号进行计数,并在达到一定数值时输出特定信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真 添加en信号,点击“restart”按钮

仿真波形窗口

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

可以在控制台窗口,输入命令控制仿真的运行

输入run 1ms, 控制仿真运行时间到1ms

基于Verilog HDL语言的ISE设计流程

--创建一个新的设计文件

选择Verilog HDL Module 输入”top”作为Verilog HDL模块的名字

点击“Next”按钮

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--创建一个新的设计文件

点击“Next”按钮

数字系统EDA技术

选择Verilog HDL Module 点击“Next”按钮

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

点击“Next”按钮

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

点击“Finish”按钮

数字系统EDA技术

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--查看综合后的结果

打开顶层模块的原理图

点击“OK”按钮

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--查看综合后的结果

顶层模块图,端口

鼠标双击该区域,打开 底层设计。

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

翻译的主要作用是将综合输出的逻 --实现设计

辑网表翻译为Xilinx特定器件的底 层结构和硬件原语。

选择top.Verilog 映射的主要作用是将设计映射到具体 型号的器件上。 布局布线的主要作用是调用Xilinx布局 布线器,根据用户约束和物理约束,对 设计模块进行实际的布局,并根据设计 连接,对布局后的模块进行布线,产生 PLD配置文件。 第一步: 转换“Translate” 第二步: 映射“Map”

基于Verilog HDL语言的ISE设计流程

--对该设计进件 刚才的设计文件

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

删除此段代码

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

实现约束文件

IP生成向导 存储器文件 原理图文件 用户文档文件 Verilog模块模板文件 Verilog测试平台模板文件 Verilog HDL模块模 板文件 Verilog HDL库模板 文件 Verilog HDL包模板 文件 Verilog HDL测试平台模板 文件 片上系统设计向导

数字系统EDA技术

添加此段代码 用于生成rst测 试信号

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

添加此段代码 用于生成rst、clk测 试信号

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

展开ISim Simulator

双击Simulate Behavioral Model

选择Implement Design, 并展开

第三步: 布局和布线”Place & Route”

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--查看布局布线后结果

选择Place & Route, 并展开 选择View/Edit Routed Design(FPGA Editor)

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--下载设计到FPGA芯片

先不烧写设计到PROM芯片中,所以选择”Cancel”按钮

数字系统EDA技术

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计文件进行综合

选中top.v文件

鼠标双击该项 控制台界面中给出综合过程的信息

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计文件进行综合

综合工具在对设计的综合过程中,主要 执行以下三个步骤:

语法检查过程,检查设计文件语法是否有错误; 编译过程,翻译和优化HDL代码,将其转换为综合工具

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--查看布局布线后结果

选择放大按钮,查看硅片细节

FPGA硅片布局

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程 CLB

--查看布局布线后结果

连线

Slice

双击,展 开Slice

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--查看布局布线后结果

关闭FPGA Editor界面

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--下载设计到FPGA芯片

准备工作:

将HEP的USB-JTAG电缆分别和计算机USB接

口及EXCD-1目标板上的JTAG7针插口连接; 计算机自动安装JTAG驱动程序; 给EXCD-1目标板上电;

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计文件进行综合

在ISE的主界面的处理子窗口 的synthesis的工具可以完成下 面的任务: 查看RTL原理图(View RTL schematic) 选中该选项并将其展开 查看技术原理图(View Technology Schematic) 检查语法(Check Syntax) 产生综合后仿真模型( Generate Post-Synthesis Simulation Model)。

--下载设计到FPGA芯片

选择Boundary Scan,(边界扫描)

选择Initialize Chain(初始化链)

鼠标右击该区域

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--下载设计到FPGA芯片

点击“Yes”按钮

Xcf04s-Xilinx的串行Flash芯片 xc3s500e-Xilinx的FPGA芯片 两个芯片连接在JTAG链路上

生成了空的工程框架

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--创建一个新的设计文件

选中器件名字,点击鼠标右键

选中New Source…

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--创建一个新的设计文件

块存储器映像文件 在线逻辑分析仪Chipscope定义和连接文件

基于Verilog HDL语言的ISE设计流程

--新建工程

输入工程名字:counter 工程所在的目录

点击“Next”按纽

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--新建工程

产品范围(product category) 芯片的系列(Family) 具体的芯片型号(Device) 封装类型(Package) 速度信息(speed) 综合工具(Synthesis Tool)

选择实现约束文件 输入”top”作为实现约束文件 的名字

点击“Next”按钮

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--添加实现约束文件

点击“Finish”按钮

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--添加实现约束文件

选择top.Verilog 实现约束文件top.ucf已经添加到设计中

关闭整个仿真窗口,继续下面的设计

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--添加实现约束文件

选中Implementation选项

选中top.Verilog,点击鼠标右键 选中New Source…

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--添加实现约束文件

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--下载设计到FPGA芯片

选择top.Verilog

选择Configure Target Device,并展开

选择Manage Configuration Project (iMPACT),并双击.

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

选中Simulation选项

选中top.Verilog,点击鼠标右键 选中New Source…

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计进行行为仿真

输入”test”作为Verilog HDL测试模 的名字

--创建一个新的设计文件

此处添加端口声明语句

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--创建一个新的设计文件

产生计数器使能信号

4位16进制计数器模块

下一步对该模块进行综合

数字系统EDA技术

基于Verilog HDL语言的ISE设计流程

--对该设计文件进行综合