第三章EDA_行为级建模

eda技术原理

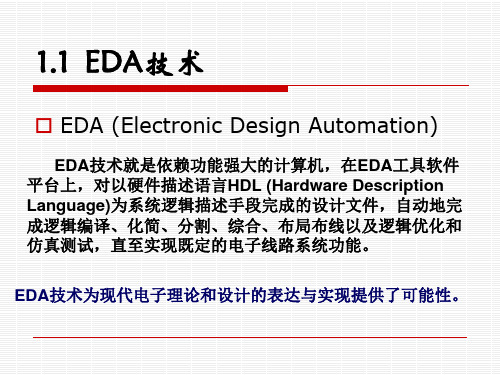

eda技术原理EDA(Electronic Design Automation,电子设计自动化)是一种利用计算机辅助进行电子硬件设计的技术,其原理主要包括以下几个方面:1. 电路建模:EDA技术首先需要将电路进行建模,将电路元件抽象为数学模型,如电阻、电容、电感等元器件被建模为方程式或者矩阵等数学表达式。

这些模型可以通过实验测量或者仿真等方式进行获取。

2. 电路仿真:通过电路仿真软件,将建模后的电路模型输入到仿真引擎中进行电路行为模拟。

仿真可以准确预测电路的性能、稳定性和功耗等参数,以评估电路的可行性。

常用的仿真工具有SPICE(Simulation Program with Integrated Circuit Emphasis)和AMS(Analog and Mixed-Signal)等。

3. 逻辑综合:逻辑综合是将高级语言描述的设计代码转换为电路门级描述的过程。

逻辑综合工具将设计文件输入,通过优化算法对设计进行优化,生成与原设计功能等效的优化后的门电路描述。

逻辑综合主要包括布尔逻辑优化和进一步进行的时序逻辑优化等。

4. 物理布局:物理布局是将逻辑电路映射到具体的芯片布局中。

在物理布局过程中,需要考虑布线、设备位置、连接规则等。

物理布局工具可以自动化生成芯片布局,以满足功能、性能、功耗和面积等要求。

5. 片图设计:片图设计是将电路物理布局转化为特定工艺规则的掩膜层次的过程。

在片图设计过程中,设计人员根据工艺规则规定的要求,设计电路的掩膜层次,以生成最终的芯片版图。

总之,EDA技术通过建模、仿真、逻辑综合、物理布局和片图设计等步骤,实现了电子电路设计的自动化和高效性。

它提高了设计师的工作效率,缩短了产品开发周期,降低了设计错误的风险,并为电子产品的设计与制造提供了可靠的工具和方法。

EDA技术及其应用(3)

1.4 EDA的优势

手工设计方法

●复杂电路的设计、调试十分困 难;

●无法进行硬件系统仿真,若某 一过程存在错误,查找和修改十 分不便;

●设计过程中产生大量文档,不 易管理;

●对于IC设计而言,设计实现过 程与具体生产工艺直接相关,因 此可移植性差;

●只有在设计出样机或生产出芯 片后才能进行实测;

EDA技术

在设计时加入用于测试的部分逻辑,即进行可测性设计(DFT ,Design For Test),在设计完成后用来测试关键逻辑。

在ASIC设计中的扫描寄存器,是可测性设计的一种,原理是 把ASIC中关键逻辑部分的普通寄存器用测试扫描寄存器来代替, 在测试中可以动态地测试、分析设计其中寄存器所处的状态,甚至 对某个寄存器加以激励信号,改变该寄存器的状态。

1.6.3 GAL

GAL的OLMC单元设有多种组态,可配置成专用组合输出、专 用输入、组合输出双向口、寄存器输出、寄存器输出双向口等, 为逻辑电路设计提供了极大的灵活性。由于具有结构重构和输出 端的任何功能均可移到另一输出引脚上的功能,在一定程度上, 简化了电路板的布局布线,使系统的可靠性进一步地提高。GAL 的出现是复杂PLD的里程碑。

1.11 编程与配置

目前常见的大规模可编程逻辑器件的编程工艺有三种: 1.基于电可擦除存储单元的EEPROM或Flash技术。 2.基于SRAM查找表的编程单元。 3.基于反熔丝编程单元。

1.12 FPGA配置器件

主动配置方式

由FPGA器件引导配置操作过程,它控 制着外部存储器和初始化过程

被动配置方式

1.2 EDA技术应用对象

全定制或半定制ASIC

实现目标 ASIC的设计和实现

FPGA/CPLD(或称可编程ASIC)开发应用

EDA课件第三章

tmp2:=d1 AND (NOT sel); tmp3:=tmp1 OR tmp2; tmp<=tmp3;

q<=tmp AFTER m; END PROCESS cale;

END ARCHITECTURE connect;

(2) 端口方向

端口方向用来定义外部引脚的信号方向是输入还 是输出。

凡是用“IN”进行方向说明的端口,其信号自端口 输入到构造体,而构造体内部的信号不能从该端口输 出。相反,凡是用“OUT”进行方向说明的端口,其信 号将从构造体内经端口输出,而不能通过该端口向构 造体输入信号。

实体说明

一个模块中仅有一 个设计实体。

实体 提供设计模块的接口信息,是VHDL设计电 路的最基本部分。

实体说明具有如下的结构:

ENTITY 实体名 IS

实体说明以“ENTITTY 实体名

[类属参数说明];

IS”开始至“END ENTITTY实体 名”结束。这里大写字母表示

实体说明的框架。实际上,对

此例中的外部引脚

ARCHITECTURE connect OF mux IS SIGNAL tmp:BIT; BEGIN

cale:PROCESS(d0,d1,sel) IS VARIABLE tmp1,tmp2,tmp3:BIT;

BEGIN tmp1:=d0 AND sel;

为d0,d1,sel,q 。

库(Library)是经编译后的数据的集合,它存放包集合 定义、实体定义、构造体定义和配置定义。

设计中的子程序和 公用数据类型的集合。

程序包

IEEE标准的标准程序包 设计者自身设计的程序包

包和库具有这样的关系:多个过程和函数汇集在一起构成包 集合,而几个包汇集在一起就形成一个库。

EDA综合课程设计

04

EDA综合课程设计方法

硬件描述语言

总结词

硬件描述语言是用于描述数字电路和系统的行为、结构和连接的语言。

详细描述

硬件描述语言(如Verilog和VHDL)是电子设计自动化(EDA)中常用的语言,用 于描述数字电路和系统的行为、结构和连接。这些语言具有高级抽象的特点,使得 设计师能够以更抽象的层次描述电路,从而简化设计过程。

03

EDA综合课程设计内容

数字电路设计

数字电路设计基础

掌握数字电路的基本原理,包 括逻辑门、触发器等基本元件

的工作原理和使用方法。

组合逻辑电路设计

学习如何设计复杂的组合逻辑 电路,如加法器、比较器等。

时序逻辑电路设计

掌握时序逻辑电路的设计方法 ,如计数器、移位器等。

数字系统设计

学习如何将多个数字电路集成 在一起,形成一个完整的数字

可编程逻辑器件(如FPGA和CPLD)是实现 数字电路设计的常用硬件平台。在EDA综合 课程设计中,学生需要学习如何使用硬件描 述语言对可编程逻辑器件进行编程,以实现 所需的数字电路功能。这需要学生掌握逻辑 门、触发器等基本数字逻辑单元的使用,以 及熟悉常见的数字电路设计方法。

05

EDA综合课程设计实践

系统级电路设计

系统级电路基础

了解系统级电路的基本原理和结构, 掌握常见的系统级电路类型。

系统级电路设计方法

学习如何使用硬件描述语言进行系统 级电路设计,提高设计的效率和可靠 性。

系统级电路仿真和验证

学习如何使用仿真工具进行系统级电 路的仿真和验证,确保设计的正确性 和可靠性。

系统级电路应用

了解系统级电路在各个领域的应用, 如计算机、通信、航空航天等。

EDA的使用流程

EDA的使用流程1. 什么是EDAEDA全称Exploratory Data Analysis,即探索性数据分析。

它是数据科学中非常重要的一步,通过EDA可以帮助我们理解、总结和分析数据集,为后续的建模和预测工作提供依据。

2. EDA的主要步骤EDA的主要步骤包括数据获取、数据预处理、数据探索和数据可视化。

2.1 数据获取数据获取是EDA的第一步,通常情况下我们会从文件、数据库或者API中获取数据。

一种常见的方式是使用Python编程语言,利用pandas库来读取和处理数据。

2.2 数据预处理数据预处理是为了保证数据的质量和准确性,通常包括以下几个方面的处理:- 缺失值处理:对于缺失的数据,可以通过填充、删除或者插值等方式进行处理。

- 异常值处理:对于异常值,可以进行删除或者修正。

- 数据类型转换:将数据转换为适合分析的类型,比如将字符串转换为数值型。

2.3 数据探索数据探索是EDA的核心步骤,通过统计分析和可视化手段对数据进行探索。

主要包括以下几个方面: - 描述性统计分析:通过计算各种统计指标,如均值、中位数、方差等,来了解数据的中心趋势和离散程度。

- 相关性分析:通过计算变量之间的相关系数,来分析变量之间的线性关系。

- 统计分布分析:通过绘制直方图、概率密度图等,来了解数据的分布情况。

- 探索变量间的关系:通过绘制散点图、箱线图等,来分析变量之间的关系。

2.4 数据可视化数据可视化是通过图表方式展现数据的分布、关系和趋势,通过视觉化手段来更直观地理解数据。

常见的数据可视化工具包括matplotlib和seaborn等。

3. EDA的重要性EDA在数据科学中起到了至关重要的作用,具有以下几个重要性: - 发现数据的规律和趋势:EDA可以帮助我们通过数据的可视化和探索来发现数据中的规律和趋势。

- 异常值识别:通过EDA,我们可以识别出数据中的异常值,并进行合理的处理。

- 特征工程:EDA可以帮助我们分析数据中的特征,进而选择出最重要的特征,为后续的机器学习模型建立提供指导。

eda教程

eda教程EDA(探索性数据分析)是一种用于分析和理解数据的方法,它可以帮助我们发现数据集中的模式、异常和隐藏信息。

本文将为您介绍EDA的基本步骤和常用技术,并提供一些实用的Python代码示例。

EDA的基本步骤包括:数据收集、数据清洗、数据可视化和数据分析。

数据收集:首先,您需要收集与您感兴趣的主题相关的数据。

数据可以通过各种途径获取,例如从数据库、网站或API中获取。

数据清洗:在进行数据分析之前,您需要对数据进行清洗。

这包括处理缺失值、异常值、重复值和不一致的数据。

您可以使用Python的pandas库来快速处理这些任务。

数据可视化:数据可视化是EDA中重要的一环,它帮助我们更好地理解数据。

您可以使用Python中的matplotlib和seaborn库来创建各种图表,例如柱状图、散点图、箱线图和饼图,以展示数据的分布情况、相关性和异常值等。

数据分析:在数据清洗和可视化之后,您可以使用各种统计方法和机器学习算法对数据进行分析。

例如,您可以计算数据的统计指标(如均值、中位数和标准差),并使用t检验或方差分析等方法比较不同组之间的差异。

以下是一些常用的EDA技术和示例代码:1. 描述性统计分析:描述性统计分析可以帮助我们了解数据的基本特征。

例如,您可以计算数据的均值、中位数、标准差和四分位数,并使用Python的pandas库来实现。

示例代码如下:```pythonimport pandas as pd# 读取数据data = pd.read_csv('data.csv')# 计算均值mean = data.mean()# 计算中位数median = data.median()# 计算标准差std = data.std()# 计算四分位数q1 = data.quantile(0.25)q3 = data.quantile(0.75)```2. 箱线图:箱线图可以帮助我们了解数据的分布情况和异常值。

EDA总结知识点

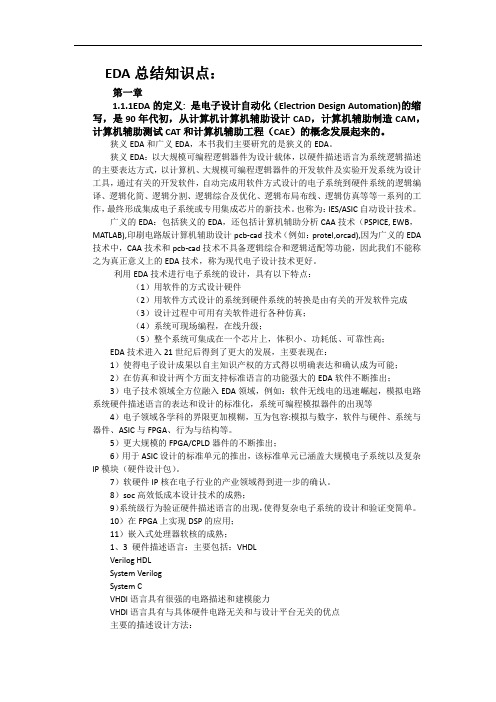

EDA总结知识点:第一章1.1.1EDA的定义: 是电子设计自动化(Electrion Design Automation)的缩写,是90年代初,从计算机计算机辅助设计CAD,计算机辅助制造CAM,计算机辅助测试CAT和计算机辅助工程(CAE)的概念发展起来的。

狭义EDA和广义EDA,本书我们主要研究的是狭义的EDA。

狭义EDA:以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真等等一系列的工作,最终形成集成电子系统或专用集成芯片的新技术。

也称为:IES/ASIC自动设计技术。

广义的EDA:包括狭义的EDA,还包括计算机辅助分析CAA技术(PSPICE, EWB,MATLAB),印刷电路版计算机辅助设计pcb-cad技术(例如:protel,orcad),因为广义的EDA 技术中,CAA技术和pcb-cad技术不具备逻辑综合和逻辑适配等功能,因此我们不能称之为真正意义上的EDA技术,称为现代电子设计技术更好。

利用EDA技术进行电子系统的设计,具有以下特点:(1)用软件的方式设计硬件(2)用软件方式设计的系统到硬件系统的转换是由有关的开发软件完成(3)设计过程中可用有关软件进行各种仿真;(4)系统可现场编程,在线升级;(5)整个系统可集成在一个芯片上,体积小、功耗低、可靠性高;EDA技术进入21世纪后得到了更大的发展,主要表现在:1)使得电子设计成果以自主知识产权的方式得以明确表达和确认成为可能;2)在仿真和设计两个方面支持标准语言的功能强大的EDA软件不断推出;3)电子技术领域全方位融入EDA领域,例如:软件无线电的迅速崛起,模拟电路系统硬件描述语言的表达和设计的标准化,系统可编程模拟器件的出现等4)电子领域各学科的界限更加模糊,互为包容:模拟与数字,软件与硬件、系统与器件、ASIC与FPGA、行为与结构等。

eda技术原理

eda技术原理EDA(Electronic Design Automation,电子设计自动化)技术是现代电子设计中不可或缺的一部分。

它是利用计算机和相关软件工具来辅助电子设计工程师完成各种电路设计、验证和优化的过程。

EDA技术的原理主要包括电路建模、逻辑综合、布局布线和仿真验证等方面。

电路建模是EDA技术的基础。

在电子设计中,我们需要将实际的电路抽象成数学模型,以方便计算机进行处理。

电路建模的原理是基于电路分析和网络理论,通过建立电路的元件模型和连接关系,将电路转化为电路方程或者矩阵方程。

这样,我们就可以利用计算机进行电路分析和计算。

逻辑综合是EDA技术的关键环节。

逻辑综合的原理是将高级语言描述的电路设计转化为门级网表,即将电路设计转化为由与门、或门、非门等基本逻辑门构成的逻辑电路。

逻辑综合的过程包括寻找最优的门级实现方式、优化电路的时序性能和面积等方面。

通过逻辑综合,我们可以将电路设计转化为计算机可以理解和处理的形式。

然后,布局布线是EDA技术的重要环节。

布局布线的原理是根据电路设计的要求和约束,将逻辑电路中的门、触发器、连线等元件进行优化和排布。

布局布线的目标是提高电路的性能和可靠性,减小电路的功耗和面积。

通过布局布线,我们可以将逻辑电路转化为物理电路,为后续的制造和生产提供便利。

仿真验证是EDA技术的最终环节。

仿真验证的原理是通过模拟电路的行为,验证电路设计的正确性和性能。

仿真验证可以分为功能仿真、时序仿真和功耗仿真等方面。

通过仿真验证,我们可以检测和调试电路设计中的错误和缺陷,保证电路设计的正确性和可靠性。

EDA技术的原理虽然复杂,但是在实际应用中却极大地提高了电子设计的效率和质量。

它不仅可以帮助电子设计工程师快速完成设计任务,还可以优化电路的性能和可靠性。

同时,EDA技术也为电子设计提供了可靠的仿真和验证手段,减少了电路设计中的错误和风险。

EDA技术的原理包括电路建模、逻辑综合、布局布线和仿真验证等方面。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

行为级建模

行为级建模

⑷ forever 循环

永久循环,执行无限的循环直到遇到系统任务 $finish

如果需要从 forever 循环中退出,可以使用 disable 语句 通常forever循环和时序控制结构结合使用

行为级建模

顺序块和并行块

块语句的作用? ቤተ መጻሕፍቲ ባይዱ为级块语句的两种类型:顺序块和并行块

① 常规延迟控制

常规延迟控制位于赋值语句的左边,用于指定一个非零延迟值

延迟的是整个赋值语 句的进行

行为级建模

② 常规延迟控制

将延迟嵌入到赋值语句中,放在赋值符的右边

将表达式的值保存在临时变量中, 然后使用常规延迟控制赋值

行为级建模

③ 零延迟控制

零延迟控制可以保证带零延迟控制的语句将在执行时刻相同的多条语句 中最后执行,从而避免发生竞争。 但如果存在多条带有零延迟的语句,它们之间的执行顺序不确定的。

行为级建模

⑵ 条件生成语句

类似if-else-if的生成构造,可以在设计模块中依据表达式值的真假,决 定是否调用以下Verilog结构:

怎样修改?

行为级建模

使用阻塞赋值来达到非阻塞赋值的目的(修改前页)

(阻塞、非阻塞对比)

阻塞与非阻塞赋值语句行为差别举例1

module non_block1; 输出结果: reg a, b, c, d, e, f; 0 a= x b= x c= x d= x e= x f = x initial begin // blocking assignments a = #10 1; // 2 a= x b= x c= x d= x e= 0 f = x b = #2 0; // 4 a= x b= x c= x d= x e= 0 f = 1 c = #4 1; // end 10 a= 1 b= x c= x d= 1 e= 0 f = 1 initial begin // non- blocking assignments 12 a= 1 b= 0 c= x d= 1 e= 0 f = 1 d <= #10 1; // e <= #2 0; // 16 a= 1 b= 0 c= 1 d= 1 e= 0 f = 1 f <= #4 1; // end initial begin $monitor($ time,," a= %b b= %b c= %b d= %b e= %b f= %b", a, b, c, d, e, f); #100 $finish; end endmodule

行为级建模

行为级建模

生成块

行为级建模

生成实例可以是以下的一种或多种类型: 模块 用户自定义原语

门级原语

连续赋值语句 initial块和always块

行为级建模

分析:

程序是否正确?有哪些改进?

中间的for循环是否能被调用?为什么?

行为级建模

⑴ 循环生成语句

允许使用者对下面的模块或模块项进行多次实例引用:

行为级建模

时序控制

行为级建模

⑴ 基于延迟的时序控制

基于延迟的时序控制出现在表达式中,它指定了语句开始执行到执行 完成之间的时间间隔 延迟字可以是数字、标示符或表达式,需要在延迟前加关键字“#”

对于过程赋值,Verilog提供了三种类型的延迟控制:常规延迟控制、 赋值内嵌延迟控制和零延迟控制

行为级建模

在实际设计中,尽量 不要使用零延迟控制

行为级建模

⑵ 基于事件的时序控制

事件:指某个寄存器或线网变量的值发生了变化。 事件可以用来触发声明语句或块语句的执行。 4种类型的事件控制:常规事件控制、命名事件控制、OR(或)事件控 制和电平敏感时序控制 ① 常规事件控制 使用符号@来标明,语句继续执行的条件是信号发生变化、正跳 变或负跳变 posedge用于指明正向跳变,negedge用于指明负向跳变

行为级建模

② 命名事件控制 用户在程序中声明 event(事件)类型变量,触发该变量,并识别 该事件是否已经发生 命名事件由关键字event声明,不能保存任何值 时间的触发用符号->表示;判断事件是否发生用@来识别

行为级建模

③ OR事件控制 多个信号或事件中发生的任意一个变化,都能够触发语句或语句块 的执行

行为级建模

设计复杂程度的不断提高 设计早期进行良好的整体规划 整体结构评估,建立在硬件所完成的算法之上 设计者从算法角度,即电路外部行为的角度进行描述 行为级建模:从一个很高的抽象角度来表示电路

行为级建模

行为级建模

结构化过程语句

两种结构化的过程语句:initial语句和 always语句,它们是行为级建模 的两种基本语句。 其他所有行为语句只能出现在这两种结构化过程语句里。 Verilog本质上是并发而非顺序的,每个语句代表一个独立的执行过程, 每个执行过程从仿真时间0开始,并且这两种语句不能嵌套使用

行为级建模

⑴ 顺序块

行为级建模

⑵ 并行块

行为级建模

并行块为我们提供了并行执行语句的机制,但如果两条语句在同一时 刻对同一变量影响,则会引起隐含的竞争这种情况要避免

行为级建模

块语句的三个特点:嵌套块、命名块和命名块的禁用

① 嵌套块 块可以嵌套使用,顺序块和并行块能够混合在一起使用

行为级建模

② 命名块

变量声明

模块 用户自定义原语、门级原语

连续赋值语句

initial块和always块

行为级建模

行为级建模

关键字generate-endgenerate来指定生成块的范围 仿真开始,先将生成块中的代码展平 关键词genvar用于声明生成变量,只能用在生成块中,确立后的仿真 代码中不存在 生成变量的值只能由循环生成语句来改变 循环生成语句可以嵌套,但是用同个生成变量作为索引的循环生成语句 不能相互嵌套 层次化引用xor_loop[0].g1, xor_loop[1].g1,……,xor_loop[31].g1

行为级建模

无限循环? 停止原因?

行为级建模

过程赋值语句

过程赋值语句的更新对象是寄存器、整数、实数或时间变量。这些类型 的变量被赋值后,其值将保持不变,直到被其它赋值语句赋予新值。过 程赋值语句只有在执行到的时候才起作用。

左侧的variable_lvalue可以是以下类型:

寄存器、整型数、实型数、时间存储器变量或存储器单元

行为级建模

行为级建模

行为级建模

⑵ for 循环

注: while循环比for循环更通用,并不是所有情况下都能用for循环代替 while循环

行为级建模

for循环一般用于具有固定开始和结束条件的循环;如果只有一个执 行循环的条件,最好用while

行为级建模

⑶ repeat 循环

repeat循环的功能是执行固定次数的循环 循环的次数必须是一个常量、一个变量或一个信号 如果循环次数是变量或信号,取循环开始执行时变量或信号的值, 而不是循环执行期间的值

(阻塞、非阻塞对比)

阻塞与非阻塞赋值语句行为差别举例2

module pipeMult(product, mPlier, mCand, go, clock); input go, clock; input [7:0] mPlier, mCand; output [15:0] product; reg [15:0] product; always @(posedge go) product = repeat (4) @(posedge clock) mPlier * mCand; endmodule module pipeMult(product, mPlier, mCand, go, clock); input go, clock; input [7:0] mPlier, mCand; output [15:0] product; reg [15:0] product; always @(posedge go) product <= repeat (4) @(posedge clock) mPlier * mCand; endmodule

(阻塞、非阻塞对比)

阻塞与非阻塞赋值语句行为差别举例2波形

非阻塞

非阻塞

(阻塞、非阻塞对比)

(阻塞、非阻塞对比)

非阻塞语句并行执行,因此临时变量不可避免的在一个周期中被赋值, 在下一个周期中被采样

请见下页实例

(阻塞、非阻塞对比)

(阻塞、非阻塞对比)

(阻塞、非阻塞对比)

阻塞赋值or非阻塞赋值?

上述类型的位选/域选 (如,address[0], address[0:7]) 上述类型的拼接

包括两种类型:阻塞赋值和非阻塞赋值

行为级建模

⑴ 阻塞赋值语句“=”

串行块中的阻塞赋值语句按顺序执行,它不会阻塞其后并行块中语句的执行。

行为级建模

若赋值两端位宽不等,则: 1.如果右侧较宽,则保留从最 低位开始的右侧值,把超过左 侧位宽的高位丢弃 2.如果左侧位宽较宽,则不足 的高位补0

行为级建模

行为级建模

选择信号中有不确定值x,则输出为x 选择信号中有高阻值z,则输出为z 选择信号中一位为x,另外一位为z,则x的优先级高

行为级建模

casex 和 casez 关键字

casez语句将条件表达式或候选项表达式中的z作为无关值,所有值为 z的位也可以用“?”表示 casex语句将条件表达式或候选项表达式中的x作为无关值

行为级建模

循环语句

循环语句的四种类型:while,for,repeat 和 forever 循环语句只能在 always 或 initial 块中使用,循环语句可以 包含延迟表达式 ⑴ while 循环 表达式的值为假,循环停止