数字逻辑总复习

数字逻辑电路总复习

128

16

4 2 1

二、常用逻辑关系及运算

1. 三种基本逻辑运算:与 、或、非 2. 四种复合逻辑运算: 与非 、或非、与或非、异或 真值表 函数式 逻辑符号

三、逻辑代数的公式和定理

是推演、变换和化简逻辑函数的依据,有些与普通代数相 同,有些则完全不同,要认真加以区别。这些定理中,摩根定 理最为常用。

第一章 逻辑代数基础

一、数制和码制 1. 数制:计数方法或计数体制(由基数和位权组成)

种类 十进制

二进制 八进制

基数 09

0 ,1 07

位权 10i

2i 8i

应用 日常

数字电路 计算机程序

备注

2 = 21 8 = 23

十六进制 0 9,A F

16i

计算机程序

16 = 24

各种数制之间的相互转换,特别是十进制→二进制的转换, 要求熟练掌握。

逻辑代数的基本公式 1. 关于常量与变量关系公式

A 0 A (1) A1 A (1’) A 1 1 (2) A 0 0 (2’)

2. 若干定律 交换律:

A B B A (3) A B B A (3’)

( A B) C A ( B C )

2. 码制:常用的 BCD 码有 8421 码、2421 码、5421 码、余 3 码等,其中以 8421 码使用最广泛。

1.十进制数到N进制数的转换 整数部分:除以N看余数 小数部分:乘以N看向整数的进位 2. N进制数转换为十进制数:方法:按权展开 3.基本逻辑和复合逻辑: (1)异或逻辑:特点:相同为0、相异为1 逻辑函数表达式:P = AB=AB+AB (2)同或逻辑:特点:相同为1、相异为0 逻辑函数表达式:P = A⊙ B =AB+AB 异或逻辑与同或逻辑是互非关系:

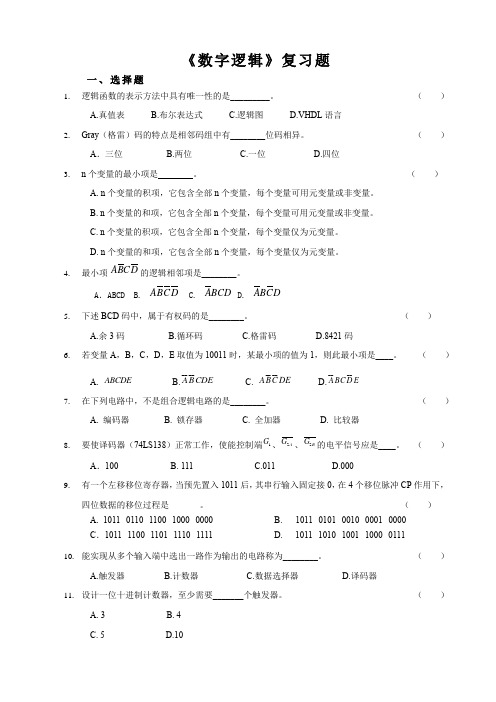

《数字逻辑》复习题

《数字逻辑》复习题一、选择题1.逻辑函数的表示方法中具有唯一性的是_________。

( )A.真值表B.布尔表达式C.逻辑图D.VHDL 语言2.Gray (格雷)码的特点是相邻码组中有________位码相异。

( )A .三位 B.两位 C.一位 D.四位3.n 个变量的最小项是 。

( ) A. n 个变量的积项,它包含全部n 个变量,每个变量可用元变量或非变量。

B. n 个变量的和项,它包含全部n 个变量,每个变量可用元变量或非变量。

C. n 个变量的积项,它包含全部n 个变量,每个变量仅为元变量。

D. n 个变量的和项,它包含全部n 个变量,每个变量仅为元变量。

4.最小项的逻辑相邻项是________。

A .ABCD B. C. D.5. 下述BCD 码中,属于有权码的是________。

( )A.余3码B.循环码C.格雷码D.8421码6.若变量A ,B ,C ,D ,E 取值为10011时,某最小项的值为1,则此最小项是____。

( ) A. B. C. D.7. 在下列电路中,不是组合逻辑电路的是________。

( )A. 编码器B. 锁存器C. 全加器D. 比较器8.要使译码器(74LS138)正常工作,使能控制端、、的电平信号应是____。

( ) A .100 B. 111 C.011 D.0009. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是 。

( ) A.1011--0110--1100--1000--0000 B. 1011--0101--0010--0001--0000 C .1011--1100--1101--1110--1111 D.1011--1010--1001--1000--011110. 能实现从多个输入端中选出一路作为输出的电路称为________。

( )A.触发器B.计数器C.数据选择器D.译码器11. 设计一位十进制计数器,至少需要_______个触发器。

数字逻辑总复习[7]课件

![数字逻辑总复习[7]课件](https://img.taocdn.com/s3/m/f7b37521b42acfc789eb172ded630b1c59ee9bc7.png)

F M 4 ( 0 ,2 ,7 ,8 ,10 ,12 ,14 ,15 )

已知 F(A,B,C)ABA C BC

则 F m 3( 0,7

) M 3(1,2,3,4,5,6 )

F m 3(1,2,3,4,5,6 ) M 3( 0,7

)

知识点: 含有无关项的逻辑函数化简。

F ( A , B ,C , D ) ( A B C D )( A B C D )( A B C D )

●填卡诺图

由下列表达式,你能想到什么?

F m 4 ( 0 ,2 ,7 ,8 ,10 ,12 ,14 ,15 )

(11)反函数的最小项表达式 F m 4 ( 1 ,3 ,4 ,5 ,6 ,9 ,11,13 )

练习2:设计一个一位全加器,能将两个一位二进制数以及 来自低位的“进位”进行相加,并产生“和”及“进位”

知识点5:

竞争和冒险

竞争:由于延迟时间的影响,使得输入信号经过不同 路径到达输出端的时间有先有后,这一现象称为竞争。

险象:由竞争导至的错误输出信号。

注意!组合电路中的险象是一种瞬态现象,它表现为 在输出端产生不应有的尖脉冲,暂时地破坏正常逻辑关系。 一旦瞬态过程结束,即可恢复正常逻辑关系。.

八进制

按位权展开求和

? 十六进制

例1:完成下列数制转换。

(127.25)10 = ( 1111111.01 )2 = ( 177.2 )8 = ( 7F.4 )16

整数

小数:?

基2乘

(88.375)10 = ( 1011000.011 )2

( 237 )8

借助二进制 ( 010 011 111 )2

F ( ( A B )D • C )( B D ) F' ( ( A B )D • C )( B D )

数字逻辑知识点总结复习进程

1、三极管的截止条件是V BE <0.5V ,截止的特点是I b =I c ≈0;饱和条件是 I b ≥(E C -Vces )/(β·R C ),饱和的特点是V BE ≈0.7V ,V CE =V CES ≤0.3V 。

2、逻辑常量运算公式3、逻辑变量、常量运算公式4、 逻辑代数的基本定律根据逻辑变量和逻辑运算的基本定义,可得出逻辑代数的基本定律。

①互非定律: A+A = l ,A • A = 0 ;1=+A A ,0=•A A ; ②重叠定律(同一定律):A • A=A , A+A=A ;③反演定律(摩根定律):A • B=A+B 9 A+B=A • B B A B A •=+,B A B A +=•; ④还原定律: A A =ch2.1、三种基本逻辑是与、或、非。

2、三态输出门的输出端可以出现高电平、底电平和高阻三种状态。

1、组合电路的特点:电路任意时刻输出状态只取决于该时刻的输入状态,而与该时刻前的电路状态无关。

2、编码器:实现编码的数字电路3、译码器:实现译码的逻辑电路4、数据分配器:在数据传输过程中,将某一路数据分配到不同的数据通道上。

5、数据选择器:逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。

6、半加器:只考虑两个一位二进制数相加,而不考虑低位进位的运算电路。

7、全加器:实现两个一位二进制数相加的同时,再加上来自低位的进位信号。

8、在数字设备中,数据的传输是大量的,且传输的数据都是由若干位二进制代码0和1组合而成的。

9、奇偶校验电路:能自动检验数据信息传送过程中是否出现误传的逻辑电路。

10、竞争:逻辑门的两个输入信号从不同电平同时向相反电平跳变的现象。

11、公式简化时常用的的基本公式和常用公式有(要记住): 1)()()C A B A BC A ++=+2)B A AB += B A B A +=+ (德.摩根定律) 3)B A B A A +=+4)B A AB BC B A AB +=++5)AB B A B A B A +=+ B A B A AB B A +=+12、逻辑代数的四种表示方法是真值表、函数表达式、卡诺图和逻辑图。

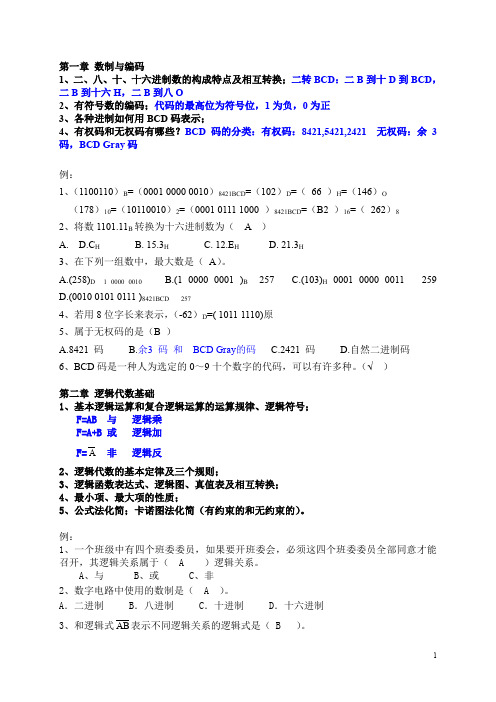

(完整word版)数字逻辑期末复习资料

第一章数制与编码1、二、八、十、十六进制数的构成特点及相互转换;二转BCD:二B到十D到BCD,二B到十六H,二B到八O2、有符号数的编码;代码的最高位为符号位,1为负,0为正3、各种进制如何用BCD码表示;4、有权码和无权码有哪些?BCD码的分类:有权码:8421,5421,2421 无权码:余3码,BCD Gray码例:1、(1100110)B=(0001 0000 0010)8421BCD=(102)D=(66 )H=(146)O(178)10=(10110010)2=(0001 0111 1000 )8421BCD=(B2 )16=(262)82、将数1101.11B转换为十六进制数为( A )A. D.C HB. 15.3HC. 12.E HD. 21.3H3、在下列一组数中,最大数是(A)。

A.(258)D 1 0000 0010B.(1 0000 0001 )B257C.(103)H0001 0000 0011 259D.(0010 0101 0111 )8421BCD 2574、若用8位字长来表示,(-62)D=( 1011 1110)原5、属于无权码的是(B )A.8421 码B.余3 码和BCD Gray的码C.2421 码D.自然二进制码6、BCD码是一种人为选定的0~9十个数字的代码,可以有许多种。

(√)第二章逻辑代数基础1、基本逻辑运算和复合逻辑运算的运算规律、逻辑符号;F=AB 与逻辑乘F=A+B 或逻辑加F=A非逻辑反2、逻辑代数的基本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简(有约束的和无约束的)。

例:1、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于( A )逻辑关系。

A、与B、或C、非2、数字电路中使用的数制是( A )。

A.二进制B.八进制 C.十进制D.十六进制3、和逻辑式AB表示不同逻辑关系的逻辑式是( B )。

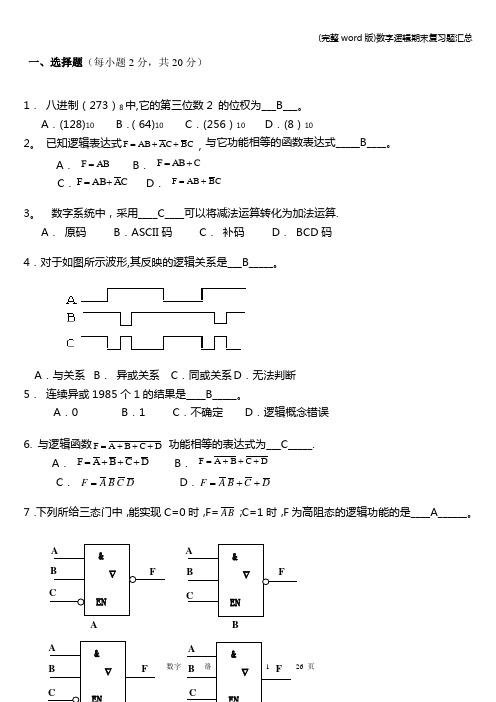

(完整word版)数字逻辑期末复习题汇总

一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10 C .(256)10 D .(8)10 2。

已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。

A .AB F = B .C AB F +=C .C A AB F +=D . C B AB F +=3。

数字系统中,采用____C____可以将减法运算转化为加法运算.A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断 5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6. 与逻辑函数D C B A F +++= 功能相等的表达式为___C_____.A . D CB A F +++= B .D C B A F +++=C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。

8。

如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。

A . 500KHzB .200KHzC . 100KHzD .50KHz9.下列器件中,属于时序部件的是_____A_____。

A . 计数器B . 译码器C . 加法器D .多路选择器10.下图是共阴极七段LED 数码管显示译码器框图,若要显示字符“5",则译码器输出a ~g 应为____C______.A . 0100100B .1100011C . 1011011D .0011011二、填空题(每小题2分,共20分)11。

TTL电路的电源是__5__V ,高电平1对应的电压范围是__2.4-5____V.12。

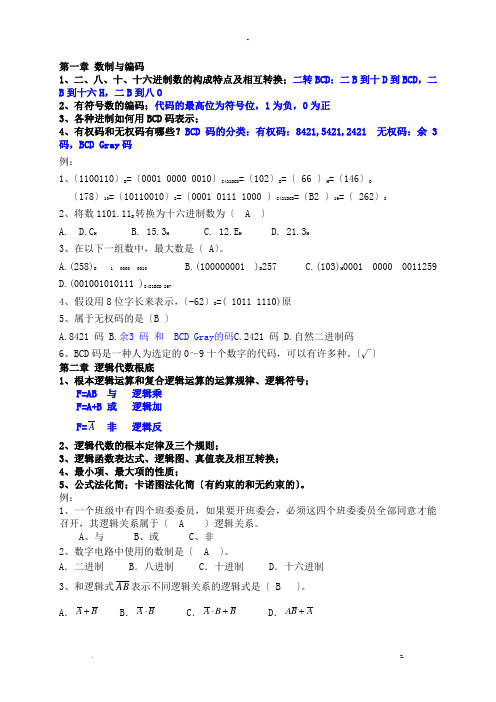

数字逻辑期末复习资料

第一章 数制与编码1、二、八、十、十六进制数的构成特点及相互转换;二转BCD :二B 到十D 到BCD ,二B 到十六H ,二B 到八O2、有符号数的编码;代码的最高位为符号位,1为负,0为正3、各种进制如何用BCD 码表示;4、有权码和无权码有哪些?BCD 码的分类:有权码:8421,5421,2421 无权码:余3码,BCD Gray 码 例:1、〔1100110〕B =〔0001 0000 0010〕8421BCD =〔102〕D =〔 66 〕H =〔146〕O〔178〕10=〔10110010〕2=〔0001 0111 1000 〕8421BCD =〔B2 〕16=〔 262〕8 2、将数1101.11B 转换为十六进制数为〔 A 〕A. D.C HB. 15.3HC. 12.E HD. 21.3H 3、在以下一组数中,最大数是〔 A 〕。

A.(258)D1 0000 0010B.(100000001 )B 257C.(103)H 0001 0000 0011259D.(001001010111 )8421BCD 2574、假设用8位字长来表示,〔-62〕D =( 1011 1110)原5、属于无权码的是〔B 〕A.8421 码B.余3 码 和 BCD Gray 的码C.2421 码D.自然二进制码 6、BCD 码是一种人为选定的0~9十个数字的代码,可以有许多种。

〔√〕 第二章 逻辑代数根底1、根本逻辑运算和复合逻辑运算的运算规律、逻辑符号;F=AB 与 逻辑乘 F=A+B 或 逻辑加F=A 非 逻辑反2、逻辑代数的根本定律及三个规则;3、逻辑函数表达式、逻辑图、真值表及相互转换;4、最小项、最大项的性质;5、公式法化简;卡诺图法化简〔有约束的和无约束的〕。

例:1、一个班级中有四个班委委员,如果要开班委会,必须这四个班委委员全部同意才能召开,其逻辑关系属于〔 A 〕逻辑关系。

A 、与B 、或C 、非 2、数字电路中使用的数制是〔 A 〕。

数字逻辑总复习

数。 激励表又称驱动表。它表明触发器由现态转换到次态, 对其输入状态的要求。 状态图是状态转换图的简称。它用圆圈和箭头表示时 序逻辑状态及其转换关系。 状态表是状态转换表的简称。状态表和状态图在表示 时序电路逻辑的实质是一样的,只是形式不同。 波形图即是按照时间的变化,画出反映时钟脉冲、输 入信号、触发器状态之间对应关系的波形。

VHDL基本结构

实体(Entity)声明

结构体(Architecture)

VHDL语法

数据类型

逻辑运算 关系运算

算术运算

赋值 语句 进程 组件、过程、函数

例1:VHDL

例2:VHDL

例3:状态机设计

例3:状态机设计(续)

逻辑设计流程( Quartus II )

到的状态称为次态,用Qn+1表示。

RS触发器

S

SET

Q

R

CLR

Q

D触发器

D

SET

Q

CLR

Q

Qn+1 = D

JK触发器

J

SET

Q

K

CLR

Q

例:触发器

试画出各触发器

Q端在初态为0 及1两种条件下 的波形。

例:触发器(续)

解:

同步时序逻辑逻辑描述方法

特性函数就是次态Qn+1的逻辑表达式,也称为次态函

新建项目

新建设计文件 设计输入

编译、引脚配置

仿真 下载

例:组合逻辑分析

分析如图(a)所示的逻辑电路。

解:

1.根据给出的逻辑电路图可写出输出函数表达

式

S AB A AB B

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A B A B

A B A B

AB AC BC AB AC

A AB A B

(19) AB AC A B A C

同或和异或

(18) AB AB A B AB

最小项的性质?

卡诺图的特点:

用几何相邻表示逻辑相邻 相接 — 紧挨着 相对 — 行或列的两头 相重 — 对折起来位置重合

VCC YS 16 15 YEX I3 14 13 I2 12 I1 11 I0 Y0 10 9 Y2 Y1 Y0 6 7 9 YS 15 YEX 14

主要包括二进制编码器、二 – 十进制编码 器和优先编码器等。

74LS148 1 2 3 4 5 6 7 8 5 4 3

74LS148 2 1 13 12 11 10

四、常用中规模集成组合逻辑电路

1. 加法器:实现两组多位二进制数相加的电路。 根据进位方式不同,可分为串行进位加法 器和超前进位加法器。

集成芯片: 74LS183(TTL)、C661(CMOS)— 双全加器 两片双全加器(如74LS183) 四位串行进位加法器 74283、74LS283(TTL) CC4008(CMOS) — 四位二进制超前进位加法器

两个最小项只有一个变量不同

(1) 几何相邻:

(2) 逻辑相邻:

卡诺图的合并规律?

用卡诺图化简逻辑函数的方法

画包围圈的原则:

不正确 的画圈

CD (1) 先圈孤立项,再圈仅有一 AB 00 01 11 10 种合并方式的最小项。 1 1 00 (2) 圈越大越好,但圈的个数 01 1 1 越少越好。 11 1 1 (3) 最小项可重复被圈,但每 个圈中至少有一个新的最小项。

2. 数值比较器:比较两组多位二进制数大小的电路。

集成芯片: 7485、74L 85(TTL) CC14585、C663(CMOS) — 四位数值比较器

3. 编码器:将输入的电平信号编成二进制代码的电路。

集成芯片: 74148、74LS148、74LS348(TTL)— 8 线 – 3 线优先编码器 74147、74LS147(TTL)— 10 线 – 4 线优先编码器

同步 D 触发器

Q

n1

D

(3)边沿触发器:时钟边沿控制。

CP上升沿(或下降沿)时刻有效

特性方程

Q n1 D

Q n 1 JQ n K Q n

边沿 D 触发器 边沿 JK 触发器

2. 根据逻辑功能不同,边沿触发器可分为 (1)JK 触发器 (2)D 触发器 (3)T 触发器

Q n 1 JQ n K Q n

二、时序电路逻辑功能的表示方法 逻辑图、逻辑表达式、状态表、卡诺图、 状态转换图(简称状态图)和时序图

三、时序电路的基本分析方法

实质: 逻辑图

状态图

关键: 求出状态方程,列出状态表,根据状态表画 出状态图和时序图,由此可分析出时序逻辑 电路的功能。 四、时序电路的基本分设计方法 实质: 状态图 逻辑图

触发器的相关概念

一、触发器和门电路一样,也是组成数字电路的基 本逻辑单元。它有两个基本特性:

1. 有两个稳定的状态(0 状态和 1 状态)。 2. 在外信号作用下,两个稳定状态可相互转换;没 有外信号作用时,保持原状态不变。

因此,触发器具有记忆功能,常用来保存二进制信息。

二、触发器的逻辑功能 指触发器输出的次态 Qn+1 与输出的现态 Qn 及输入 信号之间的逻辑关系。触发器逻辑功能的描述方法主要 有特性表、卡诺图、特性方程、状态转换图和波形图 (时序图)。

拉电流负载、灌电流负载、扇出系数、 开门电阻、关门电阻、输入端短路电流、 噪声容限、传输延迟时间等;

TTL和CMOS集成门电路对比各有什么特点?

A B CA BCຫໍສະໝຸດ 例UCCR F

A B 1

&

题

“异或”门

1 F

D

R

3V

ui 5 sin t(V )

uo

电路的输出表达式?

等同于什么门?

输出电压的最小值? 3V

5. 数据选择器: 在地址码的控制下,在同一时间内从 多路输入信号中选择相应的一路信号 输出的电路。常用于数据传输中的并集成芯片: 串转换。

74153、74LS153 — 4选 1 数据选择器 74151、74LS151(TTL)— 8 选 1 数据选择器

Y D0 A1 A0 D1 A1 A0 D2 A1 A0 D3 A1 A0

关键: 根据设计要求求出最简状态表(图),再通 过卡诺图求出状态方程和驱动方程,由此画 出逻辑图。

五、计数器 记录输入脉冲 CP 个数的电路,是极具典型性和代 表性的时序逻辑电路。 1. 按计数进制分: 二进制计数器、十进制计数器和任意进制计数器 2. 按计数增减分: 加法计数器、减法计数器和可逆(加/减)计数器 3. 按触发器翻转是否同步分: 同步计数器和异步计数器

集成芯片: 74LS138(TTL)— 3线 – 8线译码器(二进制译码器)

Y0 A2 A1 A0 m0

Y7 A2 A1 A0 m7

7442、74LS42(TTL)— 4线 – 10线译码器 74247、74LS247(TTL)— 共阳极显示译码器 7448、74248、7449、74249等(TTL)— 共阴极显示译码器

10 1 1

(4) 必需把组成函数的全部最小项圈完,并做认真 比较、检查才能写出最简与或式。

具有约束的逻辑函数的化简 一、 约束的概念和约束条件

二、化简步骤:

(1) 画函数的卡诺图,顺序为: 先填 1

╳

0

(2) 合并最小项,画圈时 ╳ 既可以当 1 ,又 可以当 0 (3) 写出最简与或表达式 注意: 合并时,究竟把 ╳ 作为 1 还是作为 0 应以得到 的包围圈最大且个数最少为原则。包围圈内都 是约束项无意义。

第五章 时序逻辑电路

主要知识点: 0501 0502 0503 0504 0505 0506 0507 0508 时序逻辑电路的基本定义、概念 时序逻辑电路的基本分析 时序逻辑电路的基本设计方法 集成二进制、十进制计数器的芯片知识 应用集成二进制计数器的设计N进制计数器(综合) 应用集成十进制计数器的设计N进制计数器(综合) 寄存器的基础知识 寄存器的应用(顺序脉冲发生器)(综合) 题量:判断题3题,选择题 8题

A B

三极管作为开关时工作区域是?

&

50 Ω

C

Y1

饱和区+截止区

C

第三章 组合逻辑电路

主要知识点: 题量:判断题 4题,选择题 10题 0301 组合逻辑电路的基本定义、概念

0302 组合逻辑电路的基本分析方法

0303 组合逻辑电路的基本设计方法 0304 集成优先编码器的工作原理和应用 0305 集成二进制译码器的电路特点 0306 集成二进制译码器的应用(综合) 0307 集成数据选择器的芯片特点和应用(综合) 0308 其他典型组合逻辑电路的集成电路及其应用(综合)

第二章 门电路

主要知识点: 0201 分立元件门电路基础知识(二极管门电路) 0202 分立元件门电路基础知识(三极管门电路)

0203 集成门电路基础知识(TTL集成门电路常识)

0204 集成门电路基础知识(CMOS集成门电路常识)

题量:判断题 2题,选择题 4题

掌握 CMOS 和 TTL 集成门电路的一些重要概念

&

1

D0 D1 D2 D3 LD

1

1

判断下图是多少进制的计数器

Q0 Q1 Q 2 Q 3 Q 4 Q5 Q6 Q7

1

CP

CTT

《数电》的主要内容

第一章、逻辑代数 第二章、门电路

第三章、组合逻辑电路

第四章、触发器 第五章、时序逻辑电路

第一章 逻辑代数

主要知识点: 0101 逻辑代数的基本概念(数的进制和基本逻辑运算的定义) 0102 逻辑代数中常量和变量的基本运算法则 0103 逻辑代数的基本公式和定理(主要是考察其与普通代数不相 同的特点) 题量:判断题 3题,选择题 8题

逻辑函数的表示方法

逻辑表达式

真值表

卡诺图

逻辑图

波形图

各自的优点?缺点?

逻辑函数

相互之间的转换方法?

F = A B+C + AD 的反函数的最简与或式为:

A B

& C & &

F = AB+ AC + AD

Y

F ( A, B, C) AB BC

F ACD C D ABC

Y BC C

0104 简单逻辑函数的公式法化简

0105 逻辑函数的公式法化简(摩根定理的应用)

0106 复杂逻辑函数的公式法化简(综合) 0107 逻辑函数的图形法化简 0108 带约束项的逻辑函数的图形法化简(综合)

常用公式

分配律

A BC ( A B) ( A C )

德 摩根定理 冗余定理 特殊公式

组合逻辑电路的概念

一、组合逻辑电路的特点 组合逻辑电路是由各种门电路组成的没有记忆功 能的电路。它的特点是任一时刻的输出信号只取决于 该时刻的输入信号,而与电路原来所处的状态无关。 二、组合逻辑电路的分析方法

逻辑图 逻辑表达式 化简 真值表 说明功能

三、组合逻辑电路的设计方法

逻辑抽象 列真值表 写表达式 化简或变换 画逻辑图

A1 A0

Y 4选1

S

D3 D 2 D1 D0

F1 BD BC

F2 AB AC

第四章 触发器

主要知识点:

0401 RS触发器的基础知识(基本电路形式和工作原理)

0402 边沿D触发器基础知识(逻辑功能定义和特点) 0403 边沿JK触发器基础知识(逻辑功能定义和特点) 0404 边沿D和JK触发器与其他触发器的转换方法 0405 集成边沿触发器的应用(画时序图)(综合) 题量:判断题 3题,选择题 5题