完整word版,09 南京信息工程大学计算机组成原理试卷A答案

南京信息工程大学计算机组成原理试题

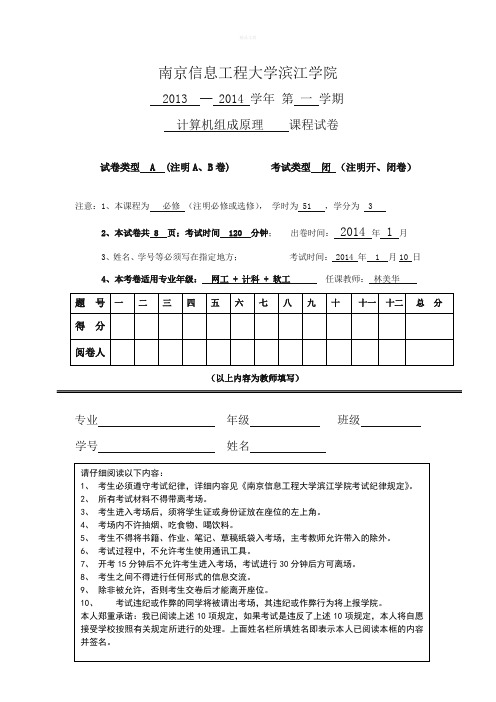

南京信息工程大学滨江学院2013 ─ 2014 学年第一学期计算机组成原理课程试卷试卷类型 A (注明A、B卷) 考试类型闭(注明开、闭卷)注意:1、本课程为必修(注明必修或选修),学时为 51 ,学分为 32、本试卷共 8 页;考试时间 120 分钟;出卷时间: 2014 年 1 月3、姓名、学号等必须写在指定地方;考试时间: 2014 年 1 月10 日4、本考卷适用专业年级:网工 + 计科 + 软工任课教师:林美华题号一二三四五六七八九十十一十二总分得分阅卷人(以上内容为教师填写)专业年级班级学号姓名请仔细阅读以下内容:1、考生必须遵守考试纪律,详细内容见《南京信息工程大学滨江学院考试纪律规定》。

2、所有考试材料不得带离考场。

3、考生进入考场后,须将学生证或身份证放在座位的左上角。

4、考场内不许抽烟、吃食物、喝饮料。

5、考生不得将书籍、作业、笔记、草稿纸袋入考场,主考教师允许带入的除外。

6、考试过程中,不允许考生使用通讯工具。

7、开考15分钟后不允许考生进入考场,考试进行30分钟后方可离场。

8、考生之间不得进行任何形式的信息交流。

9、除非被允许,否则考生交卷后才能离开座位。

10、考试违纪或作弊的同学将被请出考场,其违纪或作弊行为将上报学院。

本人郑重承诺:我已阅读上述10项规定,如果考试是违反了上述10项规定,本人将自愿接受学校按照有关规定所进行的处理。

上面姓名栏所填姓名即表示本人已阅读本框的内容并签名。

注意:所有答案必须写在后面的答题纸上,写在试卷部分的不予评分!一、选择题(每小题1分,共计20分)1.完整的计算机系统应包括:()A.运算器、控制器、存储器 B.外设和主机C.主机和实用程序 D.软、硬件系统2.完整的计算机硬件系统是由()组成的。

A.主机与外设 B.CPU与存储器C.ALU与控制器 D.硬件系统与软件系统3.完整的计算机硬件系统是由组成的。

A. 主机与外设B. CPU与存储器C. ALU与控制器D.硬件系统与软件系统4.若浮点数格式为1位阶符、6位阶码、1位数符、8位尾数,则浮点数所能表示的数的范围是( A )说明:(负数用2的补码表示,尾数部分没有规格化的情况也在考虑范围内。

08网工组成原理A卷答案

南京信息工程大学试卷(A)答案2009-2010学年第 2 学期计算机组成原理课程试卷(A卷) 本试卷共页;考试时间 120 分钟;任课教师马利;出卷时间 2010 年 6 月计算机与软件学院网络工程专业2008 年级1、2 班学号姓名得分一、填空题 (每空1分,共 20 分)1、规格化浮点运算一般需要进行对阶、求和、规格化、舍入、判断溢出等工作。

2、常用的刷新方式有三种,一种是集中式,另一种是分散式,第三种是异步式。

3、堆栈存取方式是面向栈顶操作的先进后出的存取方式,在自底向上生成方式工作的堆栈中,入栈时,堆栈指针作何调整?加(加/减),入栈时调整指针和存入数据的次序是:先调整指针,后存入数据。

4、实现机器指令的微程序一般存放在控制存储器中,而用户程序存放在主存储器中,前者的速度比后者快。

5、CPU常用的控制方式有三种:同步控制方式、异步控制方式和联合控制方式。

6、存储__程序____并按___地址__顺序执行,这是冯-诺依曼型计算机的工作原理。

7、对存储器的要求是容量大、速度快、成本低。

为了解决了这三方面的矛盾,计算机采用多级存储体系结构,即主存、 Cache(缓存)和外存。

二、选择题 (每小题 1分,共 10分)1、计算机中使用总线结构便于增减外设,同时A 。

A. 减少了信息传输线的条数B. 提高了信息传输速度C. 减少了信息传输量D. 三者均正确2、总线结构的主要优点是便于实现系统的模块化,其缺点是C 。

A. 传输的地址和控制信息不能同时出现B. 传输的地址和数据信息不能同时出现C. 不能同时具有两个总线主设备D. 不能同时使用多于两个总线设备3、用PLA器件设计的操作控制器称为PLA控制器。

从技术实现的途径来说,PLA控制器是一种 D 。

A. 用存储逻辑技术设计的控制器B. 用组合逻辑技术设计的控制器C. 用微程序技术设计的控制器D. 用组合逻辑技术和存储逻辑技术结合设计的控制器4、指令周期是指C 。

2022年南京信息工程大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年南京信息工程大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、关于Cache的3种基本映射方式,下面叙述中错误的是()。

A.Cache的地址映射有全相联、直接和多路组相联3种基本映射方式B.全相联映射方式,即主存单元与Cache单元随意对应,线路过于复杂,成本太高C.多路组相联映射是全相联映射和直接映射的一种折中方案,有利于提高命中率D.直接映射是全相联映射和组相联映射的一种折中方案,有利于提高命中率2、容量为64块的Cache采用组相联映射方式,字块大小为128个字,每4块为一组。

如果主存为4K块,且按字编址,那么主存地址和主存标记的位数分别为()。

A.16,6B.17,6C.18,8 D .19,83、假设机器字长为16位,用定点补码小数表示时,一个字所能表示的范围是()。

A.0~(1-2-15)B.-(1-2-15)~(1-2-15)C.-1~1D.-1~(1-2-15)4、假设在网络中传送采用偶校验码,当收到的数据位为10101010时,则可以得出结论()A.传送过程中未出错B.出现偶数位错C.出现奇数位错D.未出错或出现偶数位错5、当定点运算发生溢出时,应()。

A.向左规格化B.向右规格化C.舍入处理D.发出出错信息6、在集中式总线控制中,响应时间最快的是()。

A.链式查询B.计数器定时查询C.独立请求D.分组链式查询7、总线按连接部件不同可分为()。

A.片内总线、系统总线、通信总线B.数据总线、地址总线、控制总线C.主存总线I/O总线、DMA总线D.ISA总线、VESA总线、PCI总线8、计算机硬件能够直接执行的是()。

1.机器语言程序IⅡ.汇编语言程序Ⅲ.硬件描述语言程序入A.仅IB.仅I、ⅡC.仅I、ⅢD. I、Ⅱ 、Ⅲ9、下列关于配备32位微处理器的计算机的说法中,正确的是()。

该机器的通用寄存器一般为32位Ⅱ.该机器的地址总线宽度为32位Ⅲ.该机器能支持64位操作系统IV.一般来说,64位微处理器的性能比32位微处理器的高A.I、ⅡB.I、ⅢC.I、ⅣD.I、IⅡ、Ⅳ10、禁止中断的功能可以由()来完成。

09-南京信息工程大学计算机组成原理试卷A答案

09-南京信息工程大学计算机组成原理试卷A答案南京信息工程大学试卷2009-2010学年第 1 学期计算机组成原理课程试卷( A 卷) 本试卷共页;考试时间分钟;任课教师马利;出卷时间2009年12月学院专业年级班学号姓名得分一、填空题(每小题1分,共20分)1.在由n台计算机构成的并行计算机中,其运行程序的加速比一般都小于n,其主要原因是___ A__和__ B____。

程序中有不能并行的串行部分存在通信开销2.在计算机系统当中,根据应用条件和硬件资源的不同,数据传输方式可以采用A___传送、B __传送和C___传送三种方式。

并行串行分时3.完成浮点加法或减法时,需要进行对阶、求和、规格化和舍入等步骤,在对阶时,使 A 阶向B阶看齐,使小阶的尾数向 C 移位,每D 移一位,其阶码加1,直到两数的阶码相等为止。

小大右右4.在多级存储体系中,Cache存储器的主要功能是___A___,虚拟存储器的主要功能是__B___。

匹配CPU和主存之间的速度匹配主存和辅存之间的速度5.双端口存储器和多模块交叉存储器都属于A___存储器结构。

但是前者采用B___技术,而后者采用C___技术。

并行空间并行时间并行6.相联存储器不是按地址而是按_ A__访问的存储器,其在cache中存放_ B__在虚拟存储器中存放_ C__。

内容行地址表段表,页表,快表7.常用的地址映象方法有 A 、 B 、组相联映象三种。

全相联直接相联8.总线的通讯方式有A和同步两种。

异步二、选择题(每小题2分,共20分)1.计算机中使用总线结构便于增减外设,同时。

CA. 减少了信息传输量B. 提高了信息传输速度C. 减少了信息传输线的条数D. 三者均正确2.总线结构的主要优点是便于实现系统的模块化,其缺点是。

CA. 传输的地址和控制信息不能同时出现B. 传输的地址和数据信息不能同时出现C. 不能同时具有两个总线主设备D. 不能同时使用多于两个总线设备3. 指令周期是。

计算机组成原理期末考试试题及答案

计算机组成原理期末考试试题及答案一、选择题1、完整的计算机系统应包含______。

DA. 运算器、存储器和操纵器B. 外部设备和主机C. 主机和有用程序D. 配套的硬件设备和软件系统2、计算机系统中的存储器系统是指______。

DA.RAM存储器B.ROM存储器C. 主存储器D. 主存储器和外存储器3、冯·诺依曼机工作方法的根本特点是______。

BA. 多指令流单数据流B. 按地址访问并顺序执行指令C. 堆栈操作D. 存储器按内部选择地址4、以下说法中不正确的选项是______。

DA. 任何可以由软件完成的操作也可以由硬件来完成B. 固件就功能而言类似于软件,而从形态来说又类似于硬件C. 在计算机系统的层次结构中,微程序级属于硬件级,其他四级都是软件级D. 面向高级语言的机器是完全可以完成的5、在以下数中最小的数为______。

CA. (101001)2B. (52)8C. (101001)BCDD. (233)166、在以下数中最大的数为______。

BA. (10010101)2B. (227)8C. (143)5D. (96)167、在机器中,______的零的表示形式是唯一的。

BA. 原码B. 补码C. 反码D. 原码和反码9、针对8位二进制数,以下说法中正确的选项是______。

BA.–127的补码为10000000B.–127的反码等于0的移码BC.+1的移码等于–127的反码D.0的补码等于–1的反码9、一个8位二进制整数采纳补码表示,且由3个“1〞和5个“0〞组成,则最小值为______。

BA. –127B. –32C. –125D. –310、计算机系统中采纳补码运算的目的是为了______。

CA. 与手工运算方法保持一致B. 提高运算速度C. 简化计算机的设计D. 提高运算的精度11、假设某数x的真值为–,在计算机中该数表示为,则该数所用的编码方法是______码。

2021年南京信息工程大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)

2021年南京信息工程大学数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、主存按字节编址,地址从0A4000H到0CBFFFH,共有()字节;若用存储容量为32K×8位的存储芯片构成该主存,至少需要()片。

A.80K,2B.96K,2C.160K,5 C.192K,52、有效容量为128KB的Cache,每块16B,8路组相联。

字节地址为1234567H的单元调入该Cache,其tag应为()。

A.1234HB.2468HC.048DHD.12345H3、下列编码中,能检测出所有长度小于或等于校验位(检测位)长度的突发错的校验码是()。

A.循环冗余校验码B.海明码C.奇校验码D.偶校验码4、在定点机中执行算术运算时会产生溢出,其根本原因是()。

A.主存容量不够B.运算结果无法表示C.操作数地址过大D.栈溢出5、在浮点机中,判断原码规格化的形式的原则是()。

A.尾数的符号位与第一数位不同B.尾数的第一数位为1,数符任意C.尾数的符号位与第一位相同D.阶符与数符不同6、下列关于多总线结构的叙述中,错误的是()。

A.靠近CPU的总线速度较快B.存储器总线可支持突发传送方式C.总线之间需通过桥接器相连D.PCI-Expressx16采用并行传输方式7、在集中式总线控制中,响应时间最快的是()。

A.链式查询B.计数器定时查询C.独立请求D.分组链式查询8、下列描述中,正确的是()。

A.控制器能理解、解释并执行所有指令以及存储结果B.所有数据运算都在CPU的控制器中完成C.ALU可存放运算结果D.输入、输出装置以及外界的辅助存储器称为外部设备9、()可区分存储单元中在放的是指令还是数据。

A.存储器B.运算C.用户D.控制器10、单周期处理器中所有指令的指令周期为一个时钟周期。

下列关于单周期处理器的叙述中,错误的是()。

A.可以采用单总线结构数据通路B.处理器时钟频率较低C.在指令执行过程中控制信号不变D.每条指令的CPI为111、某计算机采用微程序控制器,共有32条指令,公共的取指令微程序包含2条微指令,各指令对应的微程序平均由4条微指令组成,采用断定法(下地址字,段法)确定下条微指令地址,则微指令中下地址字段的位数至少是()。

计算机组成原理试题及答案(考试资料)(K12教育文档)

计算机组成原理试题及答案(考试资料)(word版可编辑修改)编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(计算机组成原理试题及答案(考试资料)(word版可编辑修改))的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为计算机组成原理试题及答案(考试资料)(word版可编辑修改)的全部内容。

组成1一、选择题 (每小题选出一个最合适的答案,每小题2分,共20分)1、若十进制数为37。

25,则相应的二进制数是().(A)100110.01 (B)110101.01 (C) 100101。

1 (D)100101.012、若[x]反=1.1011,则x=(A)—0。

0101 (B)—0.0100 (C)0。

1011 (D)-0。

10113、某机器字长16位,含一位数符,用补码表示,则定点小数所能表示的最小正数是()。

(A)2-15 (B)216 (C)2-1 (D)1-2-154、若采用双符号位补码运算,运算结果的符号位为10,则()。

(A)产生了负溢出(下溢) (B)产生了正溢出(上溢)(C)运算结果正确,为负数(D)运算结果正确,为正数5、在用比较法进行补码一位乘法时,若相邻两位乘数yiyi+1为01时,完成的操作是()。

(A)无 (B)原部分积+[X]补,右移一位(C)原部分积+[-X]补,右移一位(D)原部分积+[Y]补,右移一位6、堆栈指针SP的内容是( ).(A)栈顶地址 (B)栈底地址(C)栈顶内容(D)栈底内容7、在寄存器间接寻址方式中,操作数是从( ).(A)主存储器中读出 (B)寄存器中读出(C)磁盘中读出(D)CPU中读出8、在微程序控制器中,一条机器指令的功能通常由( )。

(完整)计算机组成原理试卷(含答案),推荐文档

机指令字长 16 位,每

个操作数的地址码为 5 位。指令分为零地址码、一地址码和二地址码三种格式。若二地址码

指令有 a 种,零地址有 b 种,如操作码长度固定,则一地址码最多有几种?若操作码长度可

变,则一地址码最多允许有几种?

设一地址码 x 种。

固定长度操作码:26-a-b

(5 分)

操作码长度可变:x=(26-a)*25-b*2-5 (5 分)

与技术

成原理

3.5

(A)

课程编号: 133102 考试方式: 闭卷 考试时间: 分钟

更多的专业资料给更多有 拟卷人(签字):

拟卷日期: 2006- 审核人(签字): 12-5

5. 已知一 CPU 内部

的数据通路

5. 取指令:(5 分)

如下图所示。 指令 STA X (设该指令为单字节, X 为直接地址)的功能是 A (X)。请写出指令 STA X 的

C.取指周期结束 。

中断服务程序。效率高于前者。 4. 比较计算机组成和计算机体系结构。

A.有一个总线请求信号和一个总线响应信号 B.有N个总线请求信号和N个总线响应信号

C.有一个总线请求信号和N个总线响应信号

13. 系统总线中的数据线、地址线和控制线是根据

来划分的。

计算机组成研究的是计算机的内部属性,包括计算机的组成、计算机的数据流以及工作的基 本原理。计算机体系结构研究计算机的为外部特性,汇编语言程序员或编译程序员所看到的

B.外部设备一旦发出中断请求,CPU 应立即响应。

3. 微型计算机的发展通常以

为技术标志。

C.中断方式一般用于处理随机出现的服务请求。

A.操作系统

B.磁盘

C.软件

D.微处理器

2021年南京信息工程大学网络工程专业《计算机组成原理》科目期末试卷A(有答案)

2021年南京信息工程大学网络工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、某计算机使用4体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生访存冲突的地址对是()。

A.8004和8008B.8002和8007C.8001和8008D.8000和80042、某机器的主存储器共32KB,由16片16K×l位(内部采用128×128存储阵列)的DRAM芯片字和位同时扩展构成。

若采用集中式刷新方式,且刷新周期为2ms,那么所有存储单元刷新一遍需要()个存储周期。

A.128B.256C.1024D.163843、在C语言程序中,以下程序段最终的f值为()。

Float f=2.5+1e10;f=f-1e10;A.2.5B.250C.0D.3.54、用海明码对长度为8位的数据进行检/纠错时,若能纠正一位错,则校验位数至少为()。

A.2B.3C.4D.55、下列关于进制的说法中正确的是()。

I.任何二进制整数都可用十进制表示Ⅱ.任何二进制小数都可用十进制表示Ⅲ.任何十进制整数都可用二进制表示IⅣ.任何十进制小数都可用二进制表示A.I、ⅢB. I、Ⅱ、ⅢC.I、Ⅱ、Ⅲ、ⅣD.Ⅱ、IV6、在下面描述的PCI总线的基本概念中,不正确的表述是()。

A.PCI总线支持即插即用B.PCI总线可对传输信息进行奇偶校验C.系统中允许有多条PCI总线D.PCI设备一定是主设备7、总线的数据传输速率可按公式Q=Wf/N计算,其中Q为总线数据传输速率,W为总线数据宽度(总线位宽/8),f为总线时钟频率,N为完成一次数据传送所需的总线时钟周期个数。

若总线位宽为16位,总线时钟频率为8MHz,完成一次数据传送需2个总线时钟周期,则总线数据传输速率Q为()。

A.16Mbit/sB.8Mbit/sC.16MB/sD.8MB/s8、下列部件中,CPU存取速度由慢到快的排列顺序正确的是()。

大学期末计算机考试试题

南京信息工程大学试卷2009-2010学年第一学期计算机基础I 课程试卷( A 卷)本试卷共5 页;考试时间120 分钟;任课教师;出卷时间2009年12月学院专业年级班学号姓名得分注意:答案写在答题册上,在试卷页上做答一律无效一、单选题 (每小题 1分,共 25分)1、计算机辅助设计简称是___ __A、CAMB、CADC、CATD、CAI2、二进制数11000000对应的十进制数是___ __A、384B、192C、96D、3203、下列4种不同数制表示的数中,数值最大的一个是___ __A、八进制数110B、十进制数71C、十六进制数4AD、二进制数10010014、微机病毒系指_____。

A、生物病毒感染B、被损坏的程序C、细菌感染D、特制的具有损坏性的小程序5、为了避免混淆,十六进制数在书写时常在后面加上字母______A、HB、OC、DD、B6、某单位的人事档案管理程序属于_____。

A、工具软件B、应用软件C、系统软件D、字表处理软件7、计算机用来表示存储空间大小的最基本单位是CA、BaudB、bitC、ByteD、Word8、操作系统是。

A、软件与硬件的接口B、主机与外设的接口C、计算机与用户的接口D、高级语言与机器语言的接口9、在计算机运行时,把程序和数据一样存放在内存中,这是1946年由_____领导的研究小组正式提出并论证的。

A、图灵B、布尔C、冯·诺依曼D、爱因斯坦10、对应ASCII码表,下列有关ASCII码值大小关系描述正确的是___ __A、"CR"<"d"<"G"B、"a"<"A"<"9"C、"9"<"A"<"CR"D、"9"<"R"<"n"11、微型计算机的运算器、控制器及内存存储器的总称是__ ___。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

南京信息工程大学试卷2009-2010学年第 1 学期计算机组成原理课程试卷( A 卷) 本试卷共页;考试时间分钟;任课教师马利;出卷时间2009年12月学院专业年级班学号姓名得分一、填空题(每小题1分,共20分)1.在由n台计算机构成的并行计算机中,其运行程序的加速比一般都小于n,其主要原因是___ A__和__ B____。

程序中有不能并行的串行部分存在通信开销2.在计算机系统当中,根据应用条件和硬件资源的不同,数据传输方式可以采用A___传送、B __传送和C___传送三种方式。

并行串行分时3.完成浮点加法或减法时,需要进行对阶、求和、规格化和舍入等步骤,在对阶时,使A 阶向B 阶看齐,使小阶的尾数向C 移位,每D 移一位,其阶码加1,直到两数的阶码相等为止。

小大右右4.在多级存储体系中,Cache存储器的主要功能是___A___,虚拟存储器的主要功能是__B___。

匹配CPU和主存之间的速度匹配主存和辅存之间的速度5.双端口存储器和多模块交叉存储器都属于A___存储器结构。

但是前者采用B___技术,而后者采用C___技术。

并行空间并行时间并行6.相联存储器不是按地址而是按_ A__访问的存储器,其在cache中存放_ B__在虚拟存储器中存放_ C__。

内容行地址表段表,页表,快表7.常用的地址映象方法有 A 、 B 、组相联映象三种。

全相联直接相联8.总线的通讯方式有A和同步两种。

异步二、选择题(每小题2分,共20分)1.计算机中使用总线结构便于增减外设,同时。

CA. 减少了信息传输量B. 提高了信息传输速度C. 减少了信息传输线的条数D. 三者均正确2.总线结构的主要优点是便于实现系统的模块化,其缺点是。

CA. 传输的地址和控制信息不能同时出现B. 传输的地址和数据信息不能同时出现C. 不能同时具有两个总线主设备D. 不能同时使用多于两个总线设备3. 指令周期是。

DA. CPU从主存取出一条指令的时间B. CPU执行一条指令的时间C. 时钟周期时间D. CPU从主存取出一条指令并执行这条指令的时间4. 组合逻辑控制器和微程序控制器的主要区别在于:。

DA. ALU结构不同B. 数据通路不同C. CPU寄存器组织不同D. 微操作信号发生器的构成方法不同5.在微程序控制器中,机器指令与微指令的关系是。

BA. 每条机器指令由一条微指令来执行B. 每条机器指令由一段微程序来解释执行C. 一段机器指令组成的程序可由一条微指令来执行D. 一条微指令由若干条机器指令组成6. 在指令格式中,采用扩展操作码设计方案的目的是。

CA. 减少指令字长度B. 增加指令字长度C. 保持指令字长度不变而增加指令操作的数量D. 保持指令字长度不变而增加寻址空间7. 指令系统中采用不同寻址方式的目的主要是。

BA. 实现存储程序的程序控制B. 缩短指令长度,扩大寻址空间,提高编程灵活性C. 可以直接访问外存D. 提供扩展操作码的可能并降低指令译码难度8. 微程序控制器中,“存储逻辑”是指将控制逻辑存储在中。

AA. ROMB. RAMC. PLAD. Cache9. 某浮点机,采用规格化浮点数表示,阶码用移码表示(最高位代表符号位),尾数用原码表示。

下列哪个数的表示不是规格化浮点数。

BA. 阶码:1111111 尾数:1.1000 (00)B. 阶码:0011111 尾数:1.0111 (01)C. 阶码:1000001 尾数:0.1111 (01)D. 阶码:0111111 尾数:0.1000 (10)10. 最早提出“存储程序”概念的是:。

BA.Babbage B.V·Neumann C.Pascal D.Bell三、计算题(每小题10分,共20分)(1)按步骤写出的10001101海明码(无步骤不得分)K=8 r=4位号: 1 2 3 4 5 6 7 8 9 10 11 12Pi占位: p1 p2 b1 p3 b2 b3 b4 p4 b5 b6 b7 b8p1: b1 b2 b4 b5 b7p2: b1 b3 b4 b6 b7p3: b2 b3 b4 b8p4: b5 b6 b7 b8p1=b1@b2@b4@b5@b7=0 @为异或p1=b1@b3@b4@b6@b7=0p1=b2@b3@b4@b8=1p1=b4@b5@b6@b7@b8=1所以海明码为: 001100011101G1=p1 @b1@b2@b4@b5@b7=0G2=p2 @b1@b3@b4@b6@b7=0G3=p3 @b2@b3@b4@b8=0G4=p4 @b4@b5@b6@b7@b8=0所以G1G2G3G4=0000经过检验无错(2)x= -0.1101,y=0.1011,用补码一位乘法求[x ×y]补=?解 [x]补=11.0011,[-x]补=00.1101 (用双符号表示)[y]补=0.1011 (用单符号表示)部分积 乘数 y n y n+1 说 明00.0000 0.10110+ 00.1101 y n y n+1=10,加[-x]补00.110100.01101 0.1011 右移一位得P 100.001101 0.101 y n y n+1=11,右移一位得 P 2+ 11.0011 y n y n+1=01,加[x]补11.01100111.1011001 0.10 右移一位得P 3+ 00.1101 y n y n+1=10,加[-x]补00.100000100.01000001 0.1 右移一位得P 4+ 11.0011 y n y n+1=01,加[x]补11.01110001 最后一步不移位即 [x ×y]补=1.01110001四、综合题(每小题8分,共40分)1、请画出三总线结构CPU 内存内存总线IOP(通道)系统总线I/O 接口I/O 接口I/O 总线…2、某假想机主要部件如图1所示。

其中:M ——主存储器 MBR ——主存数据寄存器IR ——指令寄存器, MAR ——主存地址寄存器PC 一—程序计数器 R 0- R 3——通用寄存器C ,D ——暂存器要求根据此数据通路图,画出加法指令“ADD(R1),(R2)+”的执行流程图。

该指令的含义是进行求和操作,源操作数地址在寄存器R1中,目的操作数寻址方式为自增型寄存器间址方式(先取地址后加1)。

图1 数据通路图3、某16位机器所使用的指令格式和寻址方式如下所示,该机有2个20位基址寄存器,4个16位变址寄存器,16个16位通用寄存器,指令汇编格式中的S(源),D(目标)都是通用寄存器,m是主存的一个单元,三种指令的操作码分别是MOV(OP) =(A)H,STA(OP)=(1B)H, LDA(OP)=(3C)H, MOV是传送指令,STA为写数指令,LDA为读数指令。

15 10 9 8 7 4 3 0OP —目标源MOV S,D15 10 9 8 7 4 3 0OP 基址 源 变址 STA S,M位 移 量15 10 9 8 7 4 3 0OP — 目标 LDA S,M20位地址(1)第一种指令是单字长二地址指令,RR 型;第二种指令是双字长二地址指 令RS 型,其中S 采用基址寻址或变址寻址,R 由源寄存器决定;第三种也是双字二地址指令,RS 型,其中R 由目标寄存器决定,S 由20位地址(直接寻址)决定。

(2)处理器完成第一种指令所花的时间最短,因为是RR 型指令,不需要访问存储器。

第二种指令所花的时间最长,因为是RS 型指令,需要访问存储器,同时要进行寻址方式的变换运算(基址或变址),这也要时间。

第二种指令的执行时间不会等于第三种指令,因为第三种指令虽也访问存储器,但节省了求有效地址运算的时间开销。

4、据微程序控制器组成图简述工作过程OP 指令寄存器IR 地址转移逻辑微地址寄存器状态条件………微命令信号控制存储器S 字段控 制 字 段地址译码微命令寄存器图3 微程序控制器组成原理框图工作过程1 取机器指令 CM --取指微指令---→ UIR --微指令字段-→ 译码器 –微命令--→主存 ---机器指令→ IR2 转微程序入口 IR ---操作码-→ 微地址形成电路 ---微程序入口--→ UAR ---→CM----首条微指令--→ UIR3 执行首条微指令: UIR ----微命令字段-→ 译码器 -----微命令-→ 操作部件4取后续微指令 : 微地址字段现行微地址 ----→ 微地址形成电路----后续微地址---→UAR----→运行状态CM ----后续微指令-→ UIR红色字体为箭头上的字5、有一个16K ×16位的存储器,由1K ×4位的动态RAM 芯片构成(芯片内是64×64结构),问:(1)总共需要多少RAM芯片?(2)存储体的组成框图。

(3)采用异步方式,如单元刷新间隔不超过2 ms,则刷新信号周期是多少?(4)如采用集中式刷新方式,存储器刷新一遍最少用多少读/写周期?(1)芯片1K×4位,片内地址线10位(A9--A0 ),数据线4位。

芯片总数为:(16K×16)/(1K×4)=16×4=64片(2)存储器容量为16K,故地址线总数为14位(A13─A0),其中A13A12A11A10通过4:16译码器产生片选信号CS0─CS15。

(3)刷新信号周期为:2ms/64=31.3us。

(4)若用集中式刷新,则刷新一遍用64个读/写周期。