管脚分配表

常用电子器件管脚排列图

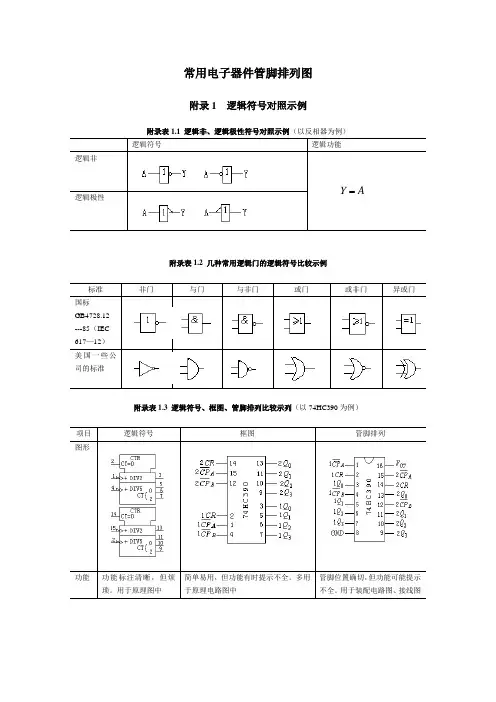

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

管脚分配

SCLK

H17

CS#

K17

DOUT

J18

EDA/SOPC开发平台

串行DAC模块(ADC7513)

SCLK

F20

CS#

F21

DIN

E20

EDA/SOPC开发平台

可调数字时钟模块CLK

CLK

N2

24MHz~1Hz,共10个时钟可选

模拟信号源

接AD的内部输入端口

EDA/SOPC开发平台

Y1

CAS#

W3

CKE

Y3

WE#

V4

CLK

AA7

BA0

Y5

CS#

Y4

BA1

AA3

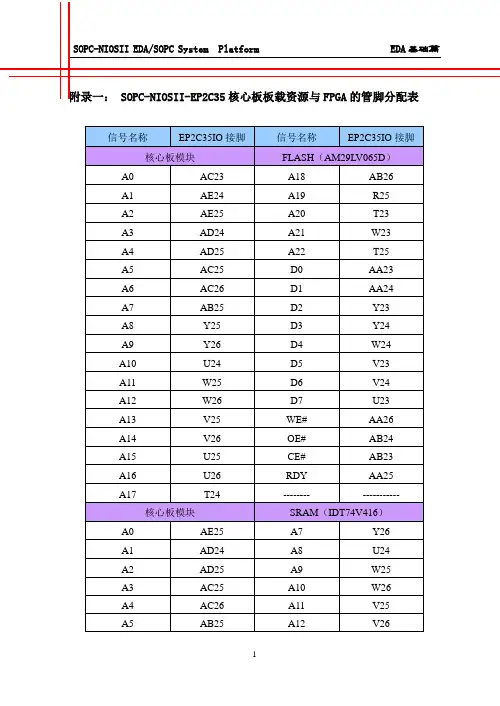

信号名称

EP2C35IO接脚

信号名称

EP2C35IO接脚

核心板模块

SDRAM(HY57V561620)

D0

P3

A0

AB3

D1

P4

A1

AB4

D2

R3

A2

AC3

D3

R4

A3

AD3

D4

T3

A4

AE2

D5

T4

A5

AD2

D6

U3

A6

-----------

核心板模块

SRAM(IDT74V416)

A0

AE25

A7

Y26

A1

AD24

A8

U24

A2

AD25

A9

W25

A3

AC25

A10

W26

A4

AC26

A11

V25

A5

AB25

A12

常用电子器件管脚排列图

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

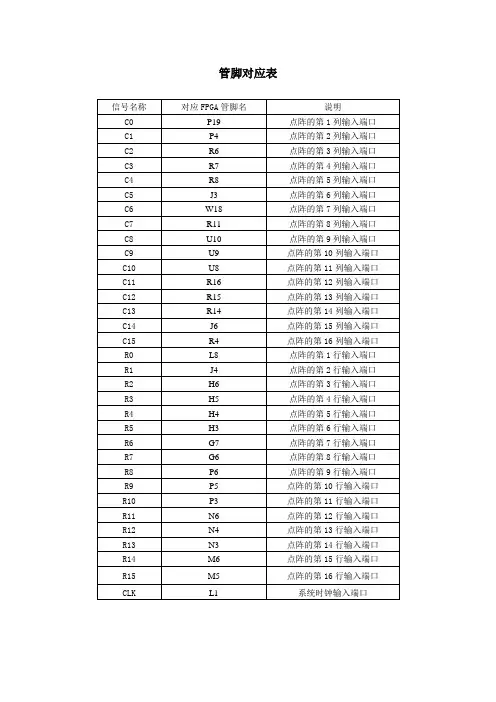

管脚对应表

点阵的第14行输入端口

R14

M6

点阵的第15行输入端口

R15

M5

点阵的第16行输入端口

CLK

L1

系统时钟输入端口

C9

U9

点阵的第10列输入端口

C10

U8

点阵的第11列输入端口

C11

R16

点阵的第12列输入端口

C12

R15

点阵的第13列输入端口

C13

R14

点阵的第14列输入端口

C14

J6

点阵的第15列输入端口

C15

R4

点阵的第16列输入端口

R0

L8

点阵的第1行输入端口

R1

J4

点阵的第2行输入端口

R2

H6

点阵的第3行输入端口

管脚对应表

信号名称

对应FPGA管脚名

说明

C0

P19

点阵的第1列输入端口

C1

P4

点阵的第2列输入端口

C2

R6

点阵的第3列输入端口

C3

R7

点阵的第4列输入端口

C4

R8

点阵的第5列输入端口

C5

J3

点阵的第6列输入端口

C6

W18

点阵的第7列输入端口

C7

R11

点阵的第8列输入端口

C8

U10

点阵的第9列输入端口

R3

H5

点阵的第4行输入端口

R4

H4

点阵的第5行输入端口

R5

H3

点阵的第6行输入端口

R6

G7

点阵的第7行输入端口

R7

G6

点阵的第8行输入端口

R8P6点阵Fra bibliotek第9行输入端口

74LS138管脚功能.

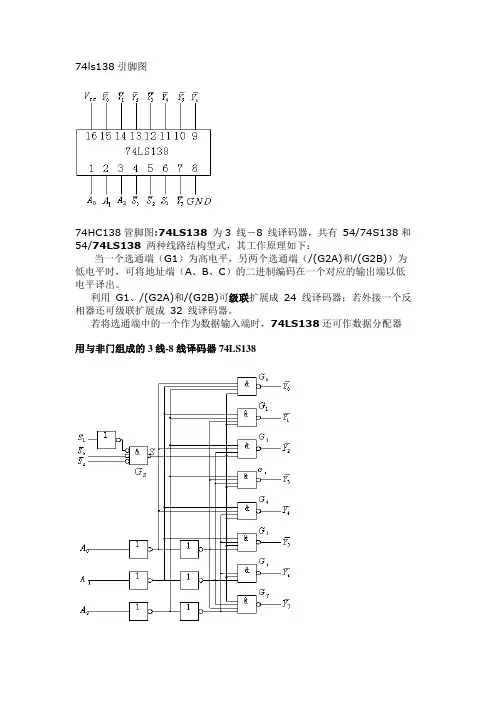

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

串口管脚分布

6

DSR

数据准备好(Data Set Ready)

6

DSR

数据准备好(Data Set Ready)

7

RTS

请求发送(Request To Send)

4

RTS

请求发送(Request To Send)

8

CTS

清除发送(Clear To Send)

5

CTS

清除发送(Clear To Send)

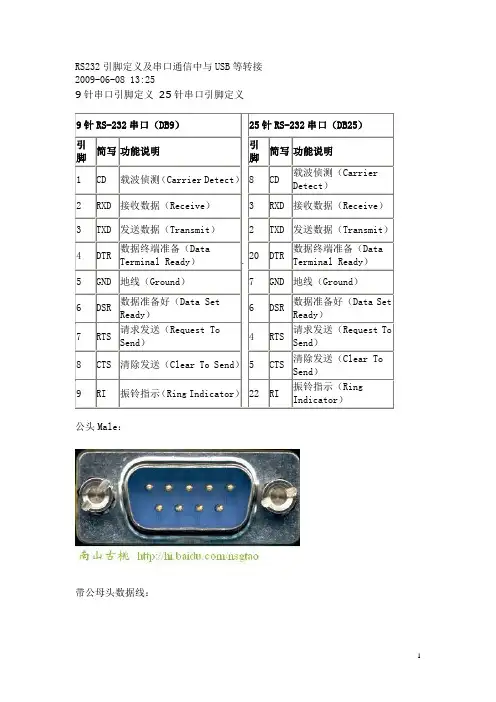

RS232引脚定义及串口通信中与USB等转接

2009-06-08 13:25

9针串口引脚定义25针串口引脚定义

9针RS-232串口(DB9)

.

25针RS-232串口(DB25)

引脚

简写

功能说明

引脚

简写

功能说明

1

CD

载波侦测(Carrier Detect)

8

CD

载波侦测(Carrier Detect)

2

RXD

接收数据(Receive)

3

RXD

接收数据(Receive)

3

TXD

发送数据(Transmit)

2

TXD

发送数据(Transmit)

4

DTR

数据终端准备(Data Terminal Ready)

20

DTR

数据终端准备(Data Terminal Ready)

5

GND

地线(Ground)

7Hale Waihona Puke GND9RI

振铃指示(Ring Indicator)

22

RI

振铃指示(Ring Indicator)

公头Male:

FPGA管脚分配图

169

FLAS H_ CS

156

音频 CODEC 模块(大板)

信号名称

对应 FPGA 引脚

SDIN

27

SCLK

33

CS

28

音频 CODEC 模块(小板)

信号名称

对应 FPGA 引脚

SDIN

93

SCLK

94

CS

88

音源模块

RESET

86

DATA

84

BUS Y

153

时钟源模块

信号名称 CLOCK(大板) CLOCK(小板)

216 VGA 接口(大板)

对应 FPGA 引脚

R

58

G

59

B

60

HS

61

VS 信号名称

62 VGA 接口(小板)

对应 FPGA 引脚

R

239

G

238

B

237

HS

235

VS 信号名称

236 PS/2 接口(大板上)

对应 FPGA 引脚

CLOCK

49

DATA 信号名称

82 PS/2 接口(大板下)

对应 FPGA 引脚

98

DB2

95

DB3

143

DB4

141

DB5

140

DB6

139

DB7

138

DB8

136

DB9

135

DB10

134

DB11

133

DB12

132

DB13

131

DB14

128

DB15

127

DB16

116

DB17

T2C5_T2C8_V5管脚分配表

管脚标号FPGA 管脚IO 方向功能SYS_CLK123I 时钟输入1SYS_CLK2132I 时钟输入2SYS_nRST 56IFPGA 复位LED06O LED15O LED23O LED34O SD_DATA031 I/O SD_DATA130 I/O SD_DATA233 I/O SD_DATA335 I/O SD_DATA434 I/O SD_DATA537 I/O SD_DATA639 I/O SD_DATA741 I/O SD_DATA877 I/O SD_DATA960 I/O SD_DATA1059 I/O SD_DATA1158 I/O SD_DATA1257 I/O SD_DATA1345 I/O SD_DATA1448 I/O SD_DATA1547 I/O SD_ADDR082O SD_ADDR186O SD_ADDR288O SD_ADDR387O SD_ADDR470O SD_ADDR569O SD_ADDR668O SD_ADDR767O SD_ADDR872O SD_ADDR975O SD_ADDR1084O SD_ADDR1174O SD_BA081O SD_BA180O SD_DQML 40O SD_DQMH61OEP2C5_EP2C8_V5核心板管脚分配表4个独立LED 灯SDRAM 数据总线SDRAM 地址总线SDRAM 的BANK 地址数据掩码SD_CS 76O 片选SD_RAS 46O 行地址选通SD_CAS 43O 列地址选通SD_WE 44O 写允许SD_CKE 63O 时钟使能SD_CLK 64O 时钟输入FLASH_DQ0180I/O FLASH_DQ1179I/O FLASH_DQ2176I/O FLASH_DQ3175I/O FLASH_DQ4173I/O FLASH_DQ5171I/O FLASH_DQ6170I/O FLASH_DQ7169I/O FLASH_ADDR0181O FLASH_ADDR1193O FLASH_ADDR2192O FLASH_ADDR3191O FLASH_ADDR4189O FLASH_ADDR5188O FLASH_ADDR6187O FLASH_ADDR7185O FLASH_ADDR8197O FLASH_ADDR9195O FLASH_ADDR10199O FLASH_ADDR11198O FLASH_ADDR12200O FLASH_ADDR13205O FLASH_ADDR14203O FLASH_ADDR15207O FLASH_ADDR16206O FLASH_ADDR17208O FLASH_ADDR1814O FLASH_ADDR1913O FLASH_ADDR2012O FLASH_ADDR2111O FLASH_ADDR2210O FLASH_CE 201O 片选FLASH_WE 165O 写信号(与网络芯片共用)FLASH_OE168O读信号(与网络芯片共用)FLASH 地址总线(与实验板V5的网络接口芯片共用地址总线)FLASH 数据总线(与实验板V5的网络接口芯片、LCD12864、LCD1602共用数据总线)管脚标号FPGA 管脚IO 方向功能KEY097I KEY199IKEY295I KEY396I 78LED_COM0137O 78LED_COM1135O 78LED_COM2139O 78LED_COM3138O 78LED_COM4142O 78LED_COM5141O 78LED_COM6144O 78LED_COM7143O 78LED_DATA0133I/O 78LED_Da 78LED_DATA1127I/O 78LED_Db 78LED_DATA2116I/O 78LED_Dc 78LED_DATA3117I/O 78LED_Dd 78LED_DATA4128I/O 78LED_De 78LED_DATA5134I/O 78LED_Df 78LED_DATA6115I/O 78LED_Dg 78LED_DATA7118I/O 78LED_Dh KB_DATA 94I PS2数据线KB_CLK 92I PS2时钟线I2C_SCL 147O I2C 时钟线I2C_SDA 149I/O I2C 数据线LCD12864_CS1160O LCD12864_CS2161O LCD12864_E 162O LCD12864使能LCD1602_E 163O LCD1602使能RTL8019_CS 150O 网络芯片片选信号RTL8019_INT 151I 网络芯片中断信号RTL8019_RST 164O 网络芯片复位信号RXD_UART 145I TXD_UART146O实验板_V5各功能管脚分配FOR EP2C5_EP2C8LCD12864左右屏片选信号RS232串口4个按键7位8段数码管公共端口RXD_USB106I TXD_USB107OVGA_HS108O VGA_VS110O VGA_R112O VGA_G113O VGA_B114OAD_CLK89OAD_CS105O AD_DATA90I TLC5620_CLK104O TLC5620_DATA103O TLC5620_LDAC101O TLC5620_LOAD102O AD转换器TLC549接口DA转换器TLC5620接口USB_UART口VGA接口。

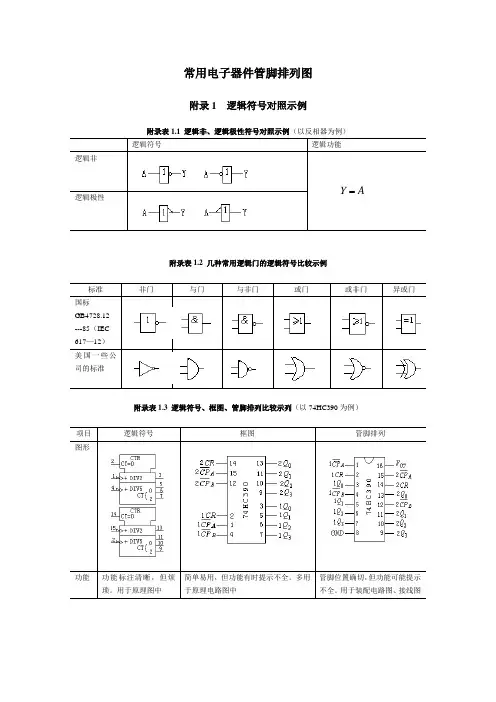

常用电子器件管脚排列图

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC 390为例)附录2 集成电路1. 集成电路命名方法 集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍 集成电路I C 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有L M (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与C M OS 集成电路的注意事项 (1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

附录图 2.1双列直插式集成电路的引脚排使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

②电路的各输入端不能直接与高于和V 5.5+低于的低内V 5.0-阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

芯片管脚排列图整理

附录7 常用集成电路引脚排列一、 集成运算放大器二、集成比较器 三、集成功率放大器五、74附录图7.1 LM741 附录图7.2 LM324附录图7.3 LM358 附录图7.4 0P07附录图7.5 LM339 附录图7.6 LM311附录图7.7 LM386 附录图7.8 LM380附录图7.9 556双时基电路 附录图7.10 555 时基电路附录图7.11 74LS00 四2输入 附录图7.12 74L S02四2 正与非门 输入正或非门 附录图7.13 74LS04 六反相器 附录图7.14 74L S08 四2 输入正与门附录图15 74LS10 三3输入 附录图16 74LS13双4输入正 正与非门 与非门(有施密特触发器) 附录图17 74LS14 六反 附录图18 74LS27 三输入 相器施密特触发器 正或非门附录图19 74LS32 四2输入 附录图20 74LS86四异或门正或门附录图7.21 74LS42、74145 附录图7.22 74LS 46、47、48、4线 – 10线 译码器 247、248249 BCD 七段译码器/ 驱动器附录图23 74LS73 双下降 附录图24 74LS74双上升沿D沿JK 触发器 触发器附录图25 74H78双主从JK 触发器 附录图26 74L S90十进制 异步计数器 (公共时钟、公共清除)附录图27 74LS138 3线– 8线 附录图.28 74LS139 双2 译码器 线–4线译码器 附录图29 74LS160 十进制 附录图30 74L S190十进制 同步计数器 同步加 / 减计数器 附录图31 74LS192 十进制同步 附录图32 74LS194 4位双向 加 / 减计数器(双时钟) 移位寄存器(并行存取)74LS193 4位二进制同步加 / 减计数器(双时钟)附录图7.33 4001四2输 附录图7.34 4002 双4入正或非门 输入正或非门六、 CMOS 集成电路附录图7.35 4011四2输入 附录图7.36 4012 双4输 正与非门 入正与非门附录图.37 4013双主从 附录图38 4017 十进制计数/ 型D 触发器 脉冲分配器 附录图7.39 4022 八进制计 附录图7.40 4023 三3输数/脉冲分配器 入正与非门附录图7.41 4071 四 附录图7.42 4070 四异 输入正或门 或门 附录图7.43 4066 四双向 附录图7.44 4069 六模拟开关 反相器 附录图7.45 40106 六施 附录图7.46 4082 双4输入密特触发器 正与门 附录图7.47 40110 计数 / 附录图7.48 40160 锁存 /七段译码 / 驱动器 十进制同步计数器 附录图7.49 40192 十进制同步加 附录图7.50 40194双向移位 / 减计数器 (双时钟) 寄存器 (并行存取) 40193 四位二进制加 / 减计数器 (双时钟)CD4060引脚排列 CD40110引脚排列 其它信息:高性能的静态C MOS 技术;150MHz(6.57ns 周期时间);低功耗(1.8V 核,135MHz ;1.9V 核,150MH z ;3.3V I /O )设计;3.3V Flas h 编程电压;片上存储;达到128K×16闪存(8×4K 和6×16K 扇区);2K×16 OTP ROM ;L0和L1:2个4K×16单存取RAM 块;H0:1个8K×16单存取RA M 块;M0和M1:2个1K×16单存取RAM 块;引导ROM (4K×16), 软件引导模块;标准匹配图标;时钟和系统控制;提供动态P LL 系数改变;片上振荡器;看门狗计时器模块;3个外部中断;提供45个外围设各中断;128位安全性开关/上锁;保护Flas h/OTP 和L0/L1单存取RAM ;主要控制外围设各;2个事件管理器(EVA ,EVB);与240×A 驱动器兼容;3个32位CPU 计时器;外围设各串行端口;串行外围设备中断;2个串行通信中断,标准UA RT ;加强控制器区域网络;具有SPI 模式的多通道缓冲串口(M cBSP );12位模数转换器,16通道;2×8通道输入多工器;2个采样保持;单个转换时间:200ns ;管道转换时间:60ns ;多达56个单独可编程,多路通用输入/输出(GPIO )引脚;先进的仿真功能;分析与断点功能;开发工具包括:AN SI C /C ++编译器/汇编器/连接器;DSP /BIOSTM ;JTAG 扫描控制器;评估模块;支持广泛的第三方合作数字电机控制;低功率模式,并节省电源;支持空闲,待机,停止模式;禁用个别外围设备时钟;封装选项:具有外部存储接口的176引脚的低轮廓四方扁平封装;温度选项:A :-40~85℃ (GHH ,ZHH ,PGF ,PBK);S/Q :-40~125℃ (GHH ,ZHH ,PGF ,P BK)附录图51 4511二进制七段 附录图52 45128选1数据选择器 译码器 附录图53 4027 双JK 触发器 附录图7.54 4025 三3输入正或非门。